Submitted:

10 December 2025

Posted:

11 December 2025

You are already at the latest version

Abstract

Keywords:

1. Introduction

2. Materials and Methods

3. Results

4. Discussion

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Park J S, Kang D-H, Kwak S M, et al. Low-temperature smoothing method of scalloped DRIE trench by post-dry etching process based on SF6 plasma[J]. Micro and Nano Systems Letters, 2020, 8(1): 1–8.

- Cho D, Hong S, Lee M, et al. A review of silicon microfabricated ion traps for quantum information processing[J]. Micro and Nano Systems Letters, 2015, 3(1): 1-12. [CrossRef]

- Zhu F, Zhang X, Zhang H. Formation mechanism of multi-functional black silicon based on optimized deep reactive ion etching technique with SF6/C4F8[J]. Science China Technological Sciences,2015,58(2):381-389. [CrossRef]

- Kim T, Lee J. Optimization of deep reactive ion etching for microscale silicon hole arrays with high aspect ratio[J]. Micro and Nano Systems Letters, 2022, 10(1). [CrossRef]

- Wu B, Yi R, Ding X, et al. Surface evolution mechanism for atomic-scale smoothing of Si via atmospheric pressure plasma etching[J]. Journal of Manufacturing Processes,2024,132353-132362. [CrossRef]

- Chen H, Zhu C, Lin G, et al. Deep silicon etching technology and applications: a review[J]. Journal of Micromechanics and Microengineering, 2025, 35(8):083001. [CrossRef]

- Gao F, Sami Y, Markku K, et al. Smooth silicon sidewall etching for waveguide structures using a modified Bosch process[J]. Journal of Micro/Nanolithography, MEMS, and MOEMS, 2014, 13(1): 013010.

- Sygaya T, Yoon D. H, Yamazaki H et al. Simple and Rapid Fabrication Process of Porous Silicon Surface Using Inductively Coupled Plasma Reactive Ion Etching[J]. Journal of Microelectromechanical Systems, 2020, 29(1): 62-6.

- Golishnikov A A, Dyuzhev A N, Paramonov V V, et al. Research and Development of a Deep Anisotropic Silicon Plasma Etching Process with Reduced Sidewall Roughness of the Structures[J]. RussianMicroelectronics,2025,53(7):676-681. [CrossRef]

- Li Y, Yu L, Zhang Y, et al. Sub-200-nm-diameter cylindrical silicon nanopillars with high aspect ratio (40:1) fabricated by SF6/C4F8-modulated ICP-RIE[J]. Materials Science in Semiconductor Processing,2025,198109817. [CrossRef]

- Lakrathok A, Supadech J, Leepattarapongpan C, et al. Design of the comb-drive structure to reduce asymmetry lateral plasma etching on the cavity SOI substrate for MEMS fabrication[J]. Journal of Physics: Conference Series,2025,2934(1):012027-012027.

- Leyi Z, Zhihong G, Yongzhi F, et al. Research on the difference in etching rates of SiO2 at the top and bottom of a high-aspect-ratio trench in C4F8/Ar/O2 plasma etching[J]. Journal of Vacuum Science& Technology A, 2025, 43(3): 033003.

- Shi Z, Jefimovs K, Romano L, et al. Towards the Fabrication of High-Aspect-Ratio Silicon Gratings by Deep Reactive Ion Etching[J]. Micromachines, 2020, 11(9): 864. [CrossRef]

- Tang Y, Saandoughsa A, OWEN K J, et al. Ultra Deep Reactive Ion Etching of High Aspect-Ratio and Thick Silicon Using a Ramped-Parameter Process[J]. Journal of Microelectromechanical Systems, 2018, 27(4): 686-697.

- Haoming G, Shengbin C, Lei L, et al. A review on the mainstream through-silicon via etching methods[J]. Materials Science in Semiconductor Processing,2022,137.

- Barrantes A A J, Mastrangeli M, Thoen J D, et al.Superconducting High-Aspect Ratio Through-Silicon Vias with DC-Sputtered Al for Quantum 3D integration[J]. IEEE Electron Device Letters,2020, (99):1. [CrossRef]

- Gao Z, Ma Z, Gao L, et al. Etching mechanism of high-aspect-ratio array structure[J]. Microelectronic Engineering,2023,279.

- J.A. A, M. M, D.J. T, et al. Fabrication of Al-Based Superconducting High-Aspect Ratio TSVS for Quantum 3D Integration[J].Proceedings of the IEEE International Conference on Micro Electro Mechanical Systems (MEMS), 2020:932-935.

- Ni Z-H, Xia Y, Hu C F, et al. Metallization filling and electrical performance of high-aspect-ratio through silicon via with electroless deposited Co liner[J]. ECS Journal of Solid State Science and Technology, 2025, 14(5): 054003. [CrossRef]

- Zhang D, Smith D, Kumarapuram G, et al. Process development and optimization for 3 μm high aspect ratio via-middle through-silicon vias at wafer level[J]. IEEE Transactions on Semiconductor Manufacturing, 2015, 28(4): 454–460. [CrossRef]

- Aixi P, Medhat, Zheng, et al. Fabrication of ultrahigh aspect ratio Si nanopillar and nanocone arrays[J]. Journal of Vacuum Science& Technology B, 2023, 41(2): 023001.

- Nonaka T, Takahashi K, Uchida A, et al. Morphology of films deposited on the sidewall during the Bosch process using C4F8 plasmas[J]. Journal of Micromechanics and Microengineering,2024,34(8):085014.

- Tomoyuki Nonaka, Kazuo Takahashi, Akimi Uchida, et al. Effects of C4F8 plasma polymerization film on etching profiles in the Bosch process[J]. Journal of Vacuum Science& Technology A, 2023, 41(6): 063004. [CrossRef]

- BatesL R, Thamban SL P, GoecknerJ M, et al. Silicon etch using SF6/C4F8/Ar gas mixtures[J]. Journal of Vacuum Science & Technology A: Vacuum, Surfaces, and Films,2014,32(4):041302.

- Jack Nos, Sylvain Iséni, Martin Kogelschatz, et al. Cryogenic cyclical etching of Si using CF4 plasma passivation steps: The role of CF radicals[J]. Applied Physics Letters, 2025, 126(3): 031602. [CrossRef]

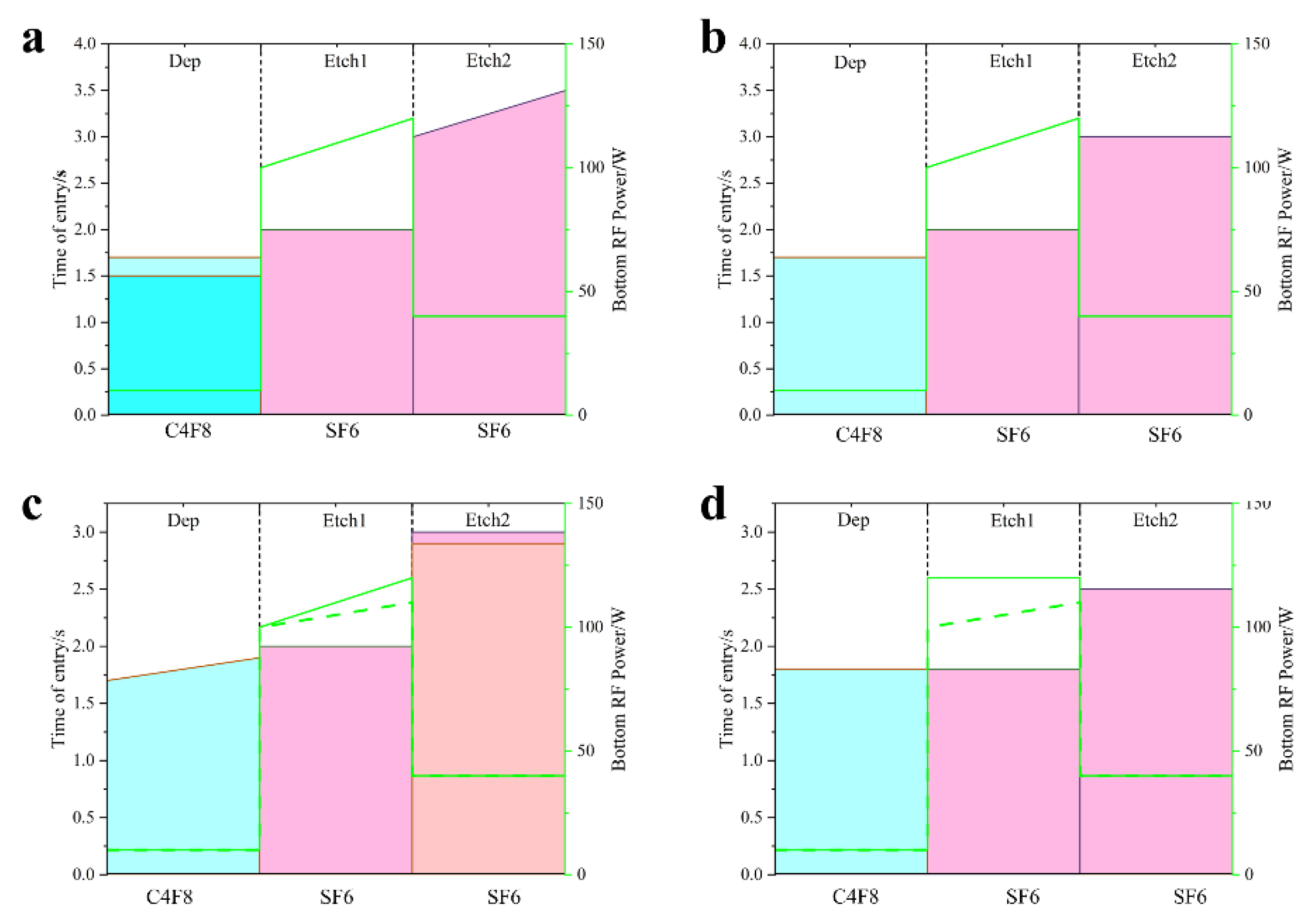

| Parameters | Cycles | Time/s | center C4F8/sccm | edge C4F8/sccm | center SF6/sccm | edge SF6/sccm | LFPower/W |

|---|---|---|---|---|---|---|---|

| Dep | 100 | 1.5 | 180 | 0 | 0 | 0 | 10 |

| Etch1 | 100 | 2 | 0 | 0 | 300 | 300 | 100 |

| Etch2 | 100 | 3 | 0 | 0 | 300 | 300 | 40 |

| Parameters | Cycles | Time(sec) | center C4F8/sccm | edge C4F8/sccm | LFPower | |

|---|---|---|---|---|---|---|

| A | Dep | 100→150→180 | 1.5 | 180 | 0 | 10 |

| Etch1 | 2 | 0 | 0 | 100 | ||

| Etch2 | 3 | 0 | 0 | 40 | ||

| B | Dep | 180 | 1.5/1.5→1.7 | 180 | 0 | 10 |

| Etch1 | 2 | 0 | 0 | 100-120/100-110 | ||

| Etch2 | 3-3.5/3-3.2 | 0 | 0 | 40 | ||

| C | Dep | 180 | 1.7/1.7-1.9 | 180 | 50 | 10 |

| Etch1 | 2 | 0 | 0 | 100-110→100-120 | ||

| Etch2 | 2.9→3 | 0 | 0 | 40 | ||

| D | Dep | 200 | 1.8 | 180 | 50 | 10 |

| Etch1 | 1.8 | 0 | 0 | 100-100→120 | ||

| Etch2 | 2.5 | 0 | 0 | 40 |

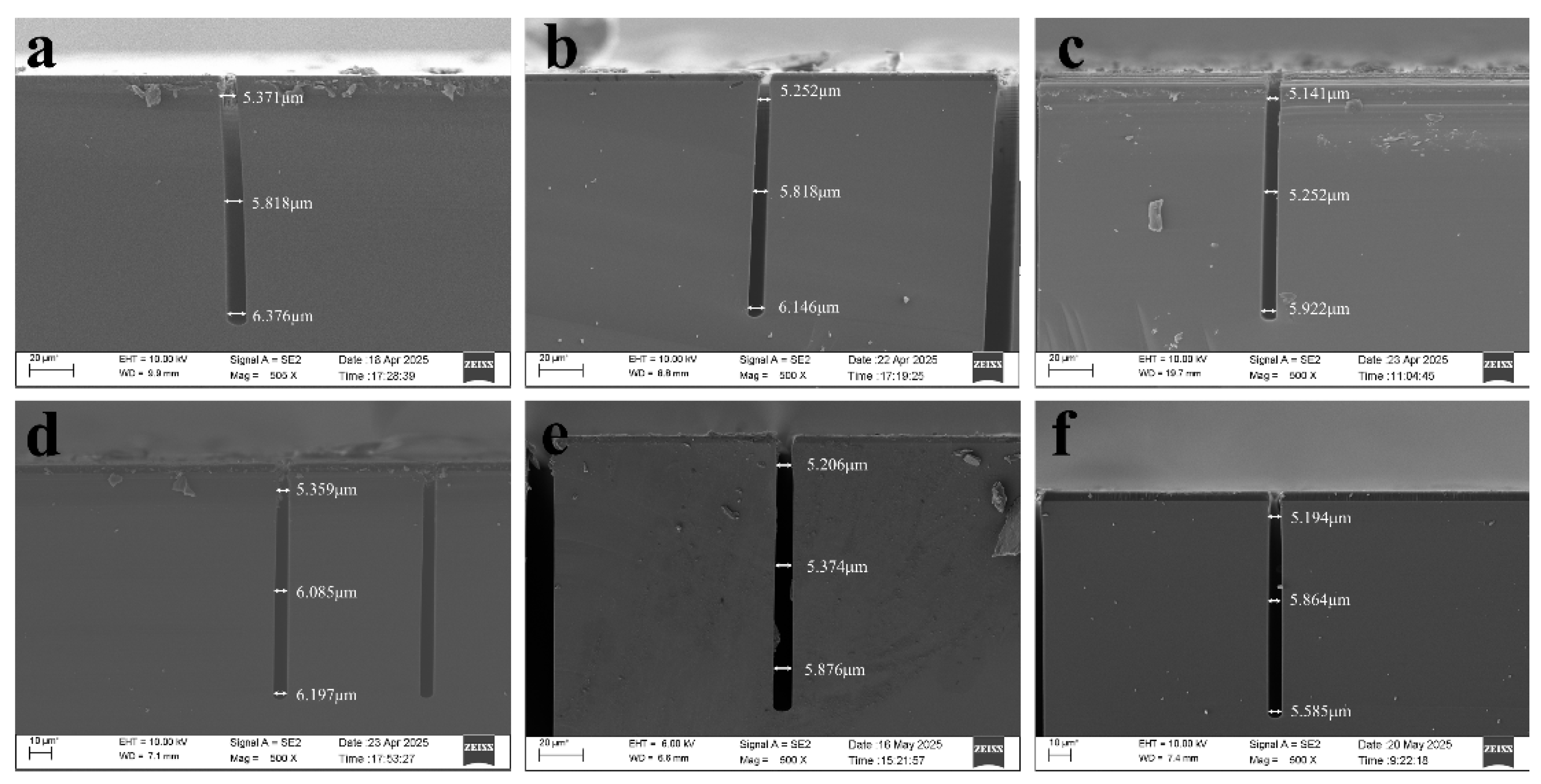

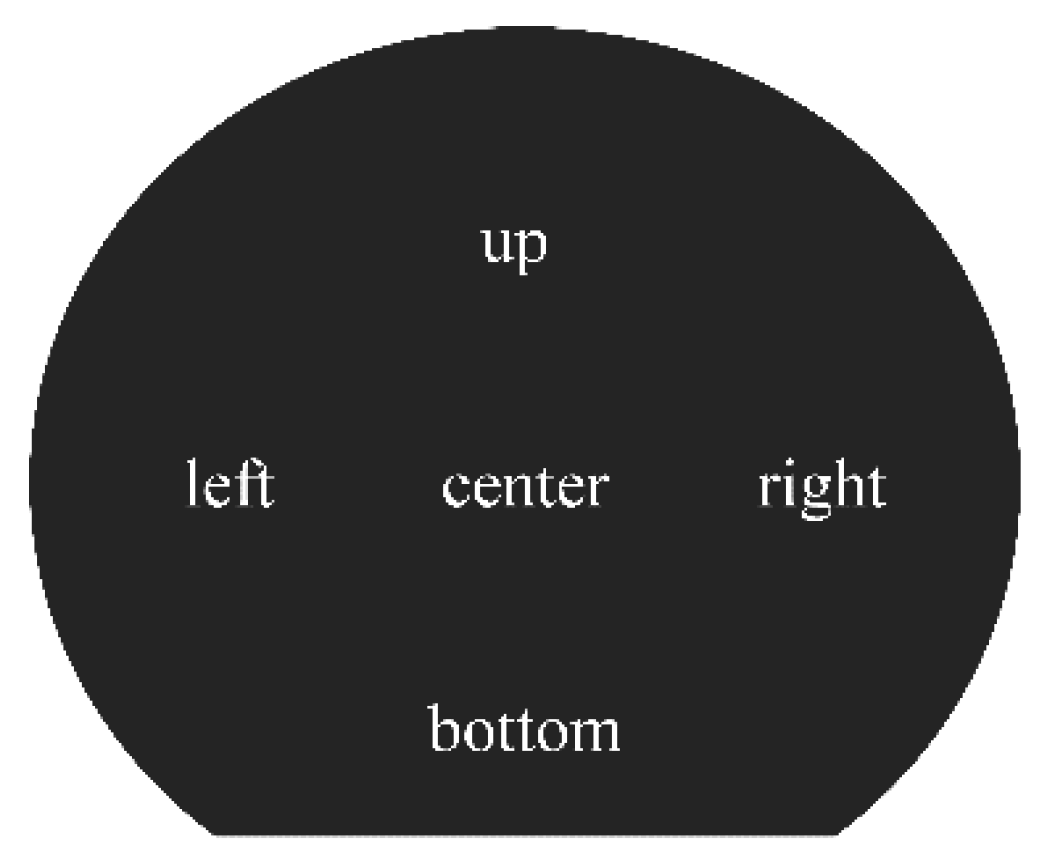

| Position | Etch Depth/μm | Opening Size Difference/μm |

|---|---|---|

| center | 106.662 | 0.279 |

| up | 106.1 | 0.279 |

| bottom | 108.3 | 0.335 |

| left | 109.427 | 0.340 |

| right | 108.3 | 0.340 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).