Submitted:

27 April 2025

Posted:

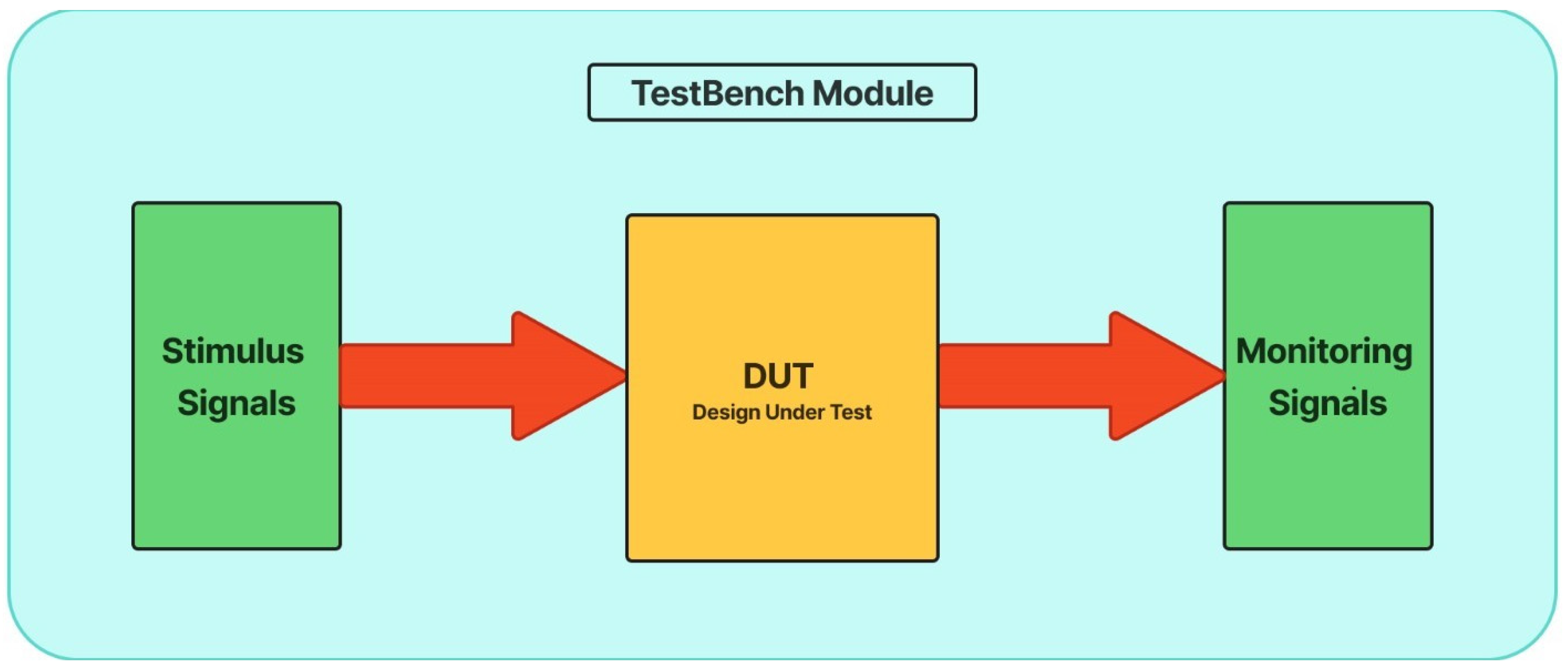

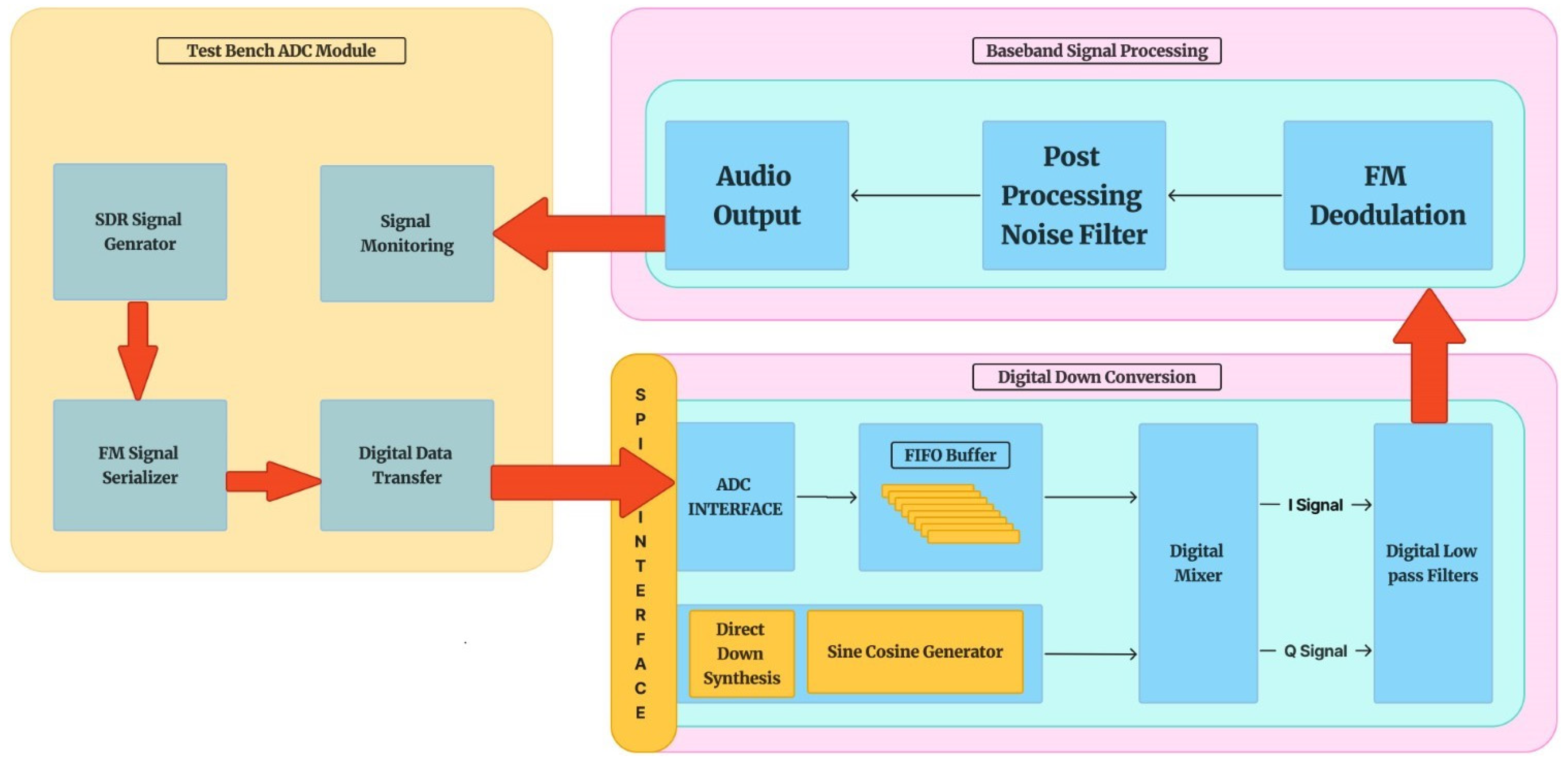

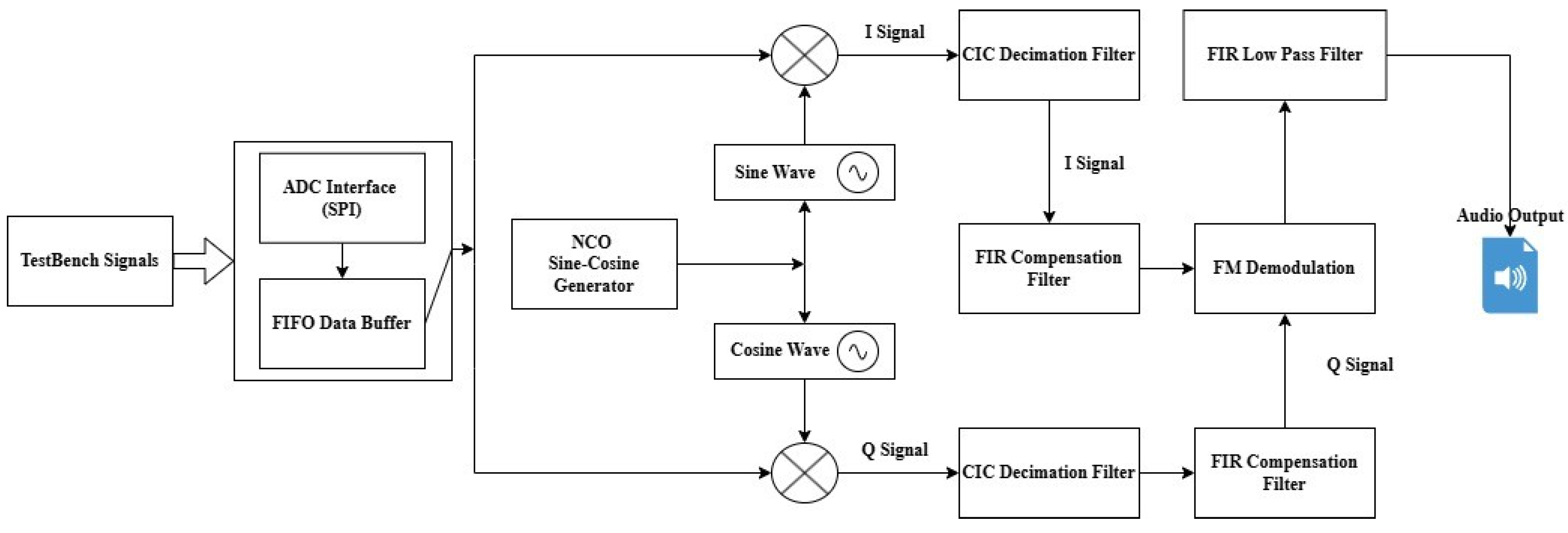

29 April 2025

You are already at the latest version

Abstract

Keywords:

1. Introduction

2. Literature

3. Methodology

-

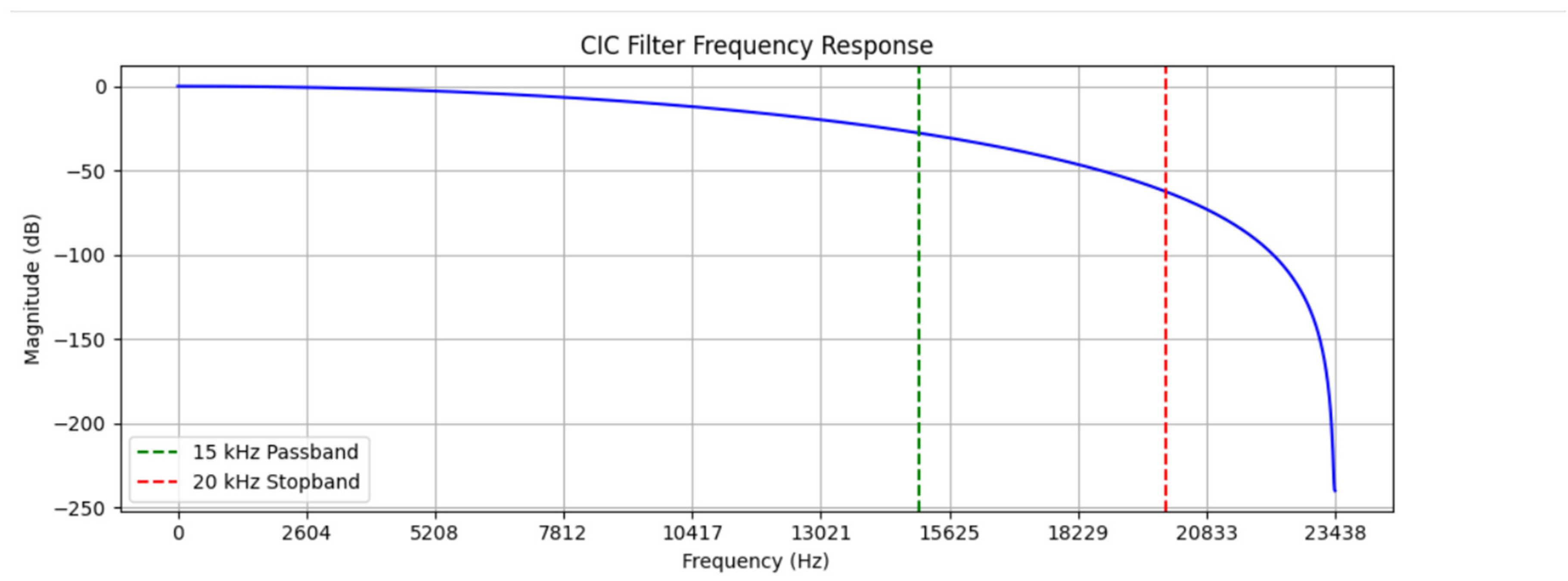

For this, the Design uses (N=4), (M=2), (D=64).Integrator Section,

- Comb Section,

4. Results and Discussion

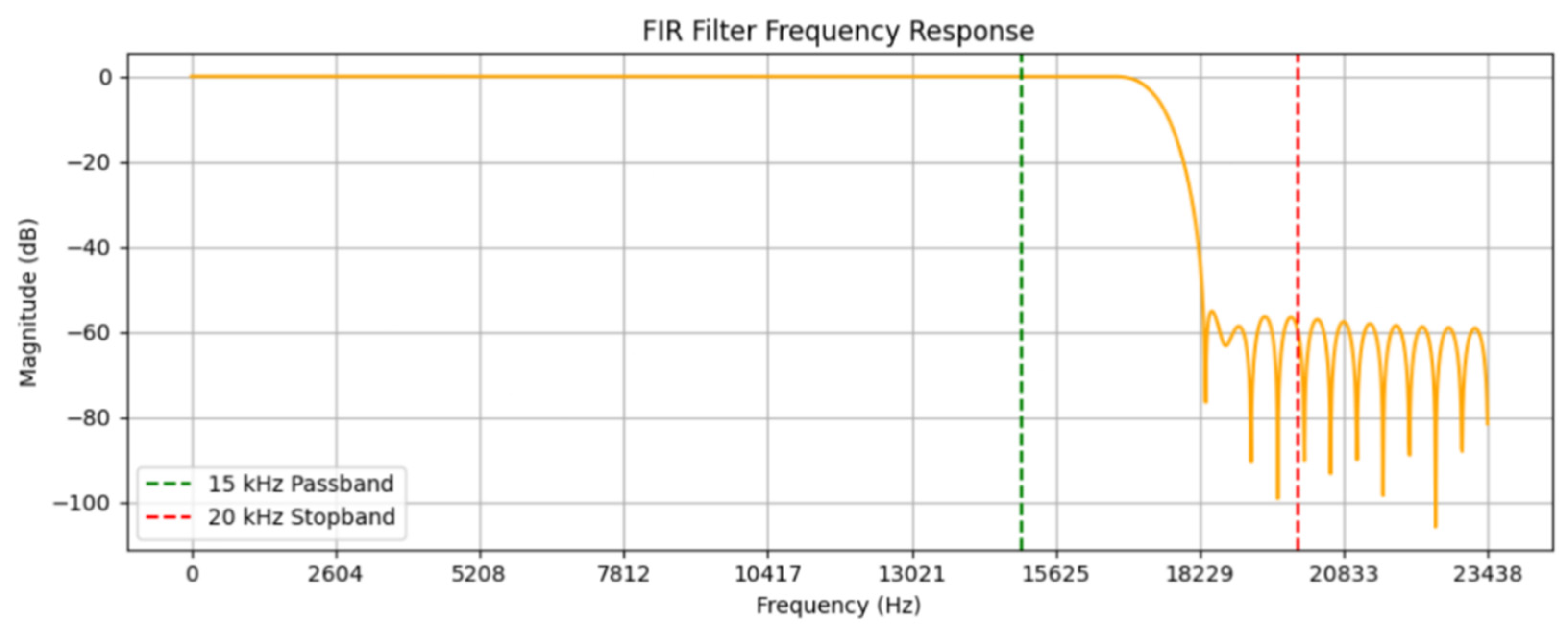

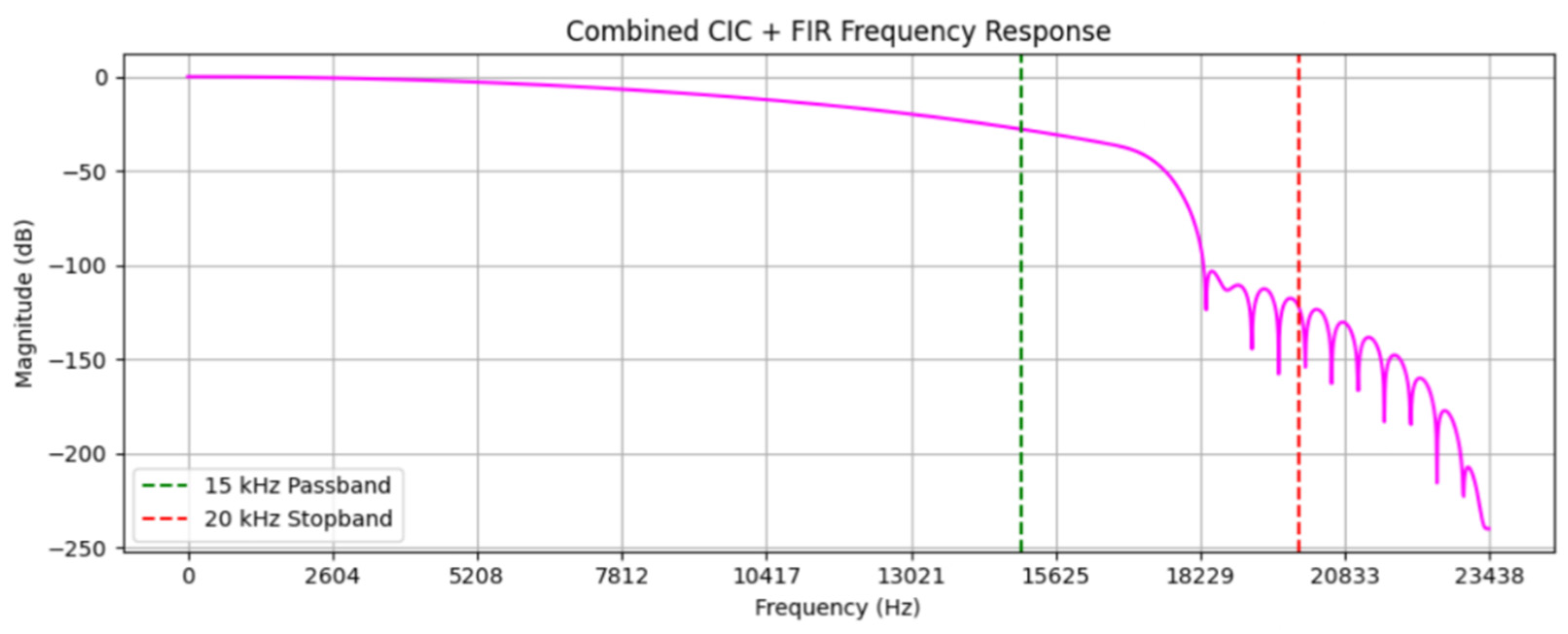

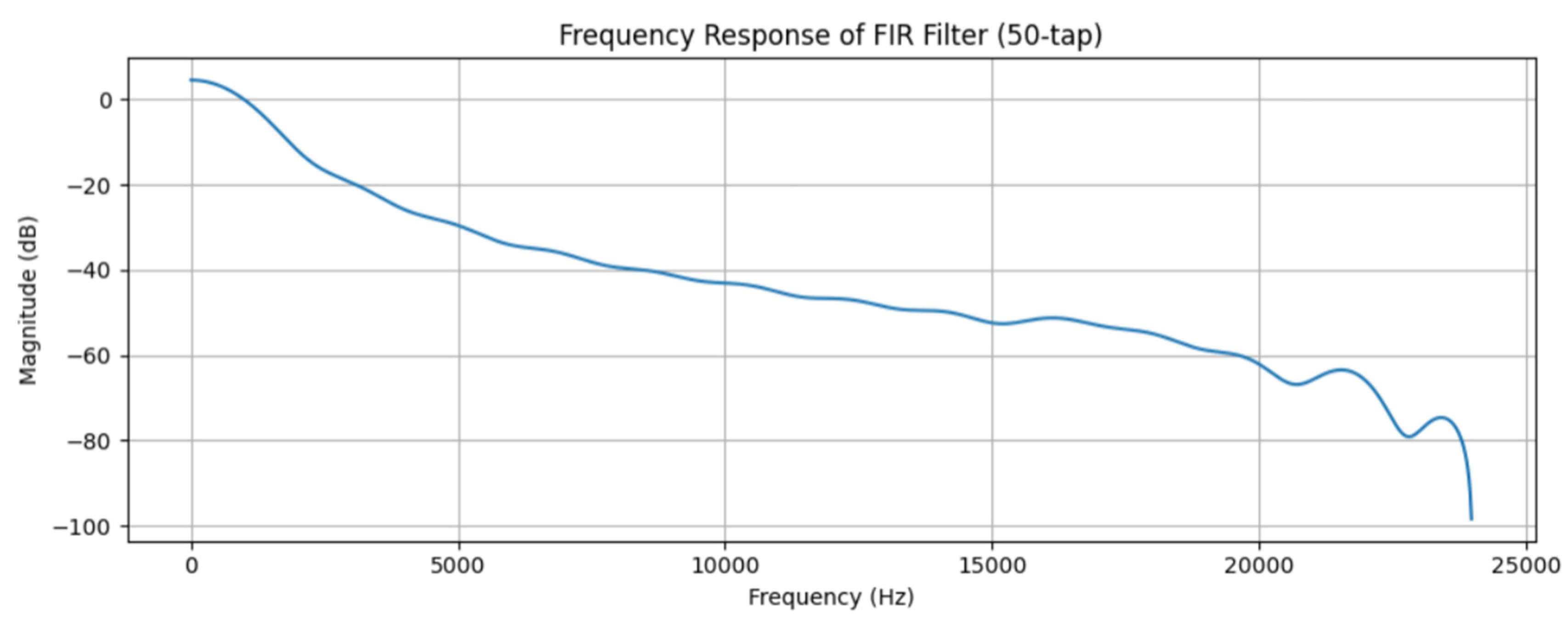

4.1. Preliminary Frequency Response Analysis

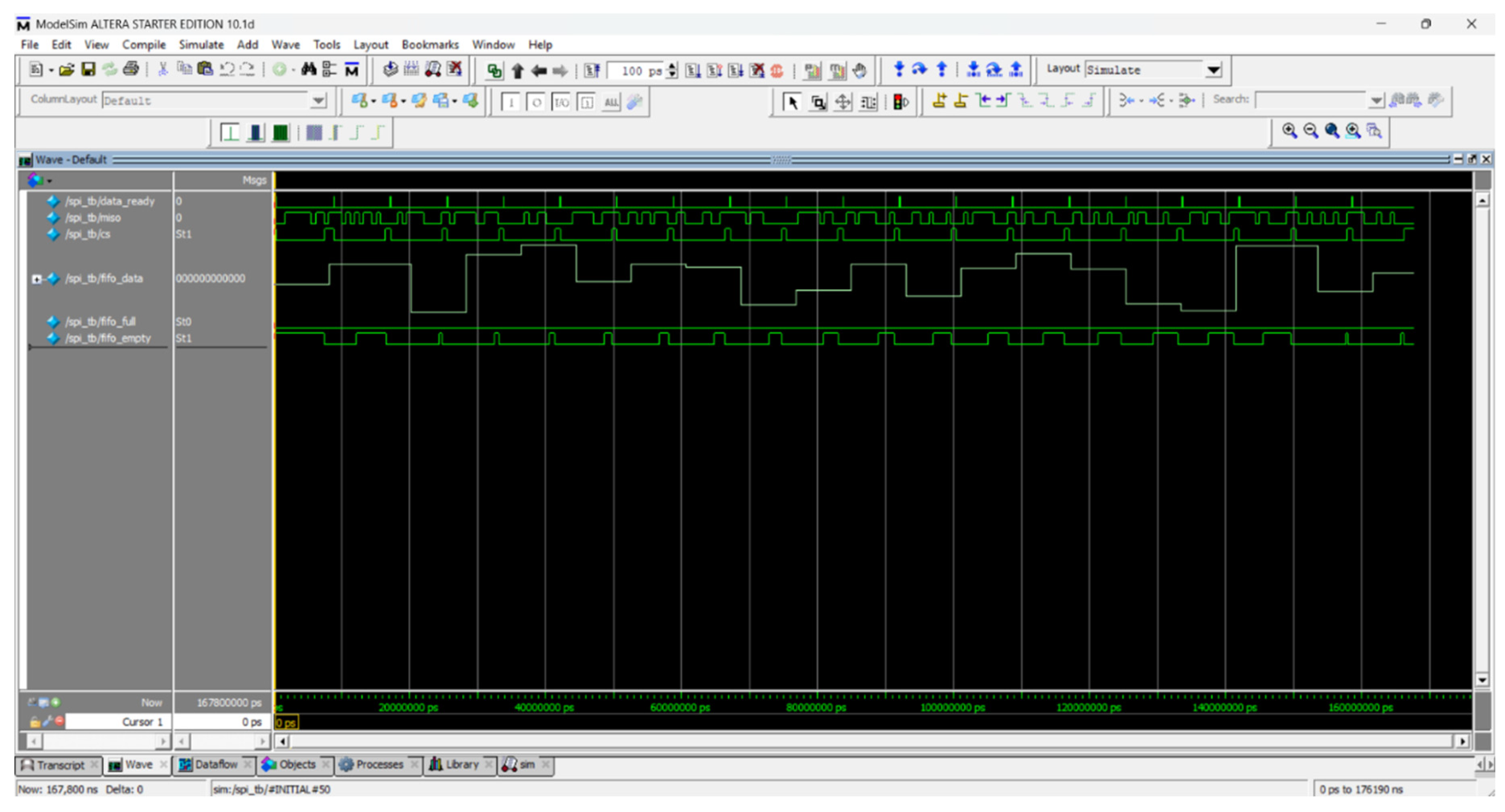

4.2. Individual Module Simulation Results

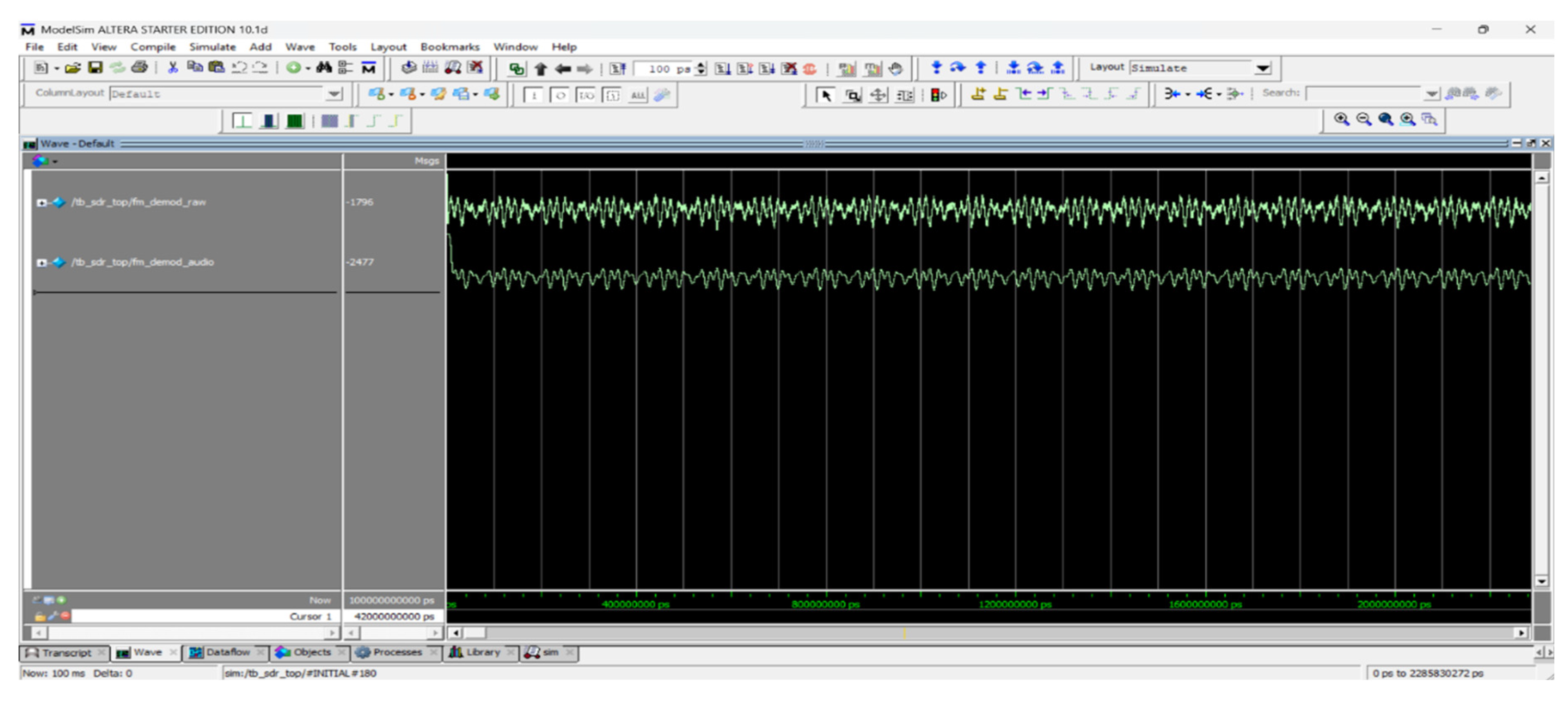

4.3. Integrated System Simulation Results

5. Conclusion

References

- Kaur, G., & Raj, V. (2008, July). Multirate digital signal processing for software defined radio (SDR) technology. In 2008 First International Conference on Emerging Trends in Engineering and Technology (pp. 110-115). IEEE.

- Mustafa, K. H. (2023). Design and implementation of SDR circuits using FPGA (Doctoral dissertation, FACULTY OF ENGINEERING Electronics Engineering and Electrical Communications Design and implementation of SDR circuits using FPGA A Thesis submitted in partial fulfillment of the requirements of the degree of Master of Science in Electrical Engineering (Electronics Engineering and Electrical Communications) by Kamal Hussein Mustafa Bachelor of Science in Electrical Engineering (Electronics Engineering and Electrical Communications) Faculty of Engineering, Alexandria University).

- S, Jahnavi & B, Pooja & FM, Santro & Vijayageetha, R. (2016). Implementation of Wide Band FM Receiver on RTL-SDR. International Journal of Engineering Research and. V5. [CrossRef]

- Liu, Ruiqiang,Ga, Fengmei. RF Transceiver Circuit FPGA Program Design and Development[J]. International Journal of Future Generation Communication and Networking,2016,9(12):395-404. [CrossRef]

- G. N. Chaubey, Digital Implementation of RF Digital Receiver on FPGA. Indian Institute of Technology, Roorkee, 2014.

- Bhakthavatchalu, R., Karthika, V. S., Ramesh, L., & Aamani, B. (2013, March). Design of optimized CIC decimator and interpolator in FPGA. In 2013 International Mutli-Conference on Automation, Computing, Communication, Control and Compressed Sensing (iMac4s) (pp. 812-817). IEEE.

- Kolawole, E. S., Ali, W. H., Cofie, P., Fuller, J., Tolliver, C., & Obiomon, P. (2015). Design and Implementation of low-pass, high-pass and band-pass finite impulse response (FIR) filters using FPGA. Circuits and Systems, 6(02), 30. [CrossRef]

- Kislal, A. O., Demiray, A., Ceylan, O., & Yagci, H. B. (2015, November). Implementation of a software defined FM mixed demodulator on FPGA. In 2015 23rd Telecommunications Forum Telfor (TELFOR) (pp. 333-336). IEEE.

- Qiang, J., Gu, Y., & Chen, G. (2020). FPGA Implementation of SPI bus communication based on state machine method. In Journal of Physics: Conference Series (Vol. 1449, No. 1, p. 012027). IOP Publishing.

- Sisterna, C., Segura, M., Guzzo, M., Ensinck, G., & Gil, C. (2011, April). FPGA implementation of an ultra-high speed ADC interface. In 2011 VII Southern Conference on Programmable Logic (SPL) (pp. 161-166). IEEE.

- Narendra N, DESIGN OF DIGITAL DOWN CONVERTER AND SIGNAL DETECTION TECHNIQUES FOR SOFTWARE DEFINED RADIO.

- Maruthi, G. B., Kumar, S. P., & Pratap, M. S. (2015). implementation of High performance DUC and DDC for Software Defined Radio Applications. International journal of computer applications, 110(6). [CrossRef]

- Jinding, G., Yubao, H., & Long, S. (2011, March). Design and FPGA implementation of linear FIR low-pass filter based on Kaiser window function. In 2011 Fourth international conference on intelligent computation technology and automation (Vol. 2, pp. 496-498). IEEE.

- N. Kumar, M. Rawat and K. Rawat, "Software-Defined Radio Transceiver Design Using FPGA-Based System-on-Chip Embedded Platform With Adaptive Digital Predistortion," in IEEE Access, vol. 8, pp. 214882-214893, 2020. [CrossRef]

- Yu, F. (2004, September). FPGA implementation of a fully digital FM demodulator. In The Ninth International Conference onCommunications Systems, 2004. ICCS 2004. (pp. 446-450). IEEE.

- Ramamurthi, B., Giridhar, K., & Srinivas, M. A. (1996). DSP-based digital FM demodulation for GMSK signals. Sadhana, 21, 101-112. [CrossRef]

- Al Bustam, H., & Shahzamal, M. A VHDL Based DAC Implementation on FPGA.

- Adiono, T., Ahmadi, N., Renardy, A. P., Fadila, A. A., & Shidqi, N. (2015, August). A pipelined CORDIC architecture and its implementation in all-digital FM modulator-demodulator. In 2015 6th Asia symposium on quality electronic design (ASQED) (pp. 37-42). IEEE.

- SUNNY, S., JOHN, J. V., & TJ, D. A. CORDIC Based FM Demodulator for Digital Telecommand Receiver.

- Liu, R., & Ga, F. (2016). RF Transceiver Circuit FPGA Program Design and Development.

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).