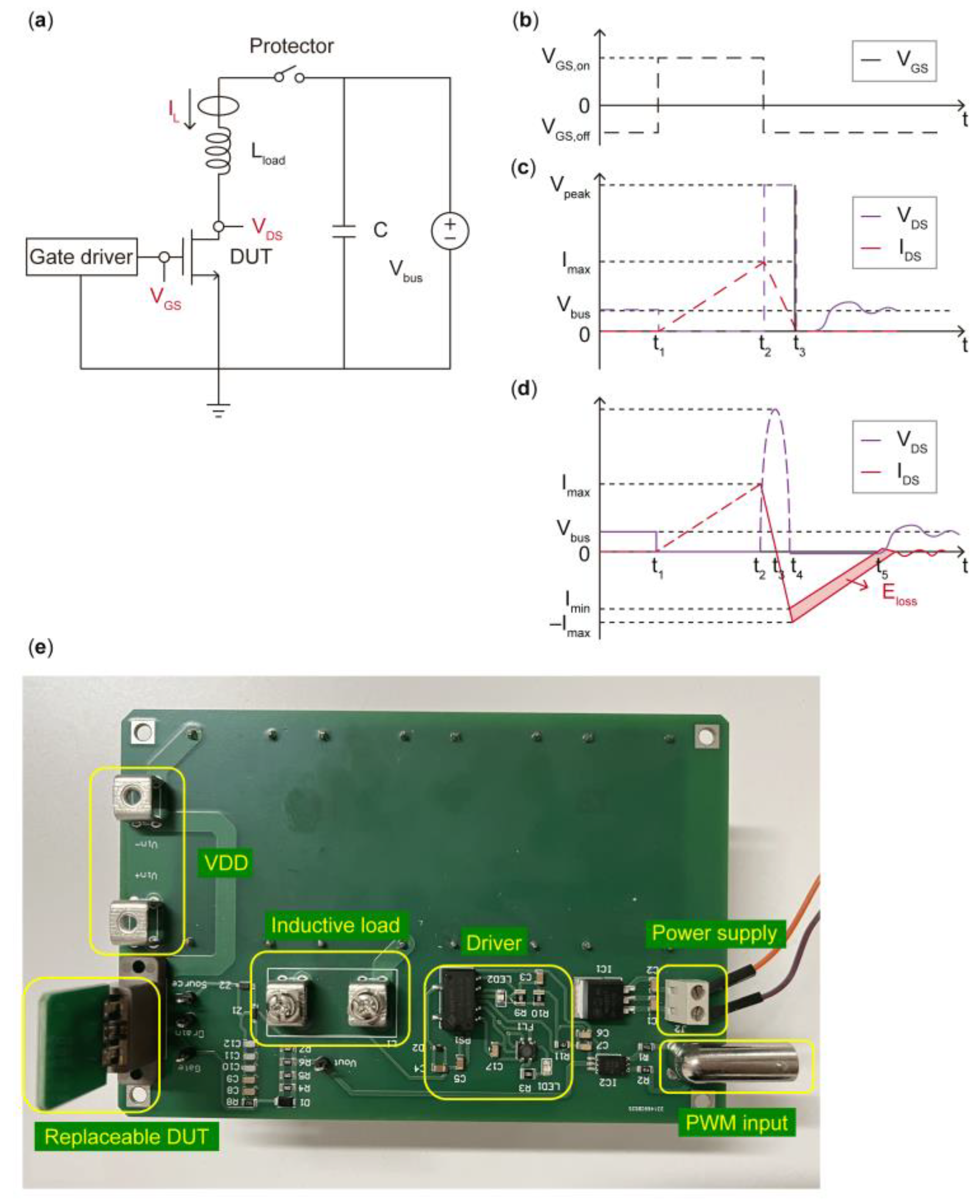

3.1. Single UIS Test

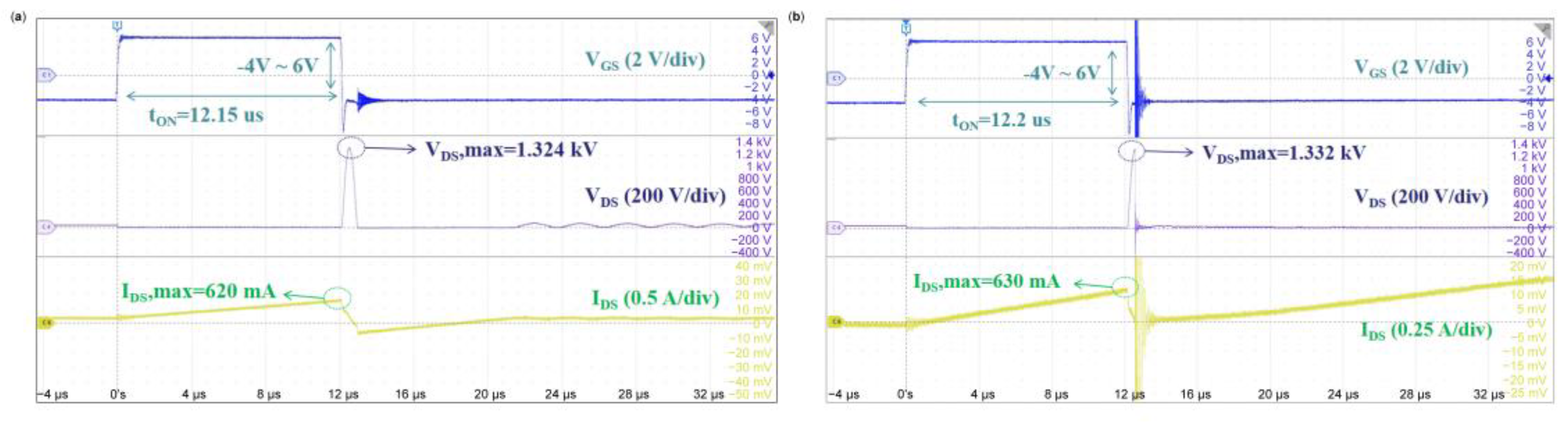

Figure 3 shows the typical room temperature single UIS waveforms of p-gate GaN Hemt during the last test before failure (

Figure 3a) and at failure (

Figure 3b) under 0.3 mH of inductive load conditions, respectively. Test conditions is as: power supply is 30V and gate driver voltage is switched from -4V to 6V. From

Figure 3a, when gate pulse width of 12.15μs is applied on gate-source of DUT, the peak current value of drain-source is 620mA, while the V

GS switches from 6V to -4V, the induced voltage is applied between drain and source with peak value about 1.324kV at this moment the current equals to zero. During the entire UIS process, V

DS rises from 0 to V

DS,max and then drops to 0, I

DS linearly decrease to a negative value and then increase to 0. The entire process lasts about 0.85μs and is similar to LC resonant [

17]. During the reverse of I

DS period, after a duration of reverse conduction, V

DS starts to oscillate and then damps to 30V. In

Figure 3b, when gate pulse width increases to 12.20μs, the charging period of inductor increases either and the peak value of I

DS will achieve to 630mA. Then after the DUT is switched off, V

DS increases rapidly to the highest point of voltage of 1.332kV at which DUT failed. After DUT failed, V

GS keeps constant at -4V and V

DS approaches to zero [

18]. After then, the current rapidly increases, which shows that the short circuit of source and drain happens after DUT failed. At this moment, DUT behaves like a passive low impendence.

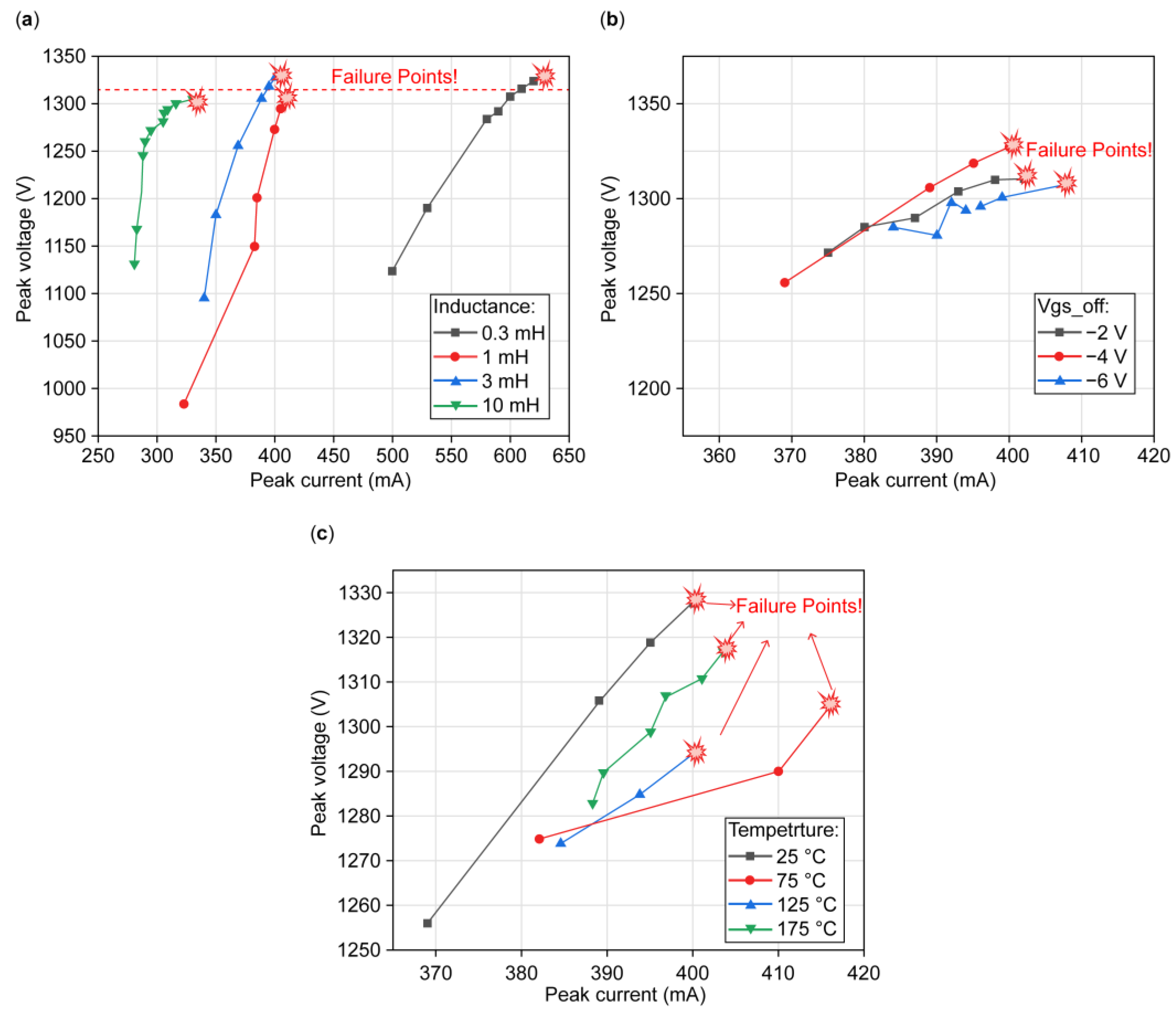

By varying different test conditions such as load inductance, Vgs_off and temperature, a series of single pulse UIS tests are conducted by gradually increasing the gate pulse to obtain failure point, and then, peak currents and peak voltages under different working conditions before device failure are extracted and concluded in

Figure 4. Datas in

Figure 4a are obtained under different inductance, (b) at different Vgs_off;(c) at different temperature.

It can be found that in

Figure 4a, with inductance increasing the peak current will obviously decreases because of increasement of charging and discharging period of load inductance , and the UIS process period will also increase. Meanwhile, critical V

DS shows little floating before device failed and less significant relationship with load inductance [

19]. In

Figure 4b, we can see that both peak current and critical peak voltage between drain and source show a little floating which maybe caused by devices differences, and have no obvious changes with variation of Vgs_off.

Figure 4c presents critical voltage versus peak current before failure under different ambient temperature, and shows no obvious relationship with temperature and likely some fluctuations.

In order to verify the failure mode under single UIS test. The failed sample with different failure mode is decaped and delayer, after local corrosion treatment without damage, optical microscope(OM) is used to observe and validate the failure point by adjusting magnification [

20].

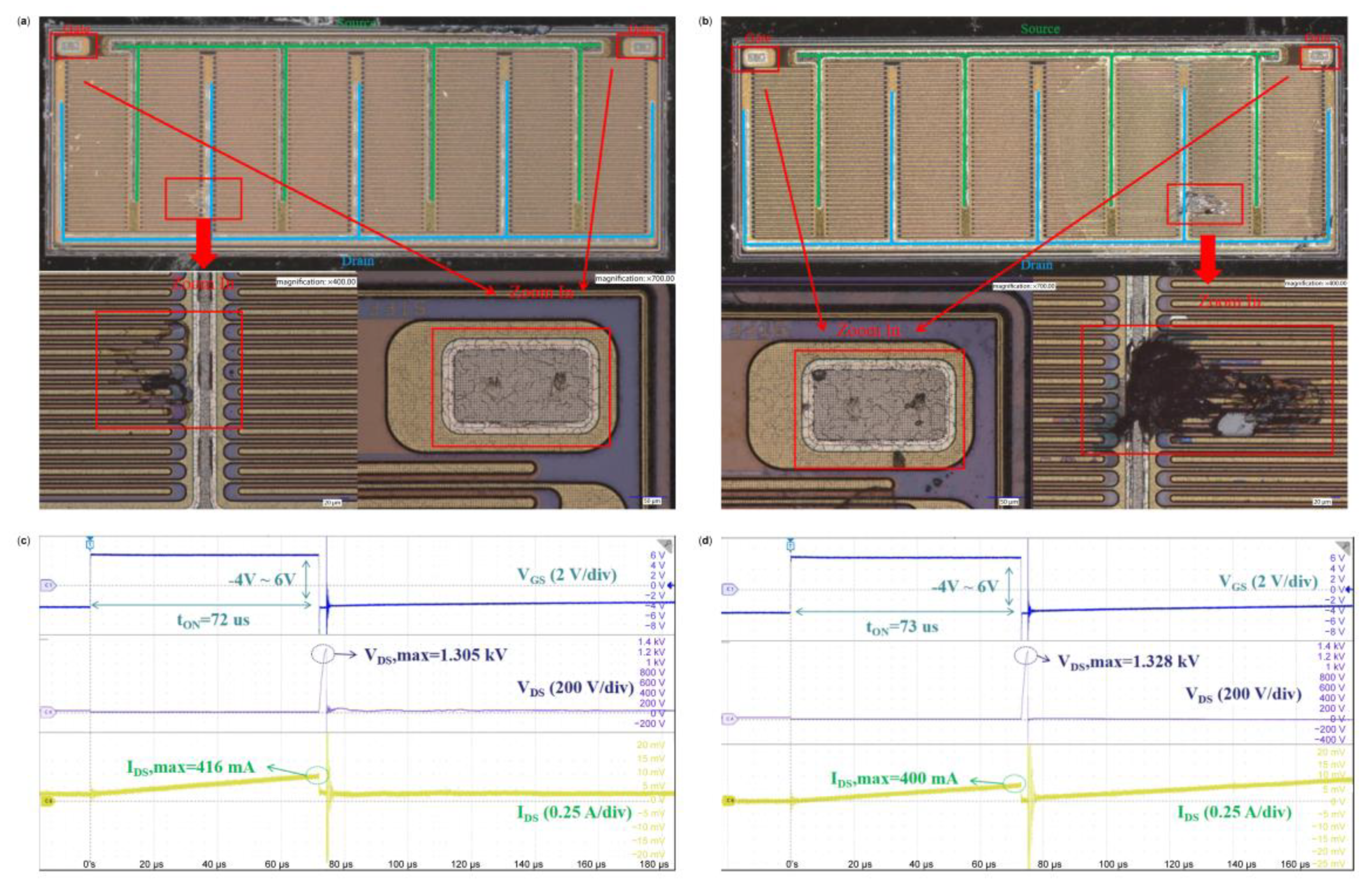

Figure 5 shows the OM imagines of decapped failure samples and waveforms at failure.

Figure 5a and 5c show the decap results of the failed devices.

Figure 5b,d are measured UIS waveforms when (a) and (b) failure occurs respectively. The failure test conditions is under 75°C with V

GS switches from -4V to 6V, load inductance L equals to 3mH in

Figure 5a,b, VDD is 30V and 25°C, -4V~6V, 3mH and 30V in

Figure 5c,d, respectively. we can see from

Figure 5a that slightly burnout compared with

Figure 5b happens in the drain metal strips region and gate region, we can confirm that the failure is caused by breakdown of drain and gate damage. Since burnout area is very small and no sharply increasement of I

DS occurs in captured curves in

Figure 5b so that we can confirm that no short circuit occur between drain and source [

21]. Comparatively, as presented in

Figure 5c that large burnout arear is found near the drain and obviously damaged arear in the surface and around gate region. So, the main failure reason of chip is related to short circuit of drain and source caused by drain failure and finally burnout with I

DS increasing sharply as shown in

Figure 5d. Meanwhile, gate electrode is also subjected to great UIS stress and leading to damage which is consistent with the captured waveform in

Figure 5d.

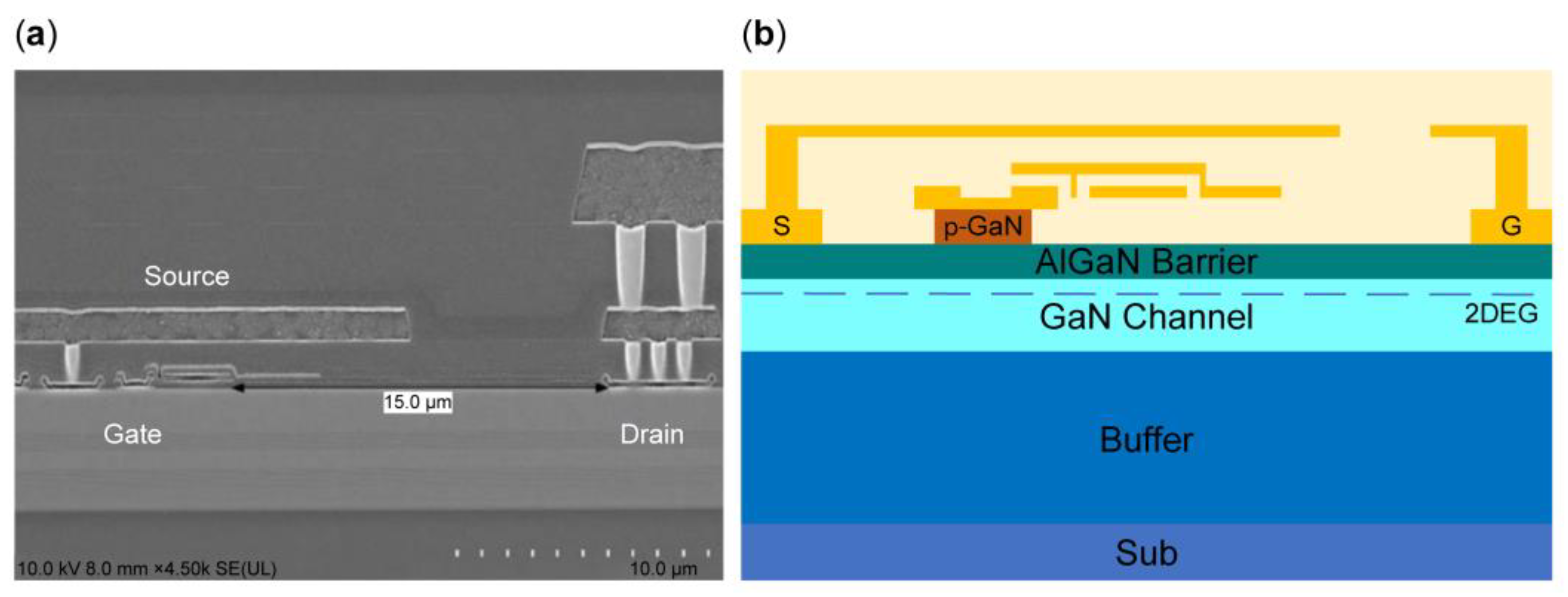

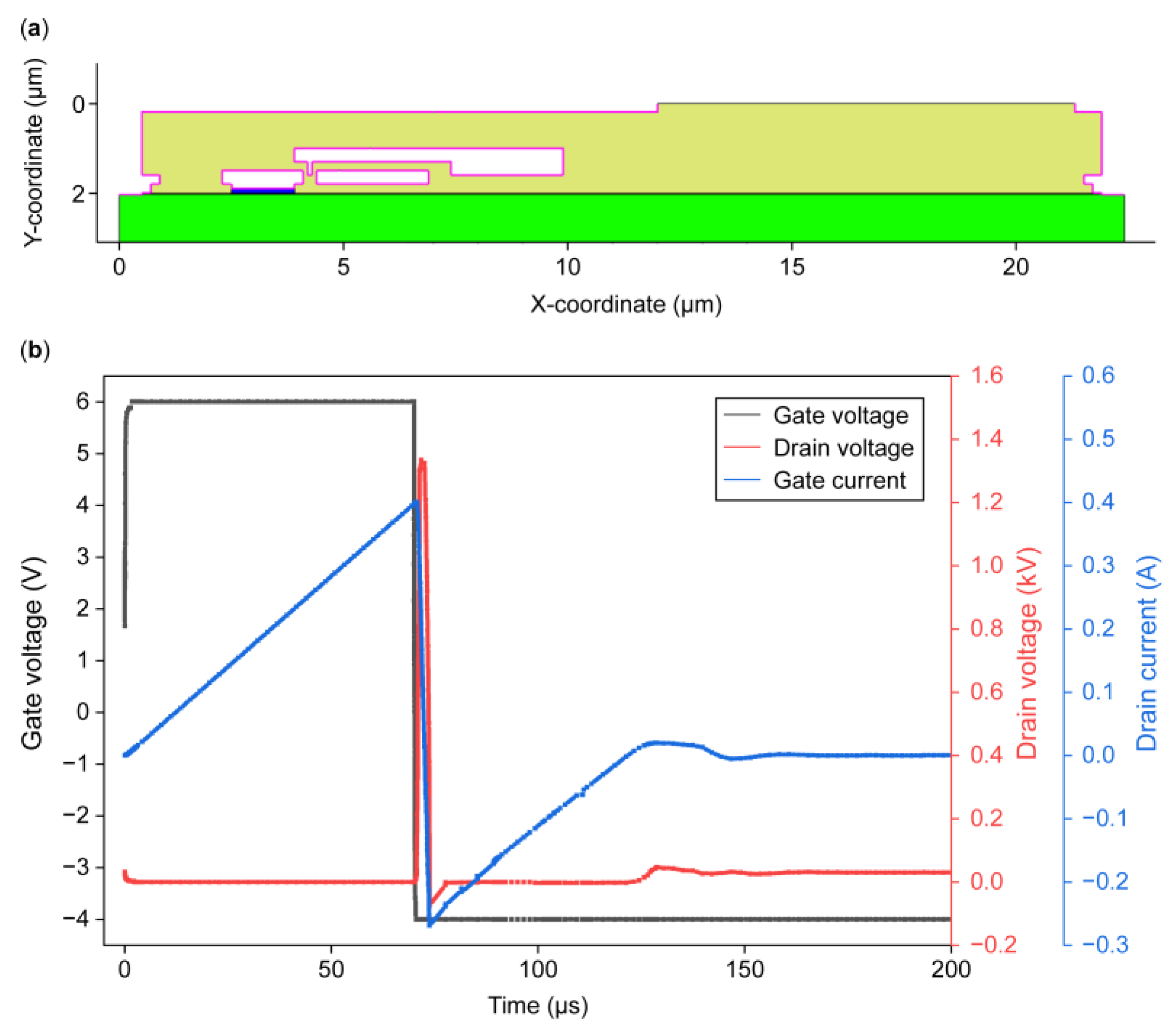

3.2. TCAD Simulation Under Single UIS Stress

To further explore the UIS failure mechanisms, TCAD simulation is synchronously used to explain the failure behave. In the simulation, the structure of the p-GaN gate HEMT comprised a 2.0 μm-thick GaN layer, a 15 nm AlGaN barrier. layer with 23% Al, and a 100 nm p-GaN layer. The gate length was 1.5 μm, the source-gate distance was 1 μm, and the gate-drain spacing was 17 μm. The doping concentration of the p-GaN layer was 3 × 10−17 cm−3. Besides above, to coincide well with the experimental datas, some corrections should be done in the key structure region. Firstly, interface states are intentionally added to AlGaN/GaN interface to explain the net polarized charges due to the piezoelectric polarization effect generated in AlGaN/GaN structure. Besides, since body traps play an important role during the UIS processing, acceptor traps in the GaN channel should be introduced with concentration of

and energy level higher above valence band about 0.9eV. Trap concentration in buffer should be higher much than the ones in channel region and the concentration is calibrated as

with energy level as same as the one in channel traps. Besides above deep-level traps, owing to the existence of heterojunction interface and processing treatment, various traps could be introduced. Shallow level traps in the interface should be taken into consideration either. In our simulation, the interface states concentration is set as within the range of

and energy level is 0.05~0.8 eV above valence band. After the well calibration of device structure, UIS processing is performed by the method of Mixed-Mode. The circuit parameters are set as follows: the load inductor L is set as 3mH, driving voltage V

GS is about -4~6V, supplied bus voltage VDD is set as 30V,conduction duration ton is set as 70μs, simulated waveforms is shown in

Figure 6b, the peak voltage and peak current is respectively almost 1.3 kV and 400mA which are close to experimental dates.

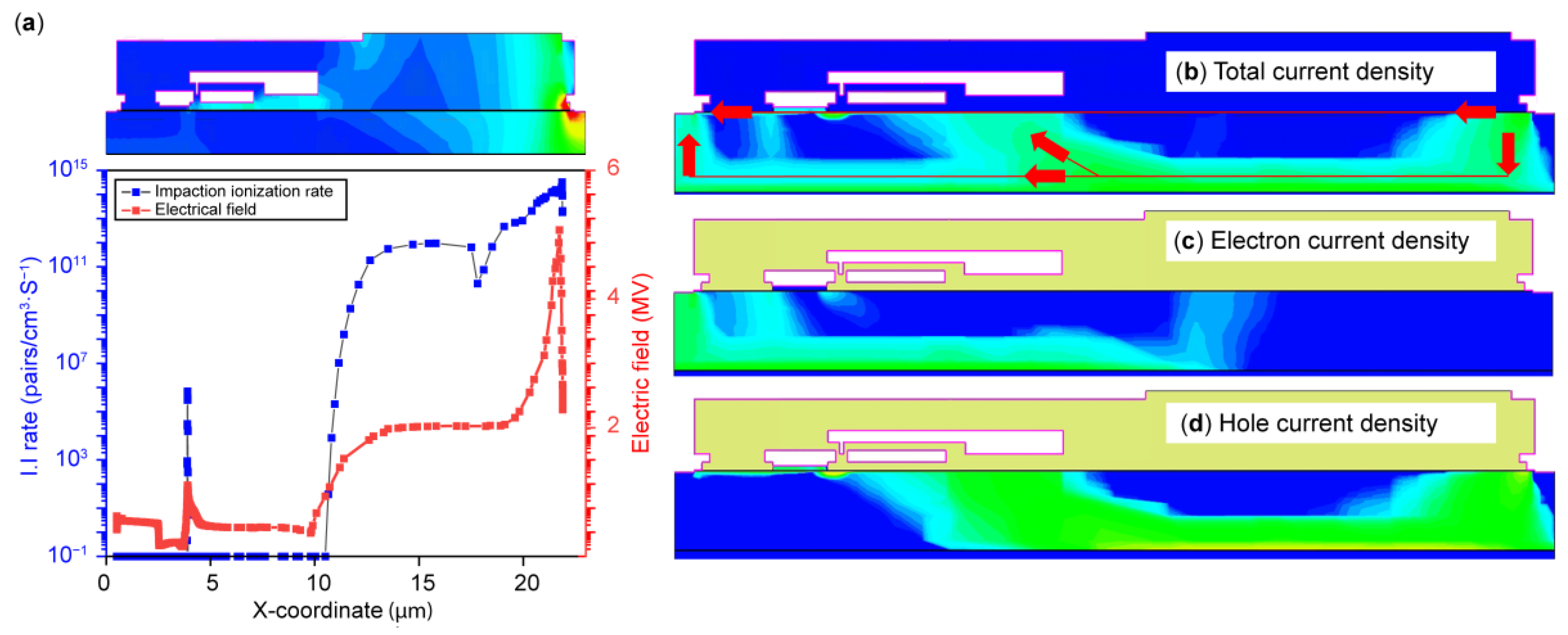

Electrical field and impact ionization versus X-coordinate are extracted at Vpeak point and plotted in

Figure 7a. Total current density, electron density and hole density profile are extracted and plotted in

Figure 7b–d. Seeing from

Figure 7a that when DUT suffered from UIS stresses, a huge voltage is dropped between source and drain, meanwhile, a large electrical field and strong impact ionization focused around drain region and then at the edge of gate field plate and source field plate. we can see from

Figure 7b that there exist three current conduction paths: current from drain flows through channel and arrive to source, the other one is current from drain passes through buffer and reach to source, the third one is current passes through buffer and flow to gate [

22]. Combination of

Figure 7a,b, it can be concluded that when the DUT suffered UIS stress striks, a large voltage is generated between drain and source and impact ionization will occur under drain electrode and thereby massive electron-hole pairs could be generated. Electrons generated would be trapped by buffer while one part of holes generated would move along channel and pass through buffer and then move to substrate, another part of holes would move to gate due to the electrical field of drain to source and then one part flow into P-GaN layer and the other part accumulated benethe the gate and finally resulting in three current conduction paths. Concluded from these four figures that DUT failure is mainly caused by huge electrical field dropped on drain which exceeds the dielectric limitation and thus leading to dielectric breakdown and DUT has been damaged. Which is different from SiC power MOSFET [

23,

24].

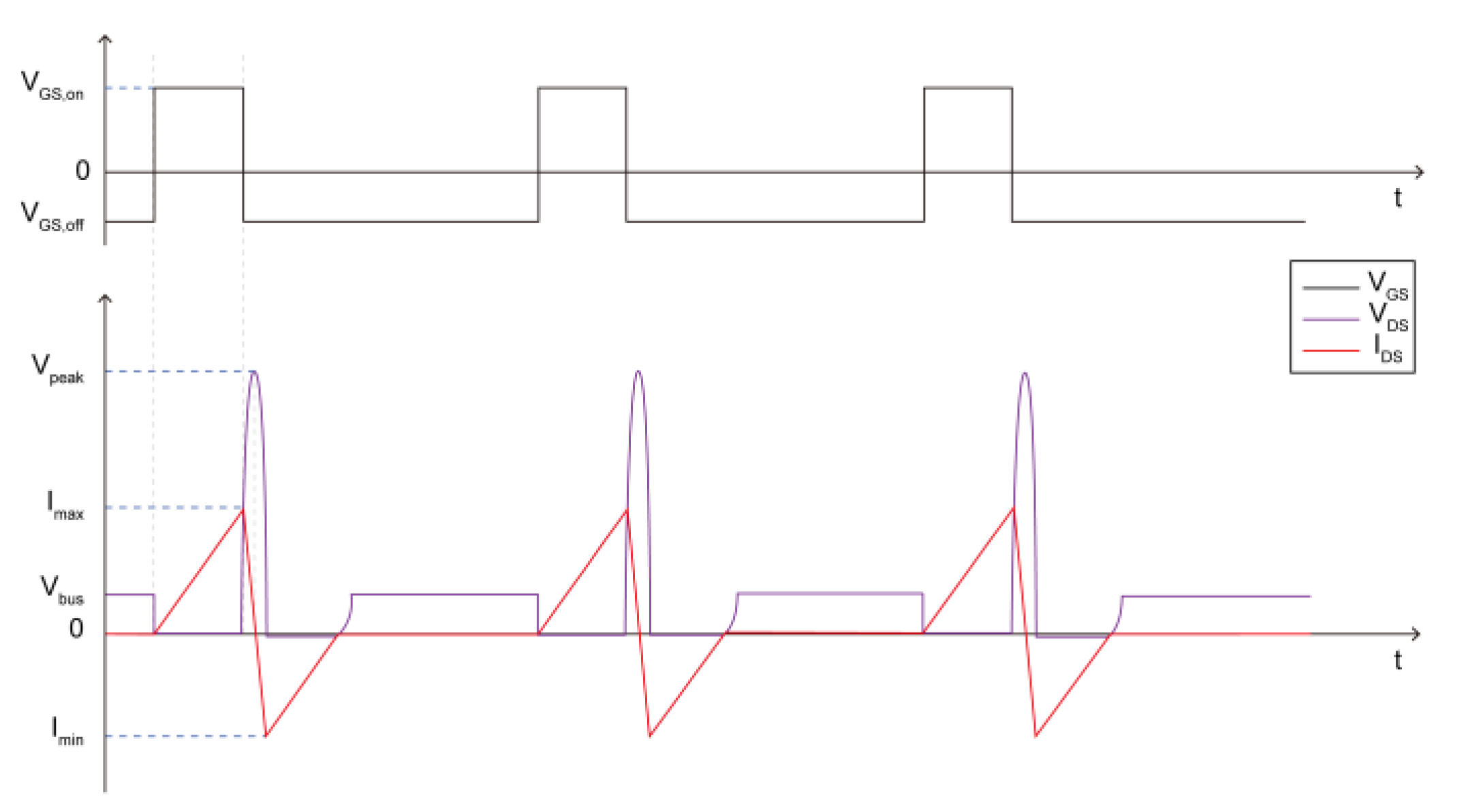

3.4. Degradation Mechanisms Under Repetitively UIS Stresses

Figure 13 gives the equivalent circuit model of gate region in P-GaN HEMT. Gate region is formed by combination of back to back Schottky diode and p-i-n diode, Schottky diode is formed by gate to metal and p-i-n diode is formed by P-GaN/i-AlGaN/N-GaN. Due to the band gap discontinuity in the interface and defects induced by processing, traps can not be ignored [

25,

26,

27].

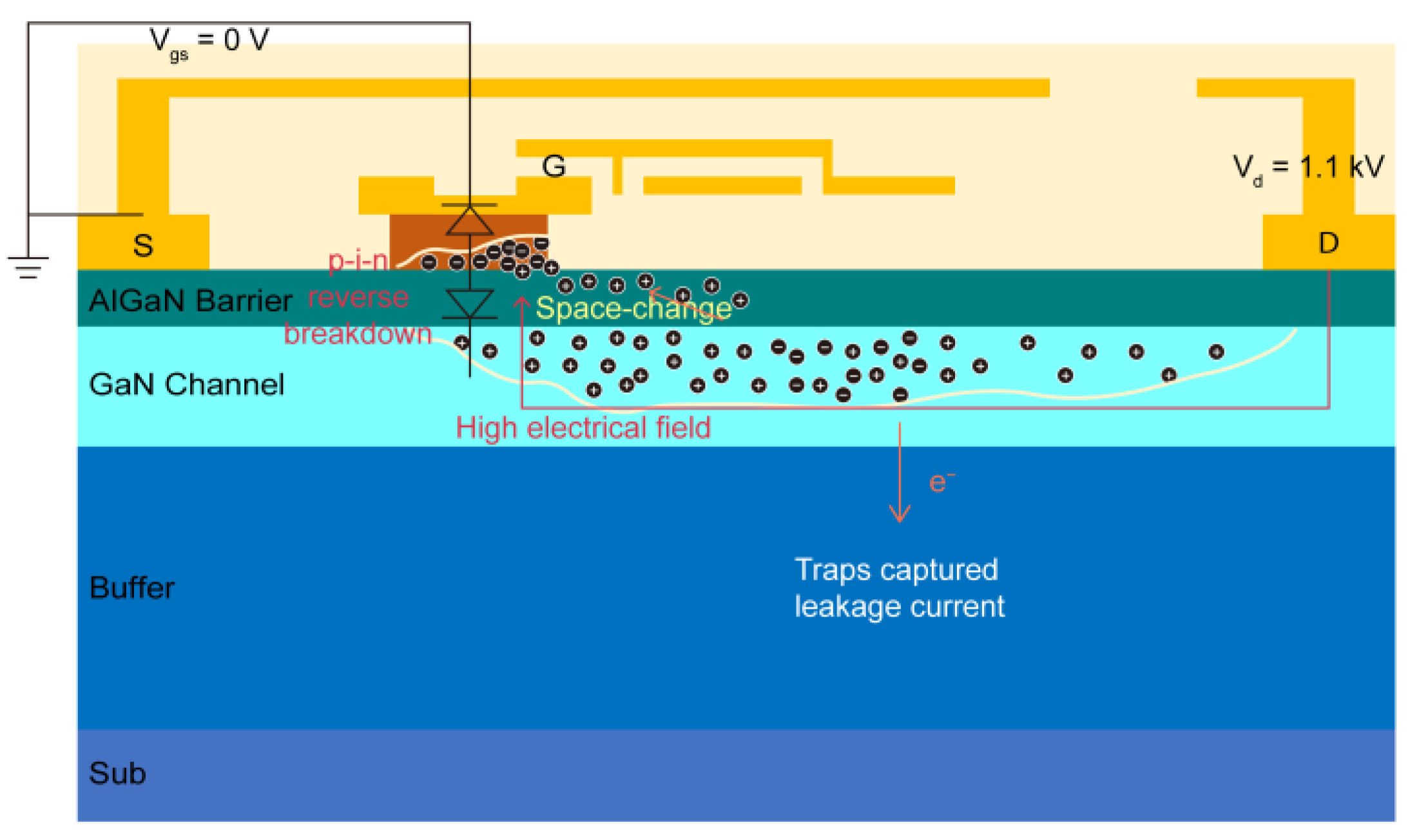

Figure 14 illustrate the impact ionization process and electrical field profile when UIS stress is applied to the DUT. Because UIS often occurs at the moment of Vgs switches from Vgs_on to zero, thus, VDD is set as 1.1kV, and gate is shorted to source as shown in

Figure 14.When DUT is striked by UIS stress, a large induced voltage is applied between drain and source. Strong impact ionization will occur in the body leading to a huge amount of electron-hole pairs generated. A high electrical field will be induced between drain and gate marked with red line , meanwhile, a vertical electrical field directing from N-GaN to P-Gan is generated near gate electrode, and then drives p-i-n diode entering into reverse blocking state. P-GaN acts as negative charge center of space-charge region, N-GaN acts as positive charge center of space-charge region. Holes generated by impact ionization were injected into gate and barrier, then captured by trap nearby, while the electrons were captured by traps in buffer.

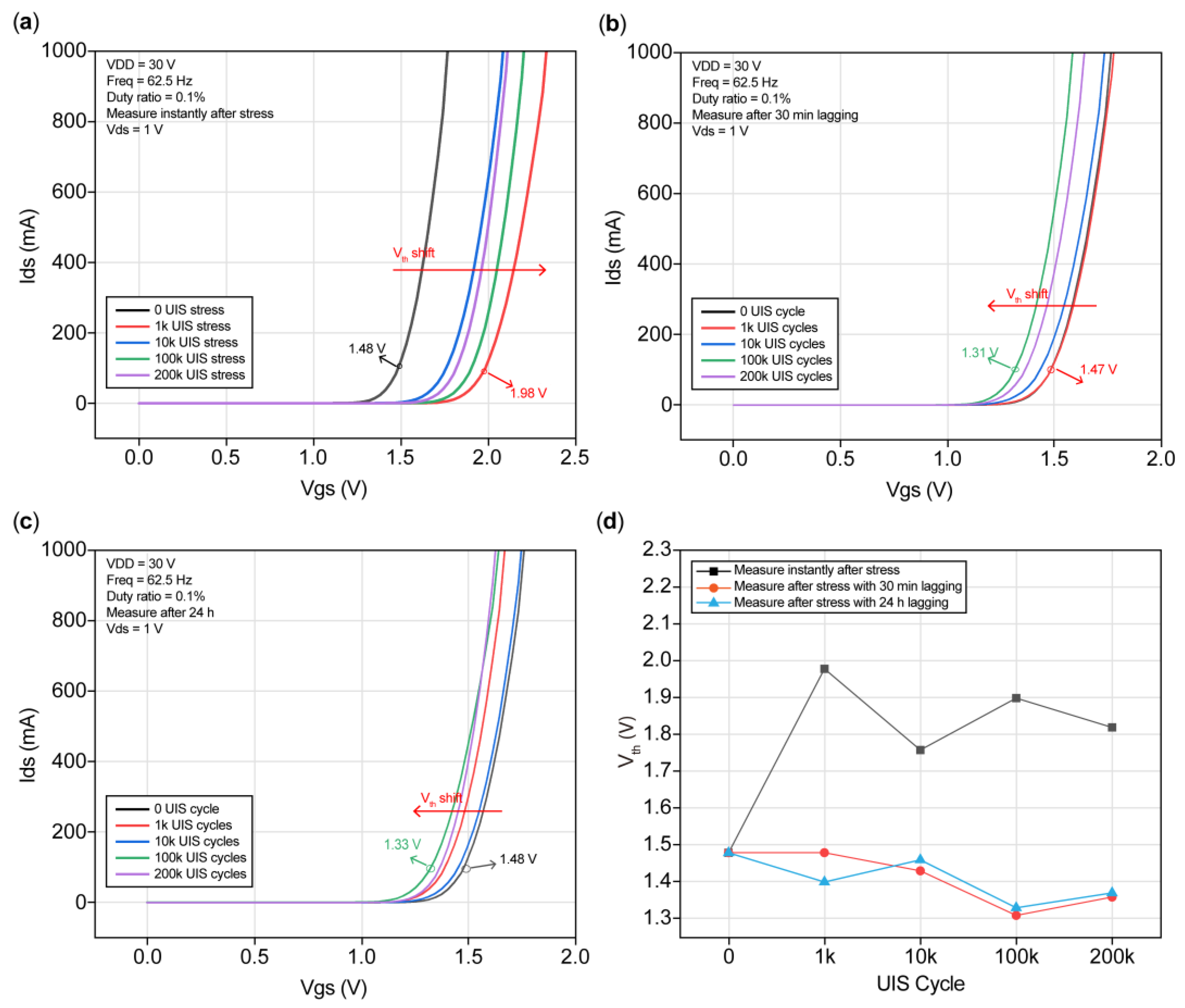

When single UIS is performed as known as before, duration of stress only lasts for several micro-seconds and since electron mobility is much larger than hole mobility, Besides, in range of a short time after the UIS stress is removed, channel electrons were trapped into electron traps in GaN buffer, amount of holes accumulated beneath gate. Besides, when UIS stress is removed, both of Schottky diode and p-i-n diode is in off state, there is no extra holes entering into P-GaN region and recombination with negatively space charge, and a negative charge center is left instead. At this moment, to turn on the DUT a pre-positive voltage should be necessary and applied to gate electrode to offset the electrical field brought by negative space-charge. Thus, threshold voltage consists two parts: one is the pre-positive gate voltage(△V) and the other is the gate voltage required to channel forming(Vth0), that is, Vth0+△V reflected in

Figure 9a that Vth slightly increased when measured instantly after UIS stressing.

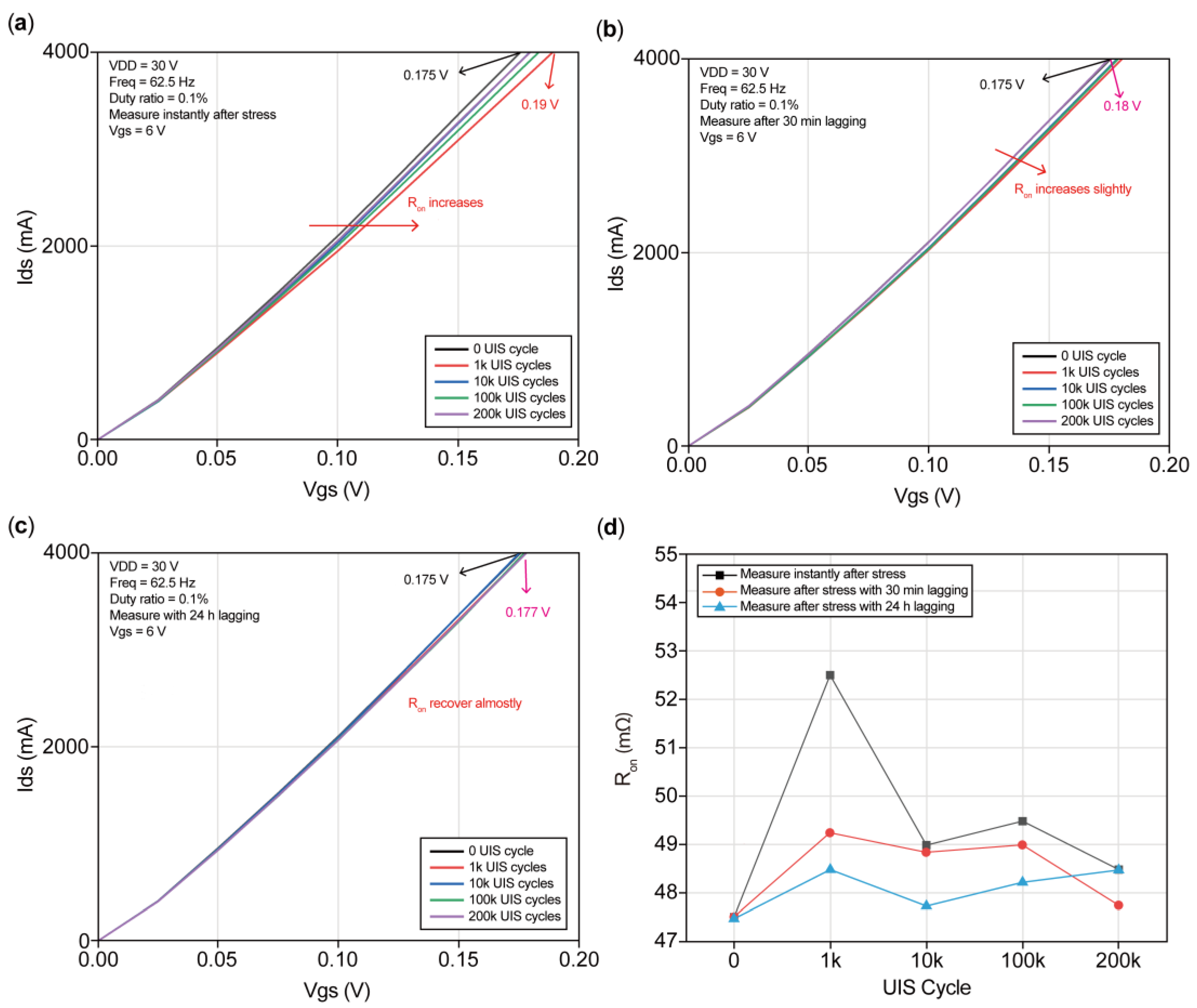

Under the condition of high-voltage bias appeared between gate and drain during UIS stresses, electrons get trapped at interface between gate and drain which performs as “virtual gate” and “virtual gate” will extend the depletion region beneath the gate to the source and drain, and additionally exhaust the channel electrons, leading to increasing of Ron. Since the virtual gate can not restored rapidly to its initial state after UIS stresses are removed, Ron when measured instantly after UIS stresses will show increasing tendency. This phenomena is consistent with those presented in

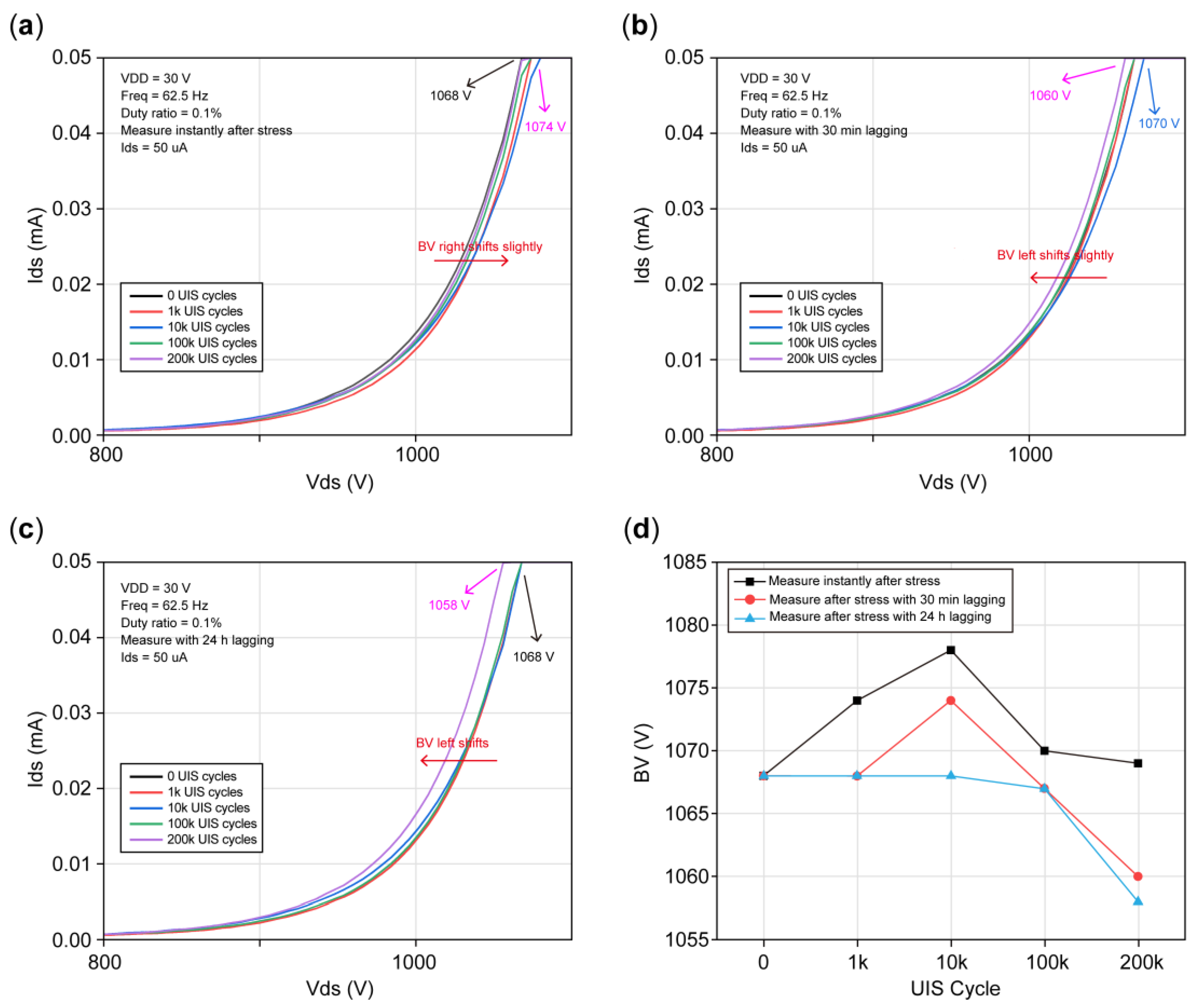

Figure 10a. Besides the effects of virtual gate, electron-trap in N-GaN buffer also play the role that Ids will decrease either which is reflected in

Figure 11a that BV presents a increasing tendency.

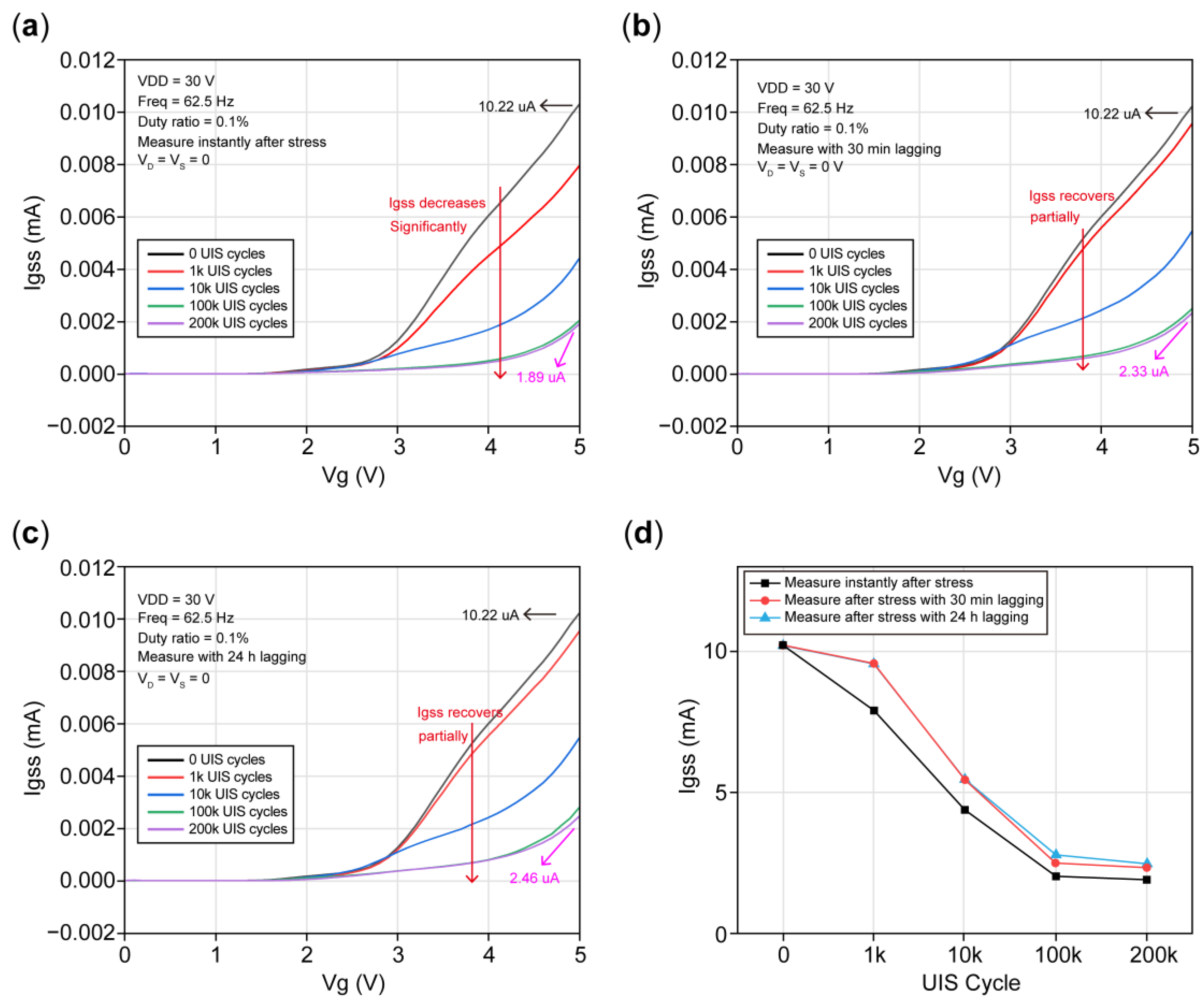

As previously described, under the conditions of high gate bias voltage, for p-i-n diode, a negative charge space is formed in P-GaN region, and a positive charge space is formed in N-GaN region. In a short time after UIS stresses is removed, due to both diodes are in off-state, there are no extra holes provided to recombine with negative space charge and electron traps in the buffer region can not also immediately release all the trapped electrons to recombine with positive space charge in N-GaN region. Thus, existence of space charge will greatly reduce Igss which phenomena also consistent with

Figure 12a.

After a period of UIS stresses removed, holes underneath the gate electrode will recombine with the negative space charges in P-GaN region, thereby, holes will accumulate in P-GaN region and Vth will decrease and shows negatively shifts. Meanwhile, electron traps in barrier and passivation layer will release the trapped electrons, virtual gate vanishes, on-state resistant gradually restores to its initial value. Electrons released by trapps in buffer will flow into channel which results in the amounts of electron is larger than that of holes and Ids will increase presented as BV left shifts. Because the space charge width resolved itself to some extent, gate leakage has a certain restored also. Above analysis is consistent with the curves with 30min lagging in

Figure 9b, 10b 11b and 12b. That is, Vth shows negatively shifting, Ron returns nearly to its initial value, while BV little decreases and gate leakage with drain short to source restores a certain extent.

Under repeated UIS stresses, inside the DUT, continuous impact ionization produce electron-hole pairs, electrons trapped and detrapped, recombination of electron-holes, space charge region widen and recovered. During these processes, due to hole mobility is much less than that of electrons and there are barriers above and below P-GaN layer, it is hard for holes injected into P-GaN to return to its initial position, accumulated holes in P-GaN region in last stress hasn’t been consumed not yet, the next stress strikes again. Thus, after repeated UIS stresses, gate will be damaged permanently and it is hard for threshold voltage and gate leakage current to return to its initial level. However, formation and disappearance of virtual gate, channel current is dominated by electron-traps, after a long time of lagging, channel resistant and blocking characteristics can almost return to their initial level. While for DUT undergoing much more repeated UIS stresses such as 200k striks, the buffer layer suffered much more and the blocking characteristics has irreversible degradation.