Submitted:

25 March 2025

Posted:

25 March 2025

You are already at the latest version

Abstract

Keywords:

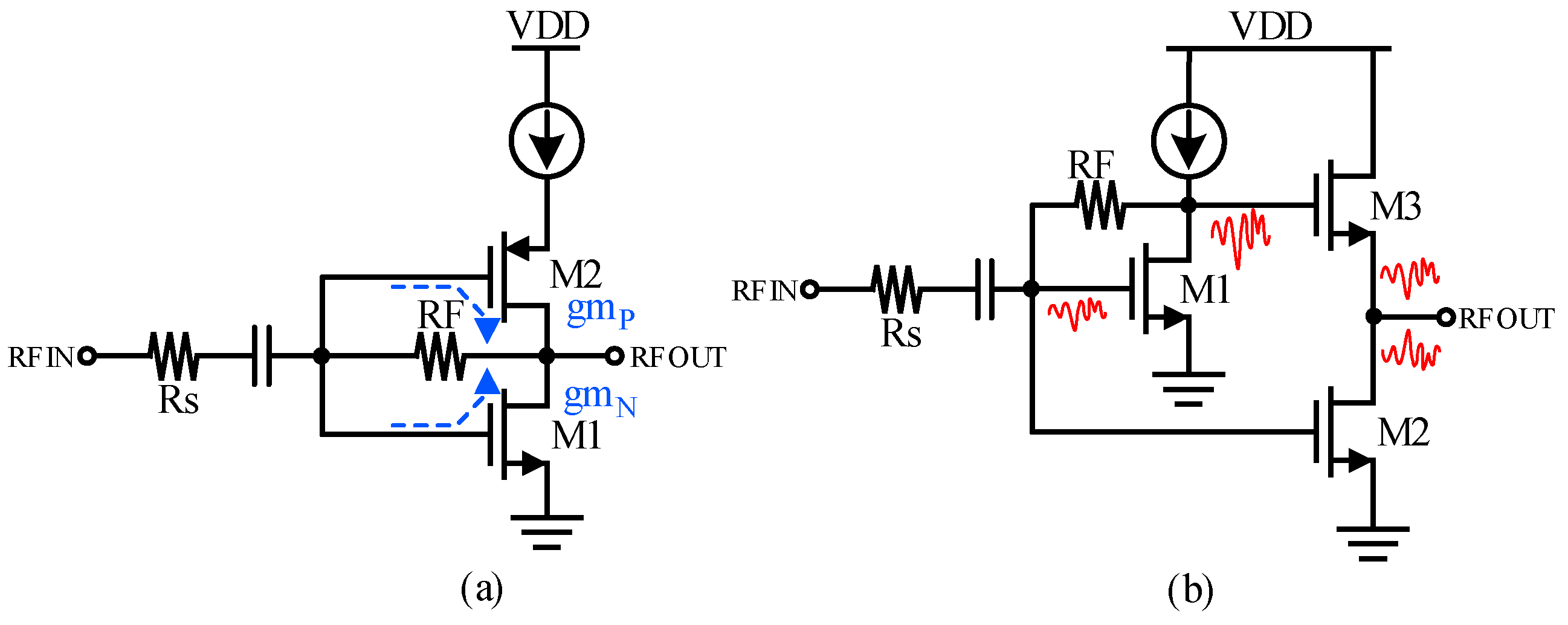

1. Introduction

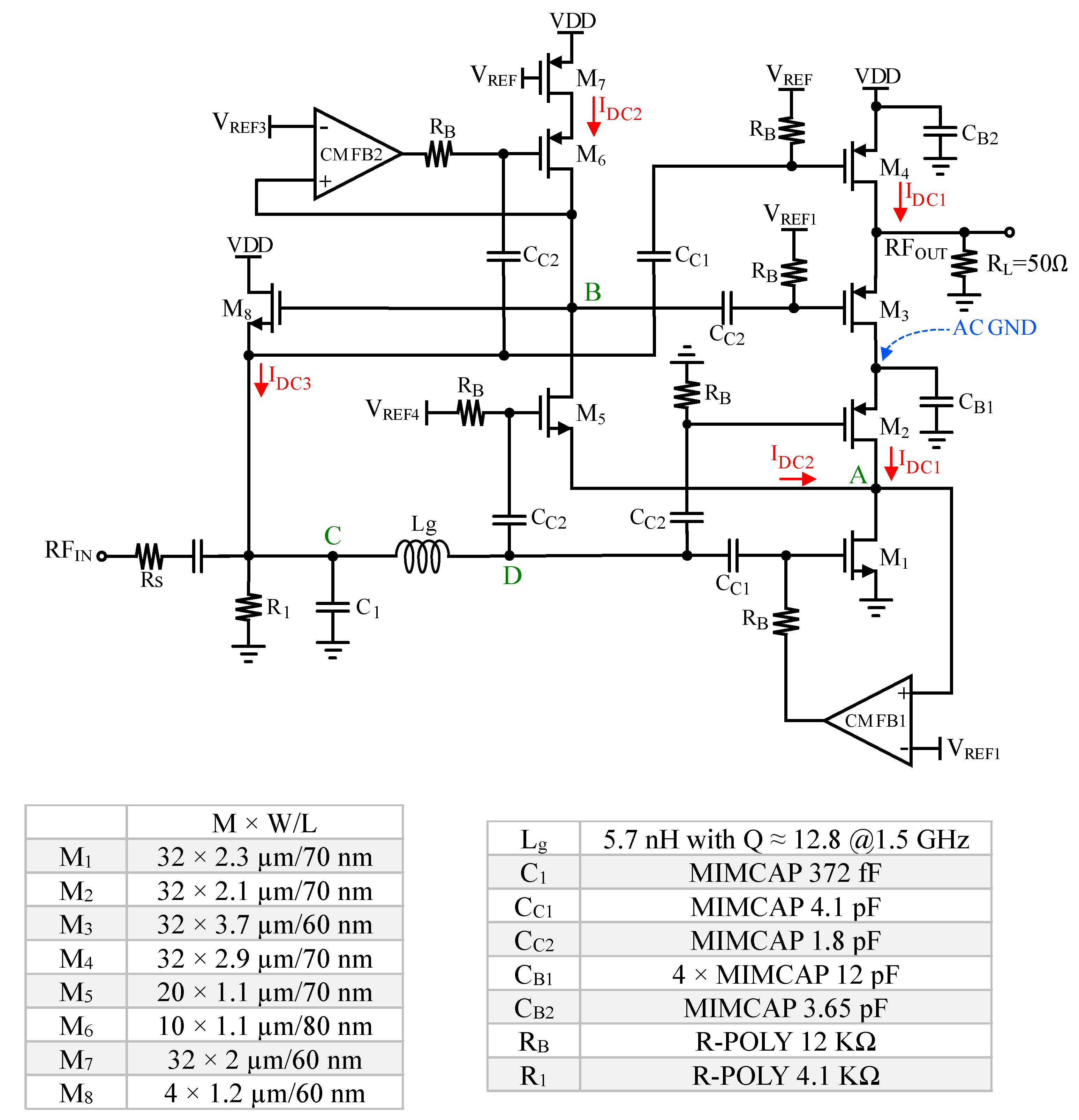

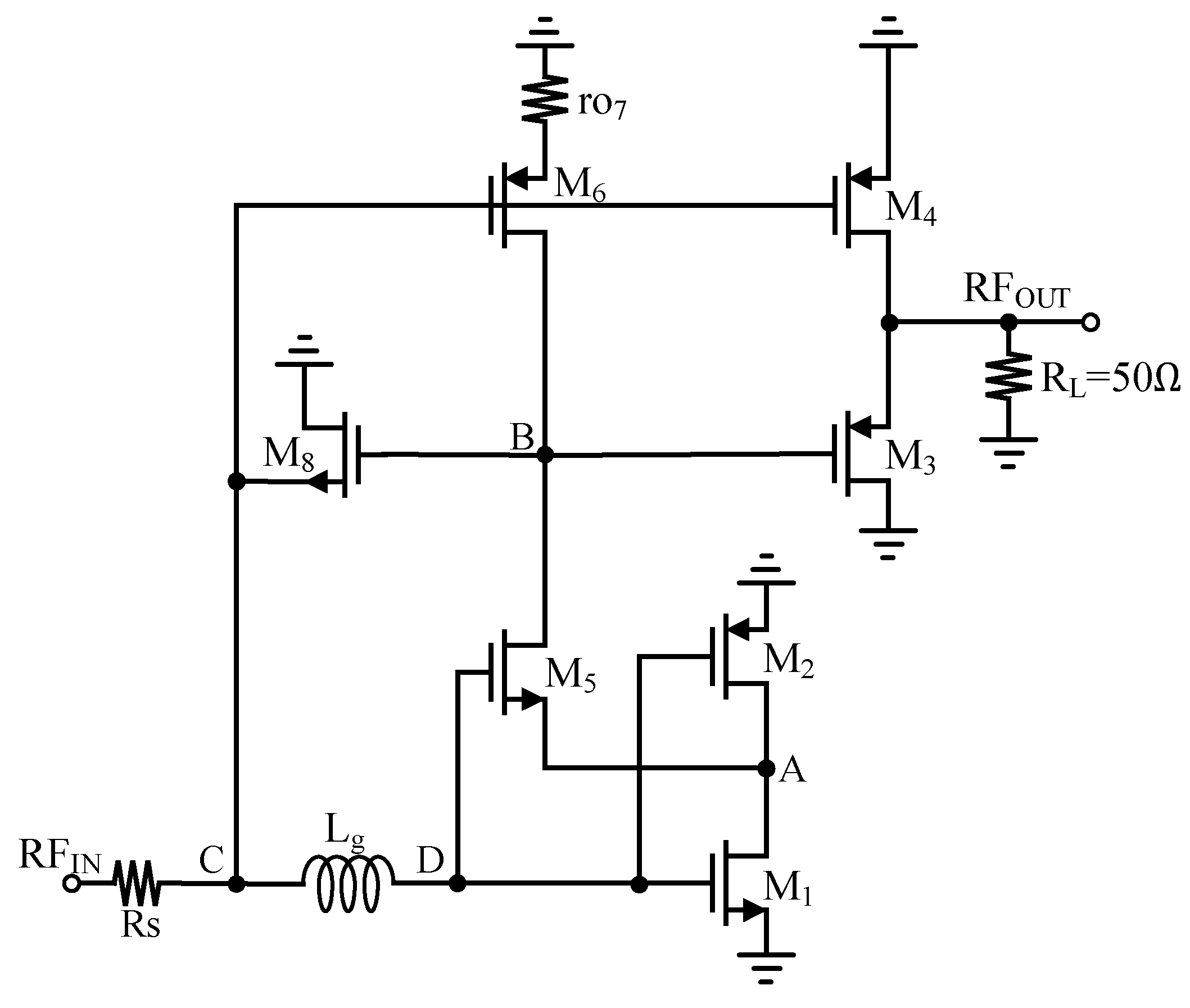

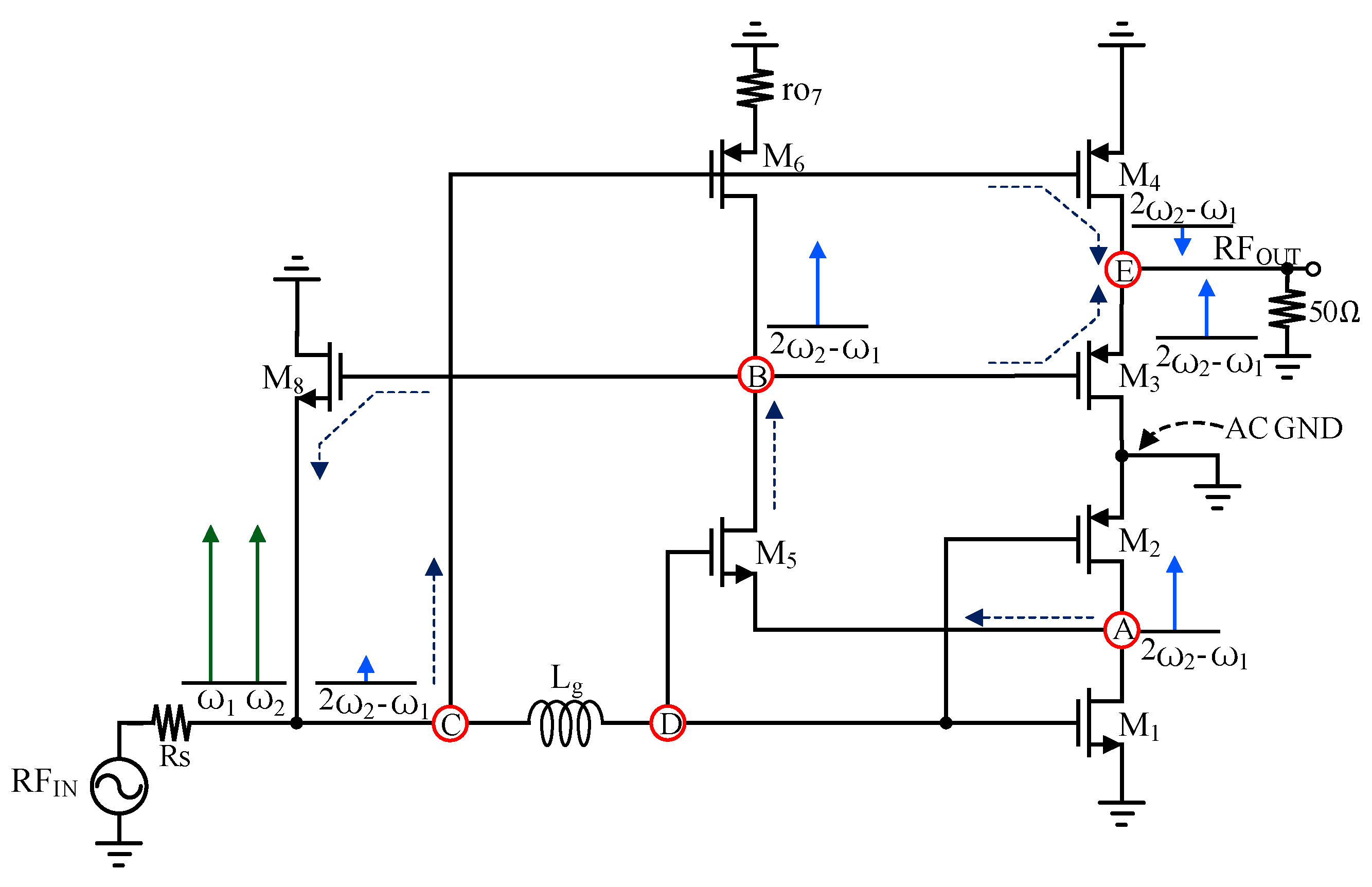

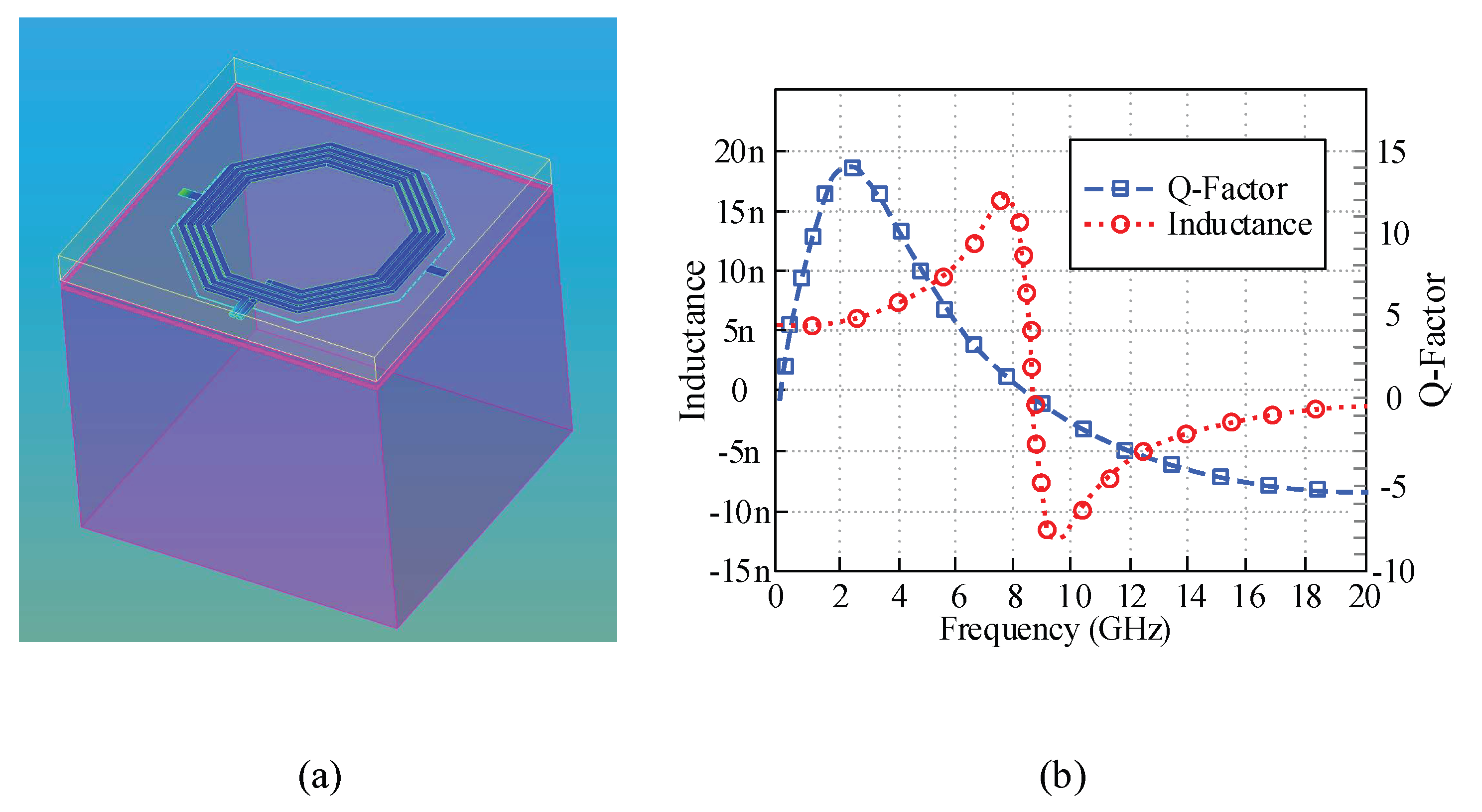

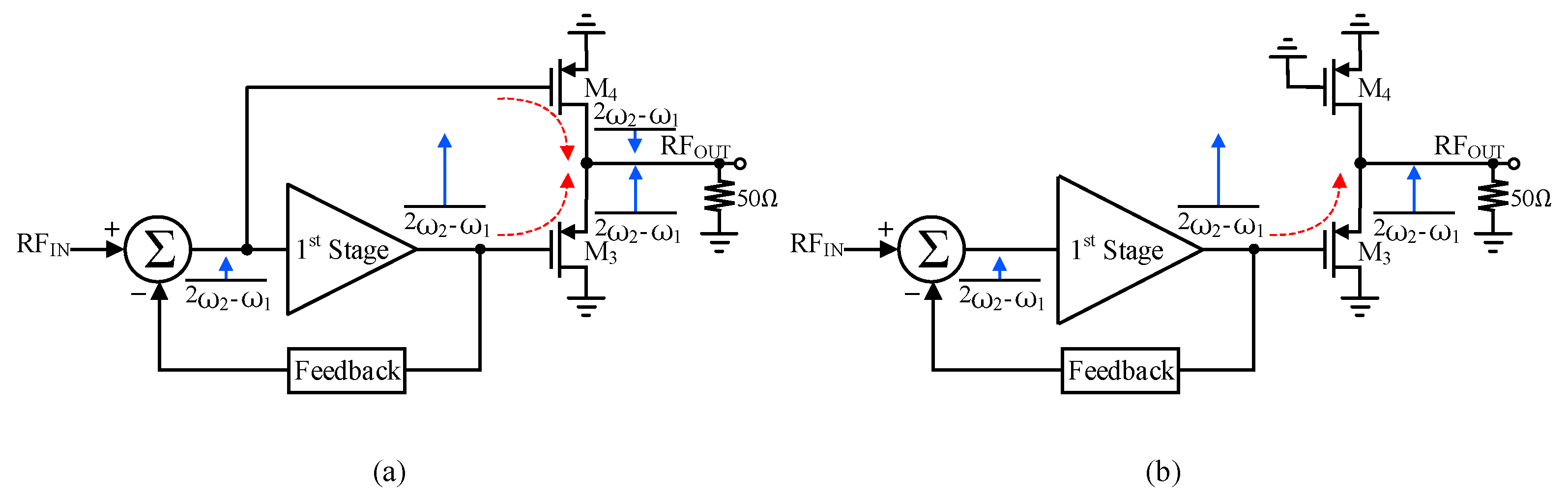

2. Analysis of the Proposed LNA

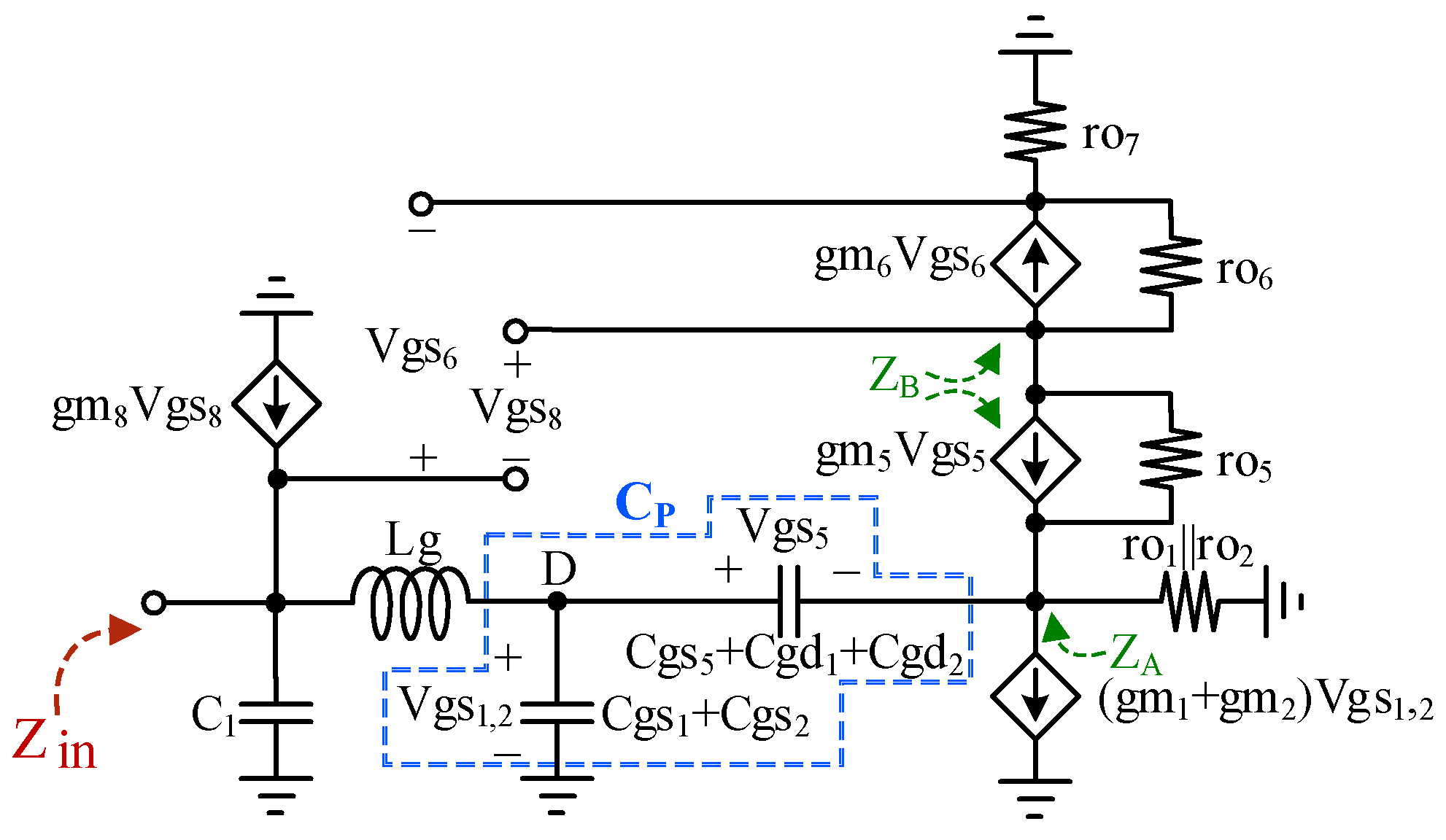

2.1. Input Impedance Matching

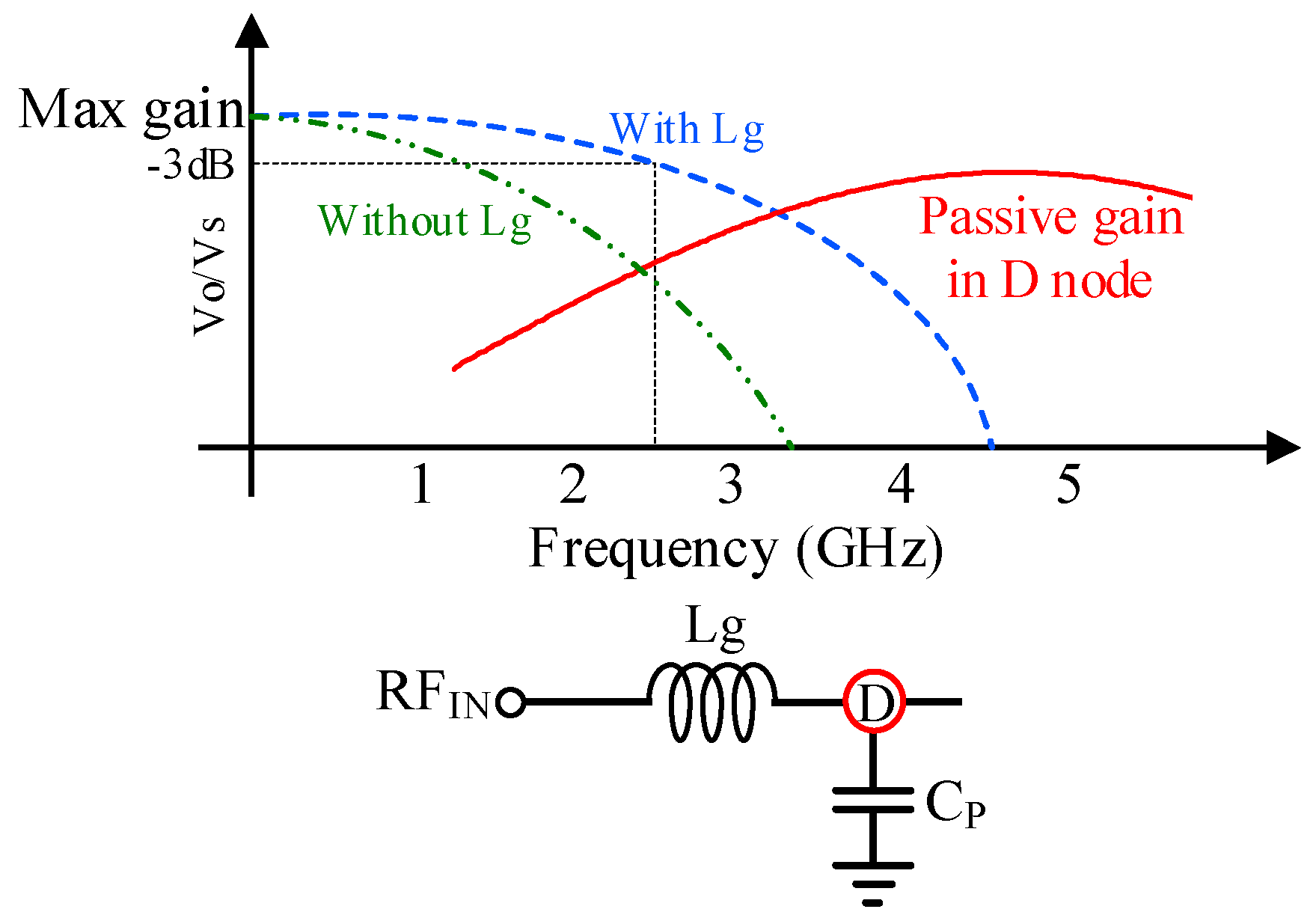

2.2. Voltage Gain

2.3. Noise Analysis

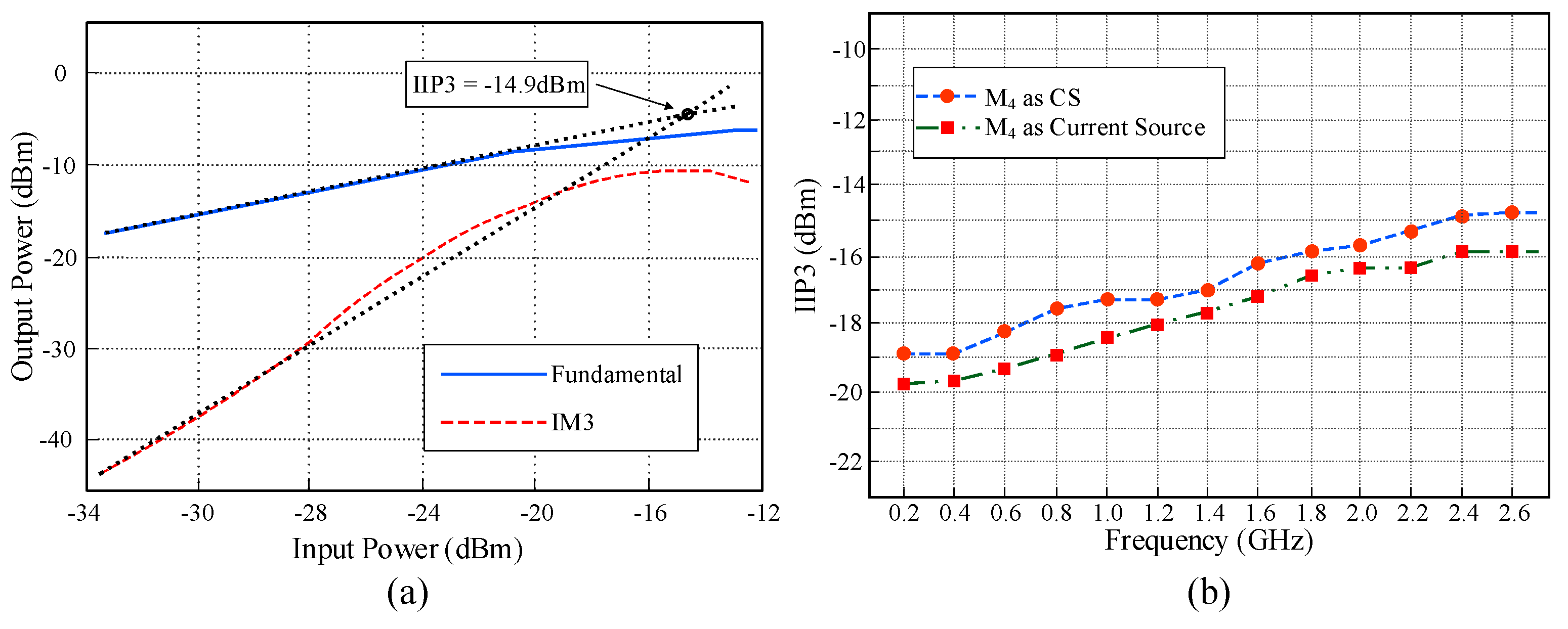

2.4. Linearity Analysis

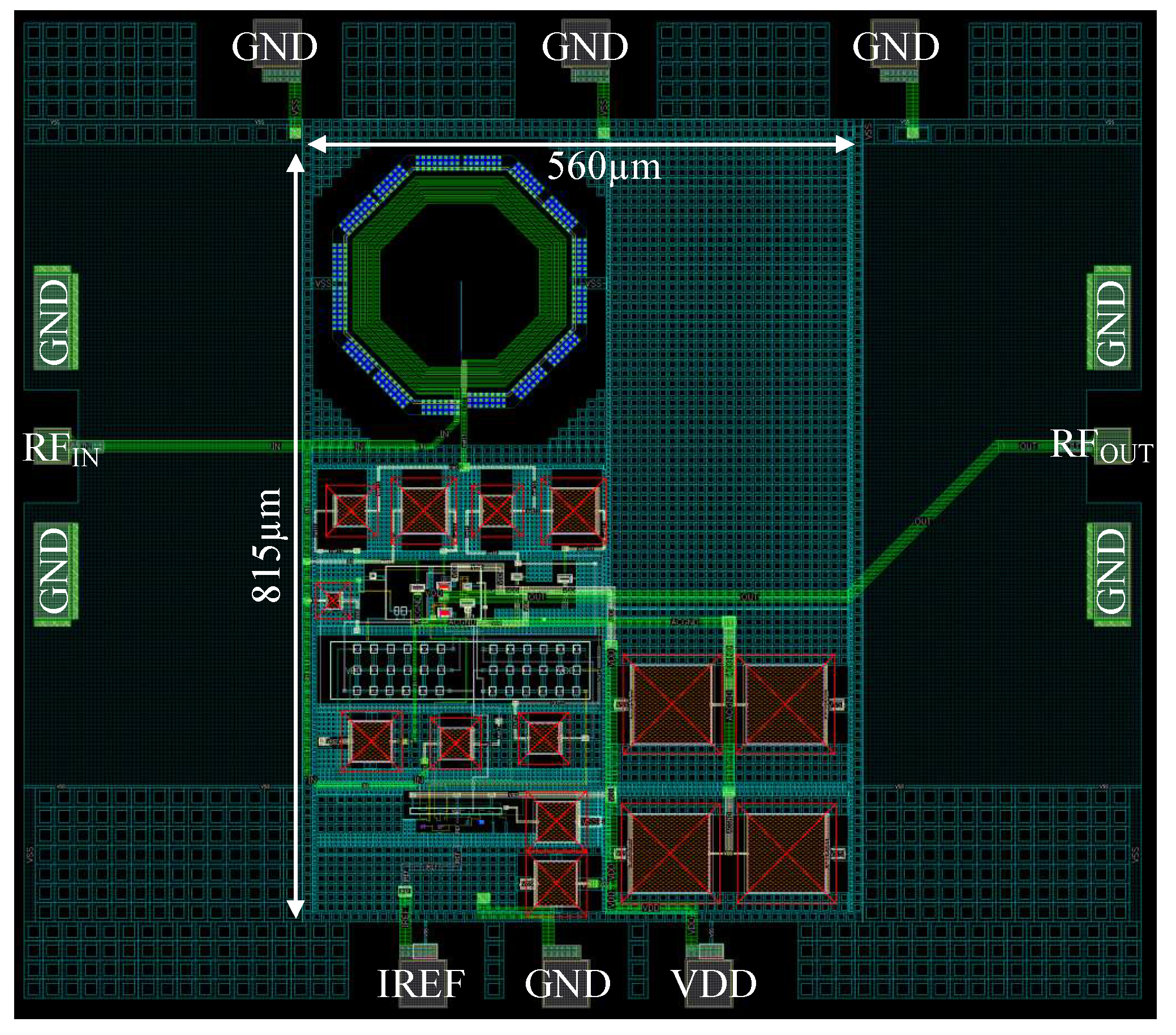

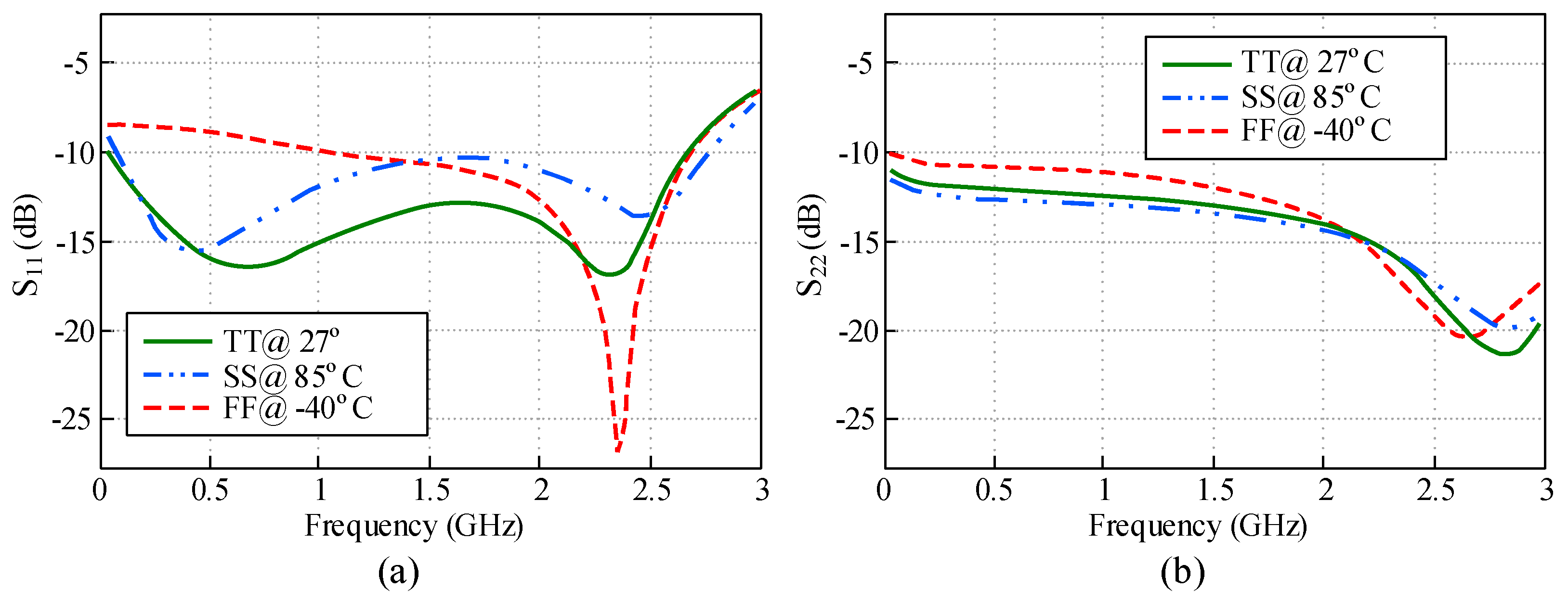

3. Simulation Results

4. Conclusions

References

- Wan, Qiuzhen, Jiong Liu, and Simiao Chen.” An Inductor less Gain-Controllable Wideband LNA Based on CCCIIs.” Micromachines, 2022, 13.11, 1832.

- Razavi, Behzad. RF microelectronics. Vol. 2. New York: Prentice Hall, 2012.

- Mir-Moghtadaei, Sayed Vahid and Farshad Shirani Bidabadi. “A CMOS 3.5 GHz Bandwidth Low Noise Amplifier using Active Inductor.” AUT Journal of Electrical engineering, 2025.

- B. Hu, X. P. Yu, W. M. Lim and K. S. Yeo, “Analysis and Design of Ultra-Wideband Low-Noise Amplifier with Input/Output Bandwidth Optimization and Single-Ended/Differential-Input Reconfigurability,” in IEEE Transactions on Industrial Electronics, 2014, vol. 61, no. 10, pp. 5672-5680.

- Shirani Bidabadi Farshad & Mir-Moghtadaei Sayed Vahid. “An Ultra-Wideband 0.1–6.1 GHz Low Noise Amplifier in 180 nm CMOS Technology”. Journal of Circuits Systems and Computers, 2020, 30, 2150104.

- K. -W. Cheng, W. -W. Chen and S. -D. Yang, “A Low Power Sub-GHz Wideband LNA Employing Current-Reuse and Device-Reuse Positive Shunt-Feedback Technique”, IEEE Microwave and Wireless Components Letters, 2022, vol. 32, no. 12, pp. 1455-1458.

- F. Bruccoleri, E. A. M. Klumperink, and B. Nauta, “Wide-band CMOS low-noise amplifier exploiting thermal noise canceling” IEEE J. Solid-State Circuits, 2004, vol. 39, no. 2, pp. 275–282.

- Hu, S., Du, J., Chen, P., Nguyen, H. M., Quinlan, P., Siriburanon, T., & Staszewski, R. B. “A Type-II Phase-Tracking receiver”,IEEE Journal of Solid-state Circuits, 2021, 56, 427–439.

- Bahareh Shirmohammadi, & Yavari, M. “A Linear Wideband CMOS Balun-LNA With Balanced Loads”, IEEE Transactions on Circuits & Systems II Express Briefs, 2021, 69, 754–758.

- S. Kim and K. Kwon, “A 50-MHz-1-GHz 2.3-dB NF noise- cancelling balun-LNA employing a modified current-bleeding technique and balanced loads”, IEEE Transaction on Circuits and System I, 2019, Reg. Papers, vol. 66, pp. 546–554.

- S. Kim and K. Kwon, “Broadband balun-LNA employing local feedback gm-boosting technique and balanced loads for low-power low-voltage applications,” IEEE Transaction on Circuits and System I, 2020, Reg. Papers, vol. 67, no. 12, pp. 4631–4640.

- S. Tiwari and J. Mukherjee, “An inductor less wideband Gm-boosted balun LNA with NMOS-PMOS configuration and capacitively coupled loads for sub-GHz IoT applications”, IEEE Trans. Circuits Syst. II,2021, Exp. Briefs, early access.

- K. H. Kishore, B. Venkataramani, R. Sanjay, and V. S. Rajan, “High gain inductor less wideband Balun-LNA using asymmetric CCC & BIST using RMS detectors”, AEU-International Journal of Electronics and Communications”, 2019, vol. 105, pp. 135–144.

- H. U. Mahmood, S. -G. Lee and J. Kim, “A 0.1–4.2 GHz, 960-μW Inductor-Less and Negative Shunt Feedback LNA With Simultaneous Noise and Distortion Cancellation and Bandwidth Extension”, IEEE Transactions on Circuits and Systems I, 2024, Regular Papers, vol. 71, no. 6, pp. 2563-2575.

- Pu, Y., Li, W., Li, Q., Ma, X., & Xu, H. A 0.2–3.2-GHz active Balun-LNA with 1.4–2.18-dB NF utilizing asymmetric current distribution in 28-nm CMOS. IEEE Microwave and Wireless Technology Letters, 2025.

- Z. Liu, C. Chye Boon and Y. Dong, “A 0.6 V, 1.74 mW, 2.9 dB NF Inductor less Wideband LNA in 28-nm CMOS Exploiting Noise Cancellation and Current Reuse,” in IEEE Transactions on Circuits and Systems I, 2024, Regular Papers, vol. 71, no. 8, pp. 3561-3572.

- J. -W. Park, D. -Y. Kim and D. Im, “A Broadband Gm-Boosted Active Feedback CMOS Low-Noise Amplifier for Low- and Mid-Band 5G Applications,” in IEEE Transactions on Circuits and Systems II: Express Briefs, 2025, vol. 72, no. 2, pp. 399-403.

- Sarpeshkar, R., Delbruck, T., & Mead, C.” White noise in MOS transistors and resistors”. IEEE Circuits and Devices Magazine, 1993, 9, 23–29.

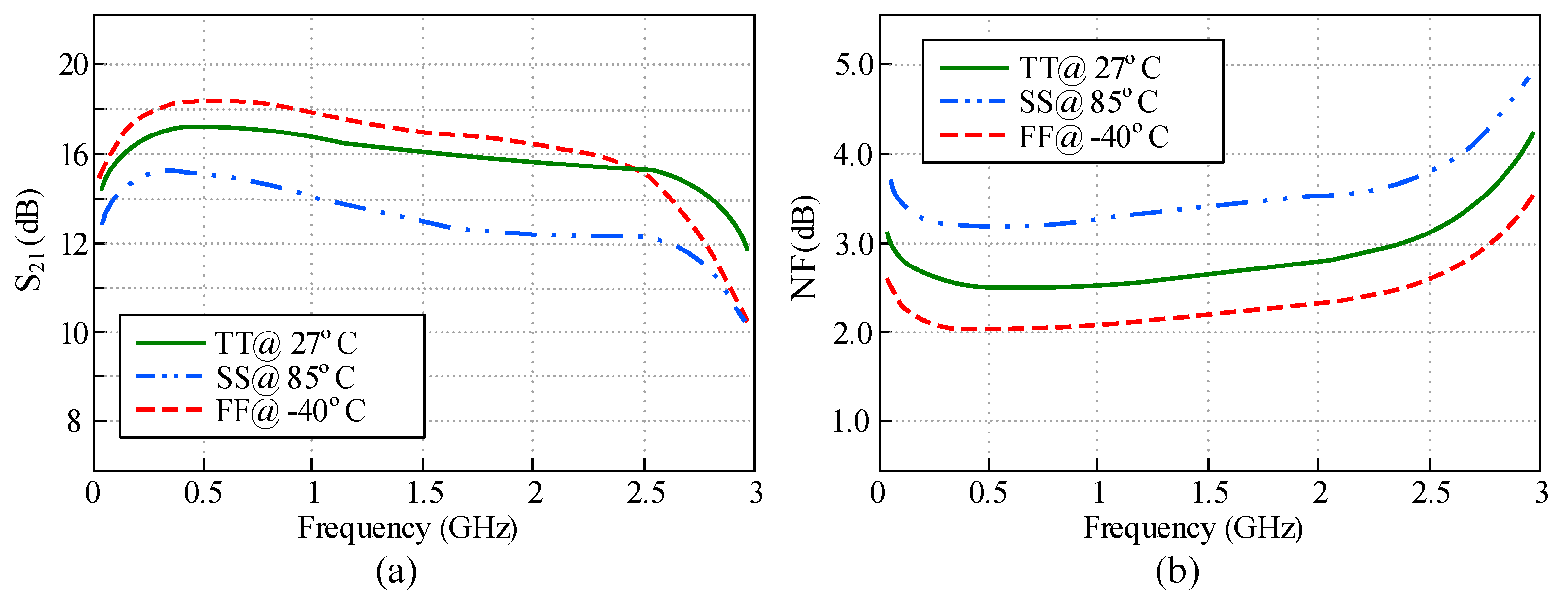

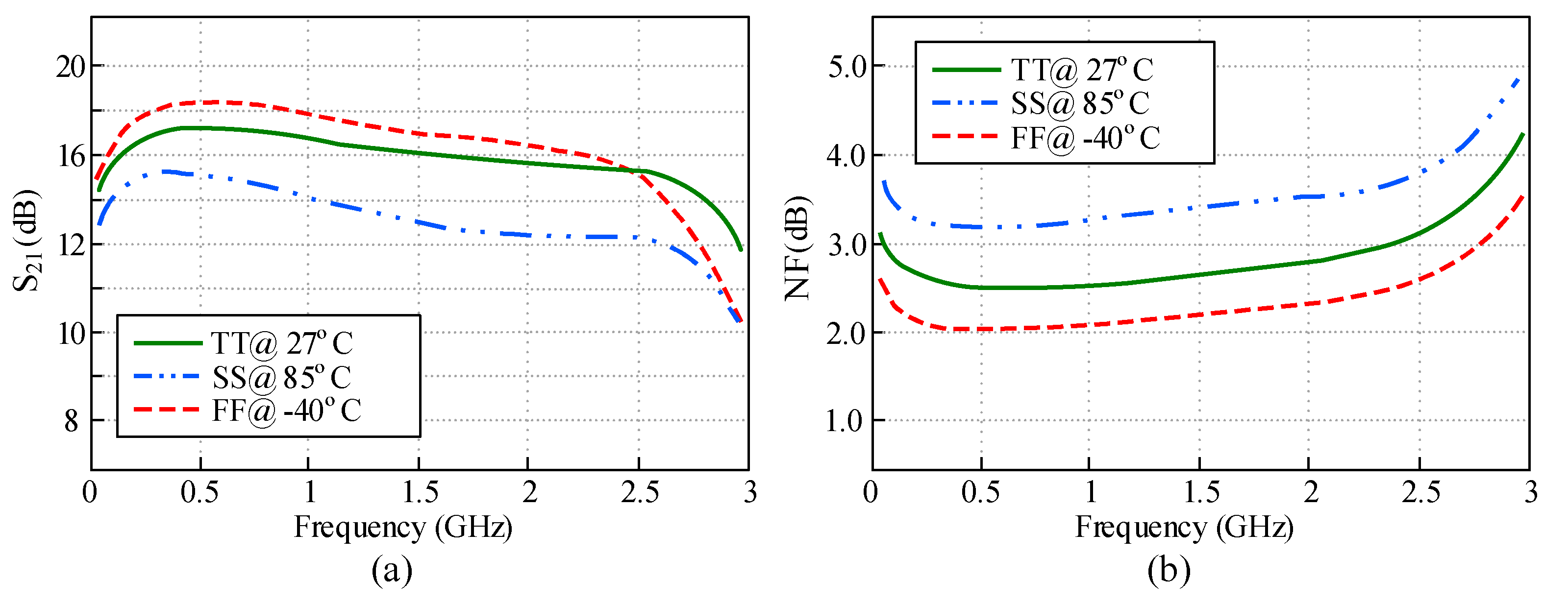

| Parameter | TT @ 27˚C | SS @ 85˚C | FF @ -40˚C |

|---|---|---|---|

| BW-3dB (GHz) | 0.17-2.68 | 0.17-2.2 | 0.17-2.54 |

| S21 (dB) | 15-17.24 | 13.58-15.58 | 15.2-18.2 |

| NFmin (dB) | 2.67 | 3.35 | 1.99 |

| IIP3 (dBm) | -14.9 | -13 | -12.6 |

| Power (mW) | 3.52 | 3.64 | 2.87 |

| Reference | CMOS Process | VDD (V) | Frequency (GHz) | S21 (dB) | NF (dB) | S11(dB) | IIP3(dBm) | Symmetric load | Power (mW) | Area (mm2) | FoM (dB) |

|---|---|---|---|---|---|---|---|---|---|---|---|

| TCAS-II’22*b [9] | 65 nm | 1.5 | 0.47-3.3 | 19.45-22 | 2.57-3.5 | <-10 | +2.81 | Yes | 12.5 | 0.057 | 11.02 |

| TCAS-I’19b [10] | 65 nm | 2.2 | 0.05-1 | 24-30 | 2.3-3.3 | <-12 | -4.1 | Yes | 19.8 | 0.045 | 6.84 |

| TCAS-I’20b [11] | 65 nm | 1 | 0.05-1.3 | 24-27.5 | 2.3-3 | <-12 | -2.2 | Yes | 5.7 | 0.046 | 17.73 |

| TCAS-II’21b [12] | 180 nm | 1.8 | 0.13-0.93 | 16.6-19.6 | 3.6-5 | <-10 | -8.5 | Yes | 3 | 0.18 | 6.52 |

| AEUE’19*b [13] | 180 nm | 1.2 | 0.18-2 | 15-20.8 | 2.65-3.8 | <-8 | -4.91 | Yes | 4.9 | 0.04 | 13.7 |

| TCAS-I’24b [14] | 65 nm | 0.78 | 0.1-4.2 | 15.6 | 4.45-6.9 | <-10 | -14.5 | No | 0.96 | 0.011 | 23.19 |

| MWT’25 [15] | 28 nm | 1.1 | 0.2-3.2 | 24.4-26 | 1.4-2.18 | <-15 | -3.6 | Yes | 17.4 | 0.018 | 19.13 |

| TCAS-I’24b [16] | 28 nm | 0.6 | 0.2-2.85 | 20 | 2.9-3.6 | <-13 | -12.3 | No | 1.74 | 0.0048 | 24.19 |

| TCAS-II’25b [17] | 130 nm | 1.3 | 0.01-1.7 | 21.5 | 1.1-1.9 | <-10 | -2.3 | Yes | 9.1 | 0.18 | 17.45 |

| This work* | 65 nm | 1 | 0.17-2.68 | 15-17.24 | 2.67-3.24 | <-10 | -14.9 | No | 3.52 | 0.45 | 15.7 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).