Submitted:

14 March 2025

Posted:

17 March 2025

Read the latest preprint version here

Abstract

Keywords:

1. Introduction

2. Materials and Methods

2.1. Related Work

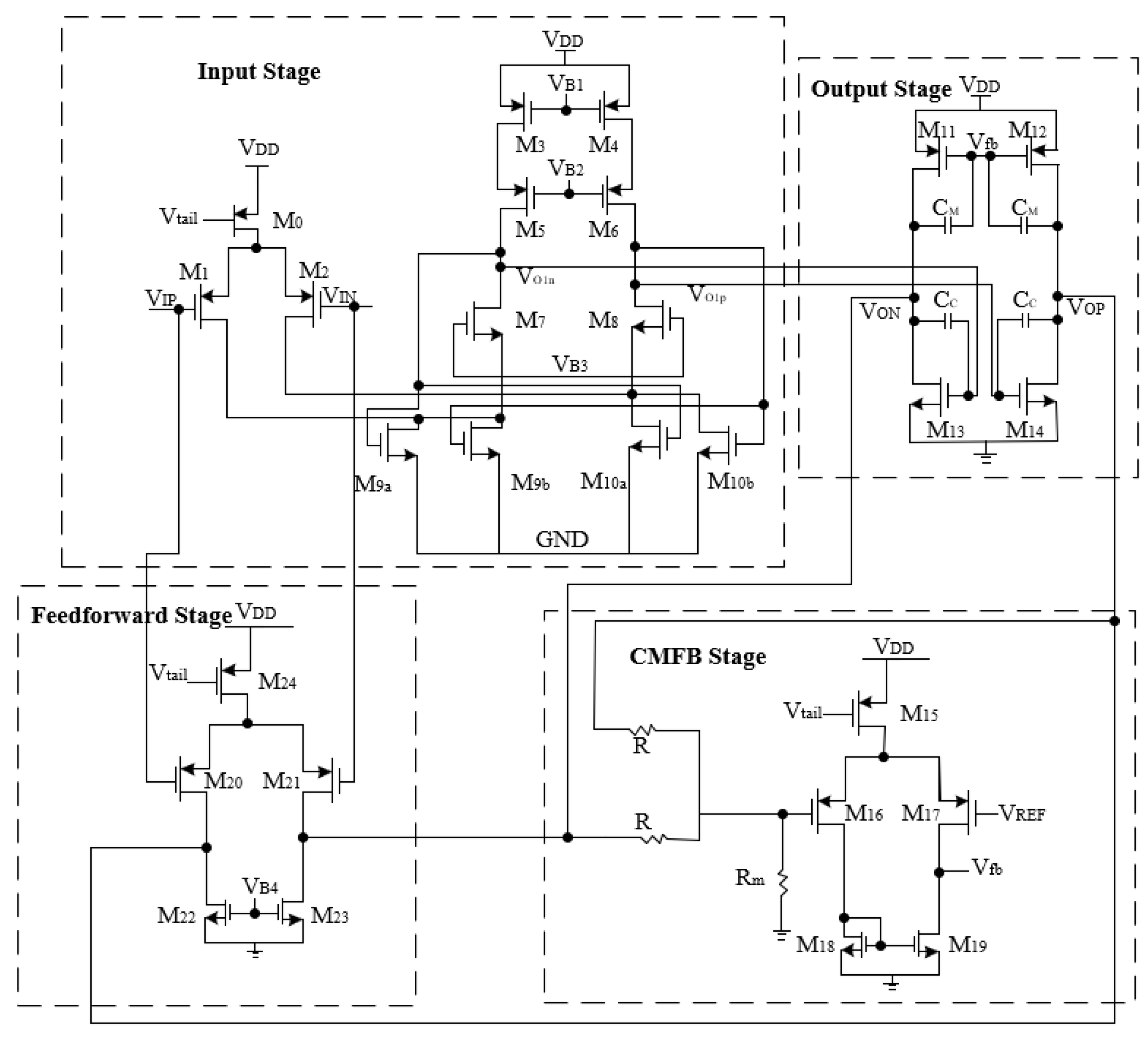

2.2. Proposed Methodology

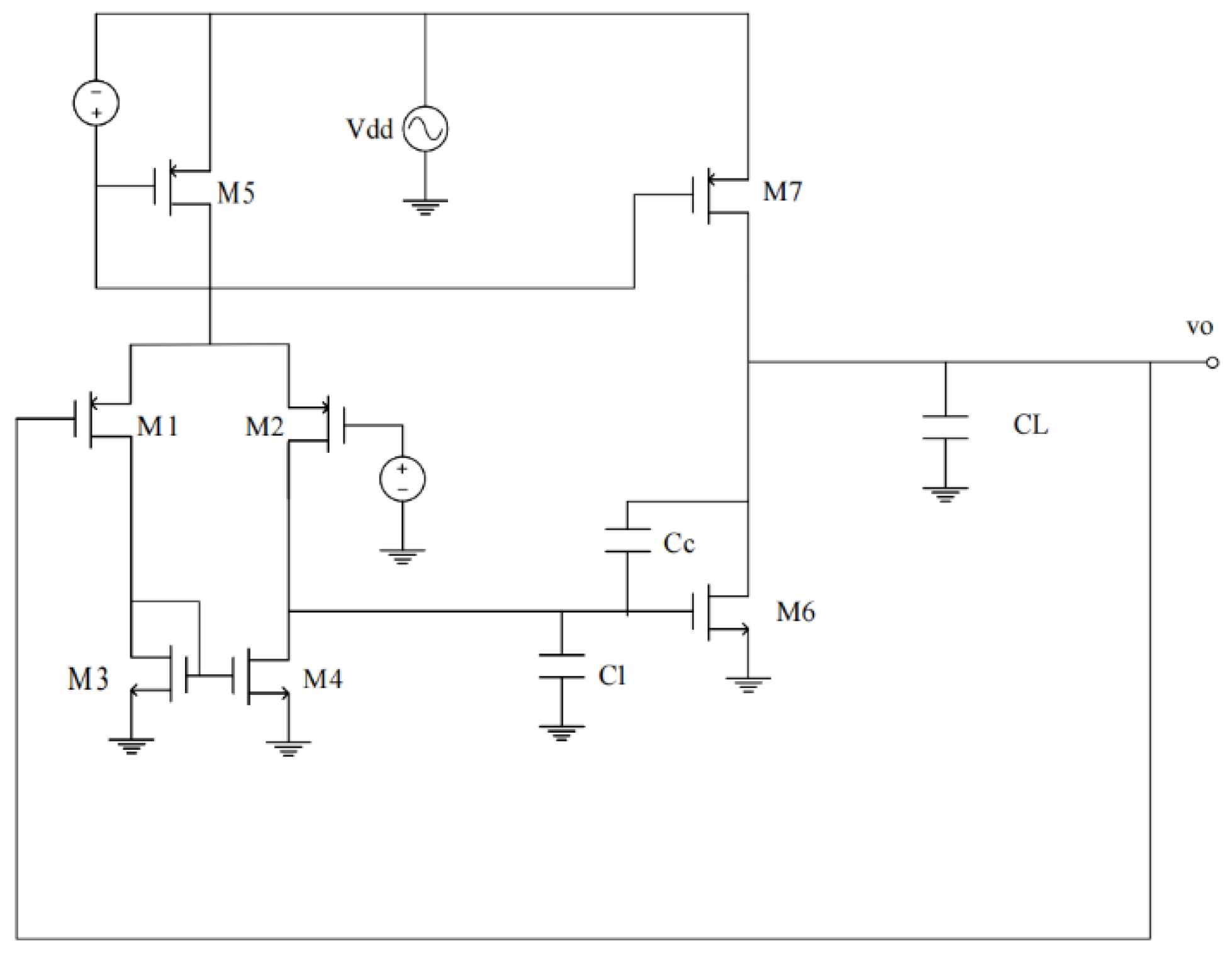

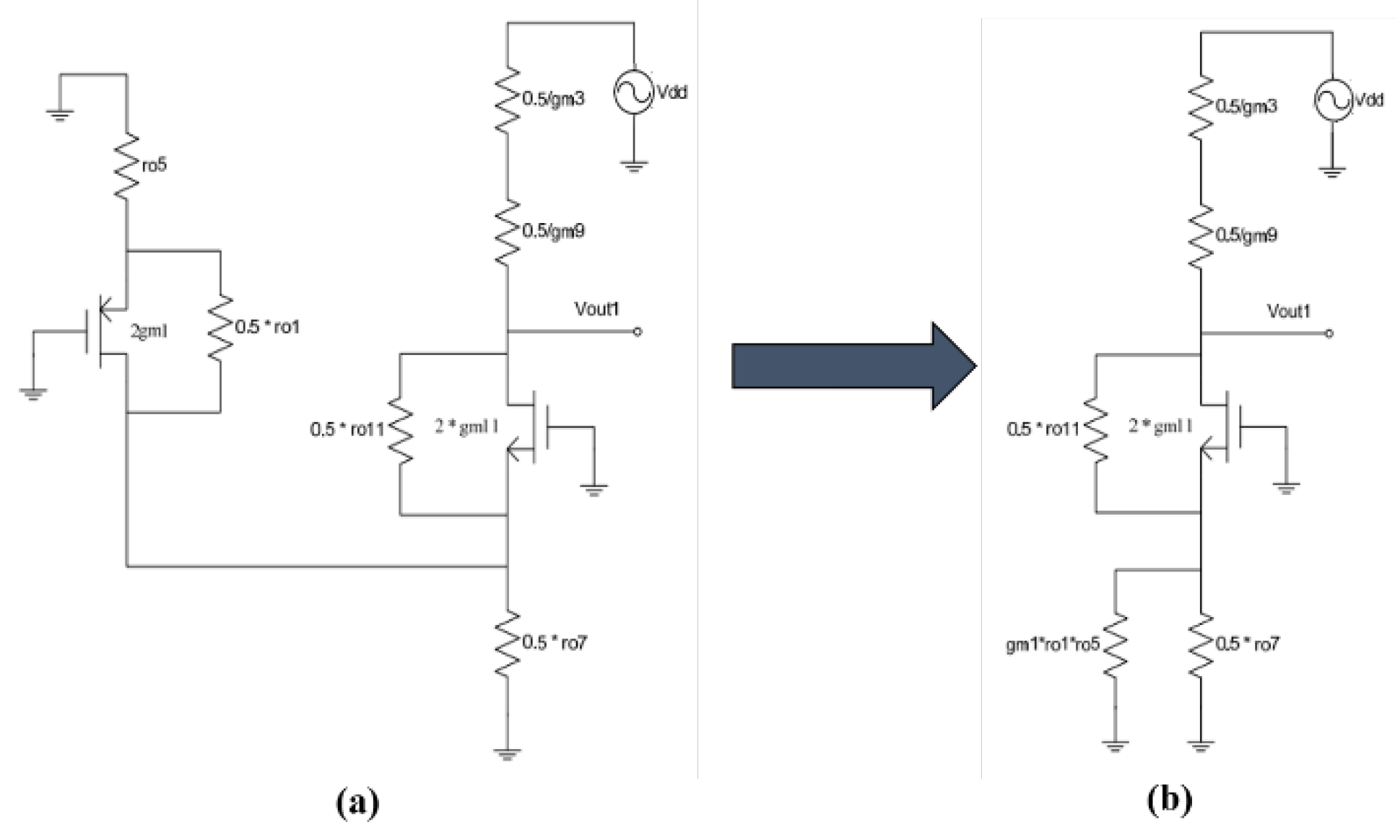

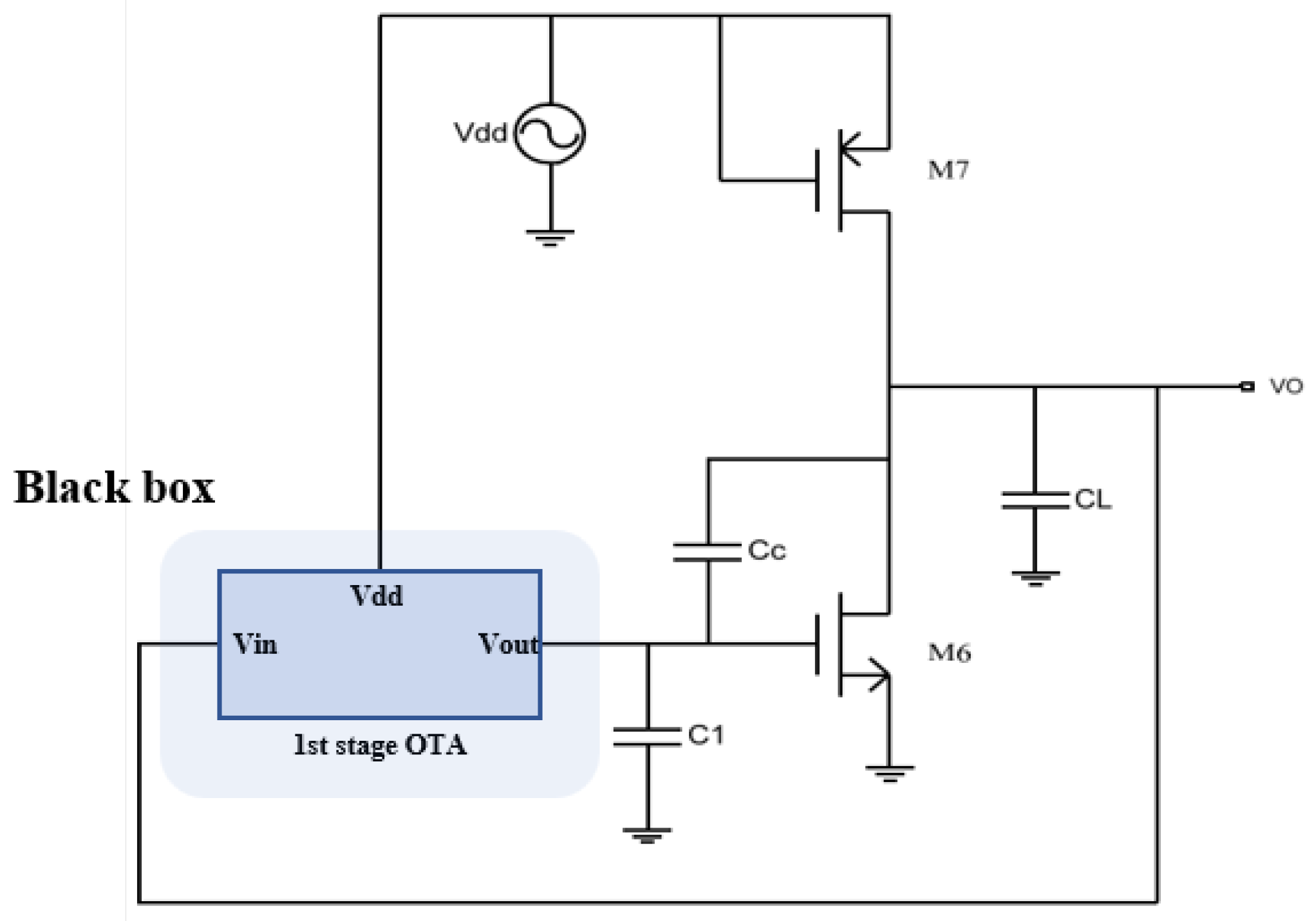

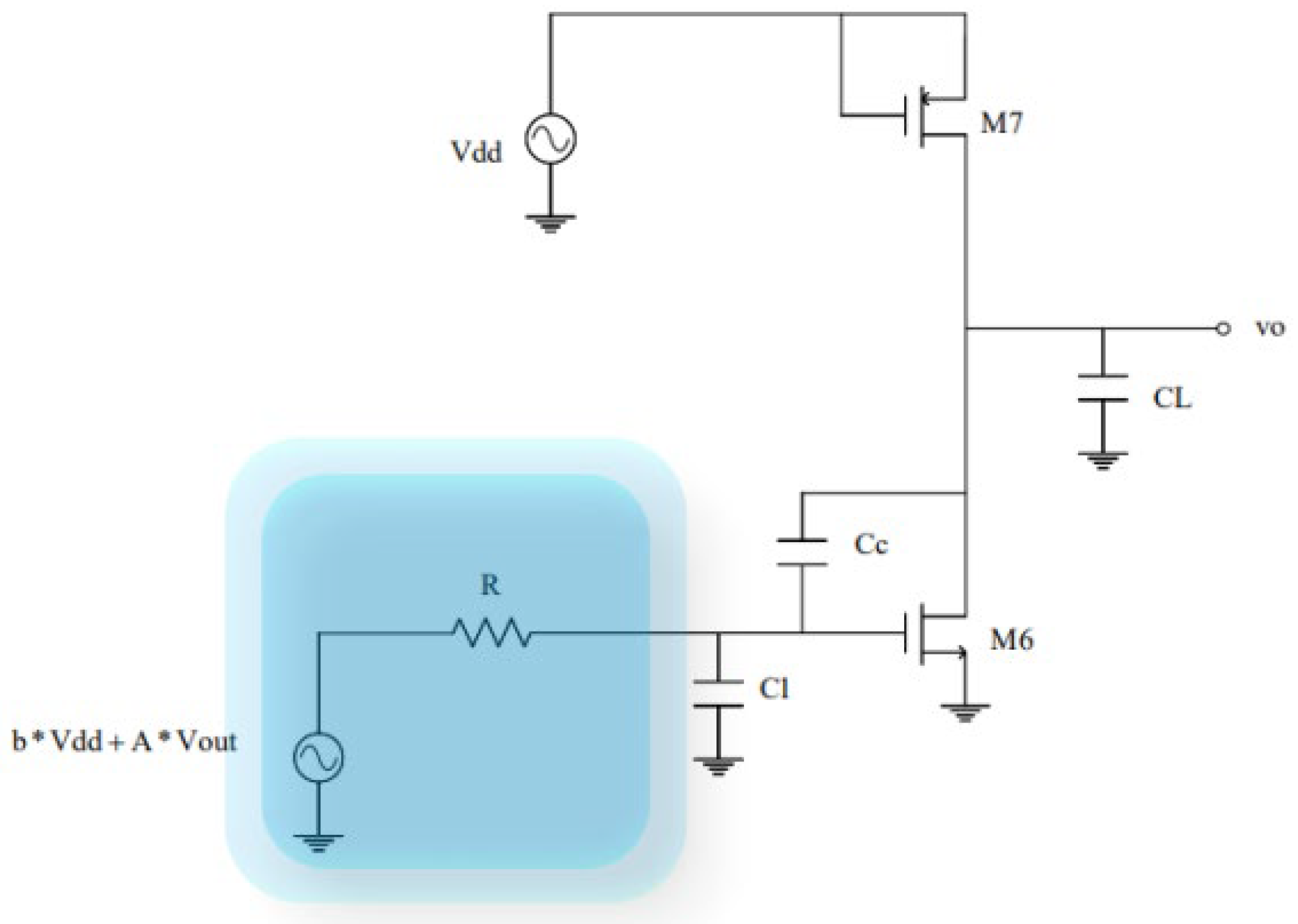

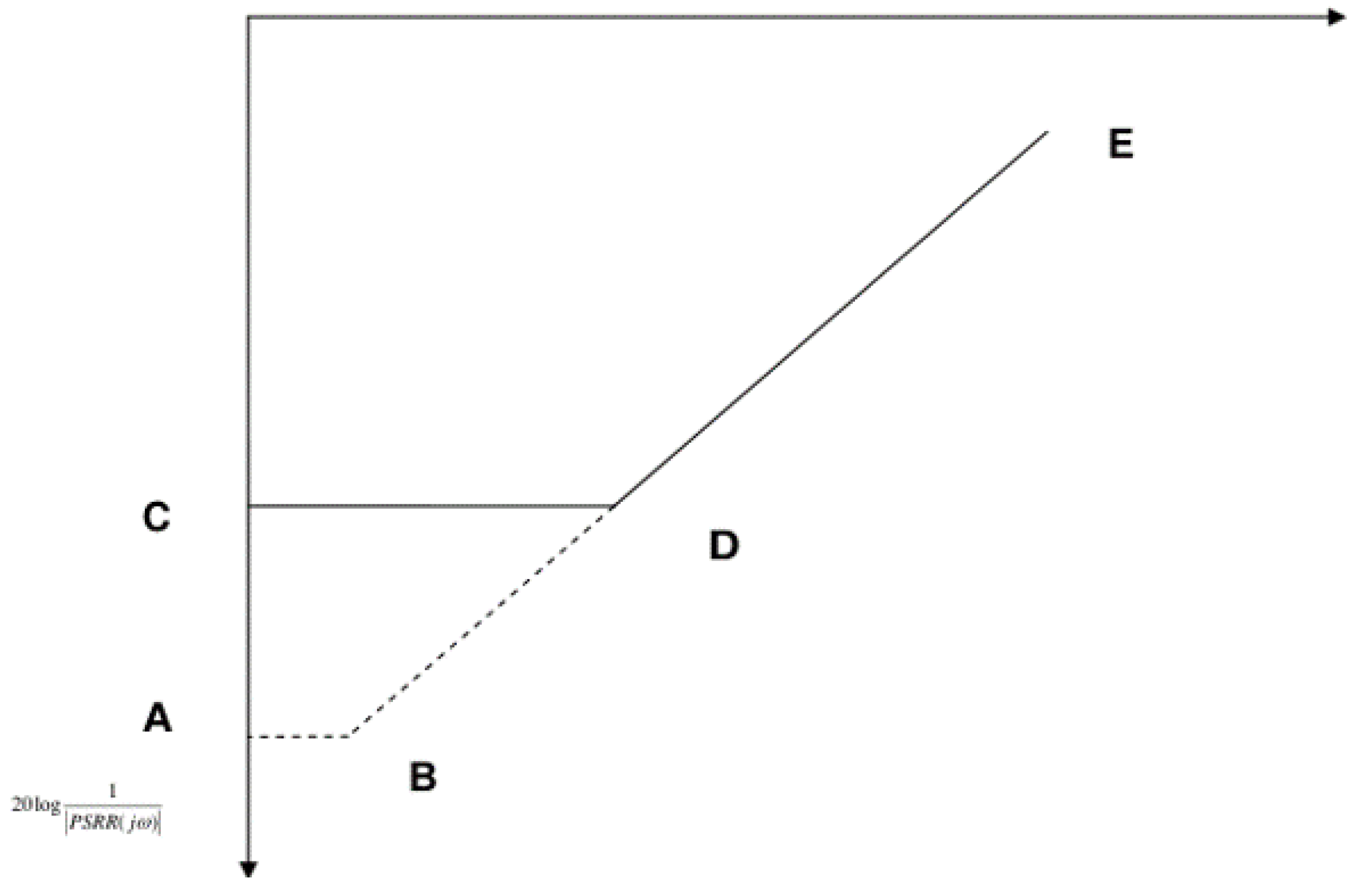

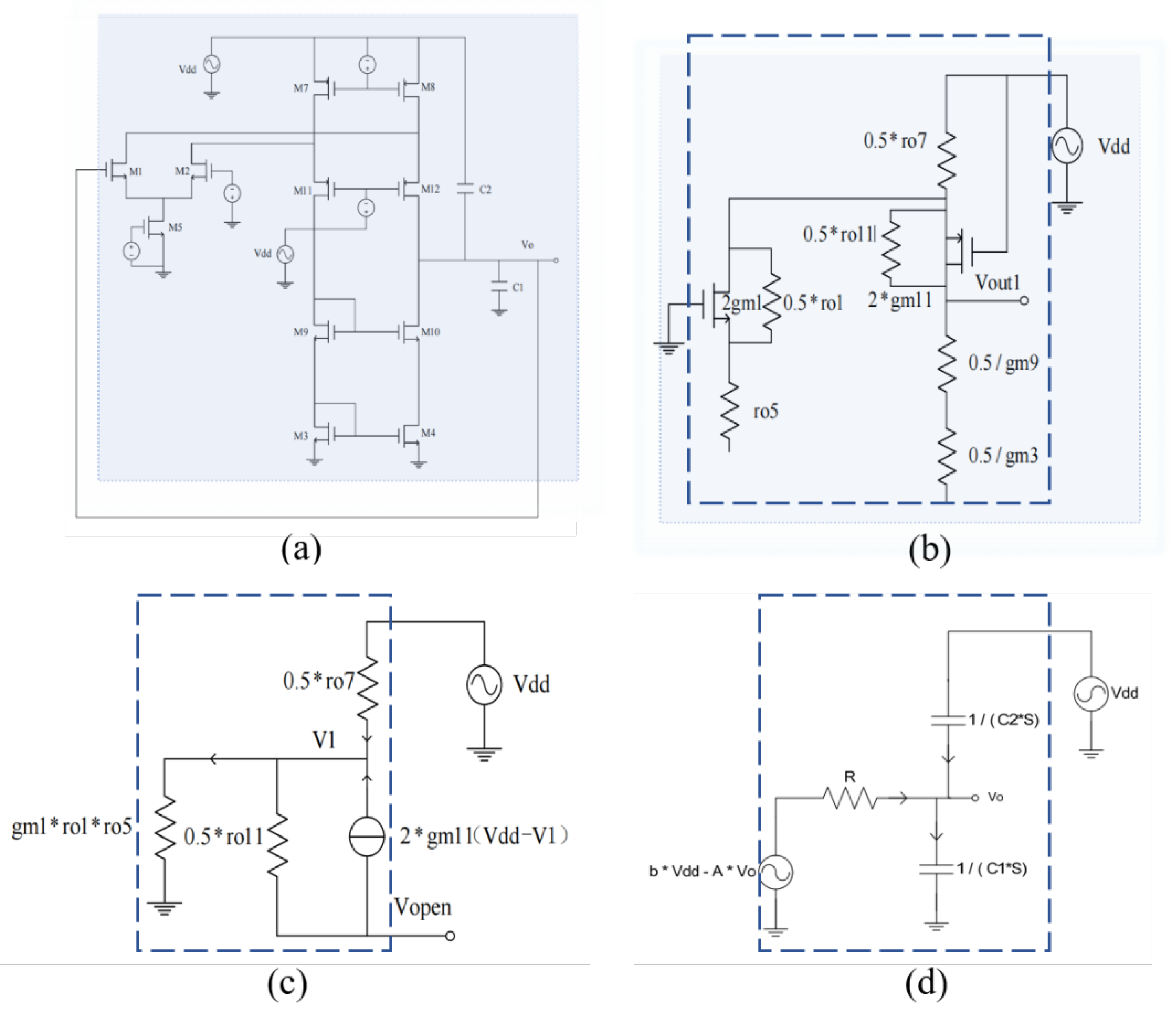

2.2.1. PSRR Calculation for P-Input Two-Stage Op-Amps

- (a)

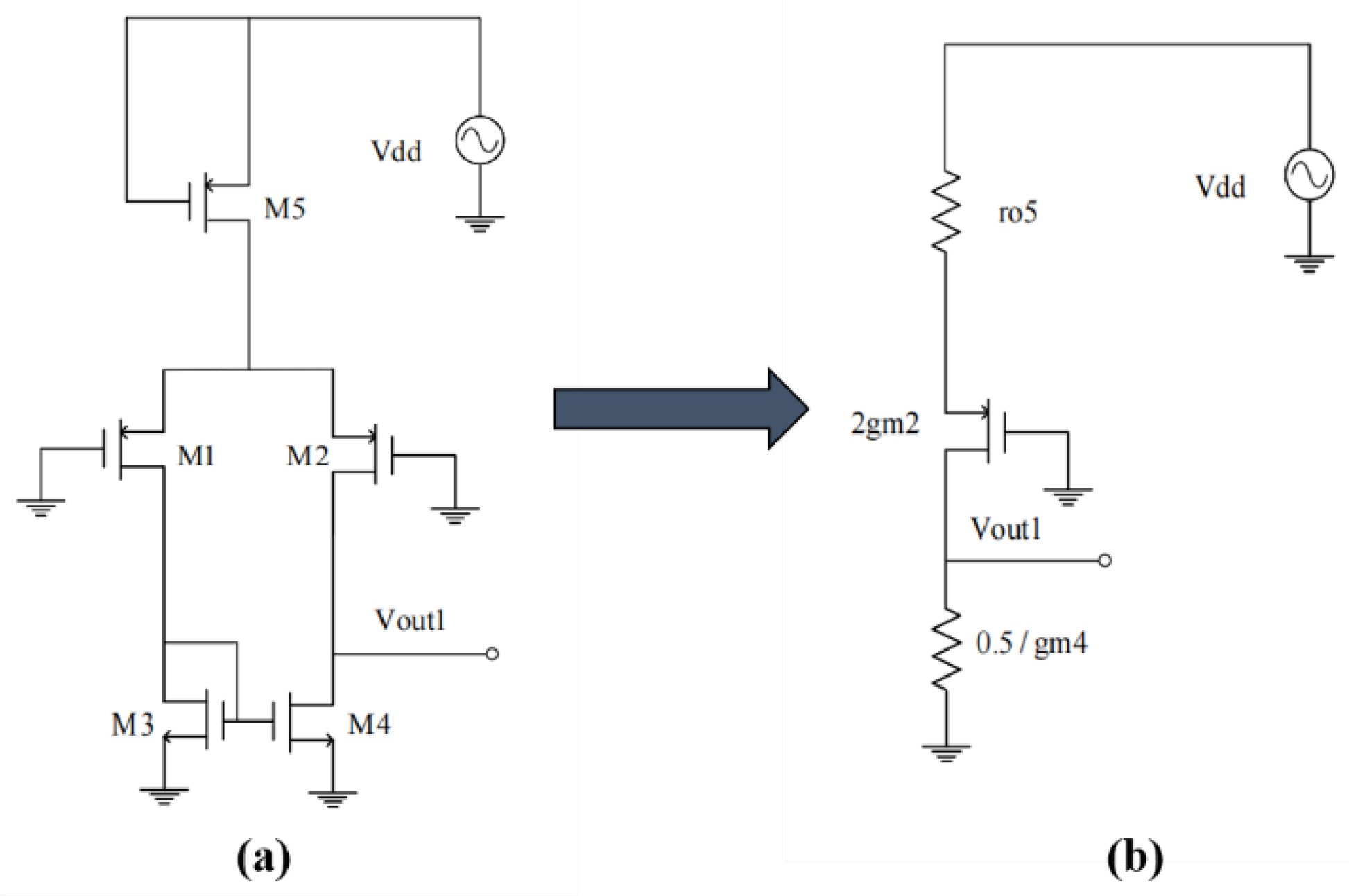

- Evaluating the Impact of Vdd on the Thevenin Equivalent Output Voltage of the First Stage

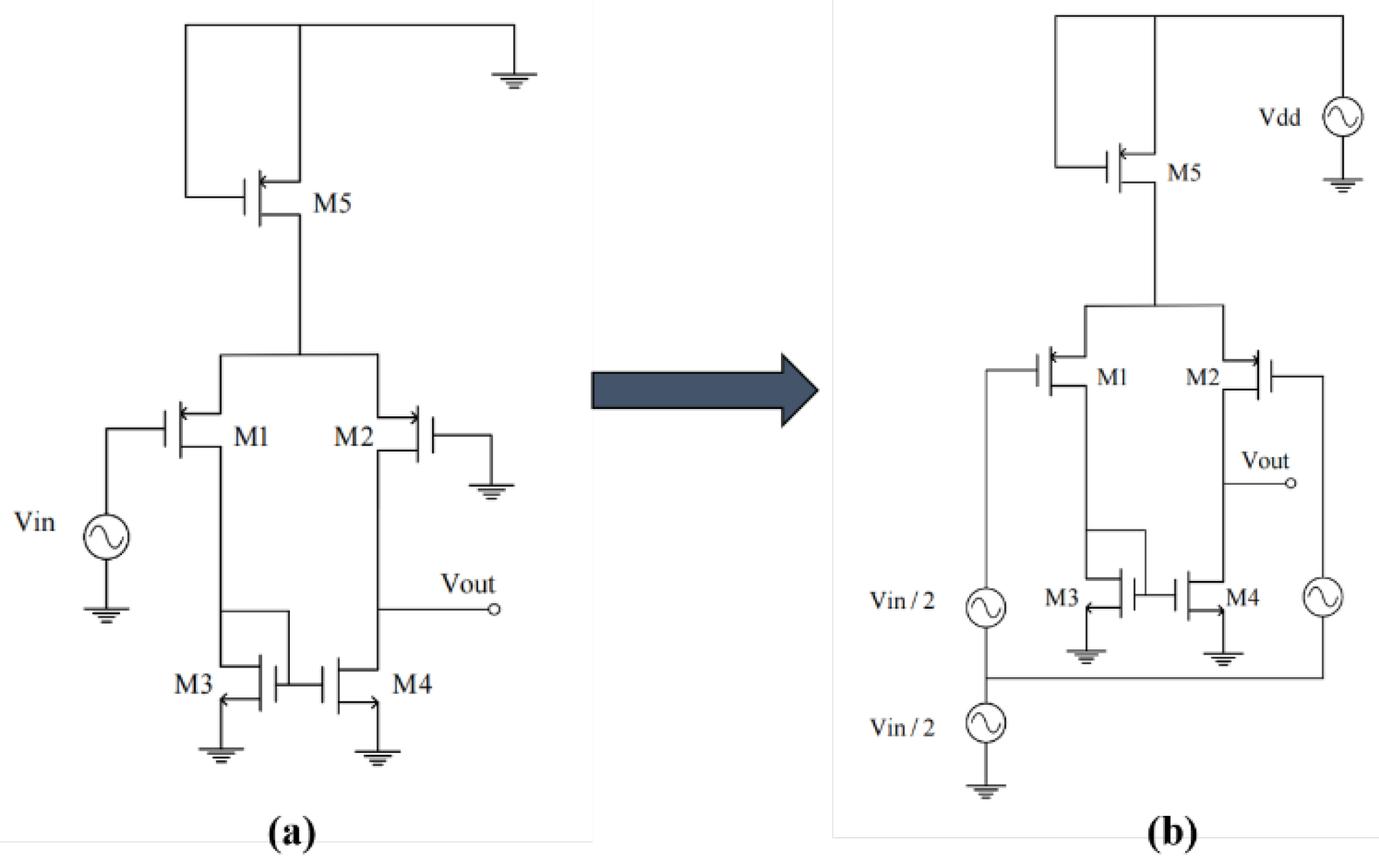

- (b) Evaluating the Impact of Vin on the Thevenin Equivalent Output Voltage of the First Stage

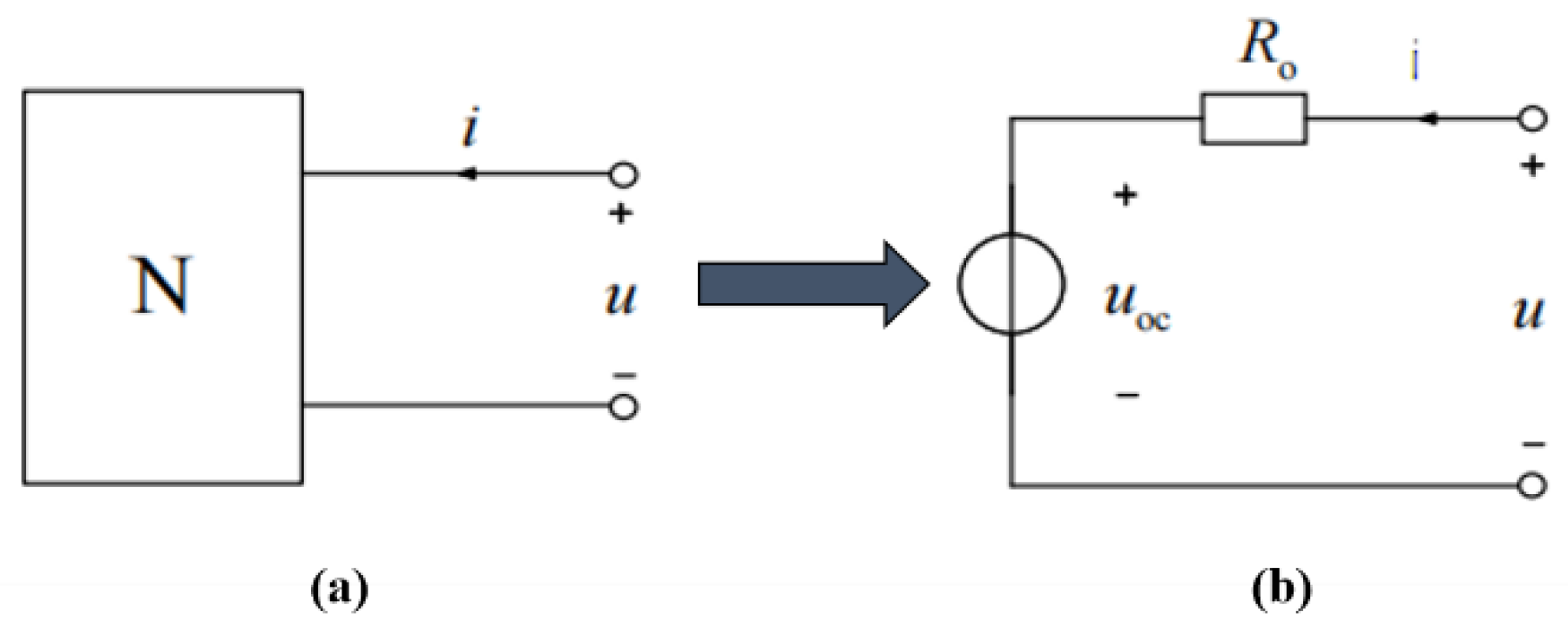

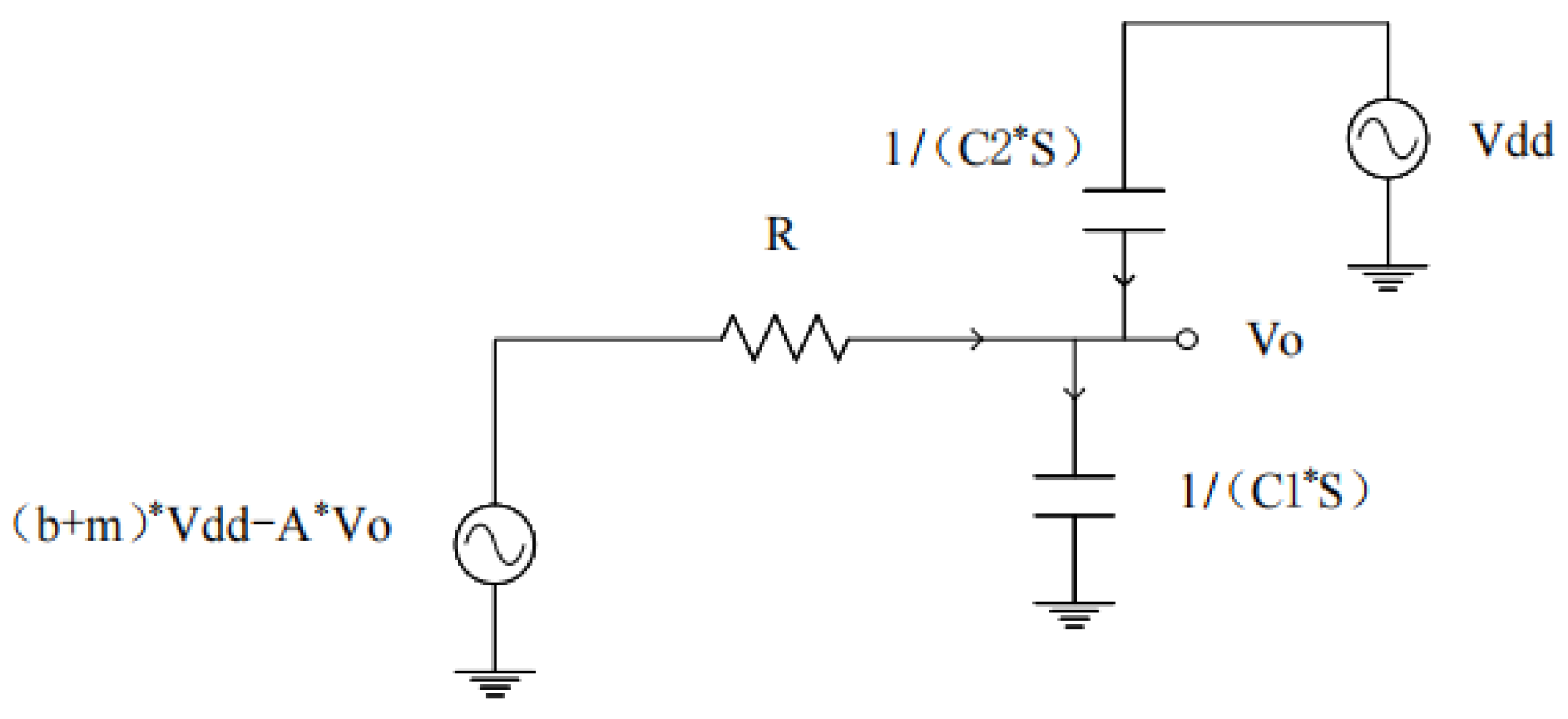

- (c) Constructing the Thevenin Equivalent Circuit

- (a)

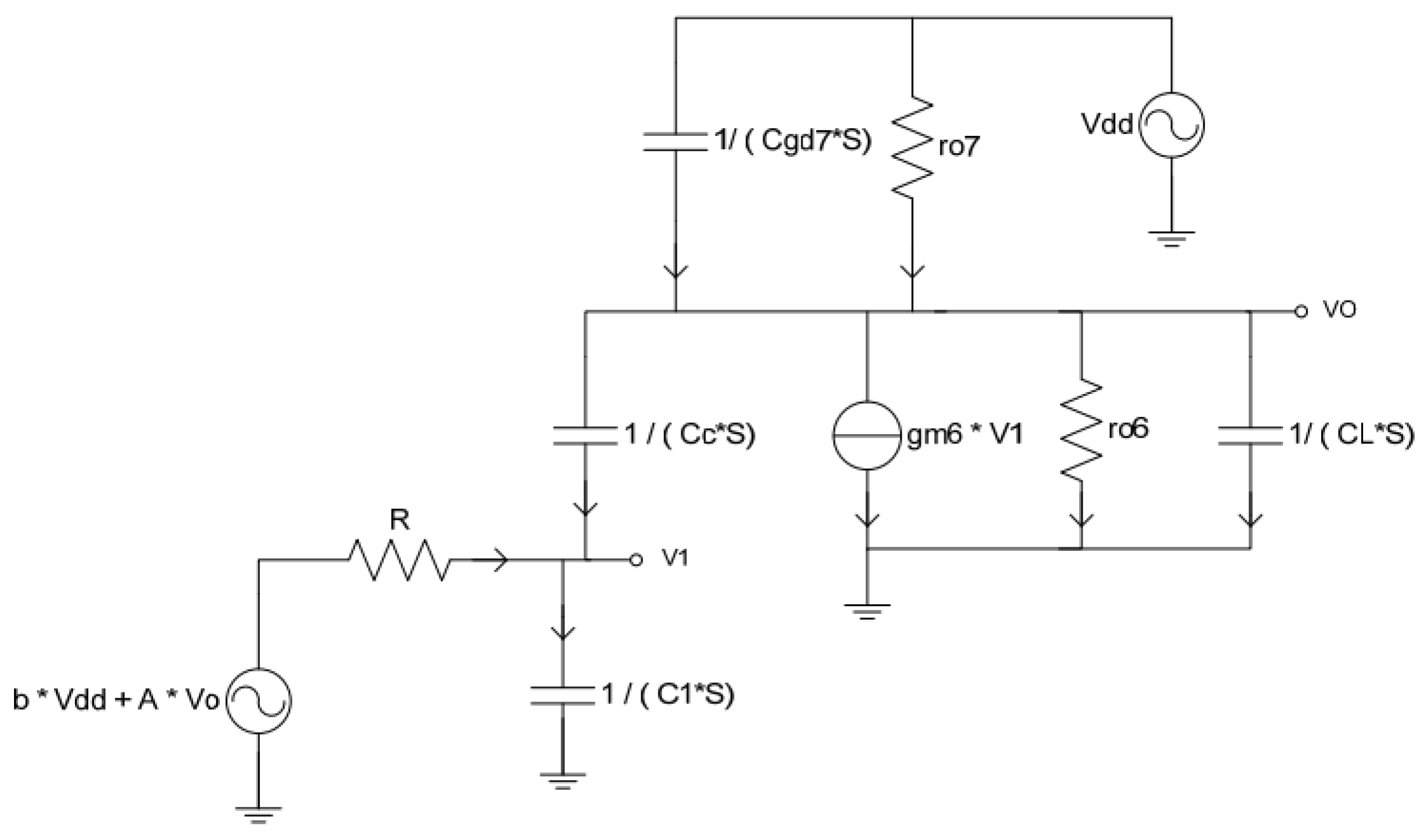

- Deriving the PSRR Transfer Function

2.2.1. PSRR Calculation for N-Input Two-Stage Op-Amps

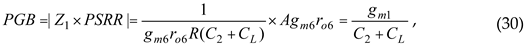

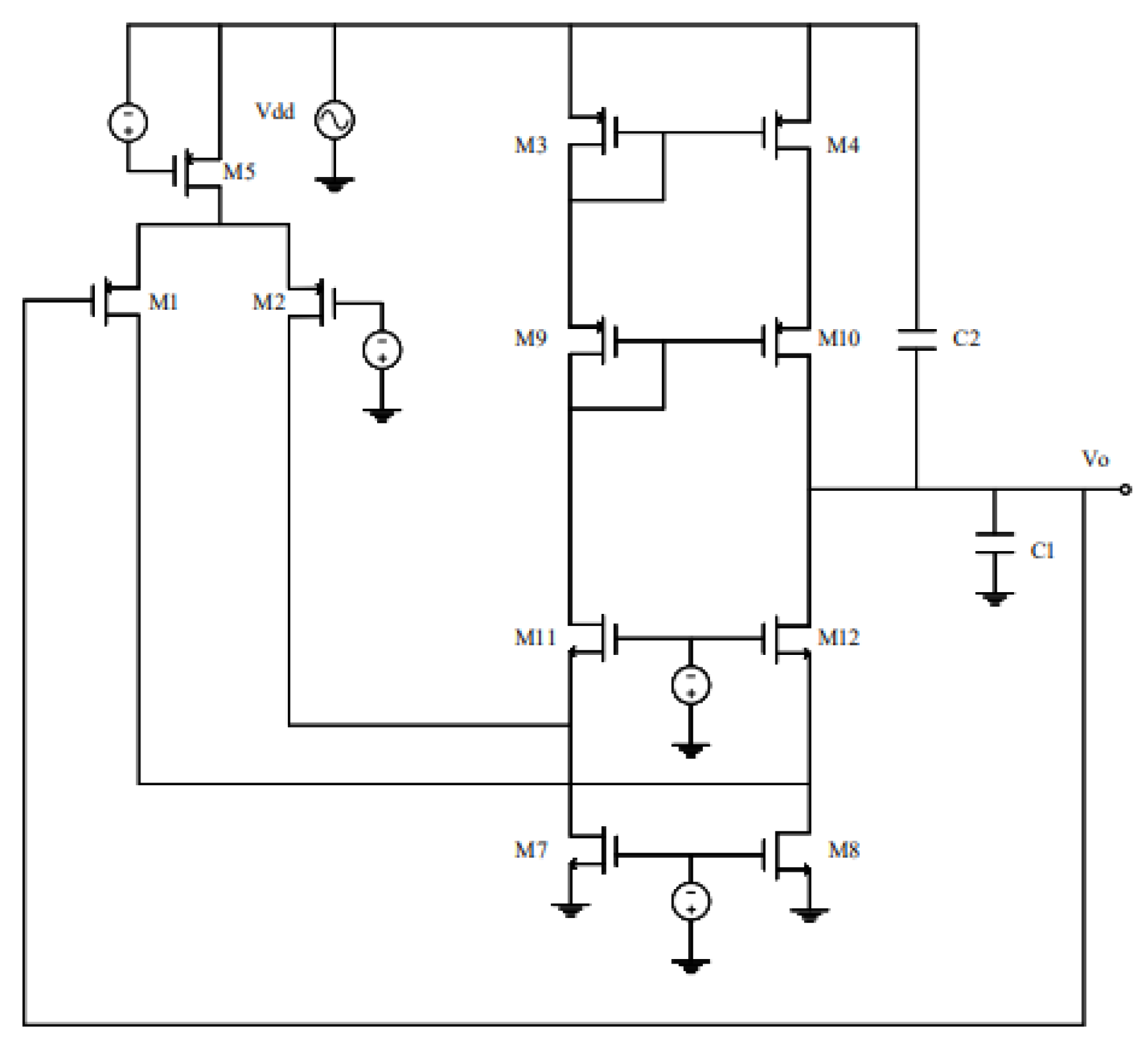

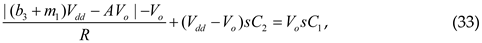

2.2.1. P-Input Folded Cascode Op-Amps

which simplifies to:

which simplifies to:- (a)

- Increasing gm1 directly raises the DC PSRR value.

- (b)

- Reducing the parasitic capacitance C2 improves the frequency response.

- (c)

- The dominant pole of the op-amp is associated with its output node. Consequently, augmenting C1 shifts this pole closer to the origin, which is advantageous for enhancing both system stability and the frequency response of the PSRR. However, it is crucial to strike a balance with the required bandwidth; one cannot indiscriminately reduce the bandwidth without considering the overall system performance requirements.

2.2.1. N-Input Folded Cascode Op-Amps

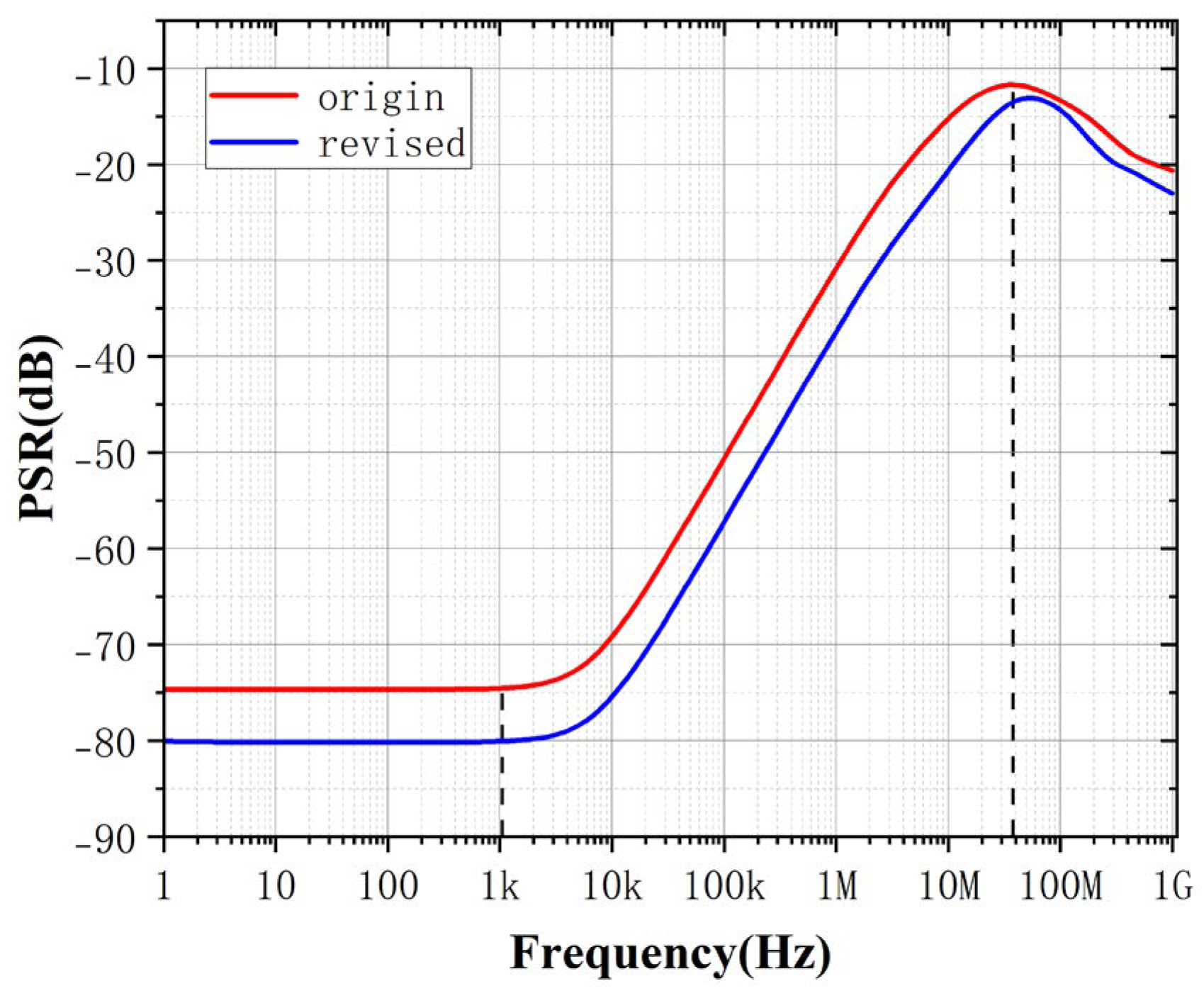

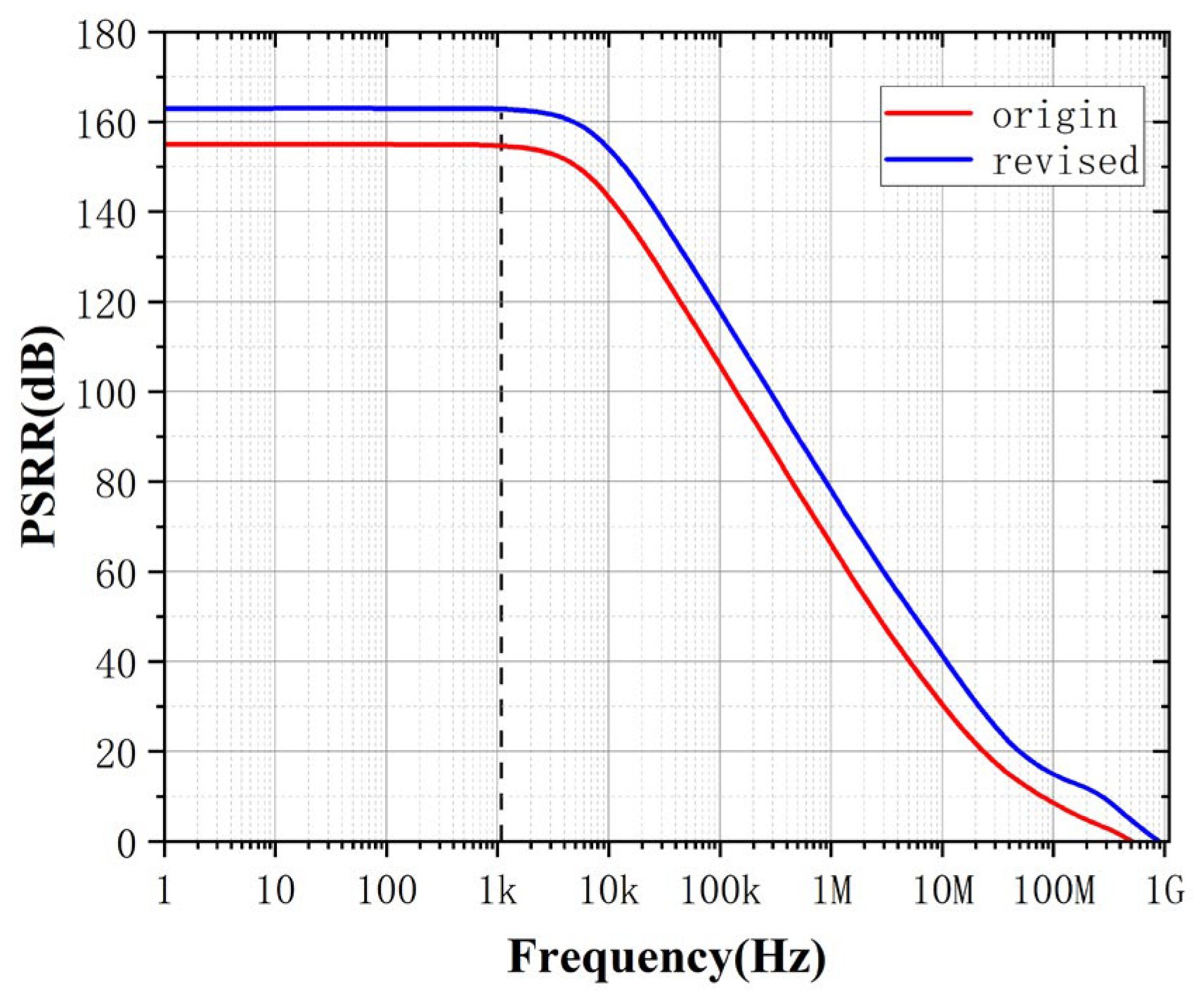

3. Results and Discussions

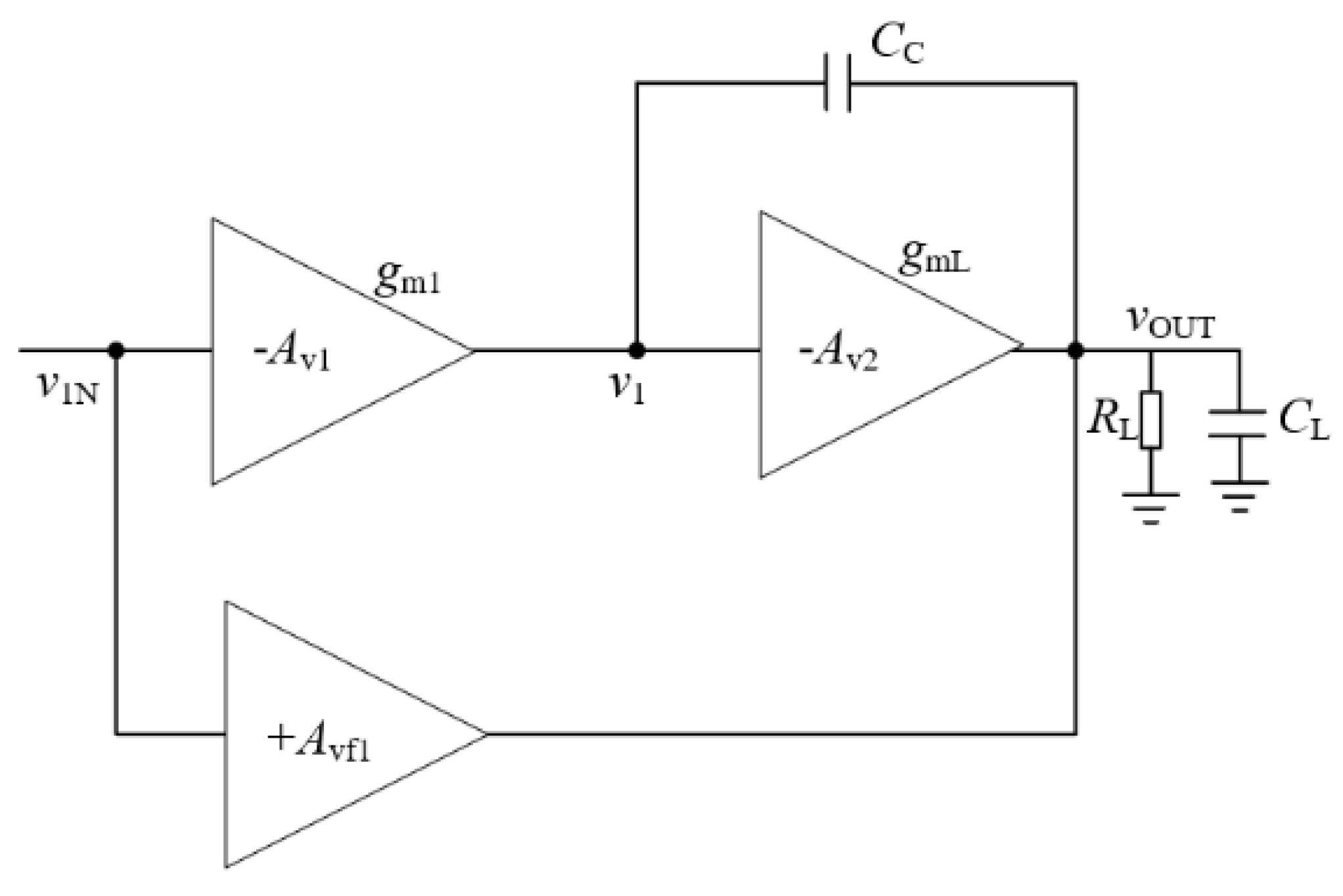

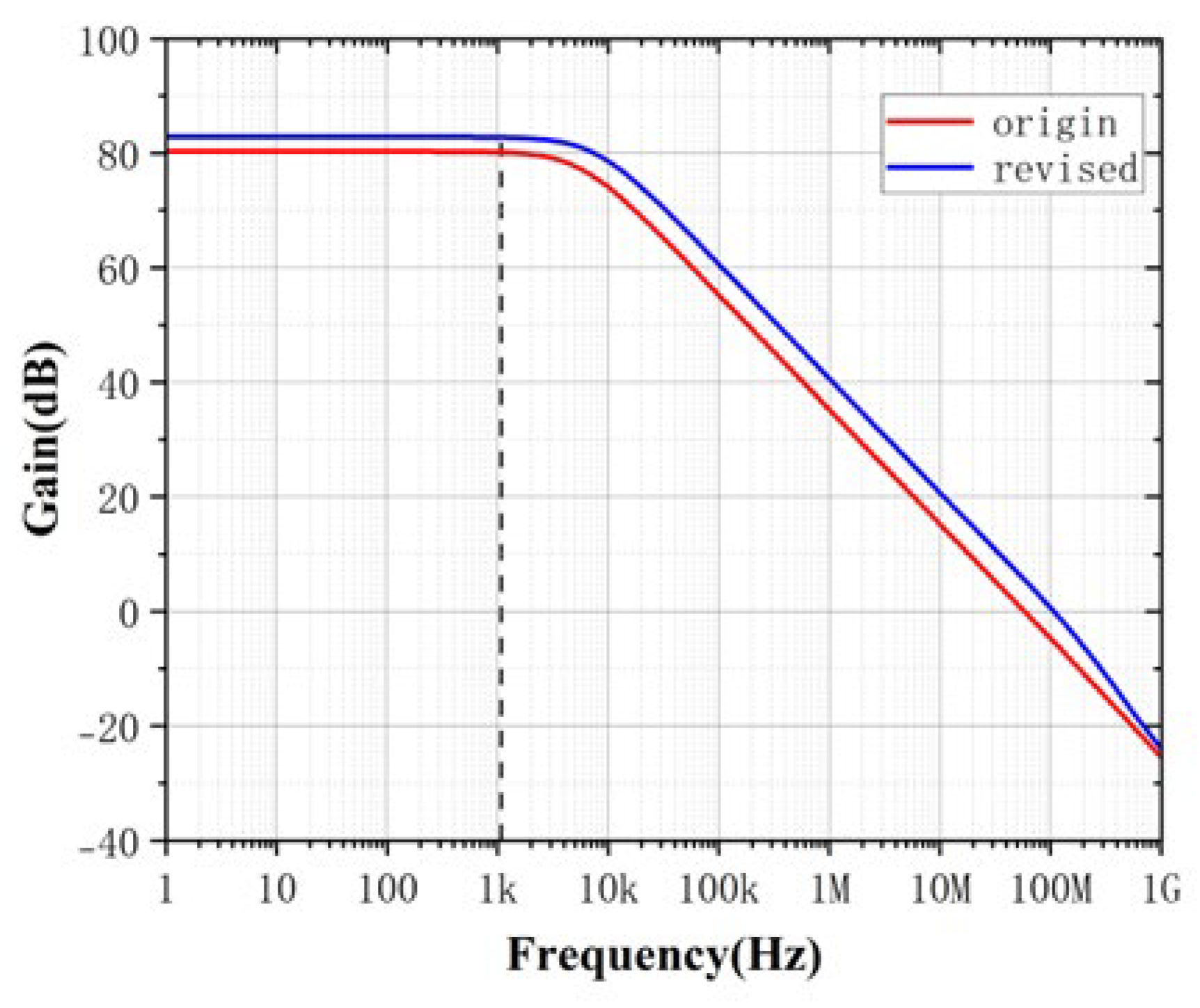

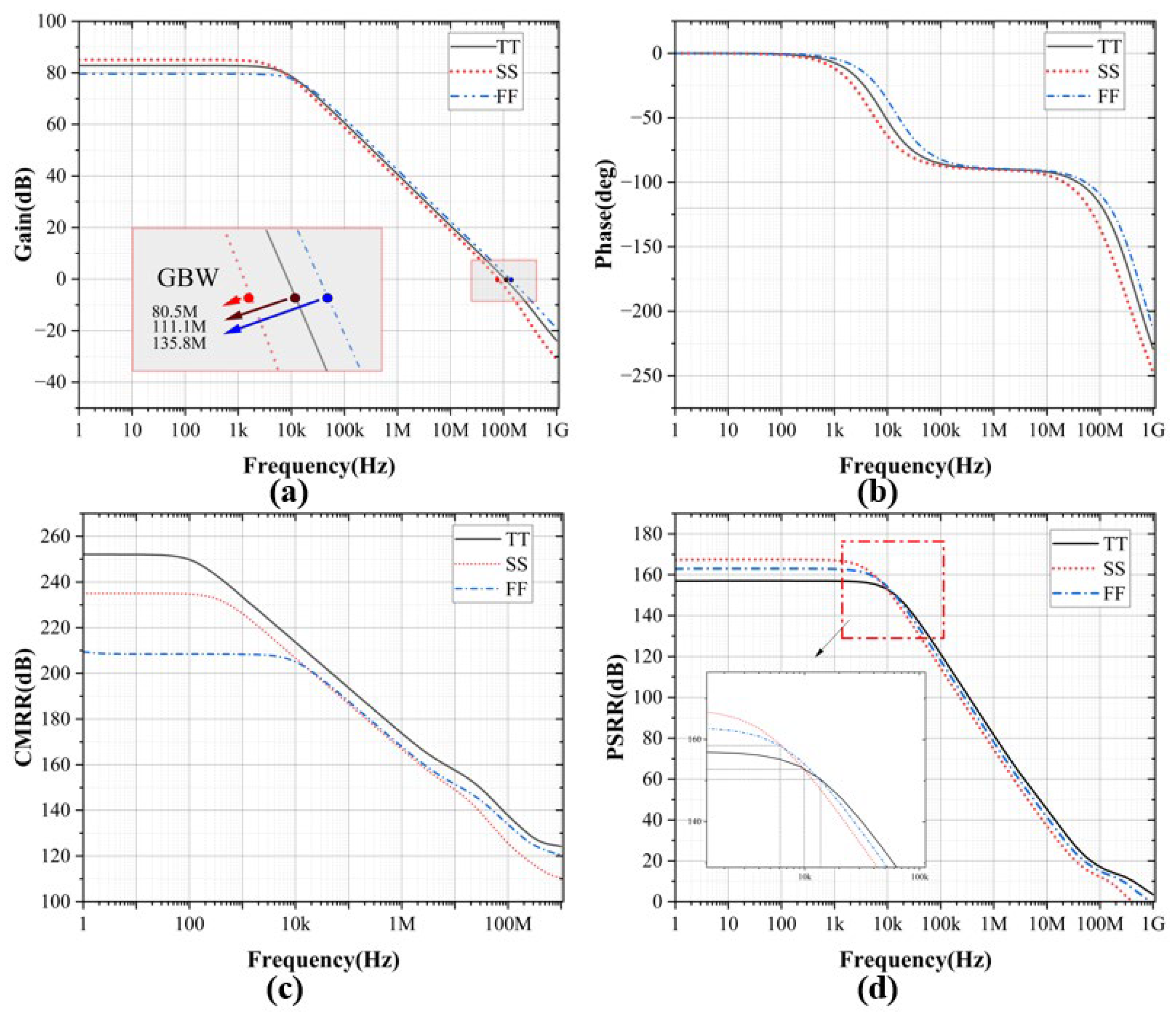

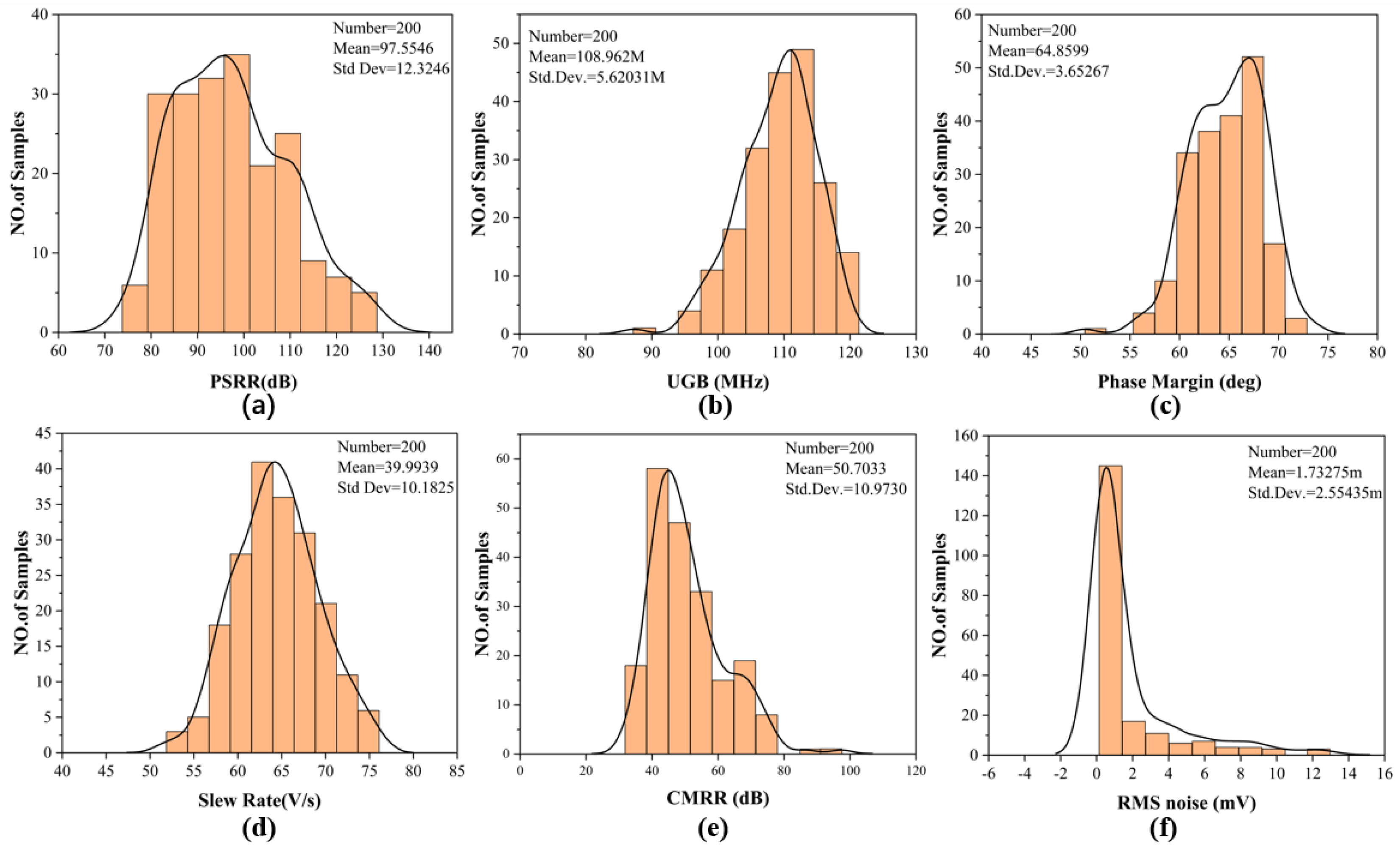

- (a)

- Gain Expression

- (b) Transfer Function Optimization

- (c) PSRR

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- J. S. Kim, S. Ha, H. Jeong and J. Roh, "A High-PSRR NMOS LDO Regulator With Intrinsic Gain-Tracking Ripple Cancellation Technique," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 71, no. 11, pp. 4951-4960, Nov. 2024. [CrossRef]

- I. Colli-Menchi, J. Torres and E. Sánchez-Sinencio, "A Feed-Forward Power-Supply Noise Cancellation Technique for Single-Ended Class-D Audio Amplifiers," in IEEE Journal of Solid-State Circuits, vol. 49, no. 3, pp. 718-728, March 2014. [CrossRef]

- C-C. Chiu et al., "A 0.6 V Resistance-Locked Loop Embedded Digital Low Dropout Regulator in 40 nm CMOS With 80.5% Power Supply Rejection Improvement," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 62, no. 1, pp. 59-69, Jan. 2015. [CrossRef]

- Y. Choi, W. Tak, Y. Yoon, J. Roh, S. Kwon and J. Koh, "A 0.018% THD+N, 88-dB PSRR PWM Class-D Amplifier for Direct Battery Hookup," in IEEE Journal of Solid-State Circuits, vol. 47, no. 2, pp. 454-463, Feb. 2012. [CrossRef]

- K. A. I. Halonen, W. M. C. Sansen and M. Steyaert, "A micropower fourth-order elliptical switched-capacitor low-pass filter," in IEEE Journal of Solid-State Circuits, vol. 22, no. 2, pp. 164-173, April 1987. [CrossRef]

- Razavi, "Design of Analog CMOS Integrated Circuits," 2nd ed., Xi'an Jiaotong University Press, 2009, pp. 358–400.

- P. E. Allen, D. R. Holberg, "CMOS Analog Circuit Design," 2nd ed., Beijing: Publishing House of Electronics Industry, 2005, pp. 232–234.

- P. R. Gray, P. J. Hurst, S. H. Lewis, and R. G. Meyer, Analysis and Design of Analog Integrated Circuits, 4th ed., Beijing: Higher Education Press, 2005, pp. 410–415.

- Bhar S, Mondal A, Srimani S, et al. A low power driver amplifier for Fully Differential ADC[C]//2019 2nd International Symposium on Devices, Circuits and Systems (ISDCS). IEEE, 2019: 1-6. [CrossRef]

- Yang and T. Lehmann, ‘‘High gain operational amplifiers in 22 nm CMOS,’’ in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), May 2019, pp. 1–5. [CrossRef]

- S. Chakraborty, A. Pandey, and V. Nath, ‘‘Ultra high gain CMOS op-amp design using self-cascoding and positive feedback,’’ Microsyst. Technol., vol. 23, no. 3, pp. 541–552, Mar. 2017. [CrossRef]

- Yongzhen Chen, Chixiao Chen, Qiang Zhang, Fan Ye and Junyan Ren, ”A 12-bit 200-MS/s sample-and-hold amplifier with a hybrid Miller-Feedforward compensation technique,” 2013 IEEE 10th International Conference on ASIC, 2013, pp. 1-4. [CrossRef]

| Parameters | |

| Supply Volatge(V) | 1.8V |

| Process | 180nm |

| Gain(dB) | >80dB |

| Phase Margin(deg) | >55 |

| GBW(MHz) | >100 |

| SR(V/us) | >80 |

| Power(mW) | <1 |

| CMRR(dB) | - |

| PSRR(dB) | >100 |

| CL(F) | 2p |

| FOM* | - |

| Parameters | Designed | This Work | 8 | 9 | 10 | 11 |

| Supply Voltage (V) | 1.8V | 1.8V | 1.8V | 1.8V | 2V | 1.2V |

| Process | 180nm | 180nm | 180nm | 180nm | 45nm | 65nm |

| Gain (dB) | >80dB | 83dB | 67dB | 66dB | 141 | 90.17 |

| Phase Margin (deg) | >55 | 61.4 | 54 | 58.5 | 60 | 88.84 |

| GBW (MHz) | <100 | 111.1 | 111.8 | 60 | 101 | 1410 |

| SR (V/us) | >80 | 100 | 32.30 | 95 | 57.7 | - |

| Power (mW) | <1 | 0.95 | 1.37 | 0.55 | 1.2 | 47.25 |

| CMRR (dB) | - | 252 | 127 | 136 | - | |

| PSRR (dB) | >100 | 131 | 68 | 83.2 | 57/67 | - |

| CL (F) | 2p | 2p | 2p | 2.3p | 1p | 4p |

| FOM* | - | 233.8 | 163.2 | 240 | 80 | 119.3 |

| Components | W/L(um) |

| M0 | 9.9/1 |

| M1 M2 | 123/1 |

| M3 M4 | 32/3 |

| M5 M6 | 15/1 |

| M7 M8 | 10/0.6 |

| M9a M9b M10a M10b | 2.05/0.945 |

| M11 M12 | 30/1 |

| M13 M14 | 4.9/3.5 |

| M15 | 10/1 |

| M16 M17 M20 M21 | 6/0.18 |

| M18 M19 | 1/1 |

| M22 M23 | 1/4 |

| M25 | 12/1 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).