Submitted:

08 January 2025

Posted:

08 January 2025

You are already at the latest version

Abstract

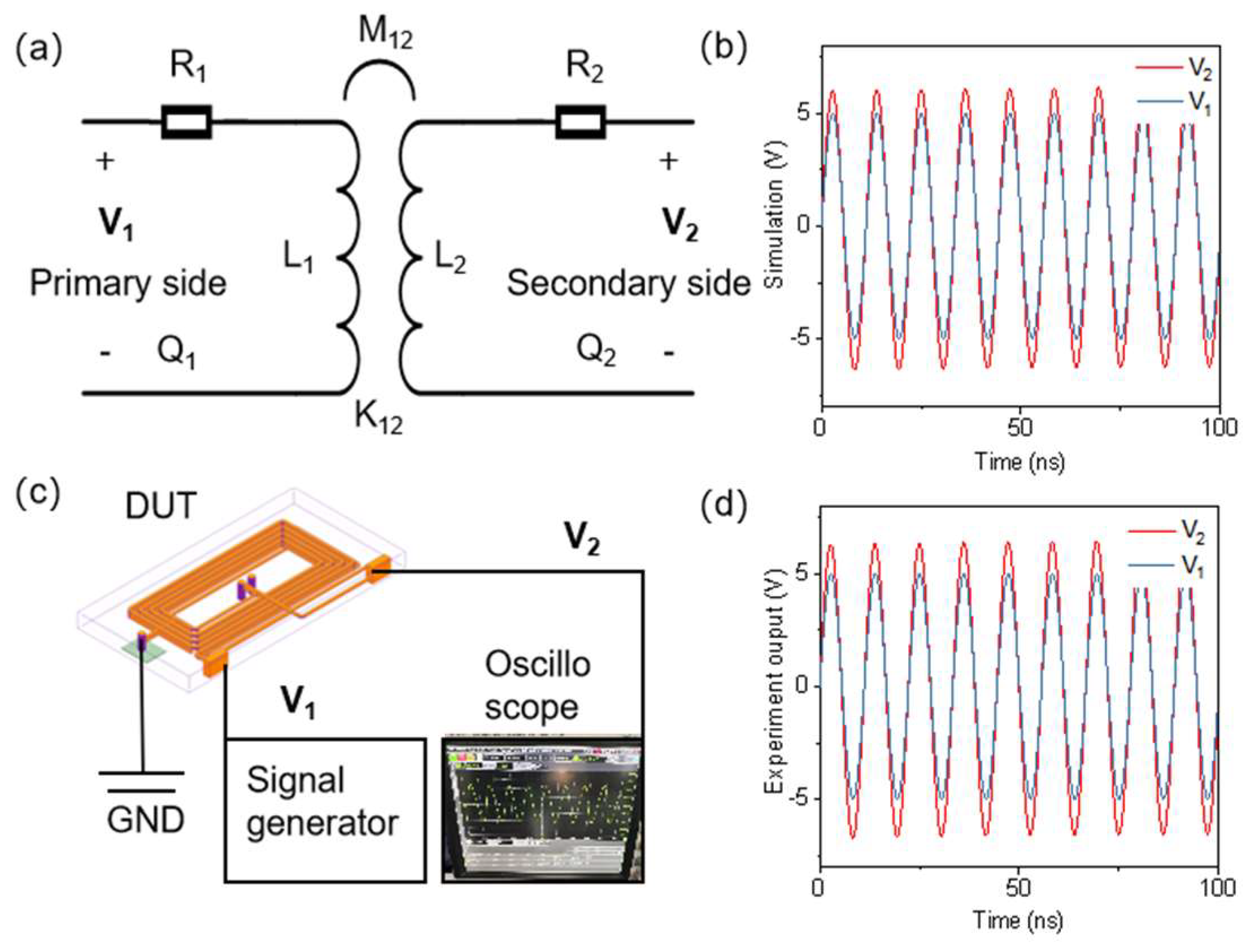

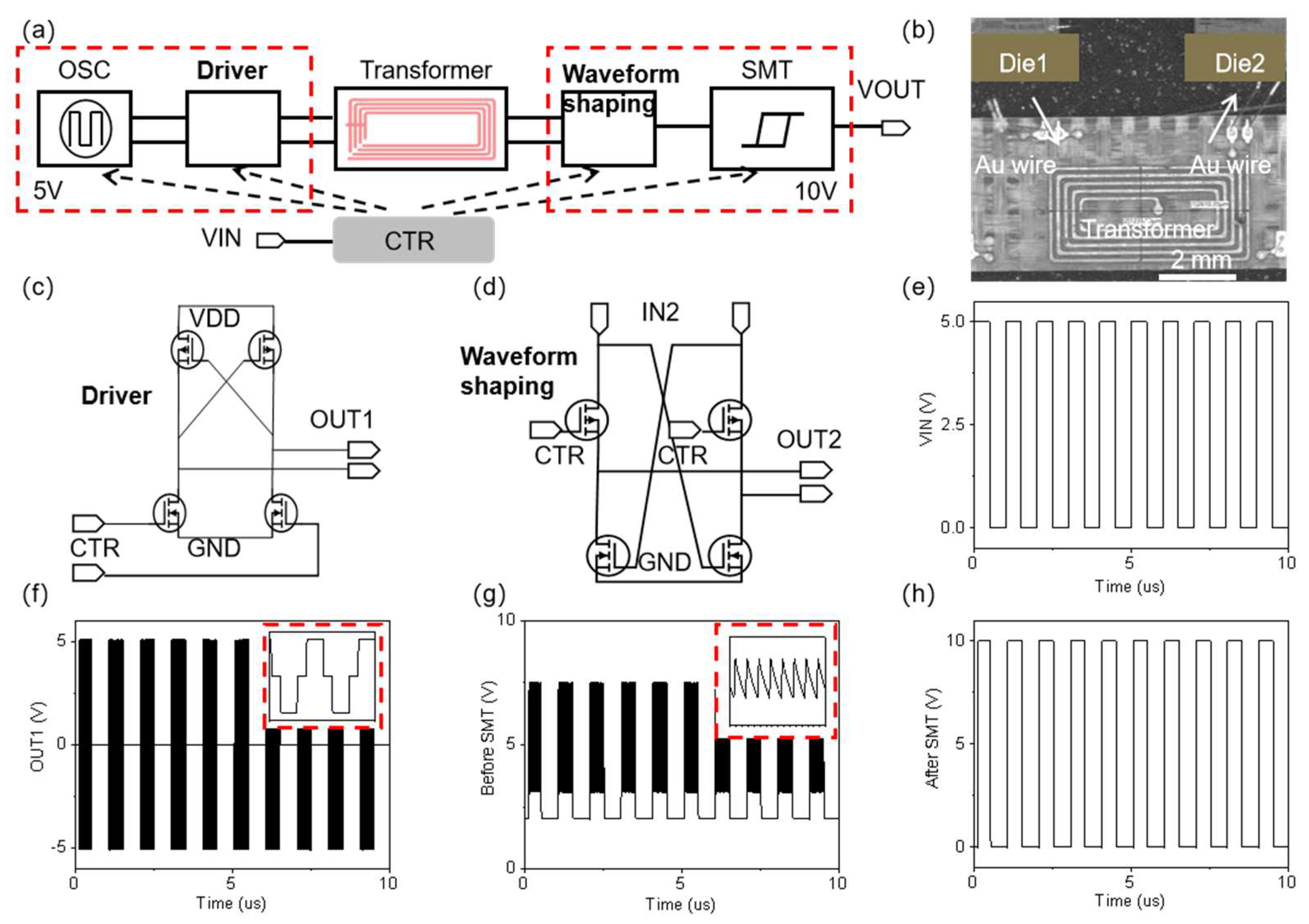

Isolation driver chips are widely used for reliable communication between low and high voltage levels, with on-chip transformers serving as the core devices for magnetic isolation. In this study, we designed, simulated, and tested an on-chip transformer that can be manufactured using PCB technology. This transformer uses copper as the conductive material and FR4 as the dielectric, theoretically achieving an insulation level of up to 3KV, making it suitable for mass production and showing significant industrial application potential. Based on this on-chip transformer, we designed corresponding encoding and decoding circuits and implemented the circuit structure through System in Package (SIP). Simulation results indicate that this isolation driver chip can reliably support communication across different voltage levels.

Keywords:

1. Introduction

2. Design and Fabrication

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Geng, C.; Luo, C.; Zhang, Z.; Wang, X.; Liu, Y.; Sun, B. Design and optimization of on chip thick plated copper transformers for galvanic isolated DC DC converter achieving up to 38.9% peak efficiency. Integr. 2023, 90, 146–156. [Google Scholar] [CrossRef]

- Derkaoui, M.; Benhadda, Y.; Chaabene, G.; Spiteri, P. On chip GaN planar transformer design for highly integrated RF systems. J. Circuits, Syst. Comput. 2023, 32. [Google Scholar] [CrossRef]

- Elalfy, D.A.; Gouda, E.; Kotb, M.F.; Bures, V.; Sedhom, B.E. Comprehensive review of energy storage systems technologies, objectives, challenges, and future trends. Energy Strategy Rev. 2024, 54. [Google Scholar] [CrossRef]

- SotoMarchena, D.; Barrero, F.; Colodro, F.; Arahal, M.R.; Mora, J.L. On site calibration of an electric drive: a case study using a multiphase system. Sens. 2023, 23. [Google Scholar] [CrossRef]

- Guo, Z.; Chu, L.; Hou, Z.; Wang, Y.; Hu, J.; Sun, W. A dual distribution control method for multi power components energy output of 4WD electric vehicles. Sens. 2022, 22. [Google Scholar] [CrossRef] [PubMed]

- Chen, C.; Pan, P.; Gu, J.; Li, X. A high voltage isolated MEMS quadsolenoid transformer with specific insulation barriers for miniaturized galvanically isolated power applications. Micromachines 2024, 15. [Google Scholar] [CrossRef]

- Mirfakhraei, S.S.; Audet, Y.; Hassan, A.; Sawan, M. A small footprint digital isolator based on CMOS integrated hall effect sensor. IEEE Sens. J. 2022, 22, 412–418. [Google Scholar] [CrossRef]

- Lv, G.; Ding, Y.; Fang, X.; Li, L.; Bai, F.; Sin, J.K.O.; Wu, R. A novel conformal thick oxide technology for on chip high voltage isolation. IEEE Trans. Compon. Packag. Manuf. Technol. 2022, 12, 704–706. [Google Scholar] [CrossRef]

- Mirfakhraei, S.S.; Audet, Y.; Hassan, A.; Sawan, M. A galvanic isolated amplifier based on CMOS integrated hall effect sensors. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 1388–1397. [Google Scholar] [CrossRef]

- Derkaoui, M.; Benhadda, Y.; Hamid, A.; Temmar, A. Design and modeling of octagonal planar inductor and transformer in monolithic technology for RF systems. J. Electr. Eng. Technol. 2021, 16, 1481–1493. [Google Scholar] [CrossRef]

- Altoobaji, I.; Ali, M.; Hassan, A.; Nabavi, M.; Audet, Y.; Lakhssassi, A.; Ieee. A fully integrated on chip inductive digital isolator: design investigation and simulation. In Proceedings of IEEE MWSCAS, 2020; pp. 868-871.

- Massaro, A. Artificial intelligence signal control in electronic optocoupler circuits addressed on industry 5.0 digital twin. Electron. 2024, 13. [Google Scholar] [CrossRef]

- Dwivedi, A.K.; Agarwal, L.; Bajpai, T.; Tripathi, S. Er doped ZnO/SnS2 PEDOT:PSS double heterostructure photodetector and Its application as optocoupler. IEEE Sens. J. 2024, 24, 25609–25616. [Google Scholar] [CrossRef]

- Pan, D.; Xiong, Z.; Lu, Q.; Miao, F.; Wu, L.; Cheng, L. A 250 Mb/s on chip capacitive digital isolator with adaptive frequency control. IEEE Solid-State Circuits Lett. 2024, 7, 231–234. [Google Scholar] [CrossRef]

- Altoobaji, I.; Hassan, A.; Ali, M.; Audet, Y.; Lakhssassi, A. A low power 0.68 Gbps data communication system for capacitive digital isolator with 1.9 ns propagation delay. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2024, 32, 952–956. [Google Scholar] [CrossRef]

- Wu, R.X.; Chen, J.L.; Liao, N.T.; Fang, X.M.; Ieee. On chip transformers with shielding structures for high dV/dt immunity isolated gate drive. In Proceedings of IEEE ECCE.

- Wang, N.N.; Miftakhutdinov, R.; Kulkarni, S.; O'Mathuna, C. High efficiency on Si integrated microtransformers for isolated power conversion applications. IEEE Trans. Power Electron. 2015, 30, 5746–5754. [Google Scholar] [CrossRef]

- Peng, L.; Wu, R.; Fang, X.; Toyoda, Y.; Akahane, M.; Yamaji, M.; Sumida, H.; Sin, J.K.O.; Ieee. A novel 3D TSV transformer technology for digital isolator gate driver applications. In Proceedings of ISPSD, 2013; pp. 69-72.

- Bajwa, R.; Yapici, M.K. Integrated on chip transformers: recent progress in the design, layout, modeling and fabrication. Sens. 2019, 19. [Google Scholar] [CrossRef] [PubMed]

- Macrelli, E. Roll up for three dimensional transformers. Nat. Electron. 2018, 1, 270–271. [Google Scholar] [CrossRef]

- Wu, R.X.; Chen, J.L.; Fang, X.M. A novel on chip transformer with patterned ground shield for high common mode transient immunity isolated signal transfer. IEEE Electron Device Lett. 2018, 39, 1712–1715. [Google Scholar] [CrossRef]

- Tiemeijer, L.F.; Pijper, R.M.T.; Andrei, C.; Grenados, E. Analysis, design, modeling, and characterization of low loss scalable on chip transformers. IEEE Trans. Microwave Theory Tech. 2013, 61, 2545–2557. [Google Scholar] [CrossRef]

- Huang, W.; Zhou, J.; Froeter, P.J.; Walsh, K.; Liu, S.; Kraman, M.D.; Li, M.; Michaels, J.A.; Sievers, D.J.; Gong, S.; et al. Three dimensional radio frequency transformers based on a self rolled up membrane platform. Nat. Electron. 2018, 1, 305–313. [Google Scholar] [CrossRef]

- Zhu, K.; Chen, H.; Li, S.; Sun, C.; Liu, F. An RF on chip transformer with Fe3O4 GO nanocomposite film. IEEE Trans. Magn. 2021, 57. [Google Scholar] [CrossRef]

- Kaeriyama, S.; Uchida, S.; Furumiya, M.; Okada, M.; Maeda, T.; Mizuno, M. A 2.5 kV isolation 35 kV/us CMR 250 Mbps digital isolator in standard CMOS with a small transformer driving technique. IEEE J. Solid-State Circuits 2012, 47, 435–443. [Google Scholar] [CrossRef]

- Derkaoui, M.; Larbi, A.; Benhadda, Y. Comparative study of different topologies of monolithic on chip planar transformer for optical VCSEL driver. Electr. Power Compon. Syst. 2024, 52, 959–970. [Google Scholar] [CrossRef]

- Wang, N.; Chen, C.; Chen, P.; Gu, J.; Pan, P.; Han, R.; Liu, M.; Li, X. MEMS casting fabricated chip style 3D metal solenoidal transformers towards integrated power supply. Micromachines 2022, 13. [Google Scholar] [CrossRef] [PubMed]

- Chen, C.; Pan, P.; Lyu, D.; Gu, J.; Liu, M.; Li, X. Wafer level fabricated tight coupling dual solenoid transformer chips with watt scale power transfer. IEEE Trans. Power Electron. 2023, 38, 5118–5127. [Google Scholar] [CrossRef]

- Wu, H.; Lekas, M.; Davies, R.; Shepard, K.L.; Sturcken, N. Integrated transformers with magnetic thin films. IEEE Trans. Magn. 2016, 52. [Google Scholar] [CrossRef]

- Bansal, U.; Garg, A.; Shalini, D. A review on recently reported grounded CMOS active inductors. Wireless Pers. Commun. 2023, 133, 913–949. [Google Scholar] [CrossRef]

- Hamid, S.S.; Mariappan, S.; Rajendran, J.; Rawat, A.S.; Rhaffor, N.A.; Kumar, N.; Nathan, A.; Yarman, B.S. A state of the art review on CMOS radio frequency power amplifiers for wireless communication systems. Micromachines 2023, 14. [Google Scholar] [CrossRef]

- Li, X.; Ni, Z.; Gu, L.; Wu, Z.; Yang, C. Micromachined high performance RF passives in CMOS substrate. J. Micromech. Microeng. 2016, 26. [Google Scholar] [CrossRef]

- Yang, R.; Hou, H.; Wang, Y.; Fu, L. Micro magnetofluidics in microfluidic systems: a review. Sens. Actuators, B 2016, 224, 1–15. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).