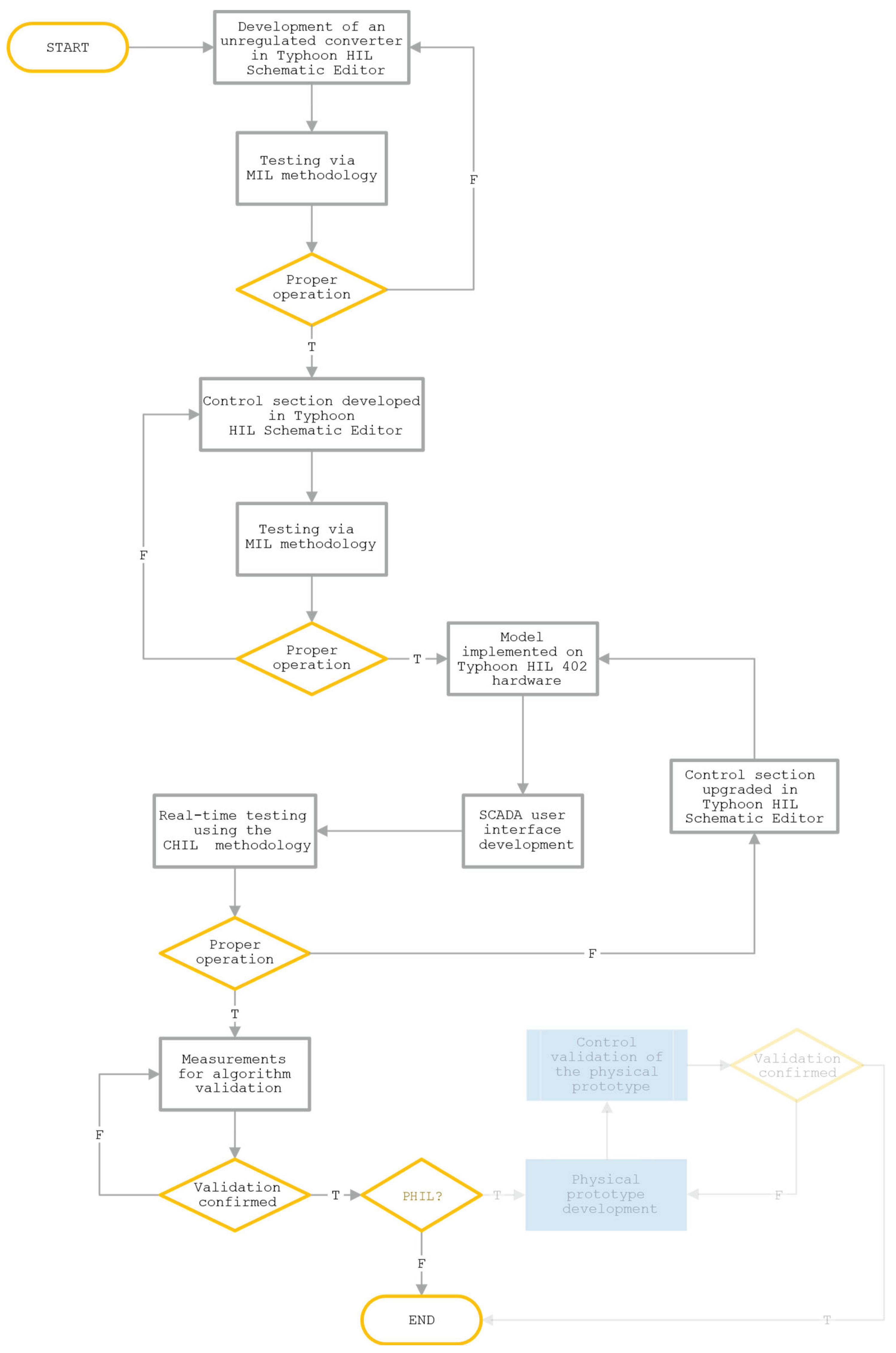

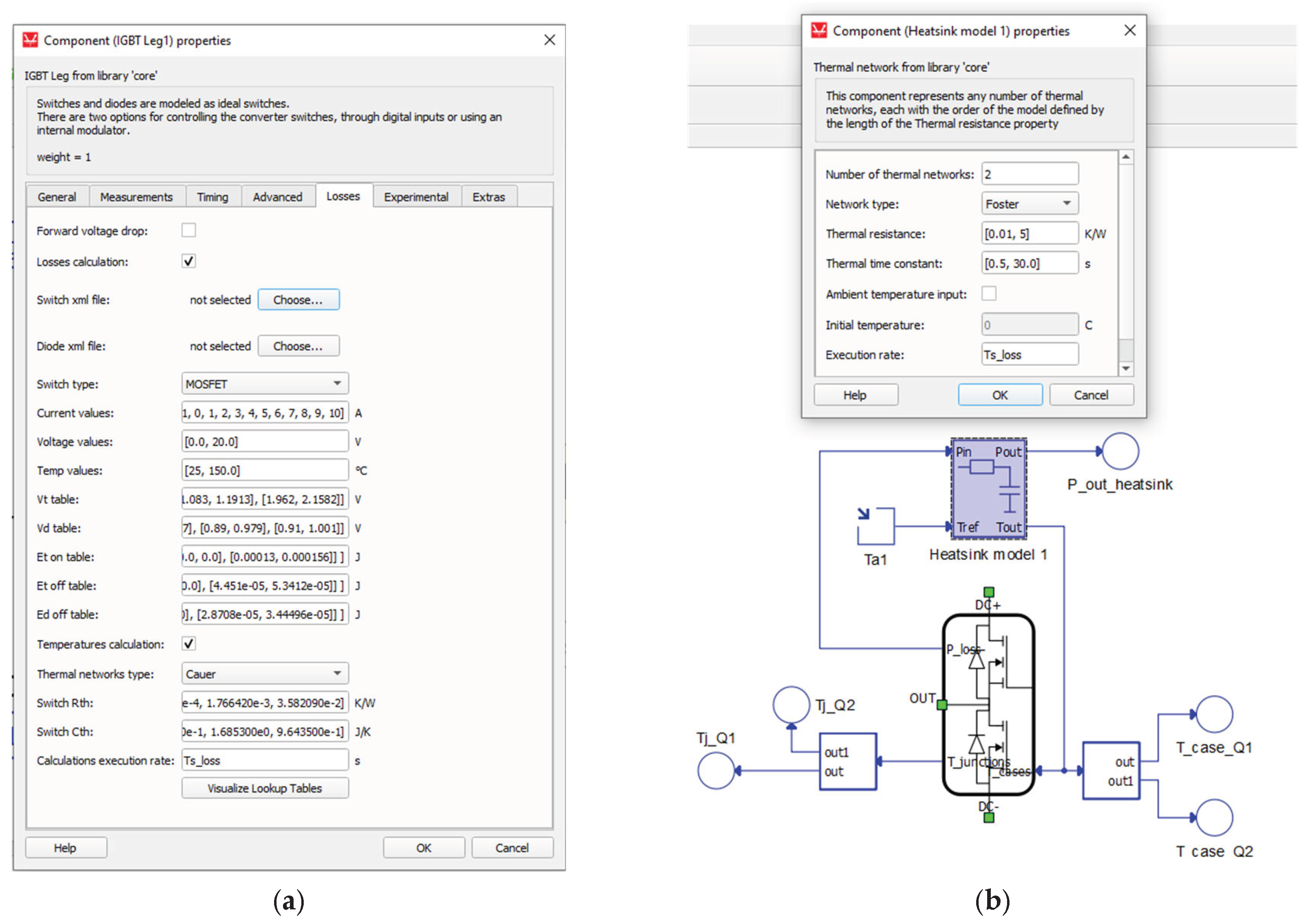

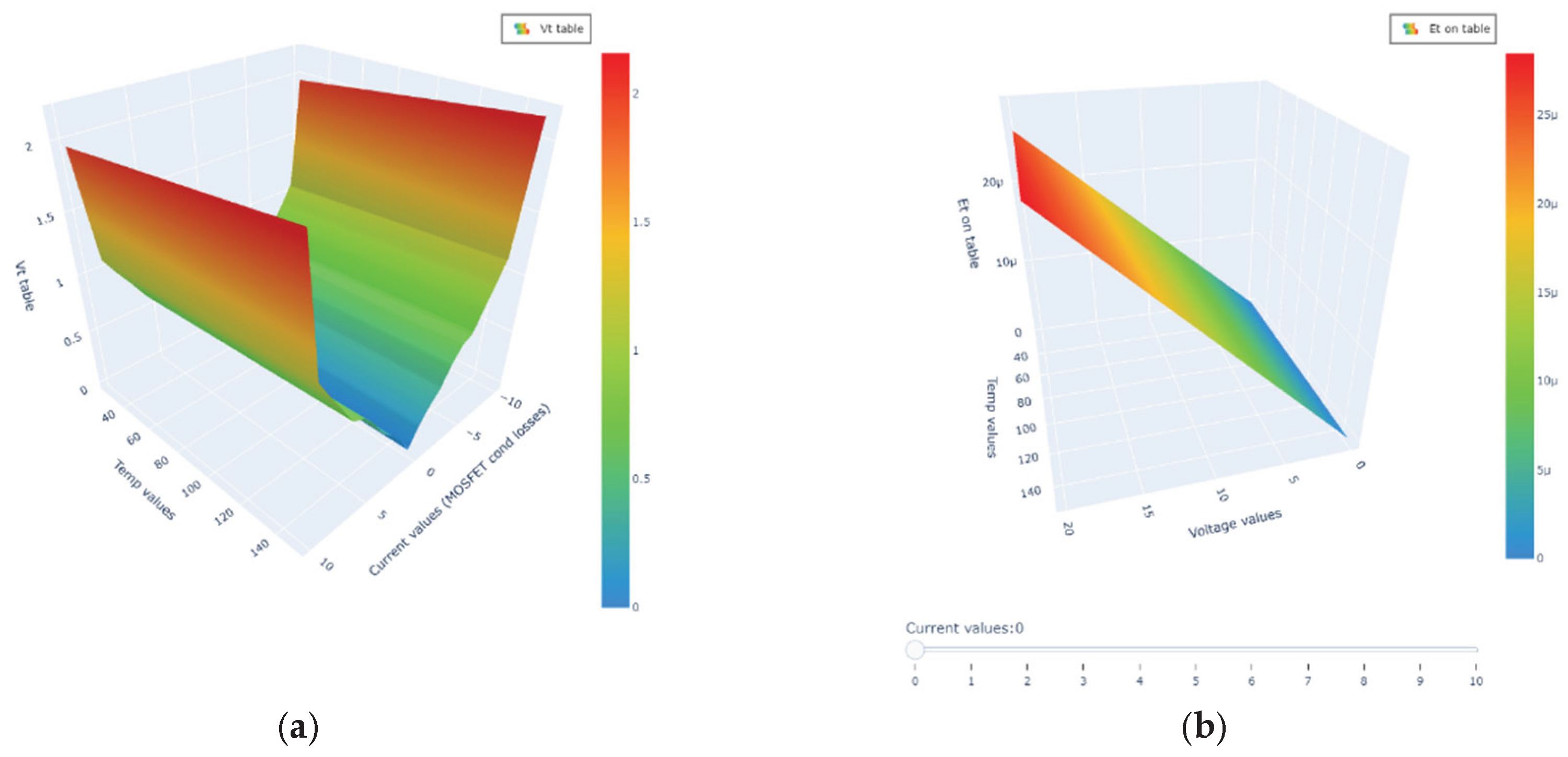

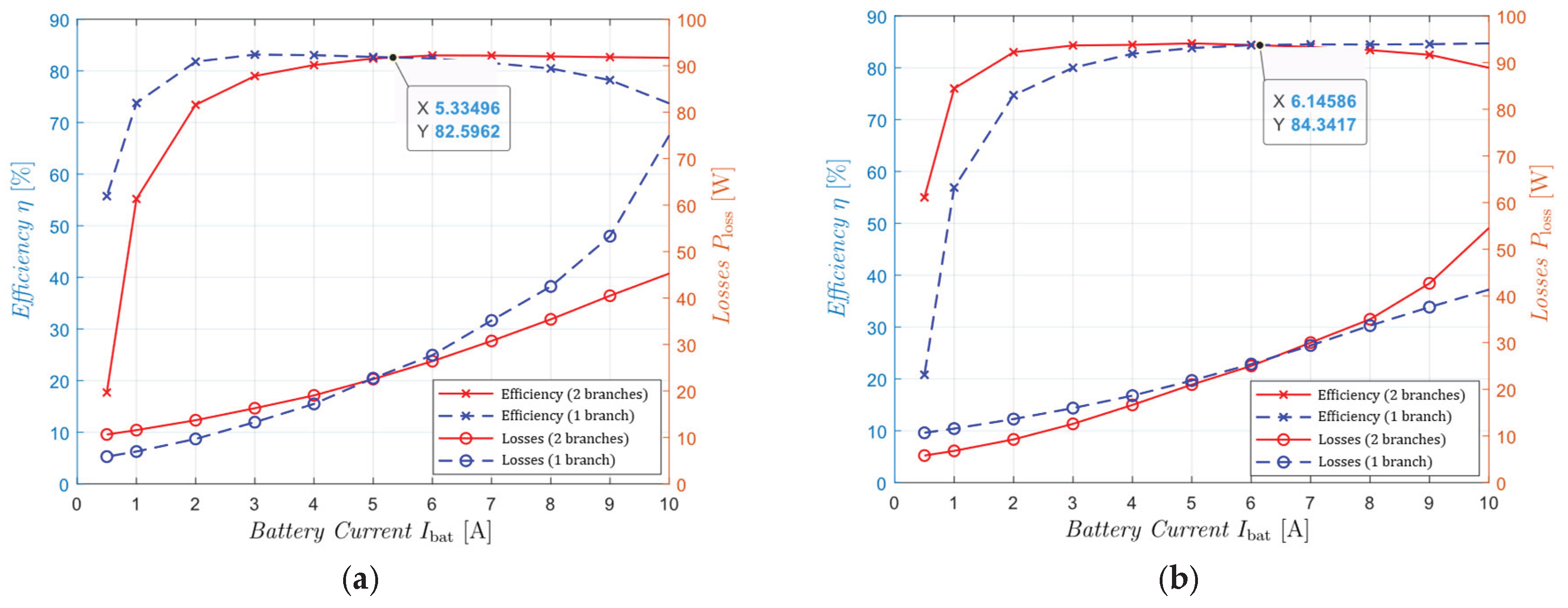

5.1. Validation Results in Boost Operation

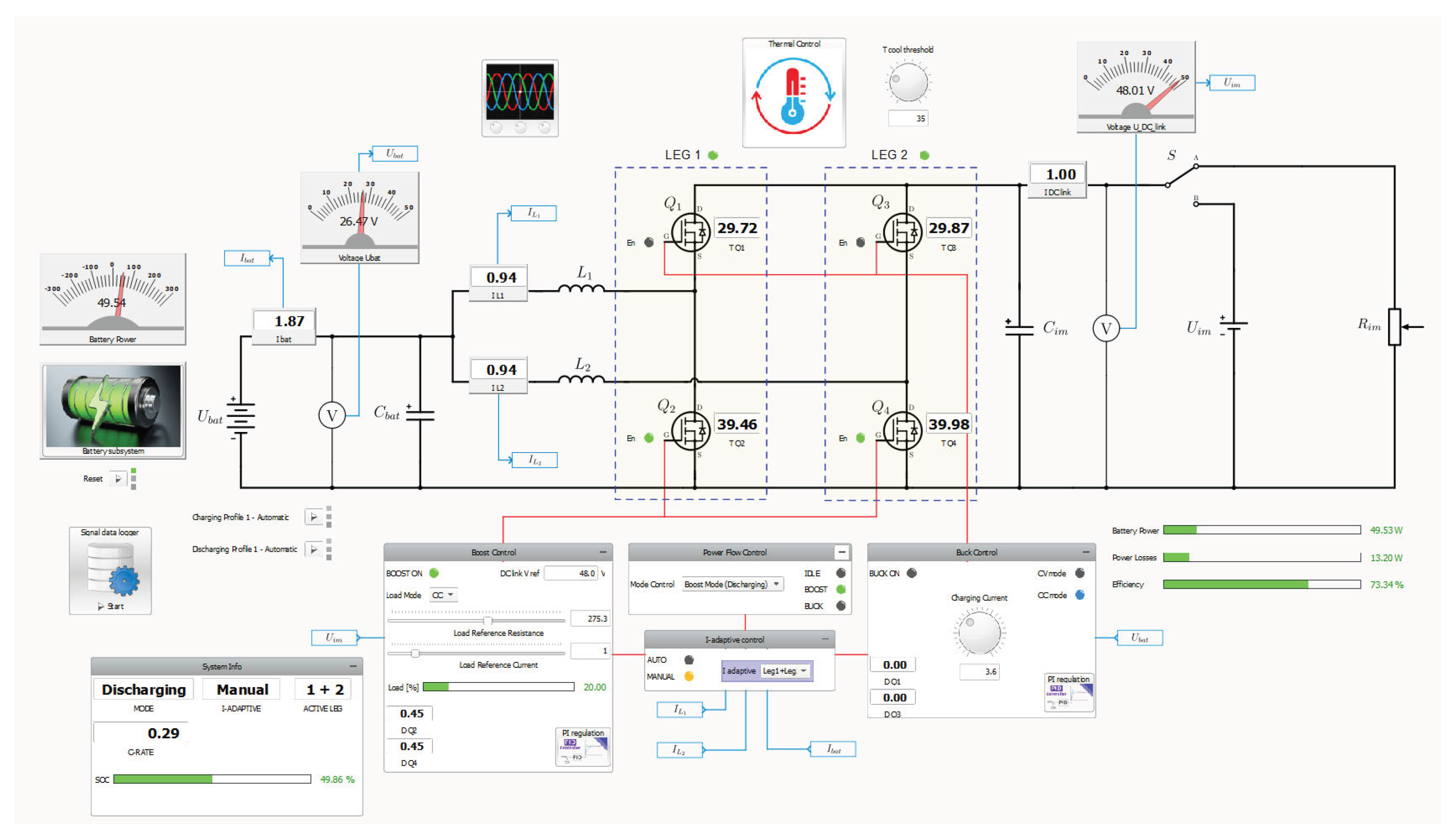

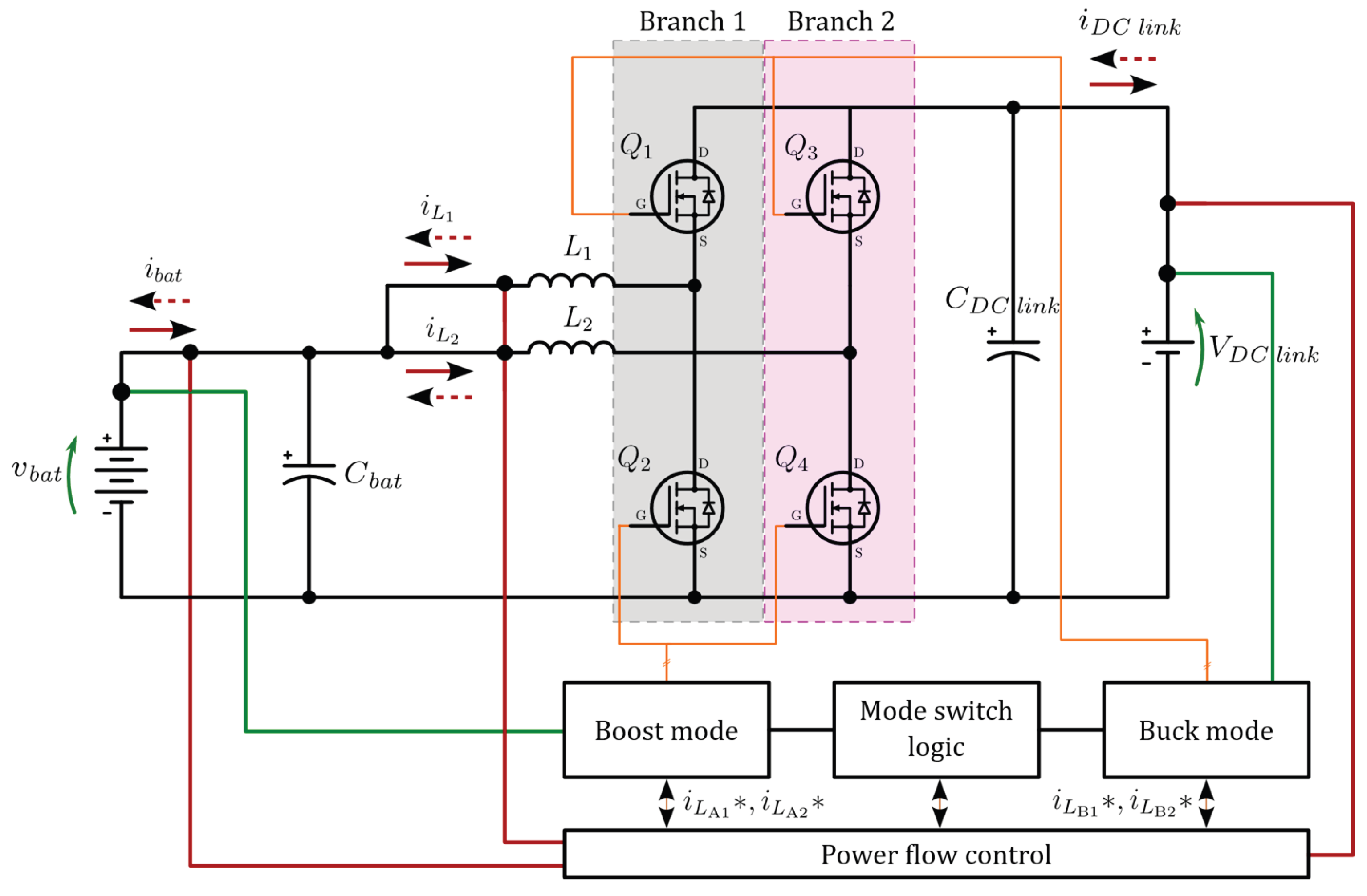

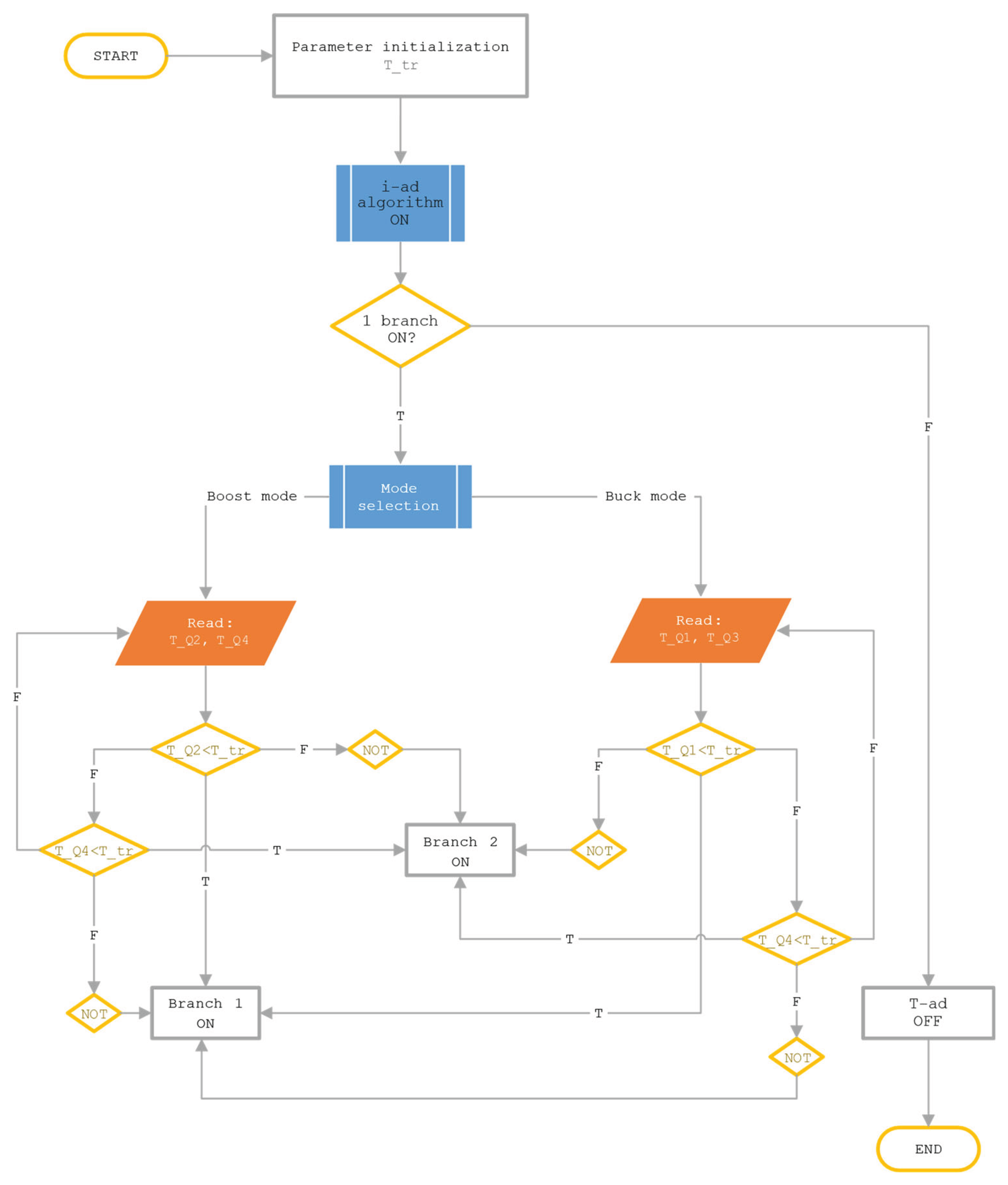

The system operates in a fully automated manner, including real-time data acquisition, with particular emphasis on monitoring the temperatures of individual power transistors. The primary objective is to validate the effectiveness of the proposed branch rotation control strategy driven by transistor operating temperature management and to evaluate its influence on the resulting thermal profiles. Special attention is given to the assessment of both average and maximum transistor temperatures, as these metrics directly reflect thermal stress and reliability implications of the control approach.

The measurement sets defined in

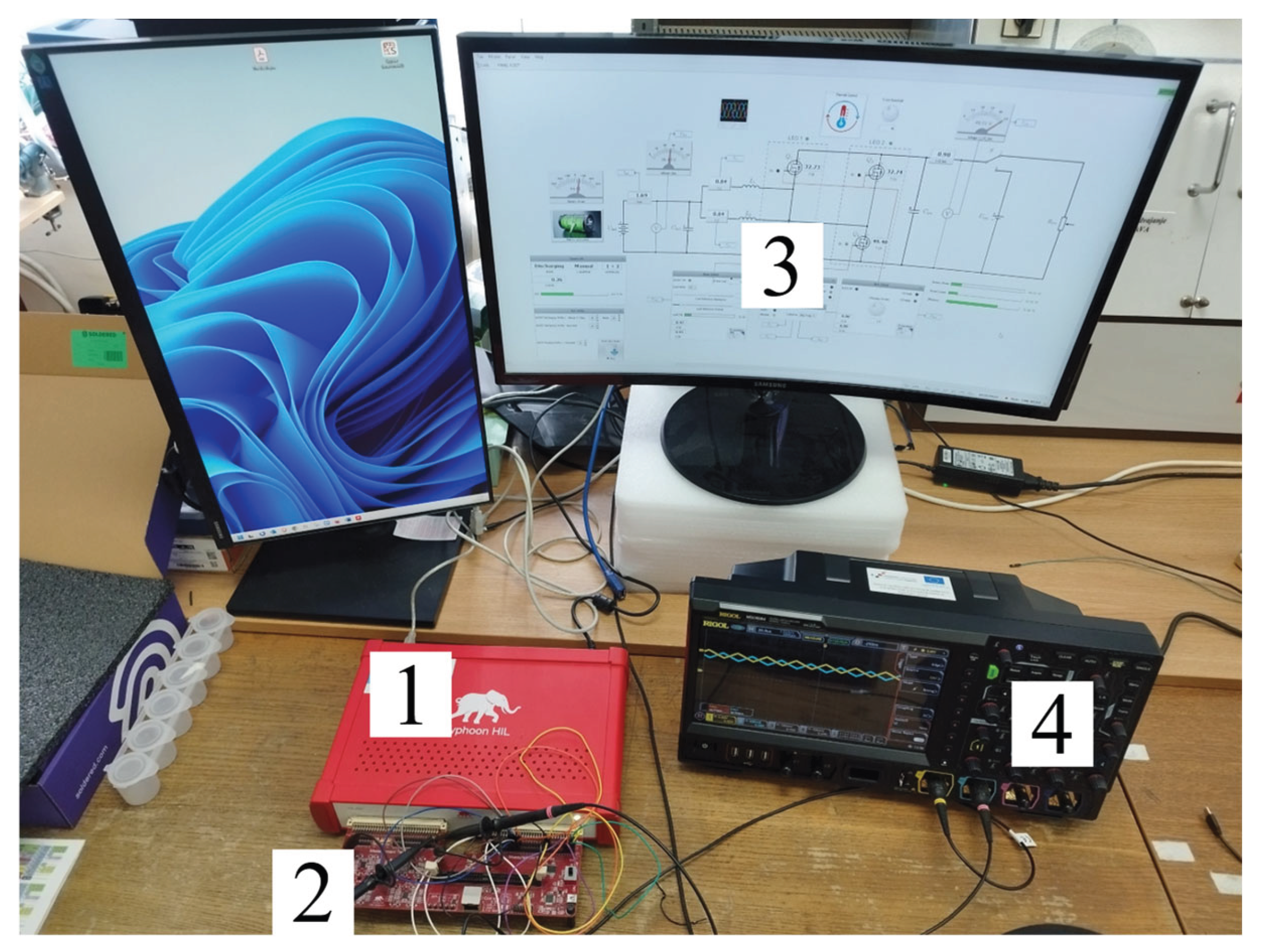

Table 5 are executed as real-time CHIL simulations. In this framework, the duration of each experiment is governed by the battery charging and discharging intervals, which are determined by the battery

ranges specified in

Table 5. The corresponding experimental results are presented in

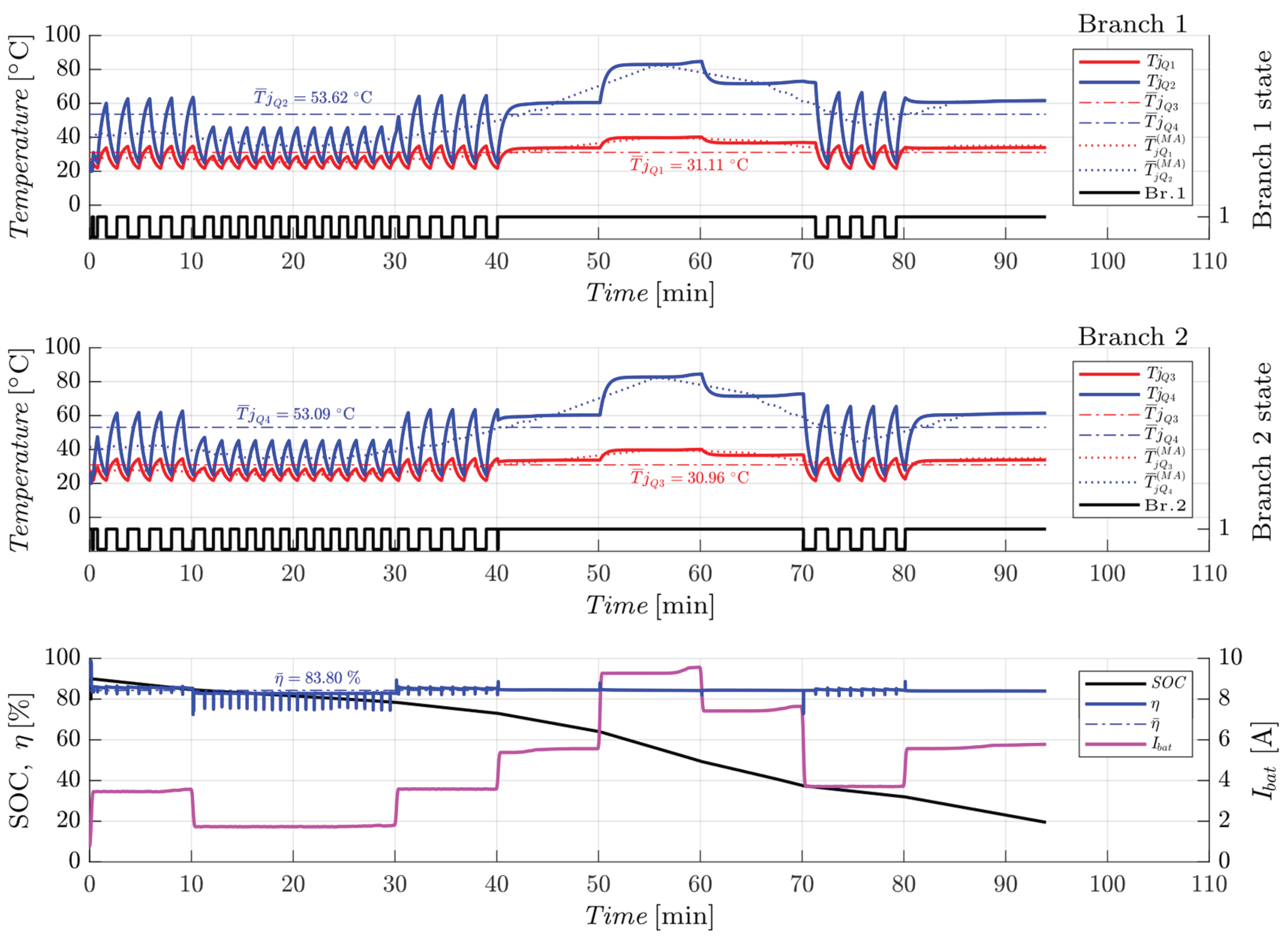

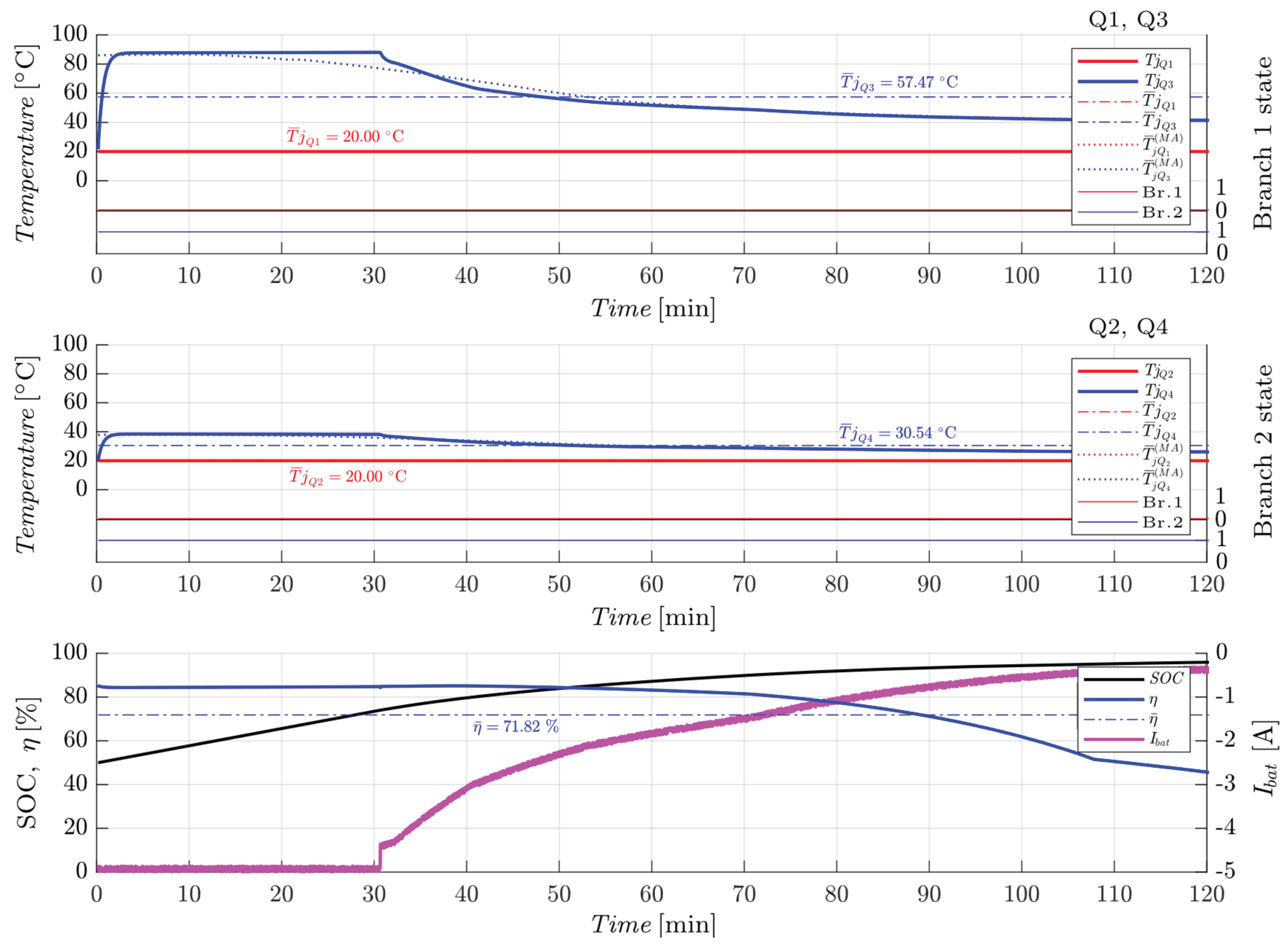

Figure 24,

Figure 25 and

Figure 26. The initial measurement set, denoted as Set 1 (

Table 5,

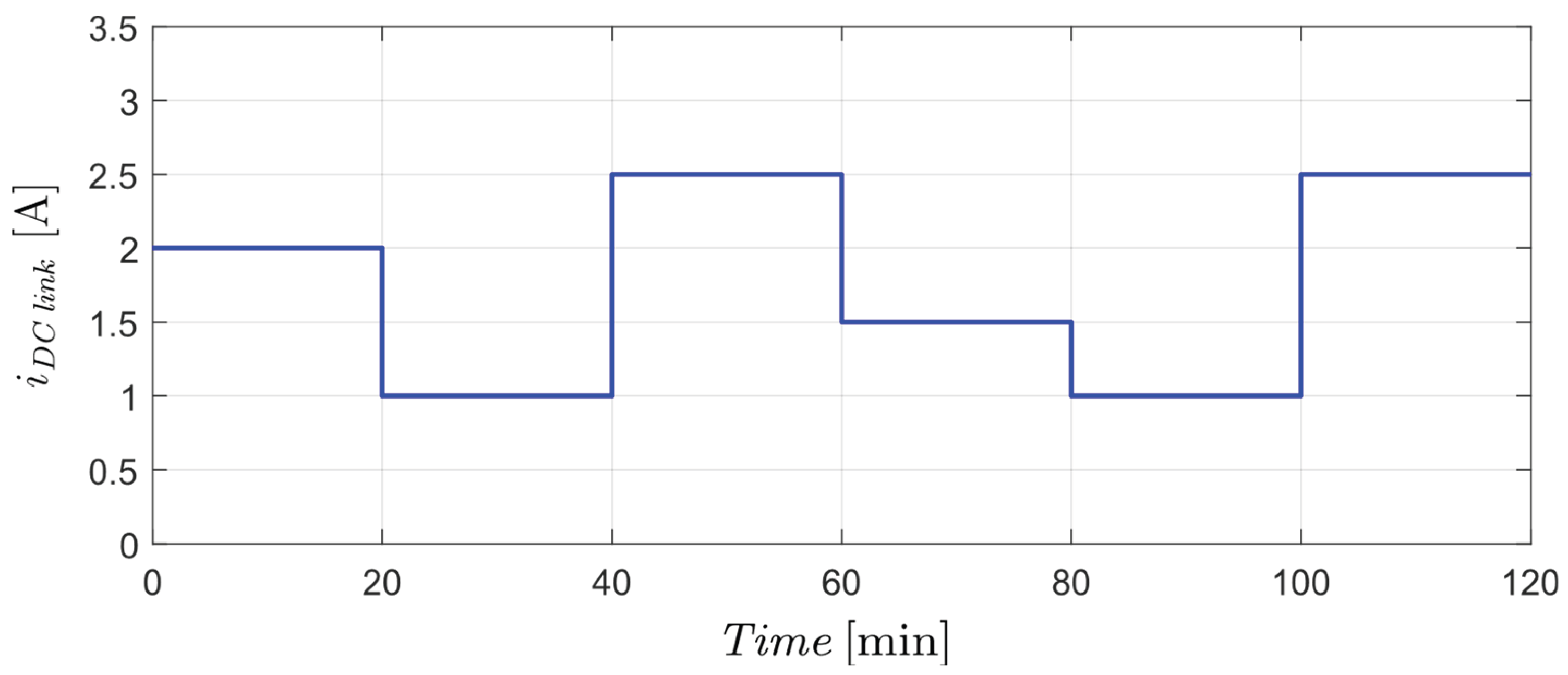

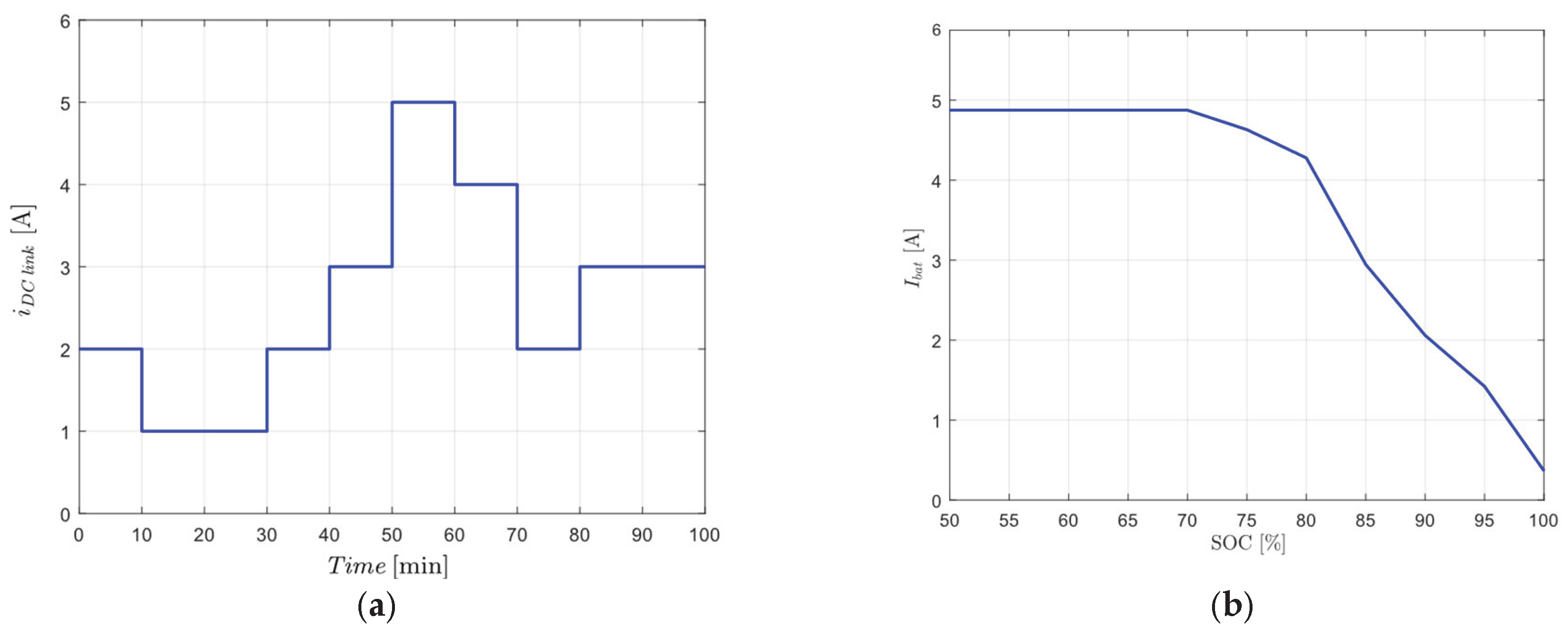

Figure 24), is used as the reference case for boost-mode operation, with the applied load profile corresponding to that shown in

Figure 23a.

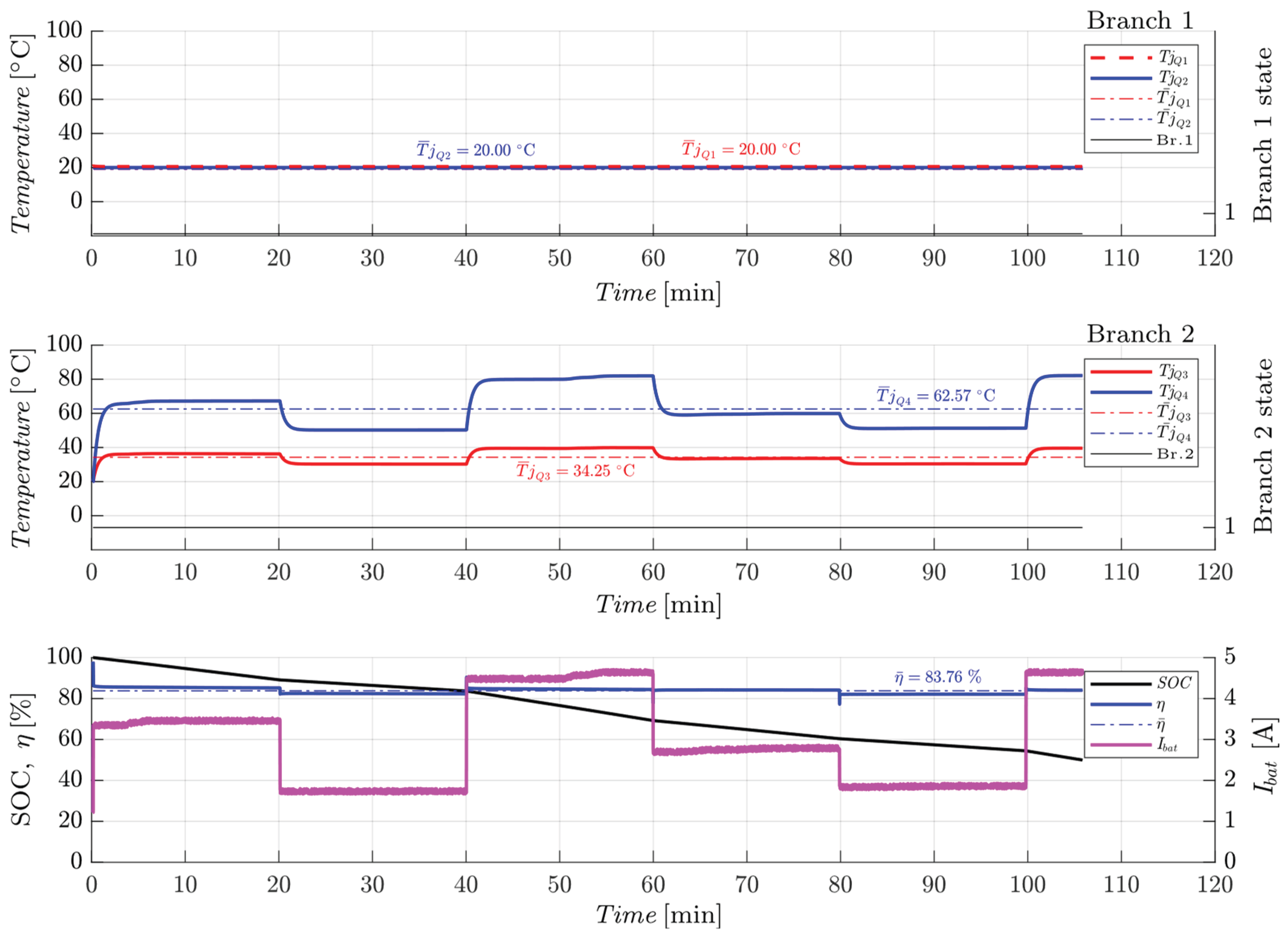

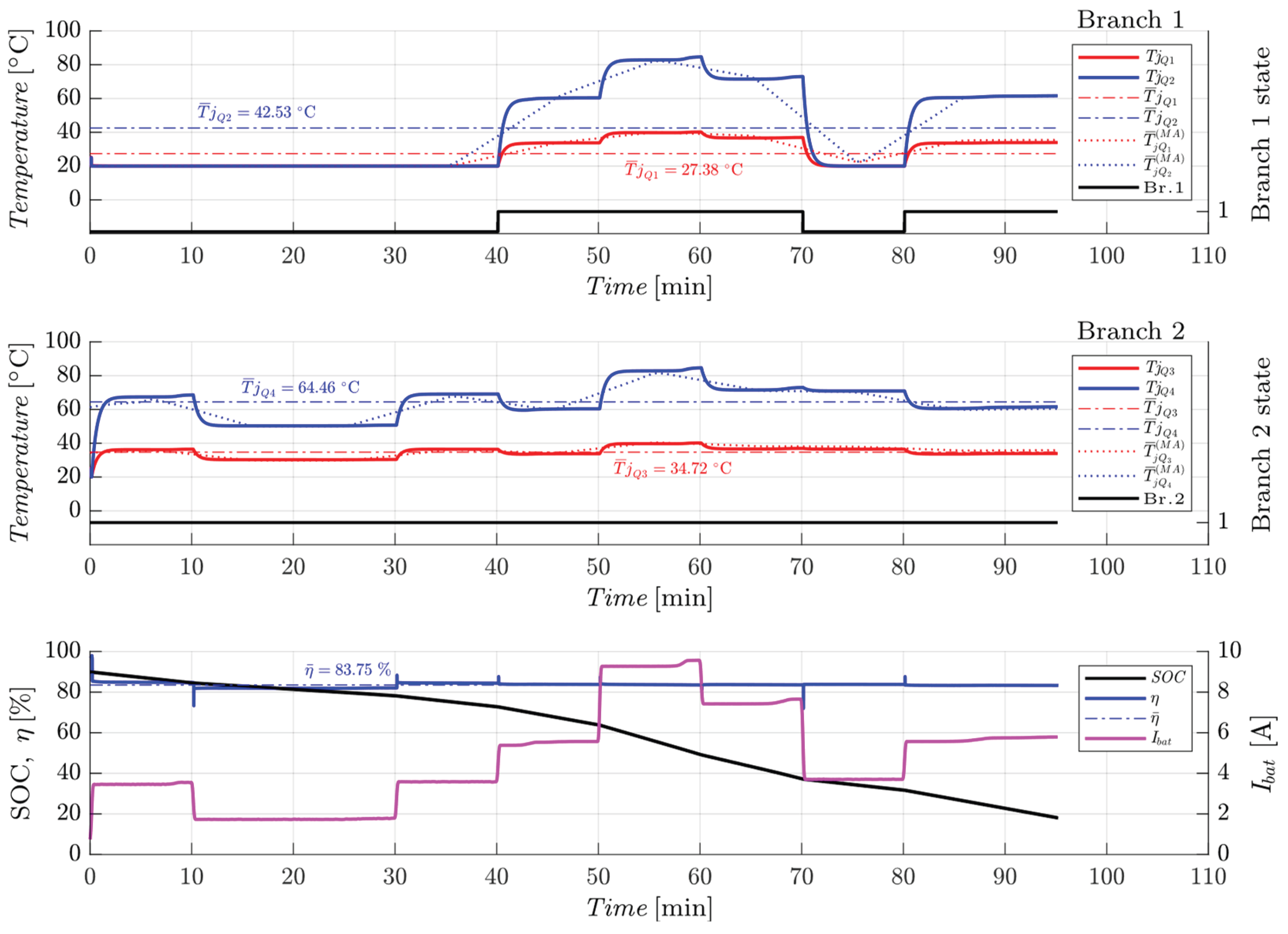

The measurement results for boost mode operation are presented using a three-window plot arrangement. The upper window shows the junction temperatures of the transistors in Branch 1 together with the corresponding switching state of this branch. The middle window illustrates the junction temperatures of the transistors in Branch 2, along with its associated switching state. The lower window displays the measured battery current and the battery , providing additional context for the operating conditions during the measurement.

These graphs also serve as a control reference to verify that the battery discharge process remains uninterrupted and consistent across all measurement sets. In

Figure 24, the average junction temperatures of the transistors in the first branch (

i

) and in the second branch (

i

) are presented, as defined by expression (1):

where

denotes the mean junction temperature of the

transistor,

represents the junction temperature of the

transistor at the

time sample, and

denotes the total number of time samples.

Additionally, to provide clearer insight into the temperature rise and decay trends, curves representing the instantaneous moving average of the transistor junction temperatures are included. These curves, referred to as the moving average (

), are calculated using expression (2):

where

denotes the instantaneous moving average junction temperature of the

transistor,

represents the number of samples within the moving average window,

is the junction temperature of the

transistor at the

time sample, and

denotes the current time index for which the moving average value is evaluated. Given that the sampling interval is set to

, a window of

samples is used to compute the moving average junction temperature of the

transistor,

. This method enables the generation of smooth temperature profiles, reflecting variations over a defined time interval of approximately

minutes.

From the analysis of the graphs in

Figure 24, it can be observed that under higher load conditions both branches are active, whereas at lower load conditions only Branch 2 remains active. The measurements associated with Branch 2 are therefore of particular importance, since this branch operates for

of the experiment duration. Consequently, Branch 2 constitutes a key reference for evaluating the effectiveness of the implemented algorithms in the subsequent measurement sets related to the boost operating mode of the converter. For measurement Set 1, the average temperature of the active transistor in branch 2 is

, while the maximum recorded temperature reaches

. The remaining performance indicators relevant to the implemented control algorithms for the conducted measurement sets are summarized in

Table 6. It should be noted that the battery current profile,

, closely follows the predefined load characteristic, which is determined by the DC-link current

.

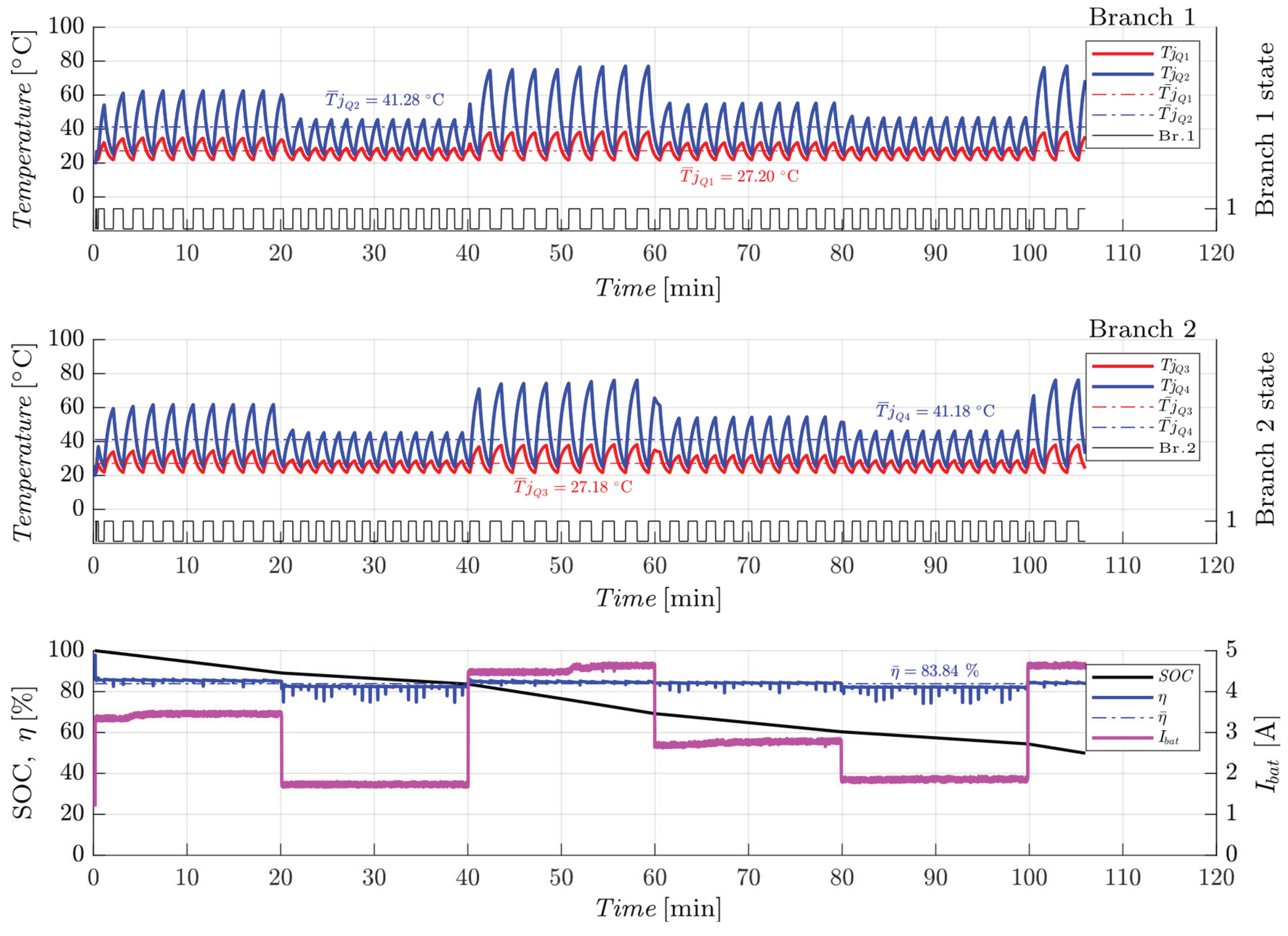

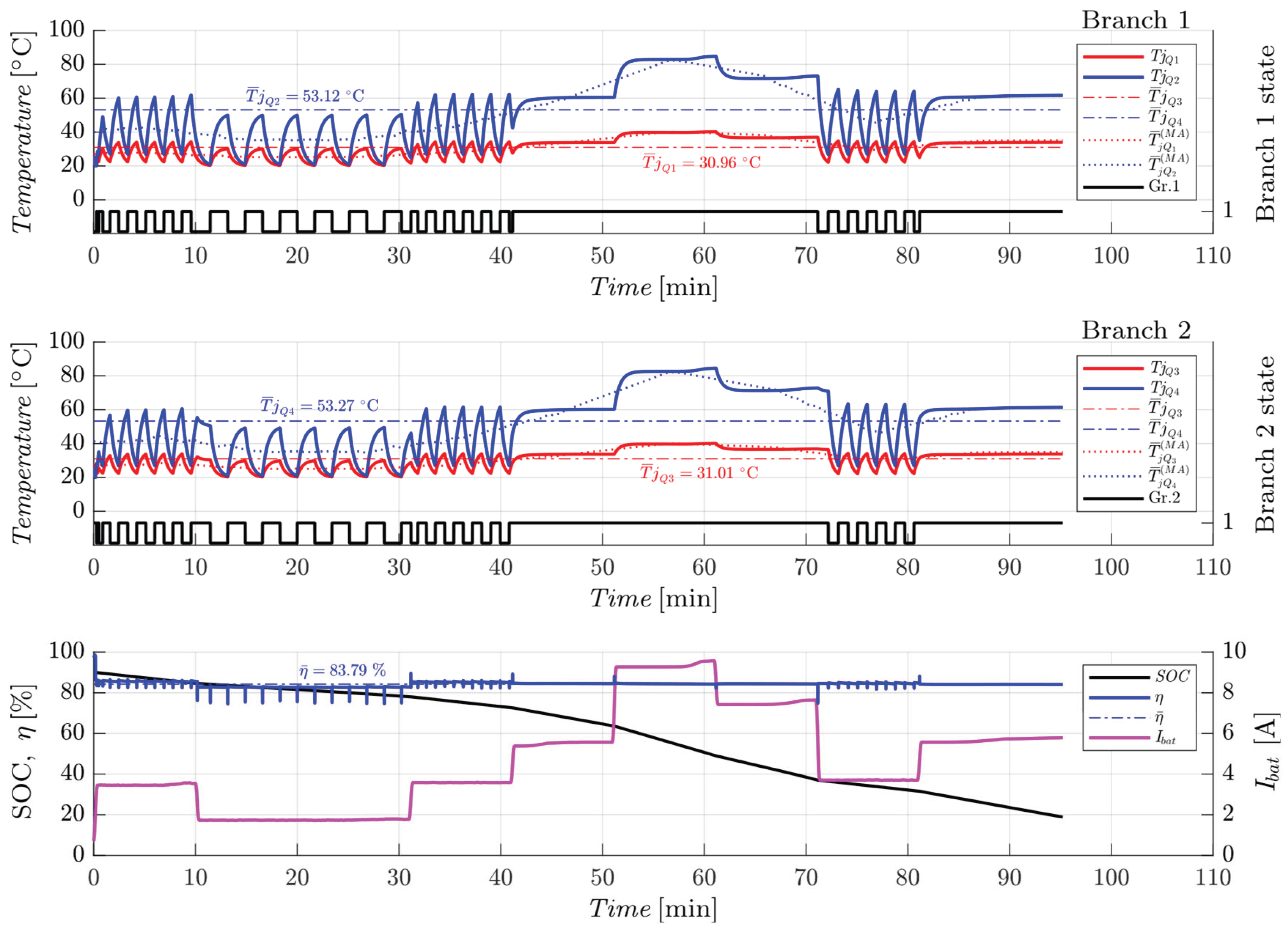

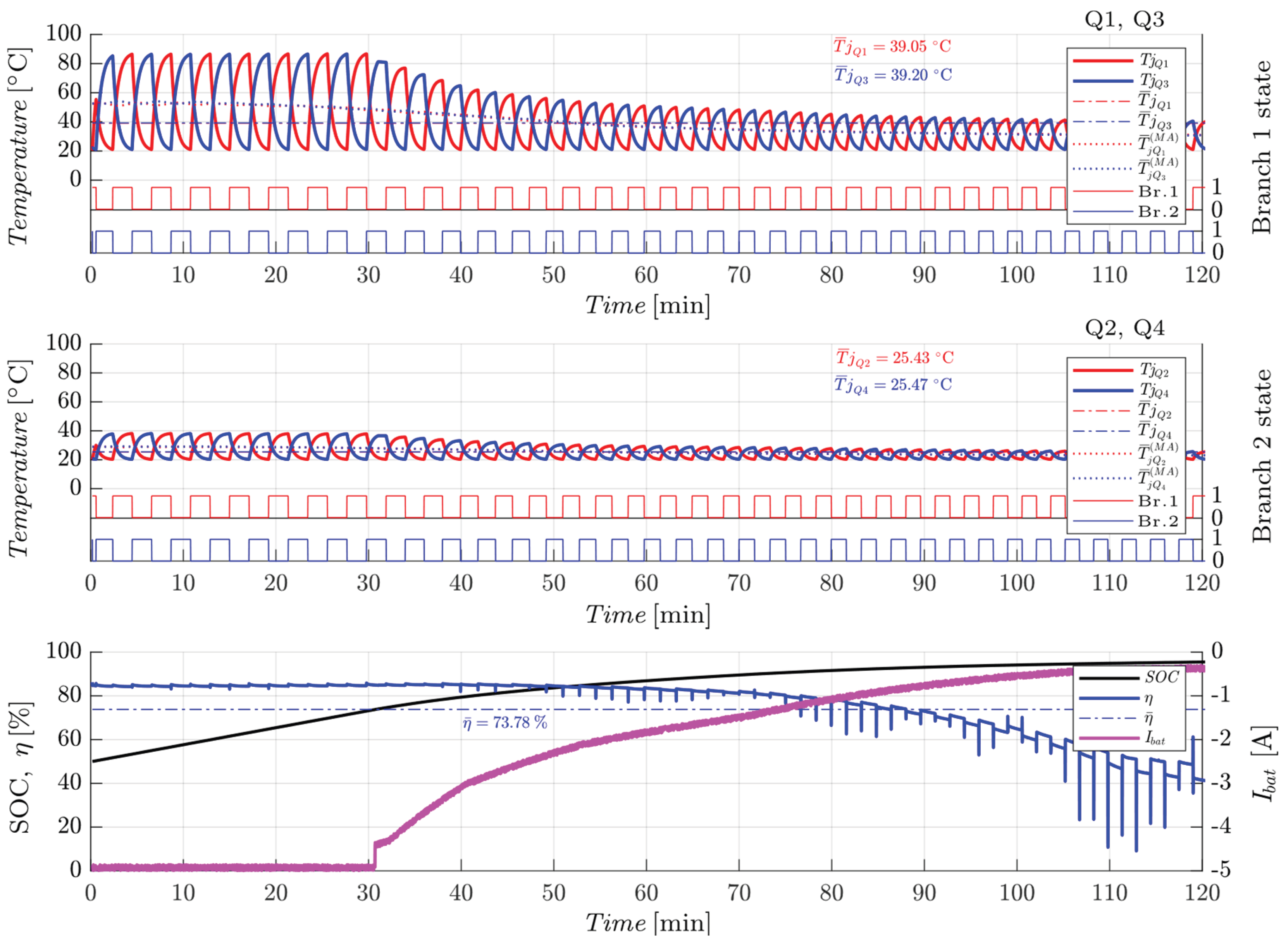

The measurement results corresponding to Set 2 are presented in

Figure 25.

As shown in

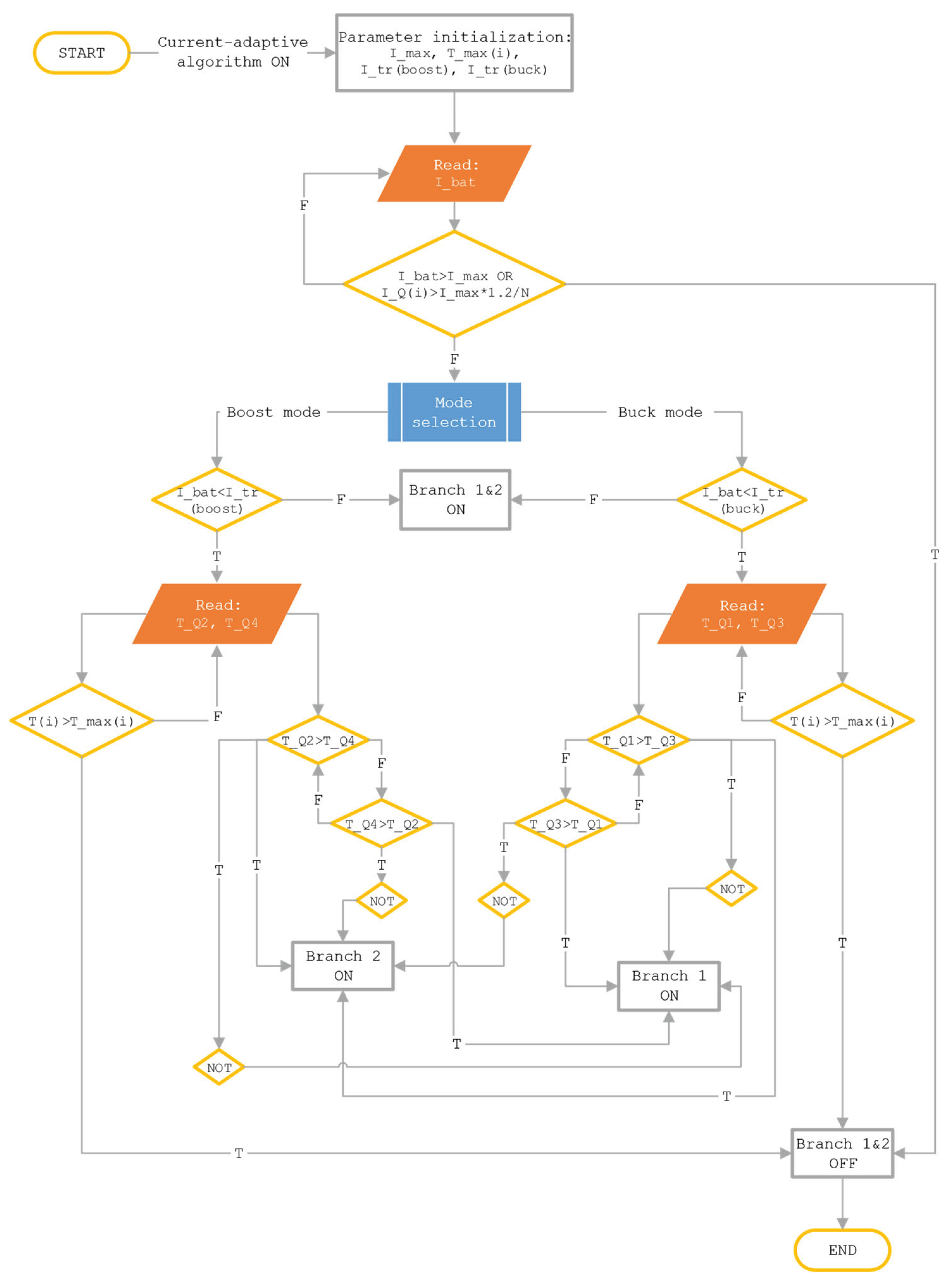

Figure 25, the recorded battery load profile exhibits characteristics identical to those observed in measurement Set 1, indicating an uninterrupted battery discharge process. This observation is particularly relevant, as the branch rotation algorithm is enabled in this measurement set, which is clearly reflected by the switching states of the converter branches shown in the first two windows of

Figure 25. The measurement results further demonstrate that branch rotation is activated when the instantaneous battery current decreases below

. This behavior is fully consistent with the expected operation of the implemented control algorithm, as defined by the decision logic illustrated in the flowchart in

Figure 20.

A key indicator of branch rotation effectiveness is the average branch activation time during operation. In contrast to Set 1, where the branch remained active for

of the experiment duration, the average activation time in Set 2 is reduced to

of the total measurement interval. As a result, the average junction temperature of the observed transistor

in Set 2 decreases to

. while the maximum junction temperature remains approximately unchanged compared to Set 1, reaching

. A comprehensive summary of the obtained results is presented in

Table 6.

It should be noted that the temperature threshold for branch rotation activation was set to

, which plays a significant role in shaping the effective thermal time constants associated with heating and cooling processes. These time constants are directly influenced by the load applied to the observed transistor and will be discussed in greater detail following the presentation of the results from the final measurement (Set 3) of the boost mode, with the corresponding plots shown in

Figure 26.

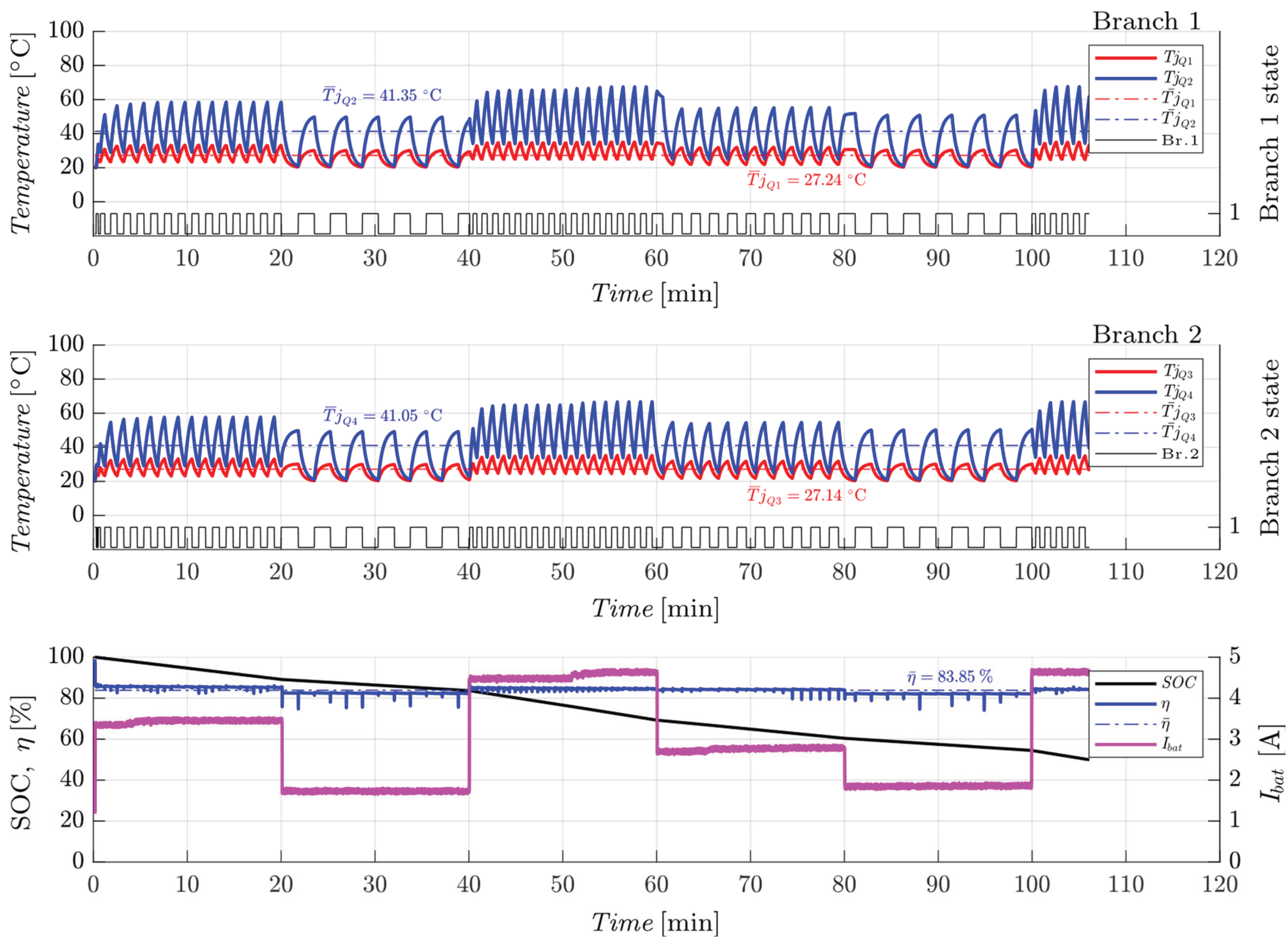

Figure 26 presents the measurement results of the final test set for boost mode operation. The battery current

and SOC profiles shown in the third window remain consistent with those observed in the first two measurement sets, indicating stable and repeatable operating conditions. In contrast to the previous set (Set 2), branch rotation in this case is governed by a variable temperature threshold range of

, which is dynamically adjusted according to the load level. Specifically, lower load conditions correspond to lower temperature thresholds for branch rotation activation, while higher load conditions result in higher rotation temperature thresholds.

This adjustment leads to variations in the effective thermal time constants associated with heating and cooling processes, which can be qualitatively observed through the switching states of Branches 1 and 2 when comparing

Figure 25 and

Figure 26. An analysis of the results from the final two measurement sets indicates that the variation in the activation temperature does not have a decisive influence on the efficiency of the algorithm in terms of reducing average and maximum transistor temperatures, nor on the average branch activation time. This behavior is primarily attributed to the fact that, for approximately

of the experiment duration, both branches operate simultaneously, during which the current-adaptive control algorithm is inactive.

A more pronounced influence of the selected branch rotation activation threshold would be expected if the operating parameters were evaluated exclusively over intervals in which the converter operates under reduced load, i.e., single-branch operation, throughout the entire experiment duration (see

Appendix A1 for an illustrative example).

Table 6 provides a comprehensive analysis of the measurement results for the converter operating in boost mode, corresponding to the predefined measurement sets listed in

Table 5.

The temperature differences calculated from

Table 5 are determined using expression (3):

where

denotes the absolute temperature difference between measurement sets

and

, expressed in degrees Celsius [°C], and

represents the corresponding relative temperature difference expressed as a percentage

. The term

refers to the characteristic temperature value (e.g., average or maximum junction temperature) obtained from measurement set

, while

corresponds to the same temperature metric obtained from measurement set

.

The key performance indicators of the proposed algorithm include the reduction of the average junction temperature of the transistor

and the maximum junction temperature

, as well as the equalization of the average activation times of the individual converter branches, denoted by

. However, according to the results summarized in

Table 6, the maximum junction temperatures remain approximately unchanged across the evaluated measurement sets. This behavior can be explained by examining the corresponding measurement plots, which show that both the load and transistor temperature profiles are identical in operating intervals where the battery current exceeds

. Consequently, the maximum junction temperature observed during the experiments is consistently defined within these high-load intervals and occurs at the same points corresponding to peak load conditions.

If the maximum junction temperature were evaluated exclusively over intervals in which the converter operates under reduced load below the activation threshold of the current-adaptive algorithm—a reduction would be observed not only in the average temperature but also in the maximum temperature, as demonstrated in

Appendix A1.

Therefore, to assess the effectiveness of the implemented control algorithms for measurement Sets 1–3, the analysis focuses on the primary performance indicators: the average junction temperatures

and

, as well as the average activation times of the corresponding transistors, denoted by

and

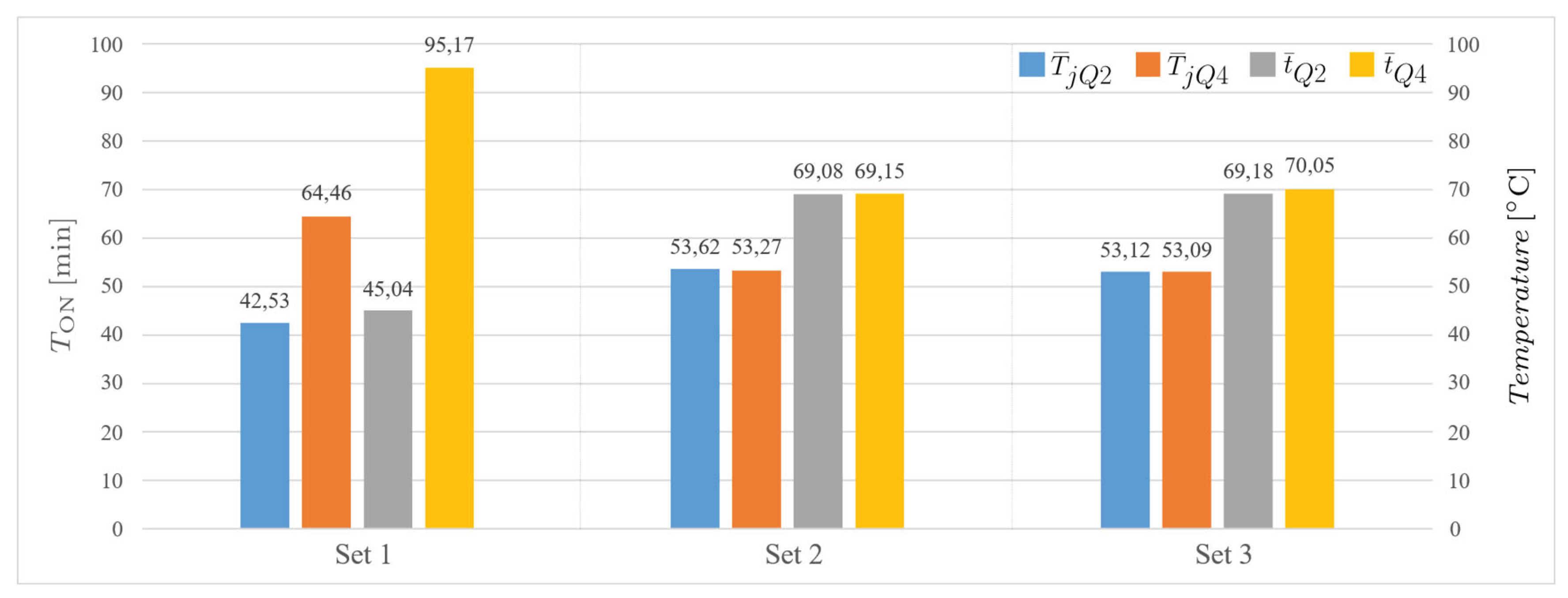

. These indicators are presented in the form of bar charts in

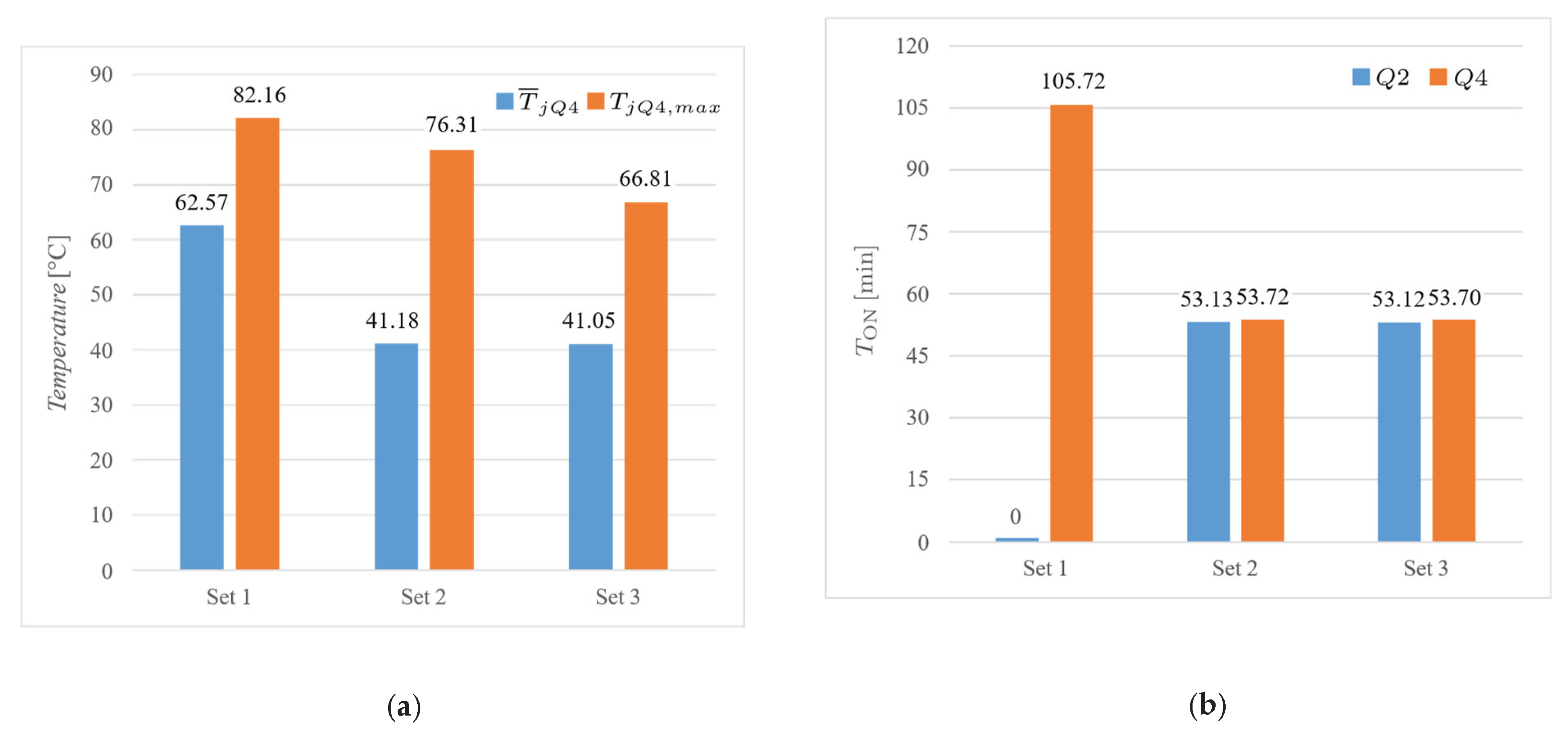

Figure 27.

As evident from the graphs in

Figure 27, measurement Sets 2 and 3 exhibit effective equalization of both average transistor temperatures and activation durations over the course of the experiment. Focusing on transistor

, which remained active for nearly the entire duration of the reference measurement Set 1 with an average activation time of

, the application of the proposed control strategy results in a reduction of the average activation duration to approximately

.

This equalization of the activation time of transistor with that of transistor confirms the effective application of branch rotation during operation, resulting in a reduction of the operational time of transistor by approximately . Such load redistribution is expected to mitigate thermal stress and may contribute to extending the lifetime of the transistor and, consequently, improving the overall reliability and longevity of the converter. Additionally, a reduction in the average junction temperature of transistor is observed, decreasing from in measurement Set 1 to approximately in Sets 2 and 3. This reduction corresponds to a decrease in thermal stress experienced by the device.

Based on the presented results and their analysis, it can be concluded that the validation of the proposed control method in boost mode operation has been successfully achieved.

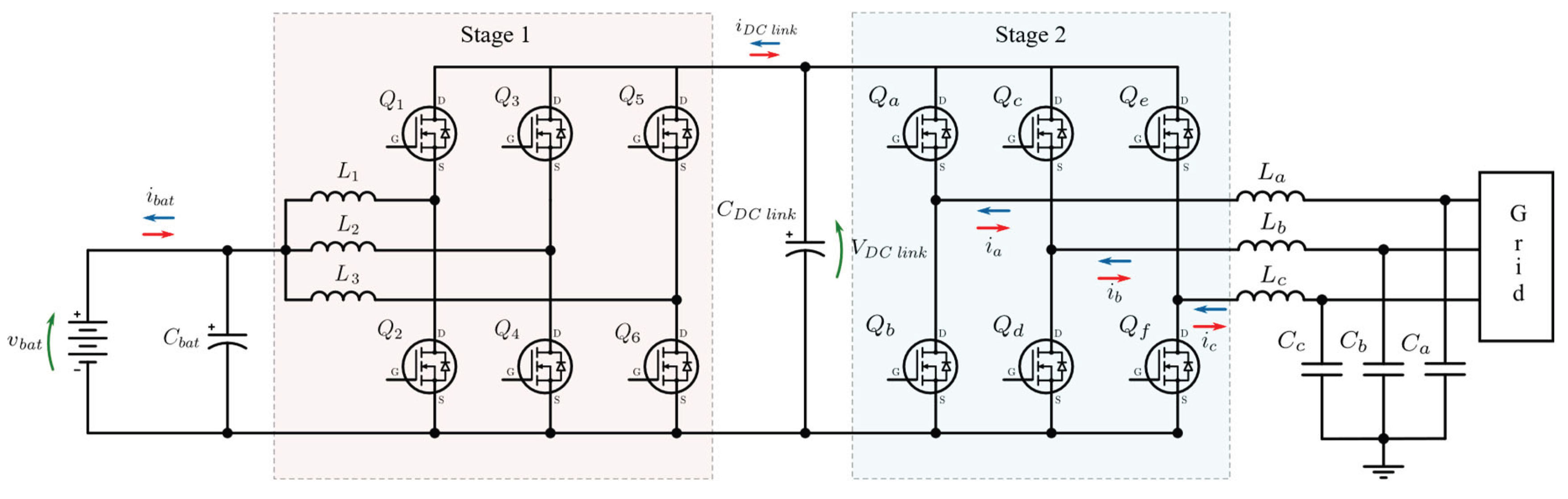

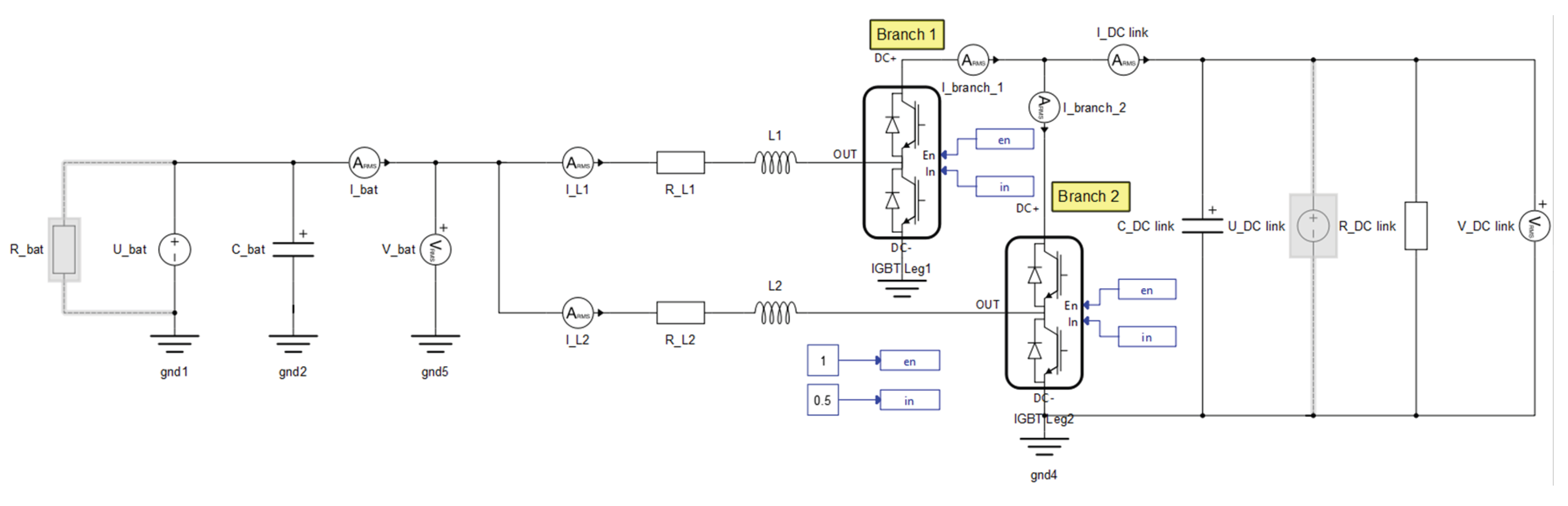

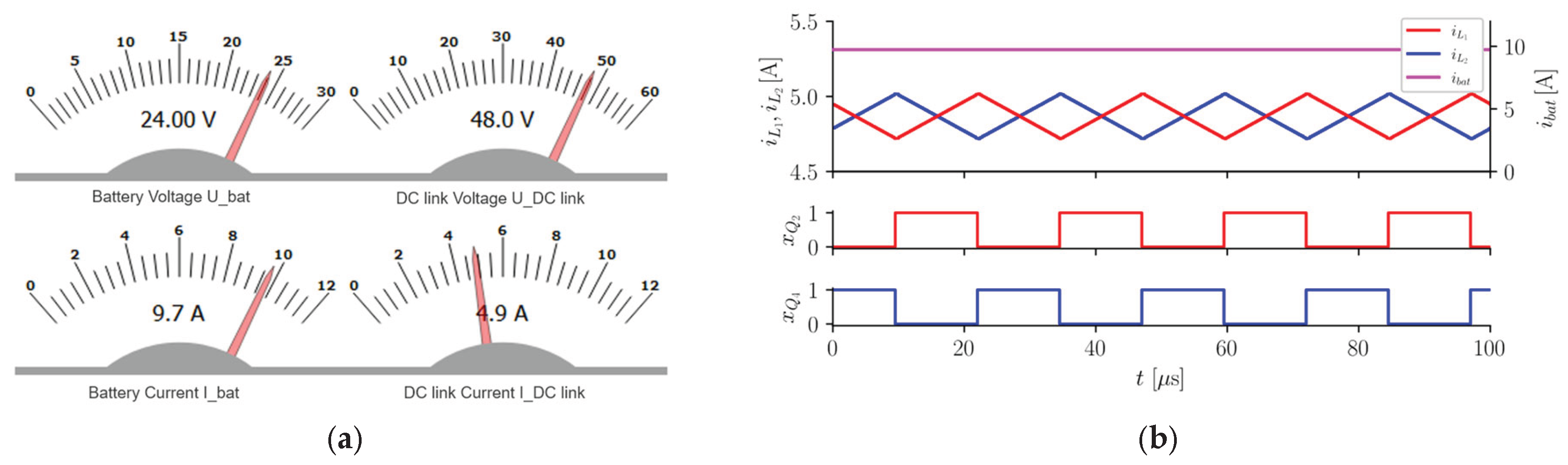

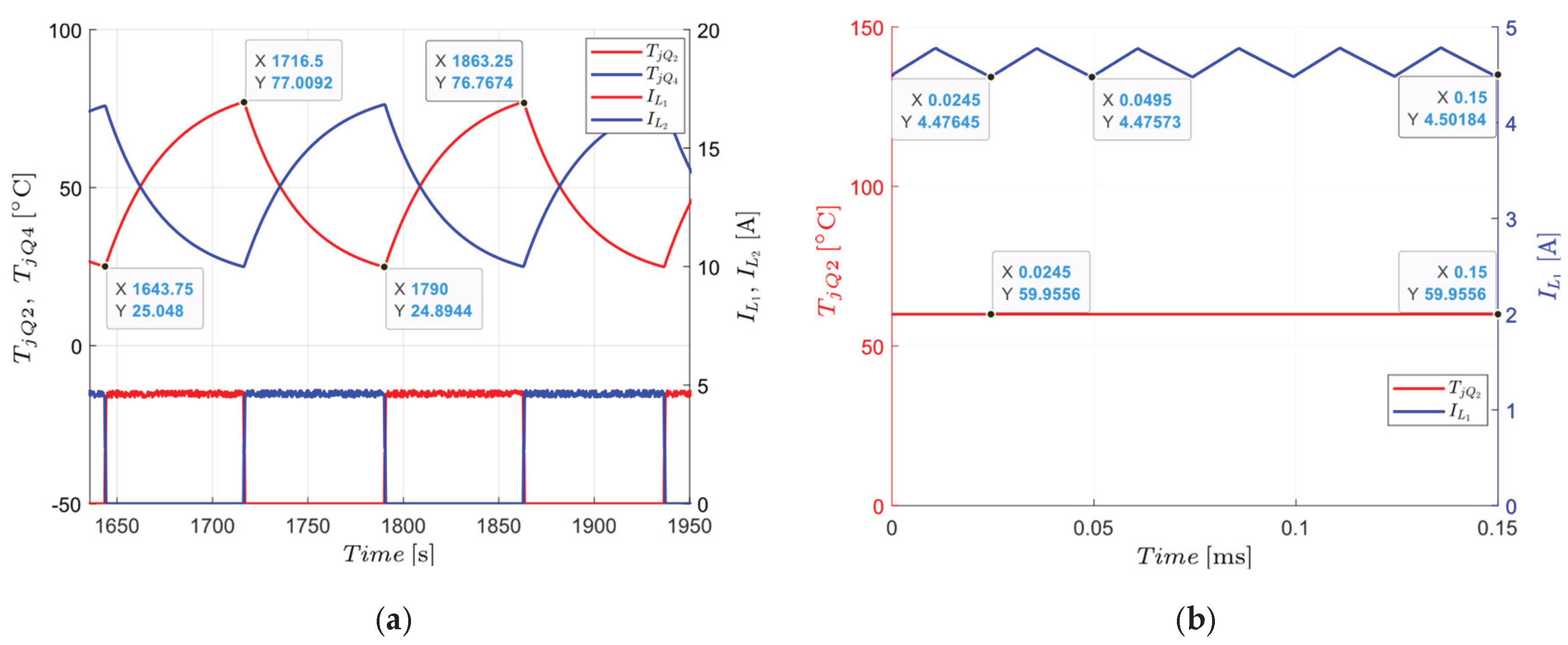

Electrical versus Thermal Time Constants

Before analyzing the measurement results for the buck operating mode, a brief observation of the thermal and electrical time constants is provided, as illustrated in

Figure 28, which compares the characteristic dynamics of thermal and electrical variables in the observed system. For illustration purposes, an operating point in boost mode was selected with a battery state of charge of

and a DC-link discharge current of

. The analysis of

Figure 28 shows that the duration of a single branch deactivation–reactivation cycle is approximately

, while the current in each converter branch remains relatively smooth over this interval (

Figure 28a). In contrast, when examining several switching periods of the inductor current, the temperature of the observed branch transistor remains smooth and essentially unchanged (

Figure 28b).

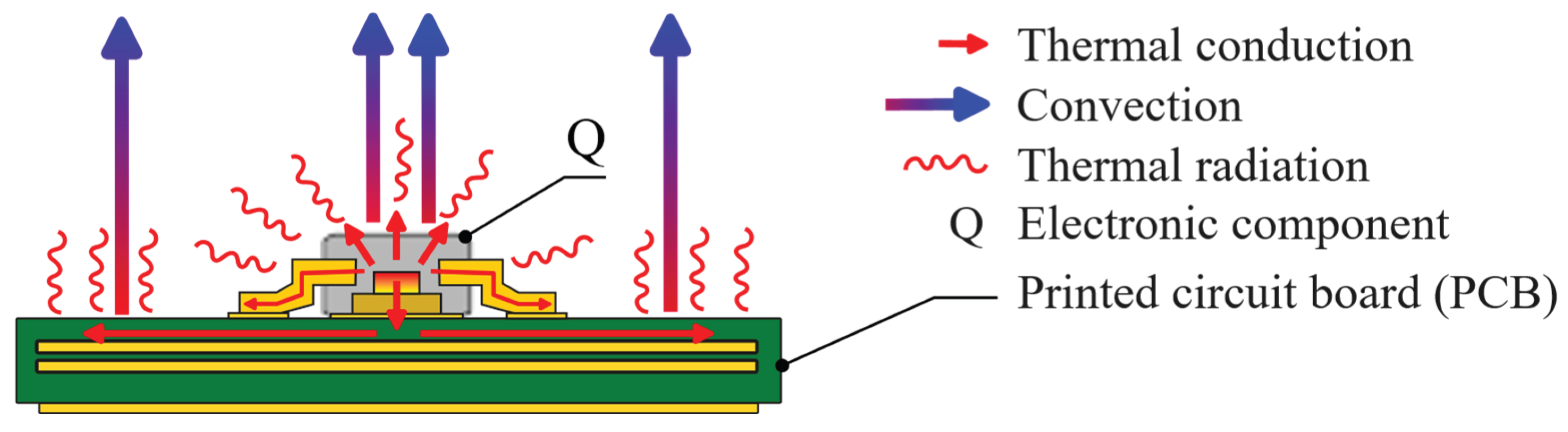

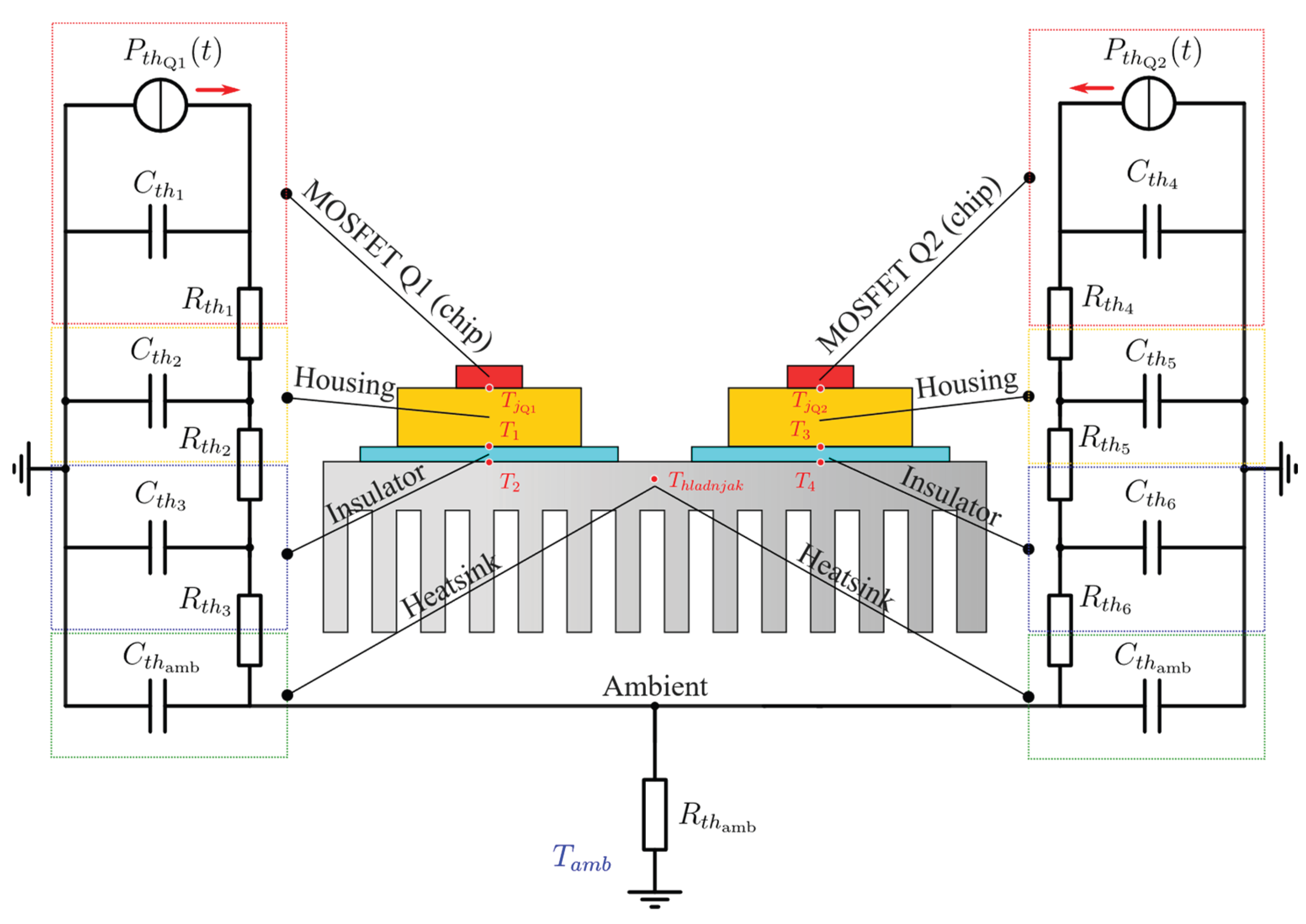

This observation clearly highlights the pronounced difference between electrical and thermal dynamics, with their corresponding time constants differing by approximately six orders of magnitude. Although the flow of current generates heat and leads to an increase in transistor temperature, these significantly different time scales imply that rapid variations in electrical quantities do not result in instantaneous temperature changes. This behavior is attributed to thermal inertia, which arises from the thermal resistances and capacitances associated with heat dissipation and cooling processes, as discussed in Subsection 3.3. Furthermore, due to the high switching frequency of the converter () relative to the branch-switching frequency () the influence of electrical switching dynamics is not observable in the temperature waveform.

5.2. Validation Results in Buck Operation

Figure 29 illustrates the measurement results corresponding to Set 4, as specified in

Table 5, used for validation of the proposed adaptive control algorithm in buck mode. The measurement results for buck mode operation (

Figure 29 and

Figure 30) are presented in a slightly different format compared to the results for boost mode operation in Sets 1–3, where the temperatures of individual transistors were displayed in separate plots. In buck mode operation, the temperatures of the active transistors from both converter branches are presented on a single plot to facilitate visualization of conduction overlap and enable detailed analysis of the associated thermal time constants. This representation provides clearer insight into the operational dynamics of the system.

Unlike the measurement sets for boost mode operation, in which the reference set allowed one or both converter branches to be active depending on the load level and the application of the current-adaptive algorithm (

Figure 23a), the reference set for buck mode operation (

Figure 29) exhibits continuous activation of the current-adaptive algorithm. Consequently, the converter operates under reduced load with a single active branch throughout the entire measurement interval. This behavior arises because the charging current, as defined by the load profile in

Figure 23b, consistently remains below the threshold required to activate the current-adaptive algorithm. Thus, the activation conditions are never satisfied. Although operation at higher charging currents would be technically feasible, the selected charging profile follows the manufacturer’s recommendations specified in the datasheets of the employed battery cells. In particular, the charging current of the 7S3P battery pack is limited to approximately

, as given in

Table 3. Additionally, conducting redundant measurements and deriving unnecessary conclusions was not required, since the relevant validation of the current-adaptive algorithm had already been performed in the first three measurement sets.

In buck mode operation, the active transistors are

and

, and their corresponding junction temperatures,

and

displayed in the first window of

Figure 29. The average junction temperature of the active transistor

is

, while the maximum recorded junction temperature reaches

, as summarized in

Table 7. The battery current graph shows an initial charging current of approximately

, which decreases after approximately

as the charging algorithm transitions into constant-voltage operation.

A detailed analysis of the obtained results is provided in

Table 7, while the measurement results corresponding to the final test set (Set 5) are presented in

Figure 30. A comparison between

Figure 29 and

Figure 30 reveals a consistent alternation of the active converter branches during operation, governed by the temperature-adaptive algorithm. The average junction temperatures of the transistors in both branches are approximately equal, with

, while the maximum junction temperatures reach

.

This result indicates that, for the fifth measurement set, the load distribution between the converter branches is effectively balanced, leading to a reduction in both the average and maximum temperatures of the second branch compared to Set 4 (

Figure 29).

The processed measurement results for buck mode operation corresponding to Sets 4 and 5 are summarized in

Table 7, from which conclusions analogous to those obtained for the boost operating mode can be drawn. Therefore, further elaboration on the influence of the implemented algorithms on the average and maximum transistor junction temperatures is not required, as the reader can directly infer the relevant trends from the presented data.

Overall, the processed measurement results for both operating modes indicate a reduction in the thermal load of the active transistors compared to the corresponding reference sets. This reduction is a direct consequence of the applied temperature-adaptive control strategy.

The obtained results confirm the successful experimental validation of both the current-adaptive algorithm and the temperature-adaptive control method under real-time operating conditions in buck-mode operation.