Submitted:

13 November 2025

Posted:

14 November 2025

You are already at the latest version

Abstract

Keywords:

1. Introduction

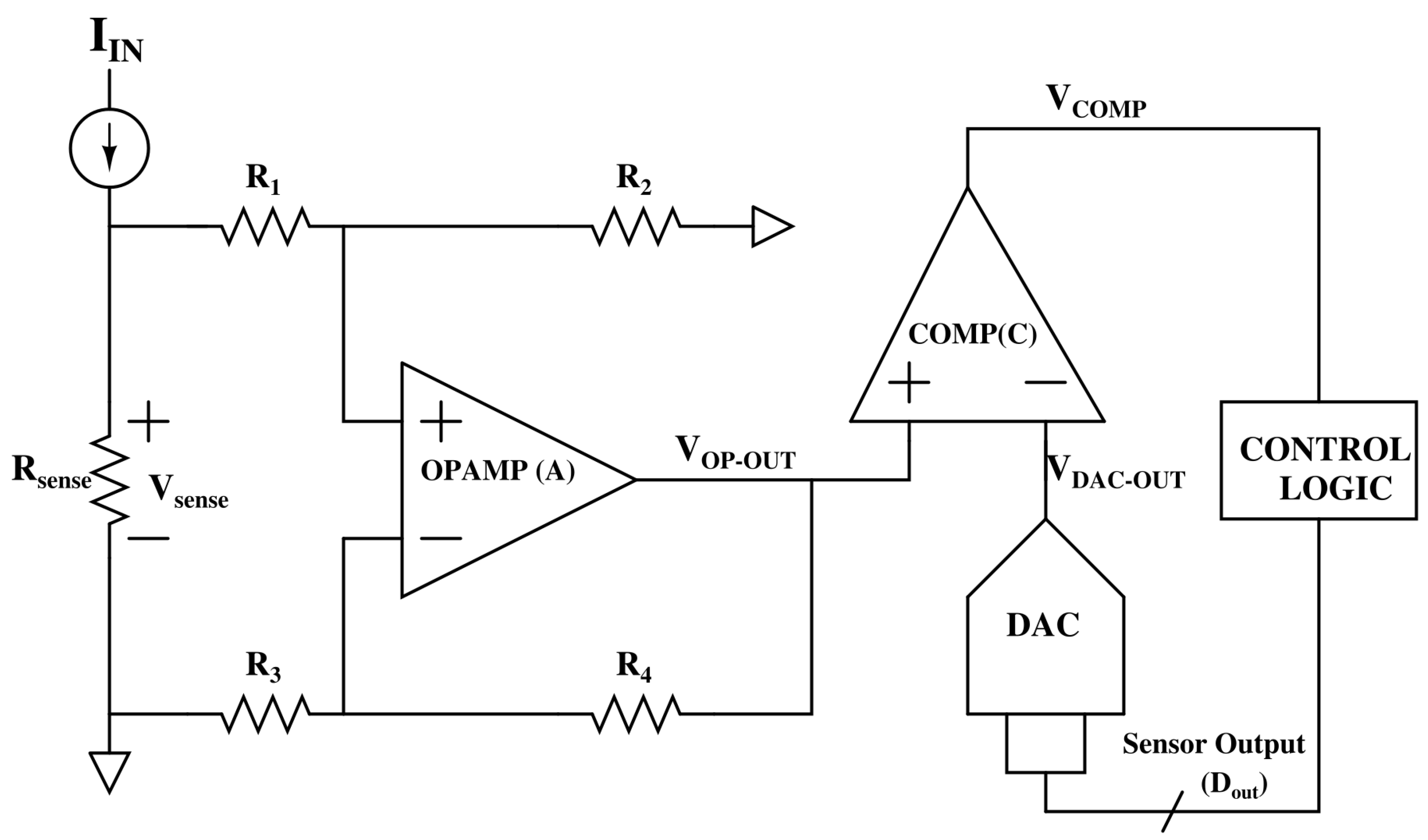

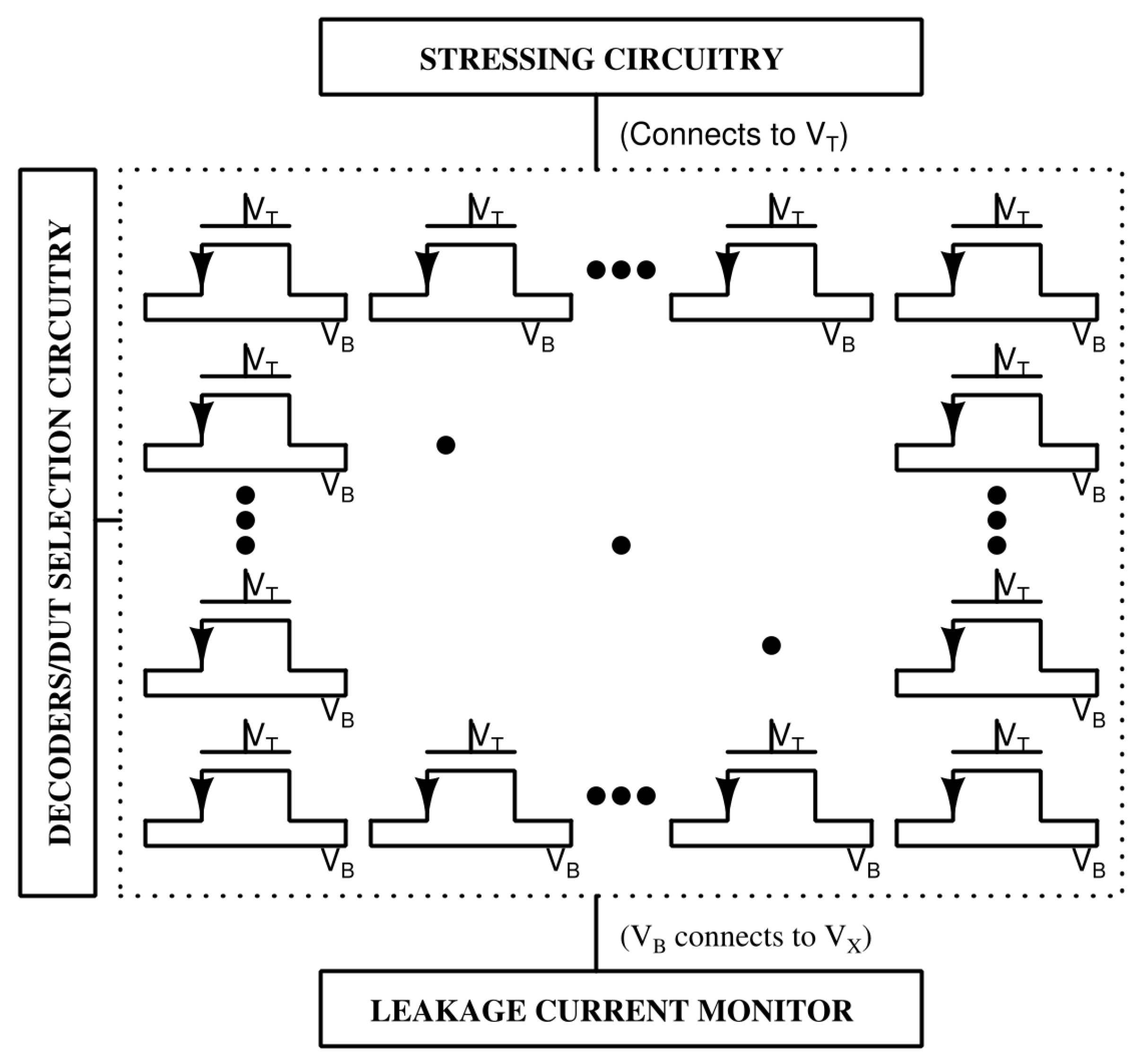

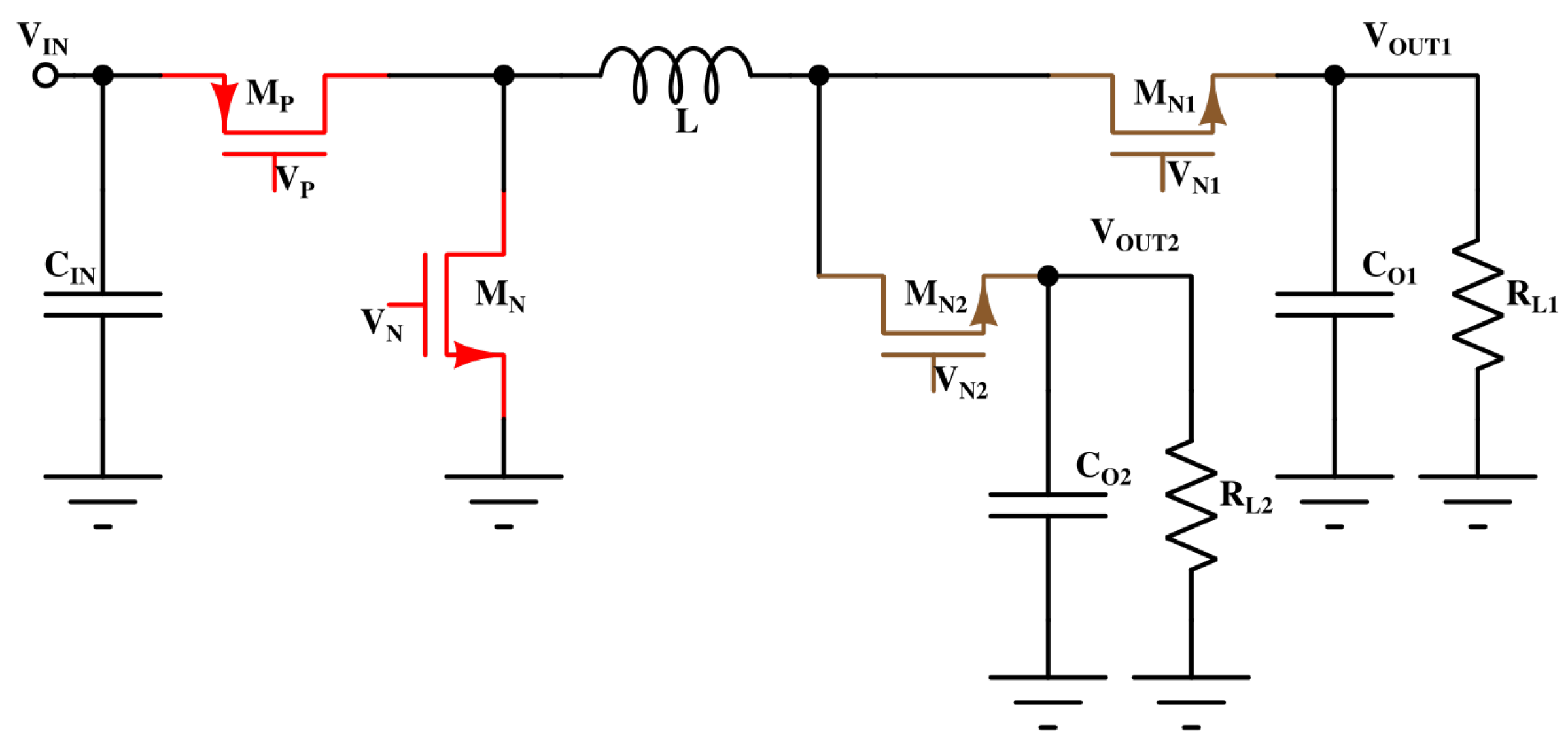

2. Proposed Leakage Current Monitor

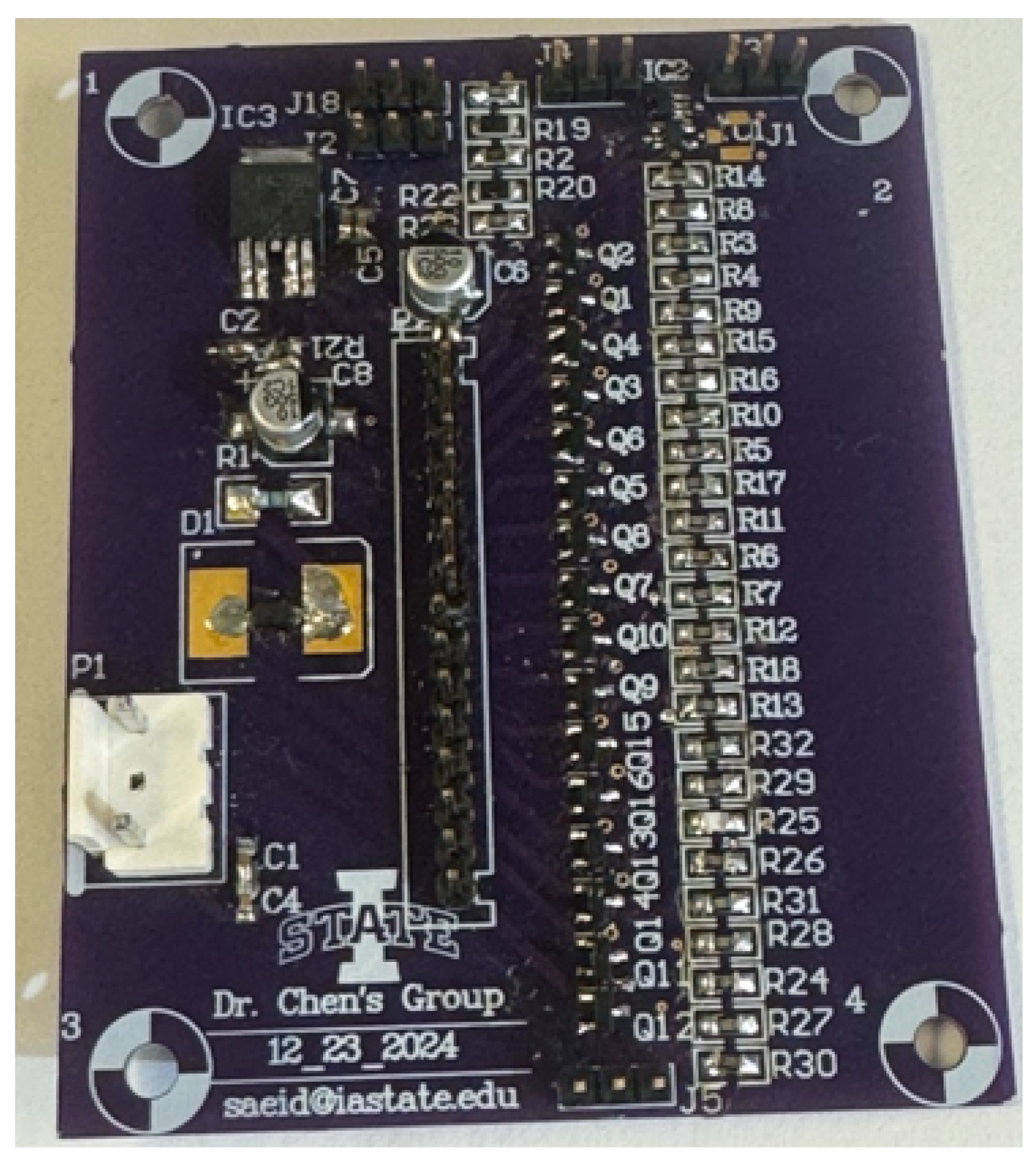

3. Board Level Implementation

4. Experimental Results

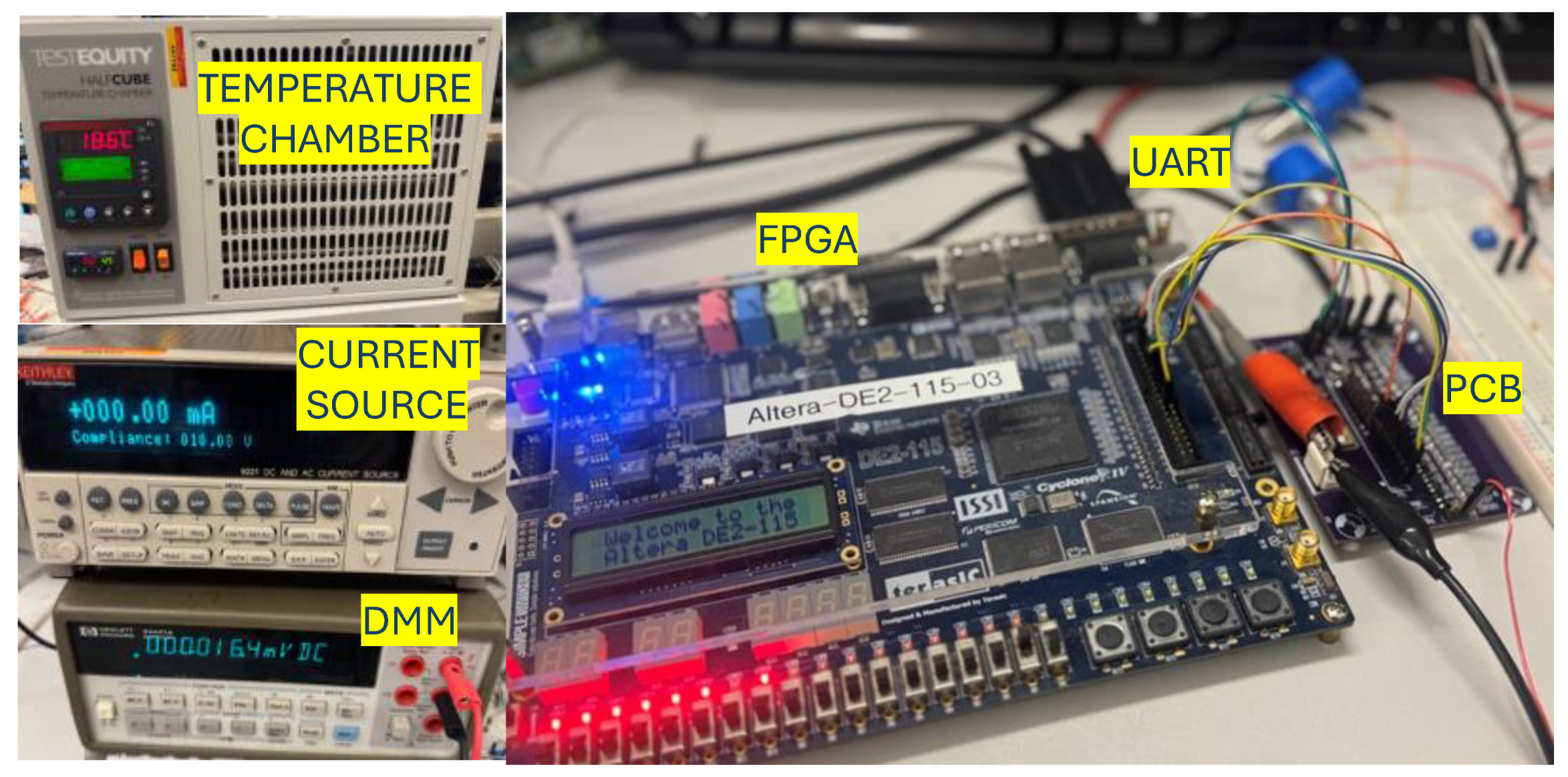

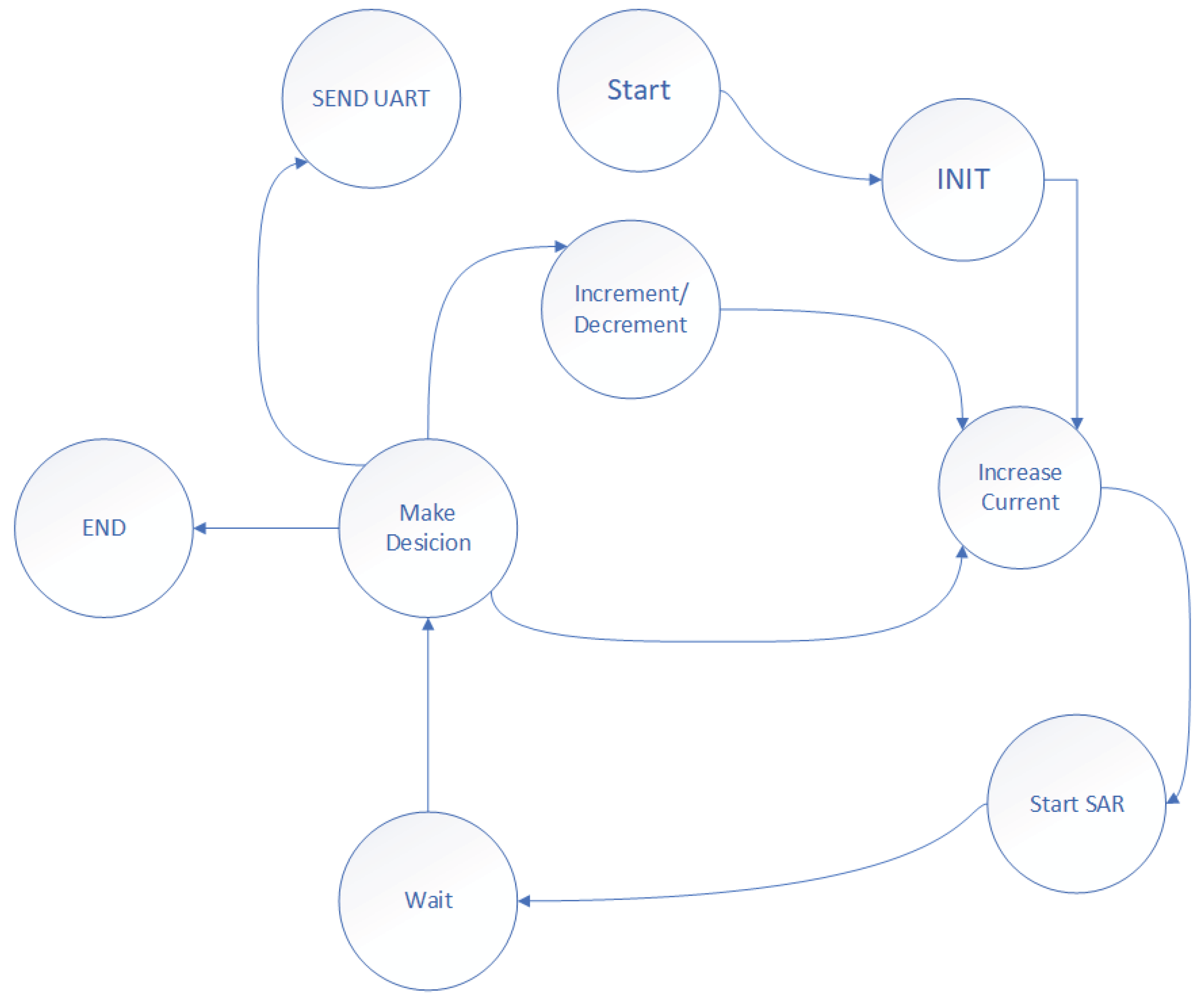

4.1. Measurement Setup and Control Flow

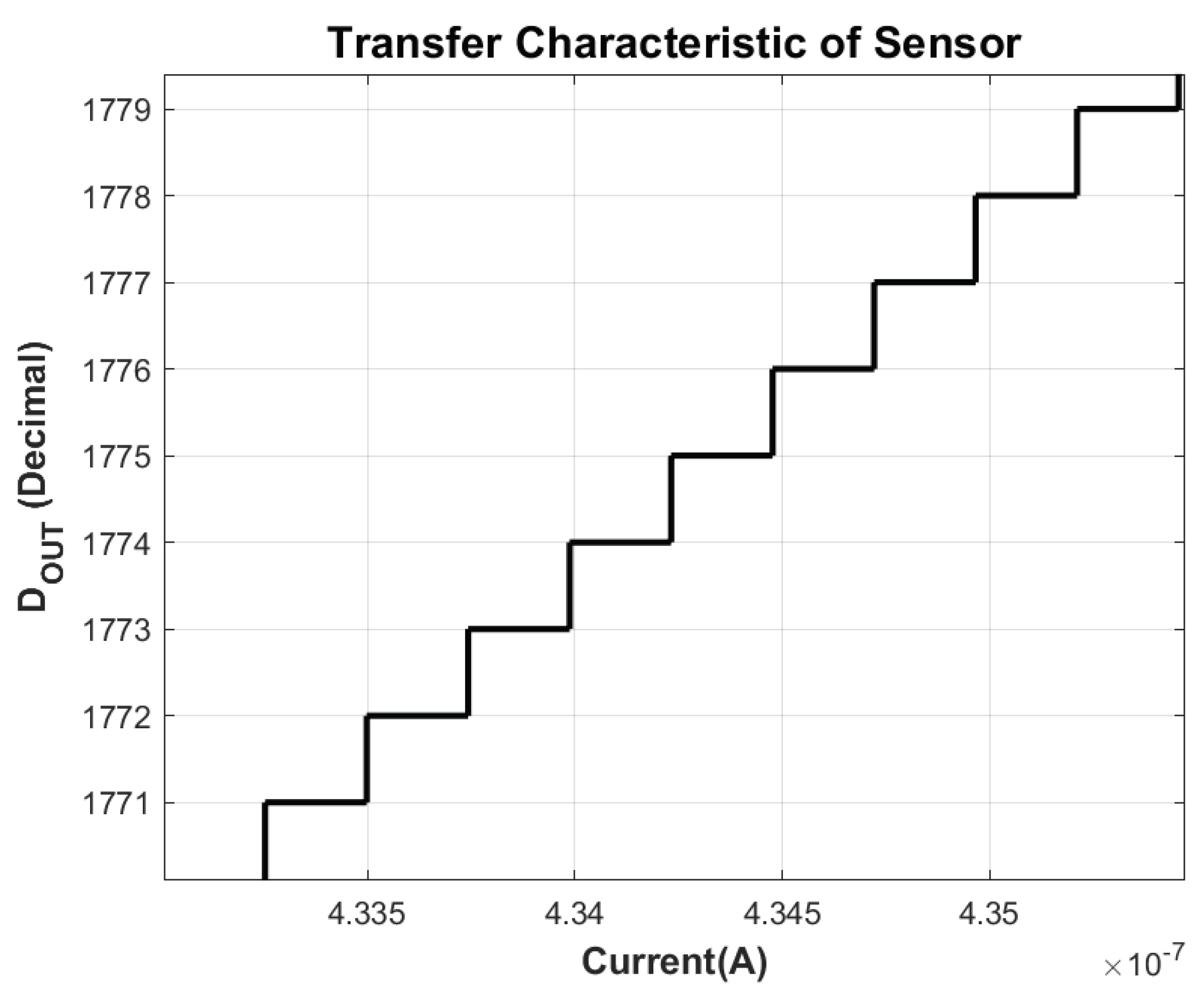

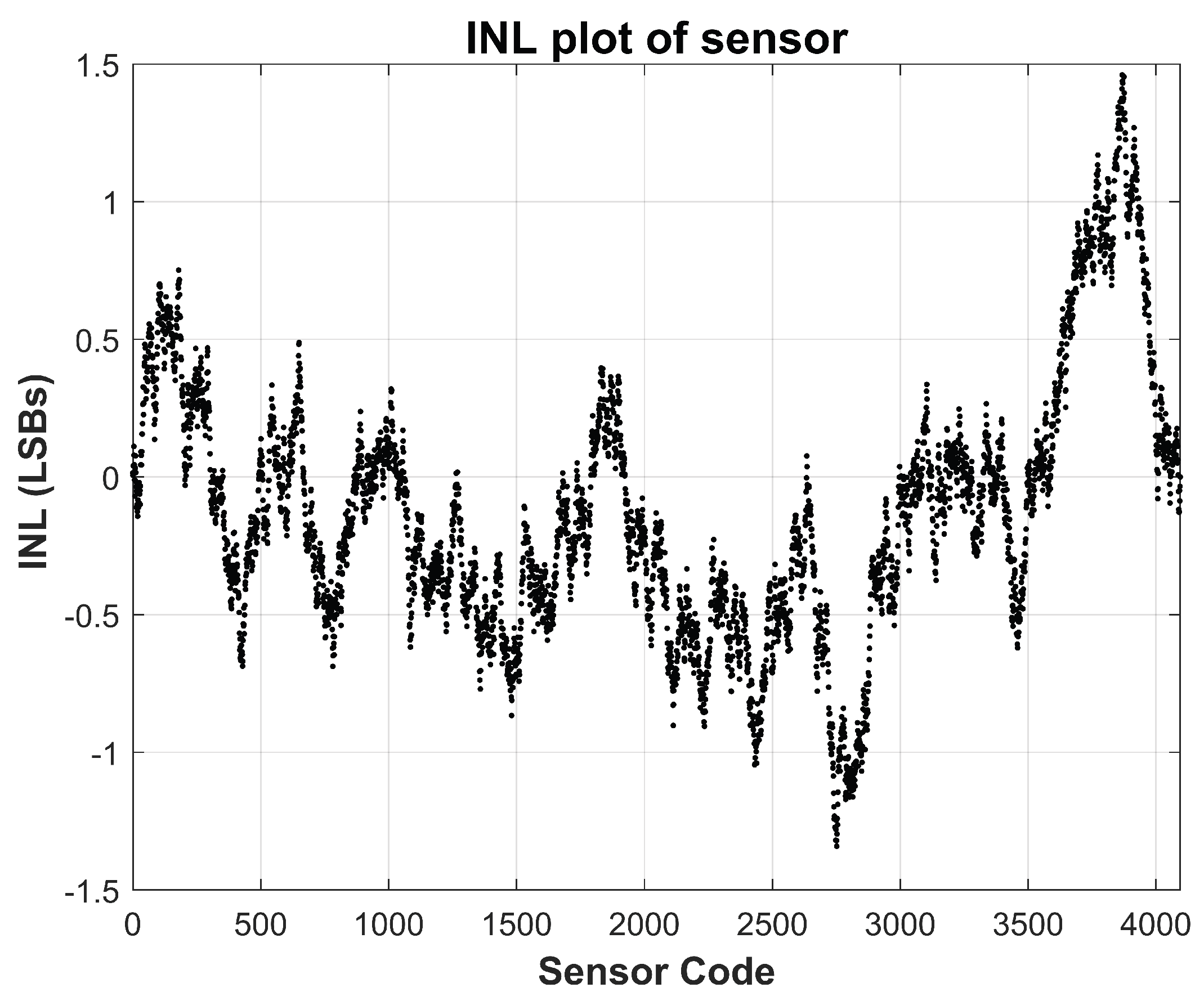

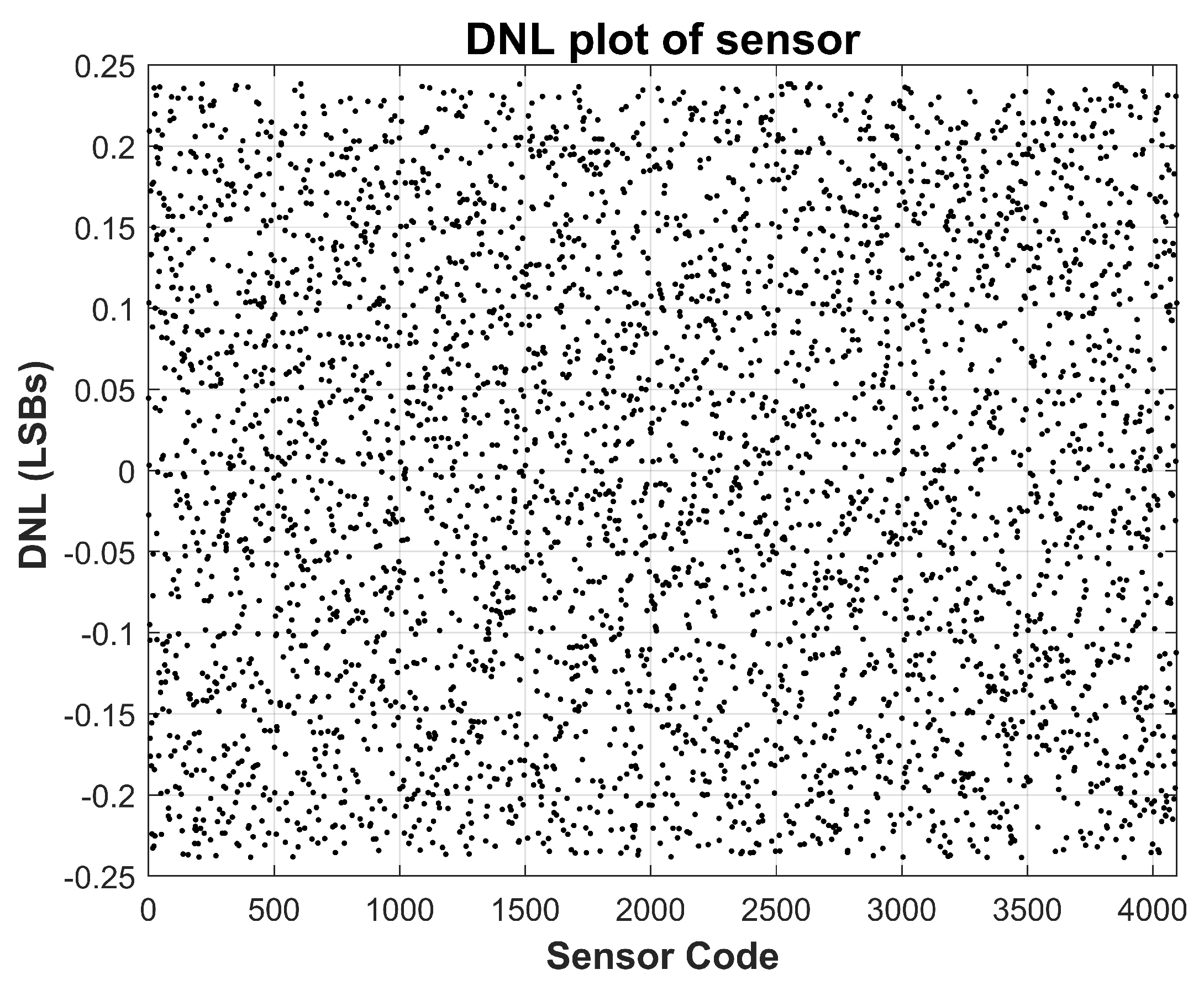

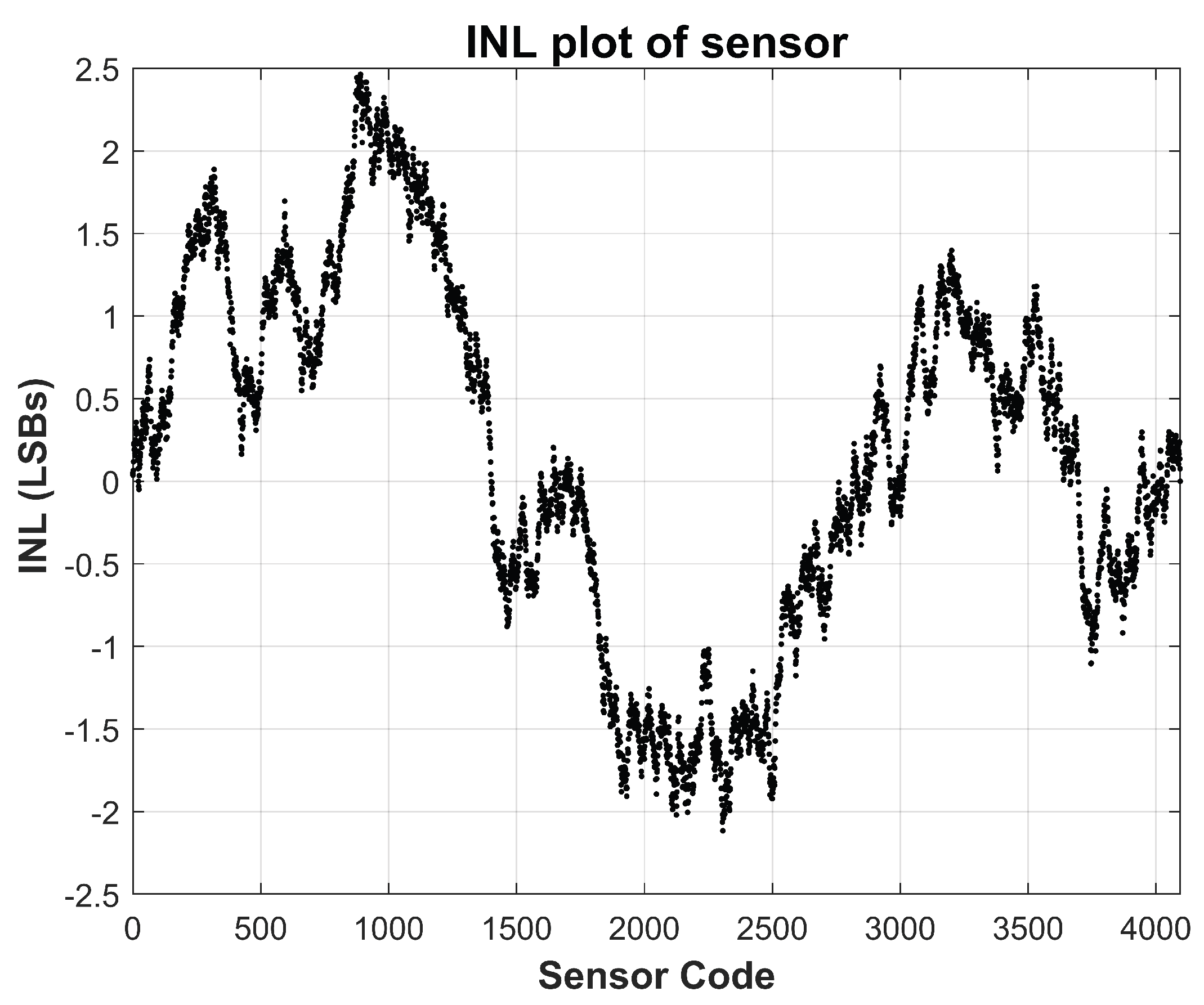

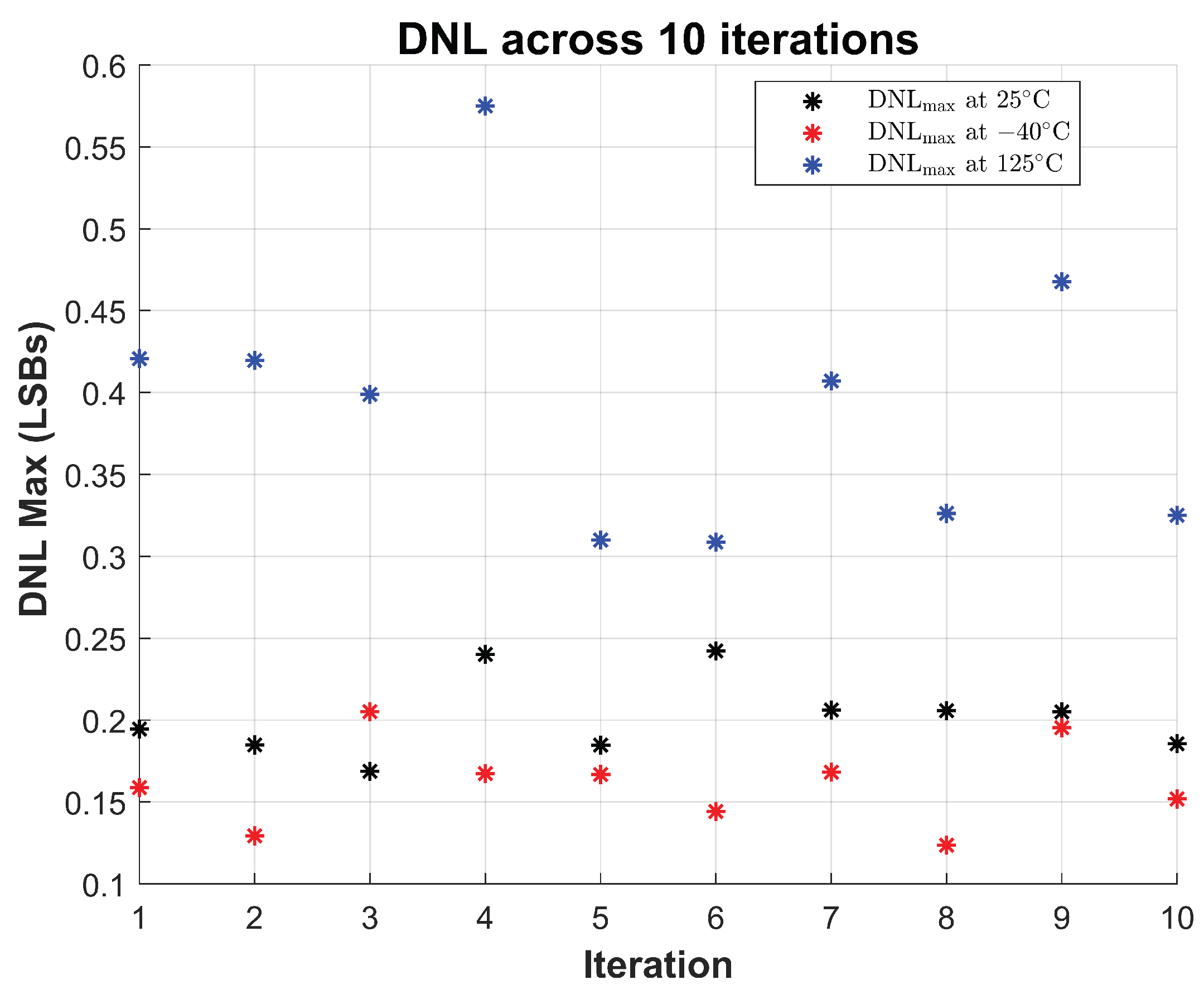

4.2. Measured Results

5. Discussion

5.1. Key Contributions and Strengths

5.2. Limitations

5.3. Comparison with Prior Work

5.4. Applications

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- AEC-Q100: Failure Mechanism Based Stress Test Qualification for Integrated Circuits, Automotive Electronics Council, Rev. H, 2014. [Online]. Available: https://studylib.net/doc/25765898/aec-q100-rev-h-base-document.

- E. Ferrati, “The reliability of the integrated circuits in automotive industry,” in Proc. IEEE Int. Workshop on Defect and Fault Tolerance in VLSI Systems (DFTVS), Venice, Italy, 1993, pp. 125–126. [CrossRef]

- Q. Zhang, X. Li, T. Zu, and R. Kang, “Belief reliability: A scientific exploration of reliability engineering,” J. Syst. Eng. Electron., vol. 35, no. 3, pp. 619–643, Jun. 2024. [CrossRef]

- P. Cheng, L.-F. Mao, W.-H. Shen, and Y.-L. Yan, “Electromigration failures in integrated circuits: A review of physics-based models and analytical methods,” Electronics, vol. 14, no. 15, Art. no. 3151, 2025. [CrossRef]

- K. Technologies, “Understanding the importance of leakage current measurement in advanced technology nodes,” Keysight Technologies, Tech. Overview 5990-9804, 2024. [Online]. Available: https://www.keysight.com/us/en/assets/7018-03320/technical-overviews/5990-9804.

- E. N. Darko, K. Bhatheja, D. Adjei, M. Strong, and D. Chen, “On-chip monitoring of Time-Dependent Dielectric Breakdown (TDDB) using a novel leakage current sensor with digital output,” in Proc. IEEE Int. Integrated Reliability Workshop (IIRW), South Lake Tahoe, CA, USA, 2023, pp. 1–6. [CrossRef]

- H. Zhou et al., “TDDB reliability in gate-all-around nanosheet,” in Proc. IEEE Int. Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2021, pp. 1–6. [CrossRef]

- C.-Y. Lin et al., “Reliability characteristics of a high density metal-insulator-metal capacitor on Intel’s 10+ process,” in Proc. IEEE Int. Reliability Physics Symposium (IRPS), Dallas, TX, USA, 2020, pp. 1–4. [CrossRef]

- D. J. M. Hamada and W. J. Roesch, “Reliability studies on thin metal-insulator-metal (MIM) capacitors,” in Proc. ROCS Workshop—Reliability of Compound Semiconductors, Monterey, CA, USA, 2008, pp. 57–72. 72. [CrossRef]

- F. Chen et al., “Reliability characterization of BEOL vertical natural capacitor using copper and low-k SiCOH dielectric for 65nm RF and mixed-signal applications,” in Proc. IEEE Int. Reliability Physics Symposium (IRPS), San Jose, CA, USA, 2006, pp. 490–495. [CrossRef]

- A. H. Fischer et al., “TDDB robustness of highly dense 65nm BEOL vertical natural capacitor with competitive area capacitance for RF and mixed-signal applications,” in Proc. IEEE Int. Reliability Physics Symposium (IRPS), Phoenix, AZ, USA, 2008, pp. 126–131. [CrossRef]

- C. LaRow, Z. Chbili, S. F. Yap, A. Kerber, and T. Nigam, “Fast TDDB monitoring for BEOL interconnect dielectrics,” in Proc. IEEE Int. Integrated Reliability Workshop (IIRW), South Lake Tahoe, CA, USA, 2017, pp. 1–4. [CrossRef]

- J. Keane, S. Venkatraman, P. Butzen, and C. H. Kim, “An Array-Based Test Circuit for Fully Automated Gate Dielectric Breakdown Characterization,” IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 19, no. 5, pp. 787–795, May 2011. [CrossRef]

- H. Nan and K. Choi, “TDDB Monitoring and Compensation Circuit Design for Deeply Scaled CMOS Technology,” IEEE Transactions on Device and Materials Reliability, vol. 13, no. 1, pp. 18–25, Mar. 2013. [CrossRef]

- K. Bhatheja, X. Jin, M. Strong and D. Chen, “Fast Gate Leakage Current Monitor With Large Dynamic Range,” IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 68, no. 5, pp. 1690–1694, May 2021. [CrossRef]

- Karimpour, S.; Sekyere, M.; Bruce, I.; Darko, E.N.; Chen, D.; McAndrew, C.C.; Garrity, D.; Jin, X.; Hatirnaz, I.; He, C. Direct Current to Digital Converter (DIDC): A Current Sensor. Sensors 2024, 24, 6789. [CrossRef]

- E. N. Darko, S. Karimpour, D. Adjei, K. Bhatheja, and D. Chen, “Ultra-low leakage current sensor with large dynamic range,” IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 72, no. 11, pp. 1650–1654, Nov. 2025. [CrossRef]

- E. N. Darko, S. Karimpour, D. Adjei, K. Tamakloe, and D. Chen, “A simple monitor for tracking leakage current in capacitors for reliability assessment,” in Proc. IEEE Microelectronics Design & Test Symposium (MDTS), Albany, NY, USA, 2025, pp. 1–6. [CrossRef]

- Texas Instruments, “OPA392: 36-V, Low Offset, Low-Drift, RRO, Precision Op Amp,” Product Datasheet, Sep. 2022 [Online]. Available: https://www.ti.com/product/OPA392.

- Microchip Technology Inc., MCP4821/22: 12-Bit DAC with SPI Interface and Internal Reference, DS22244C, 2020. [Online]. Available: https://ww1.microchip.com/downloads/en/DeviceDoc/22244c.pdf.

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).