Submitted:

11 January 2025

Posted:

13 January 2025

You are already at the latest version

Abstract

Keywords:

1. Introduction

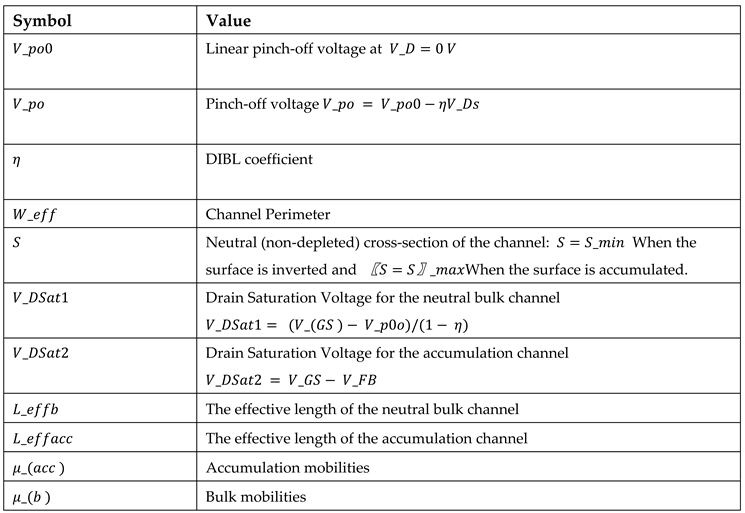

2. Mathematical Modelling of JLFET

3. Theoretical and Simulation Framework

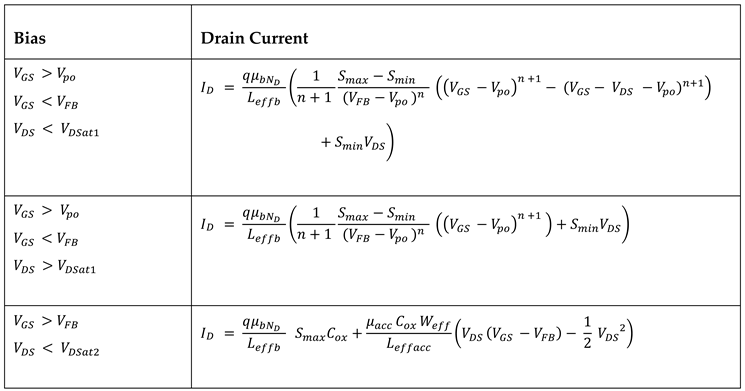

4. Device Structure of JLFET with III-V Materials

4.1. Properties of AlGaAs

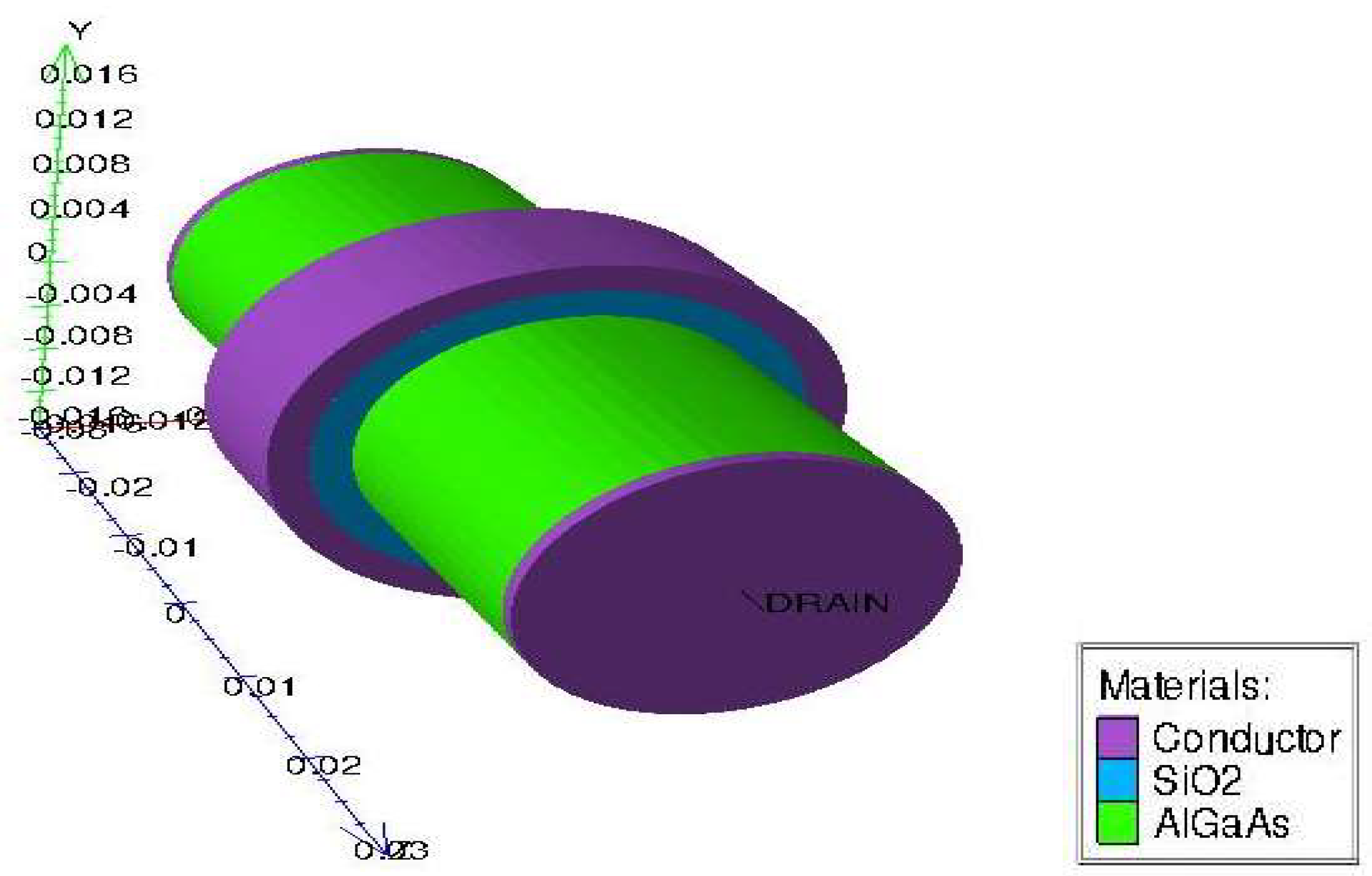

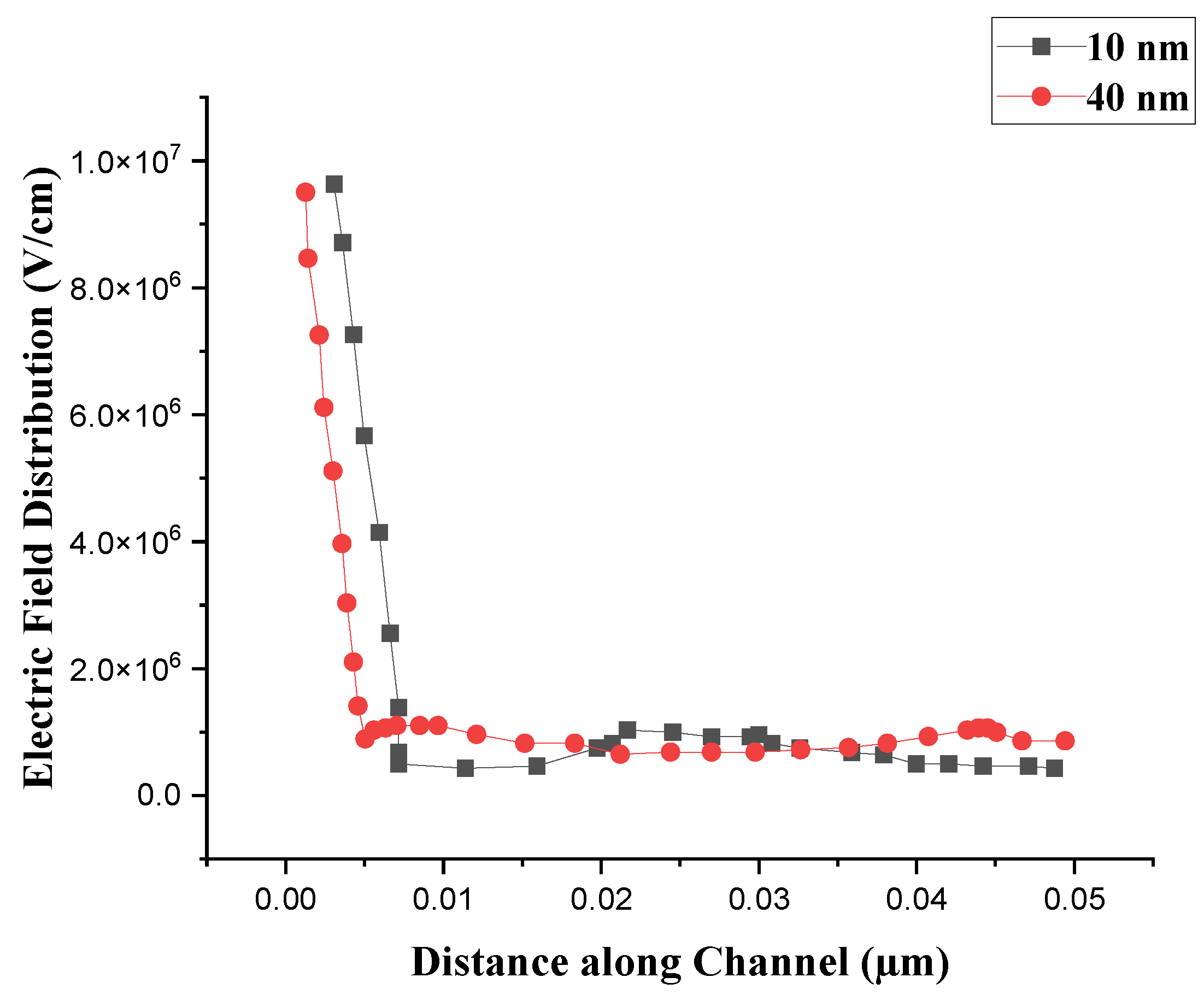

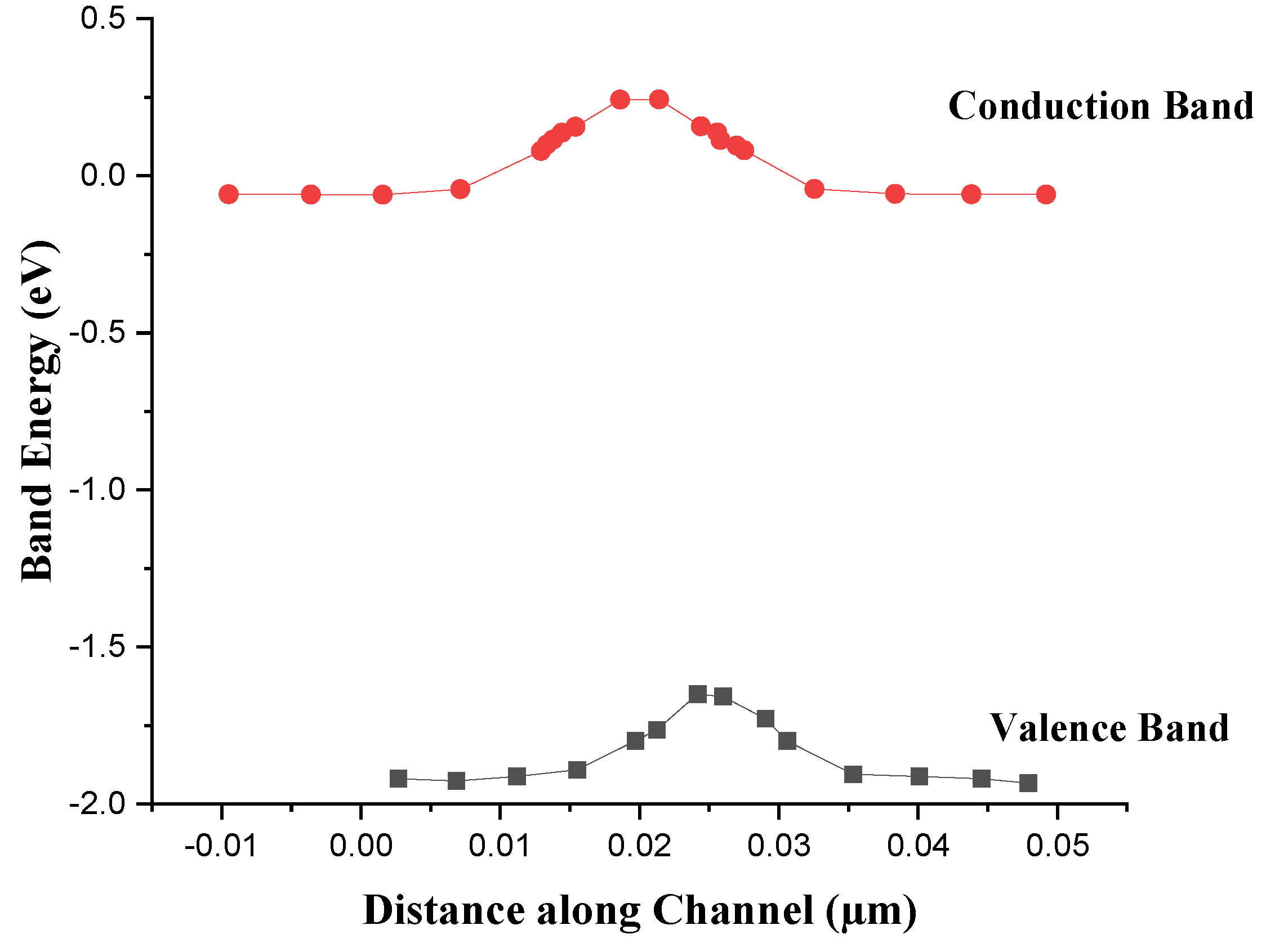

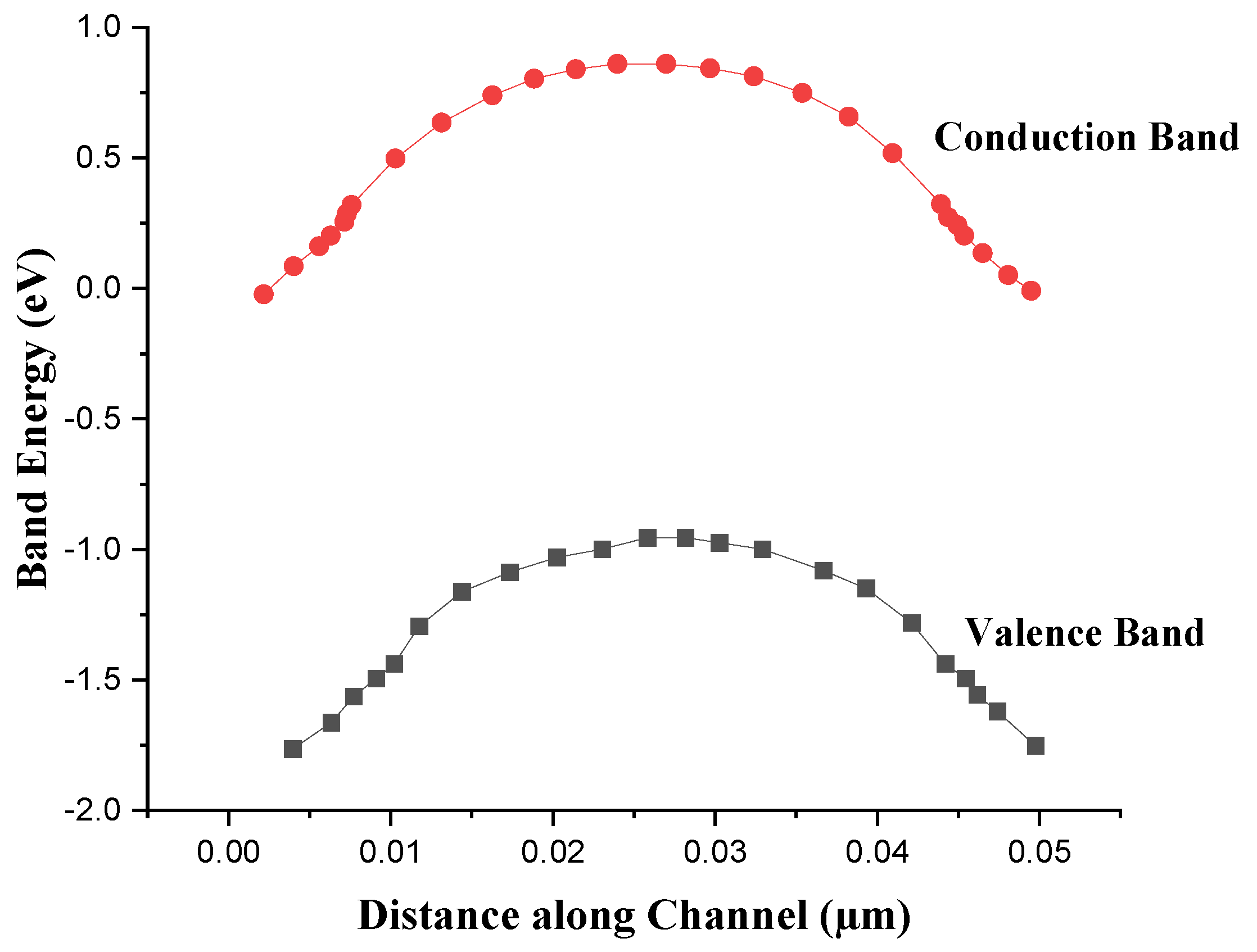

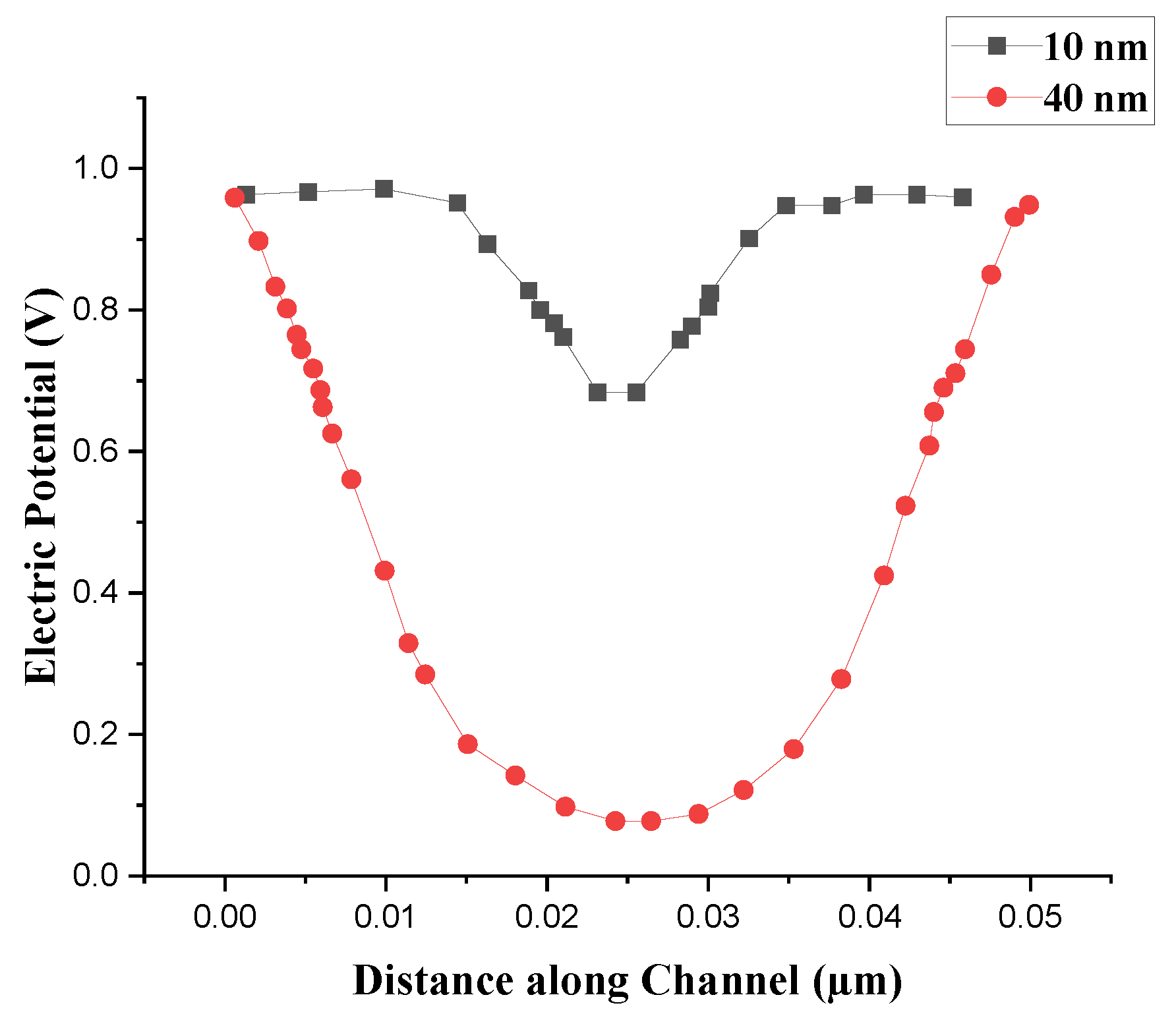

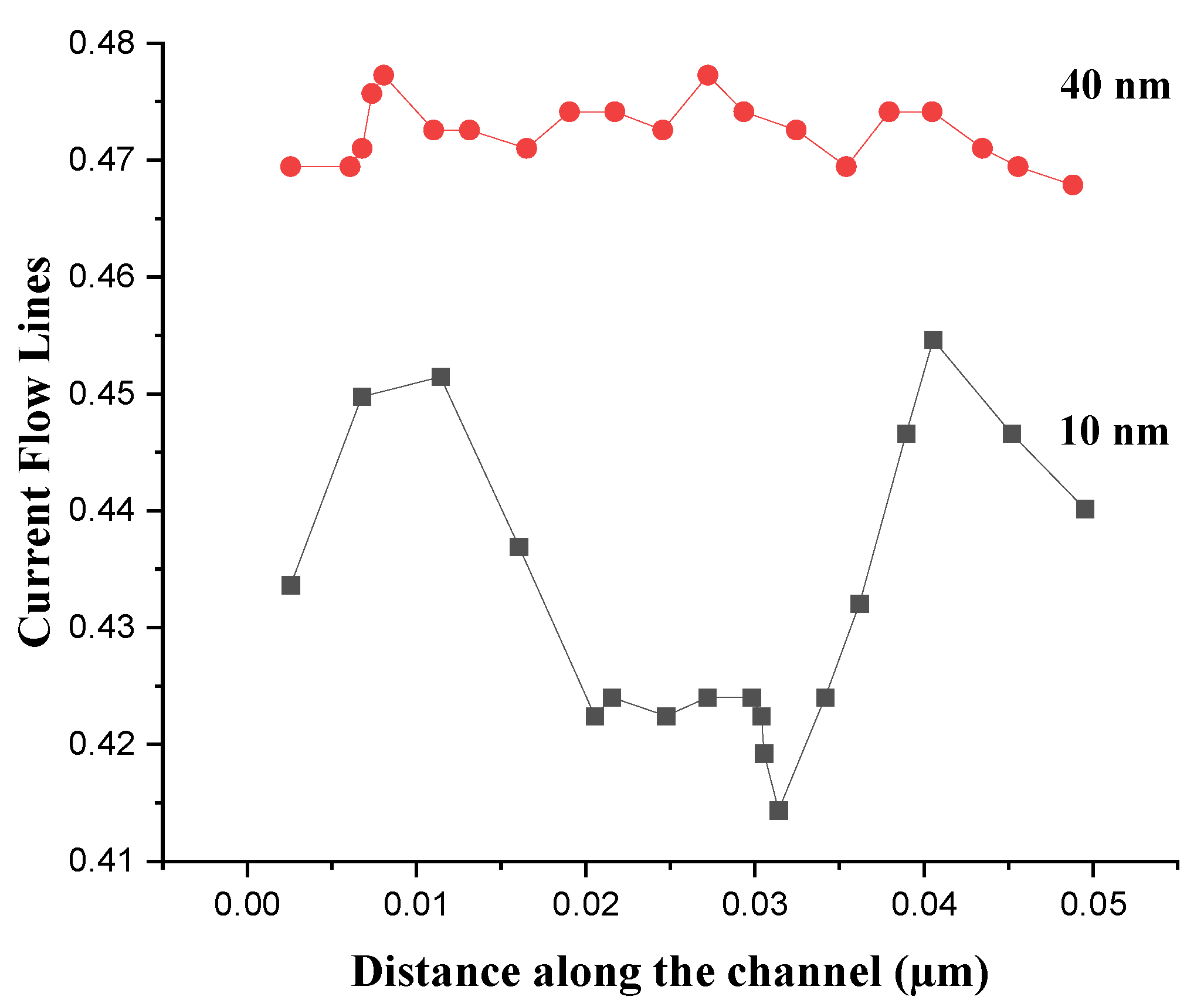

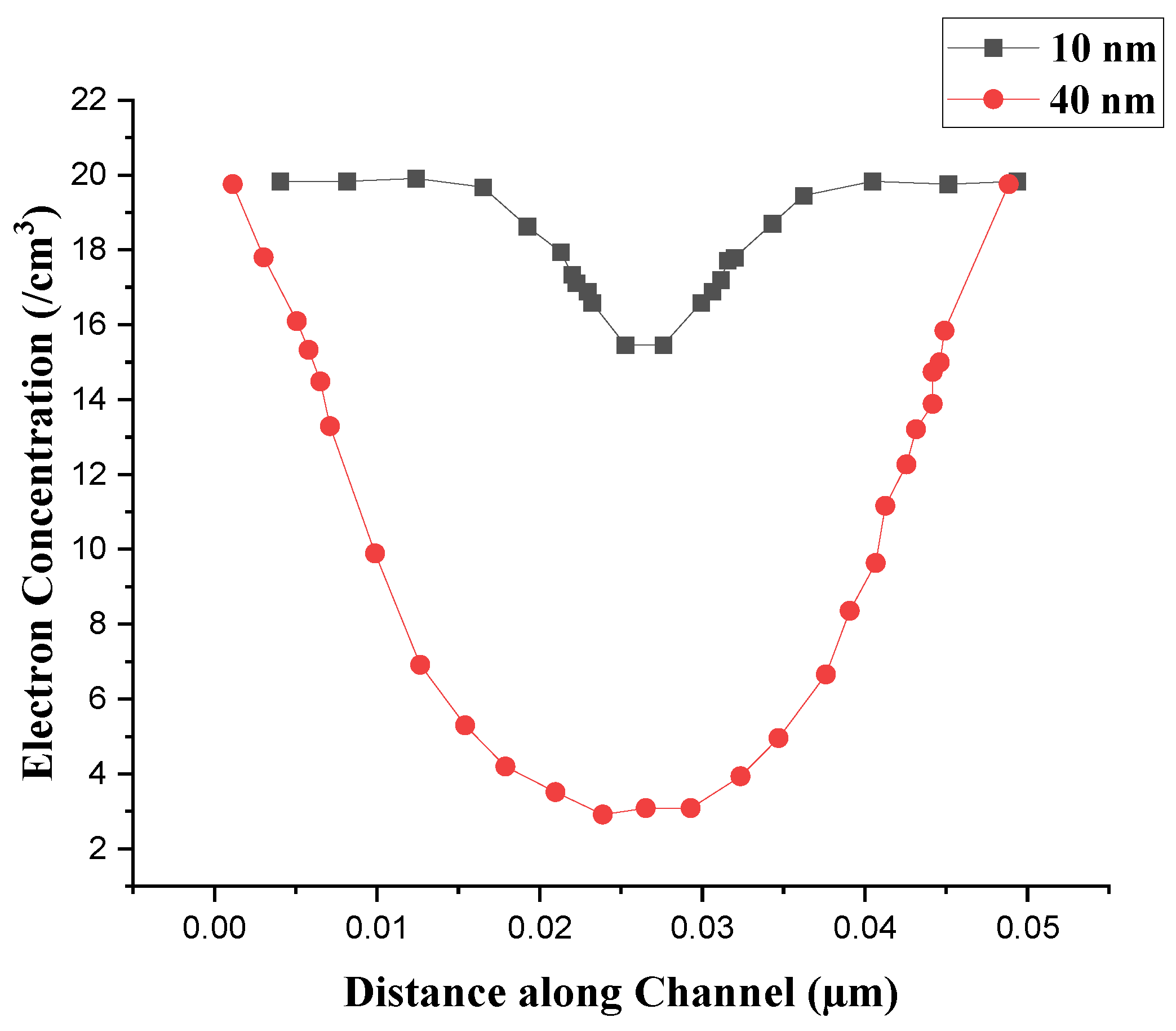

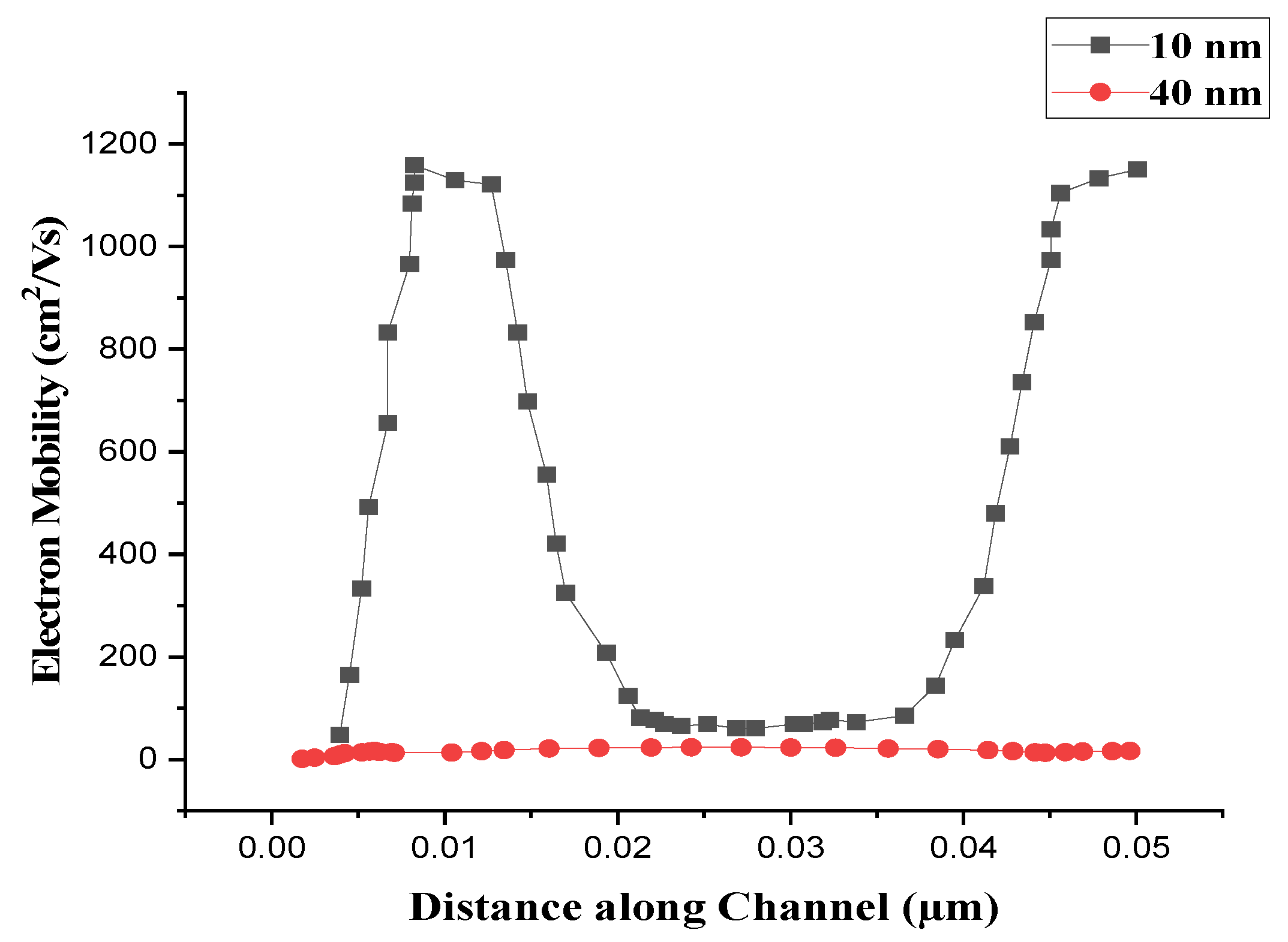

5. Results and Discussion

5.1. Comparative Study of Subthreshold Analysis of JLFET with Different III-V Materials

Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| JLFET | Juncionless field effect transistor |

| SCEs | Short channel effects |

| DIBL | Drain-induced barrier lowering |

| SS | Subthreshold slope |

| CTs | Conventional Transistors |

| NCTs | Non-conventional Transistors |

| ITRS | International Technology Roadmap for Semiconductors |

| SOI | Silicon on Insulator |

| FDSOI | Fully depleted silicon on insulator |

| PDSOI | Partially depleted silicon on insulator. |

| NCEs | Narrow channel effects |

References

- Tigelaar, H. How Transistor Area Shrank by 1 Million Fold. Springer; 2020.

- Veendrick, H. J. M. Nanometer CMOS ICs: from basics to ASICs. Basics to ASICs; 2017, 1-611.

- Dhiman, R.; Chandel, R. Nanoscale VLSI: Devices, Circuits and Applications. 2020. Vol 319. Springer Nature.

- Chen, W.K. The VLSI Handbook. CRC Press; 2018.

- Bin Ismail, R.; Ahmadi, M.T.; Anwar, S. Adv Nanoelectron 2013. Vol. 424. CRC press.

- Moore, G. E. Progress in digital integrated electronics. IEDM Tech. Digest 1975, 21, 11–13. [Google Scholar]

- Cristoloveanu, S. Fully Depleted Silicon-on-Insulator: Nanodevices, Mechanisms and Characterization. Elsevier 2021.

- Ranka, D.; Rana, A. K.; Yadav, R. K.; Yadav, K.; Giri, D. Performance evaluation of FD-SOI Mosfets for different metal gate work function. International Journal of VLSI Design & Communication Systems (VLSICS), 2011, 2, 11–24. [Google Scholar]

- Bhoir, M.S.; Mohapatra, N.R. Effects of scaling on analog FoMs of UTBB FD-SOI MOS transistors: a detailed analysis. IEEE Trans Electron Devices. 2020, 67, 3035–3041. [Google Scholar] [CrossRef]

- Kilchytska, V.; Makovejev, S.; Khairuddin, M. Perspectives of UTBB FD SOI MOSFETs for analog and RF applications. In: Nazarov AN (Alexei, N.; Kilchytska ,V.; eds. Functional Nanomaterials and Devices for Electronic Sensors and Energy Harvesting., Springer, 2014, 27–46.

- Md Arshad, M. K.; Kilchytska, V.; Emam, M.; Andrieu, F.; Flandre, D.; Raskin, J.P. Effect of parasitic elements on UTBB FD SOI MOSFETs RF figures of merit. Solid State Electron. 2014, 97, 38–44. [Google Scholar] [CrossRef]

- Balestra, F.; Cristoloveanu, S. ; Benachir, M; Brini, J. ; Elewa, T. Double Gate Silicon-on-Insulator transistor with volume inversion: A new device with greatly enhanced performance, IEEE Transactions in Electron Device Letters 1987, 8, 410–412. [Google Scholar]

- Frank, D.; Laux, S.; Fischetti, M. Montecarlo simulation of 30 nm dual-gate MOSFET: how far can silicon go? IEDM Technical Digest 1992, 553. [Google Scholar]

- Colinge, J. P. The SOI MOSFET: from Single Gate to Multigate, in FinFETs and Other Multigate Transistors, 2008, Ed., Springer US, pp. 1–48.

- Hisamoto, D.; Wen-Chin, L.; Kedzierski, J. ; Takeuchi, H; Asano, K. ; Kuo, C. FinFET-a self-aligned double-gate MOSFET scalable to 20 nm, IEEE Transactions on Electron Devices 2000, 47, 2320–2325. [Google Scholar]

- Tang, S. H.; Chang, L.; Lindert, N.; Yang-Kyu, C.; Wen-Chin, L.; Xuejue, H. FinFET-a quasi-planar double-gate MOSFET, Digest of Technical Papers, ISSCC, IEEE International Conference in Solid-State Circuits, 2001, pp. 118–119.

- Jooyoung, S.; Bo Y.; Yu Y.; Yuan, T. A Review on Compact Modelling of Multiple Gate MOSFETs,"Circuits and Systems I: Regular Papers, IEEE Transactions on Electron Devices 2009, 56, 1858–1869.

- Anvarifard, M. K.; Ramezani, Z.; Amiri, I. S.; Nejad, A. M. A nanoscale-modified band energy junctionless transistor with considerable progress on the electrical and frequency issue. Mater Sci Semicond Process. 2020, 107, 104849. [Google Scholar] [CrossRef]

- Colinge, J. P.; Lee, C. W.; Afzalian, A.; Akhavan, N. D.; Yan, R.; Ferain, I.; Murphy, R. Nanowire transistors without junctions. Nature nanotechnology, 2010, 5, 225–229. [Google Scholar] [CrossRef]

- Colinge, J. P. (2012). Junctionless transistors. In 2012 IEEE International Meeting for Future of Electron Devices, Kansai.

- Srivastava, P.; Upadhyaya, A.; Yadav, S.; Negi, C. Performance Evaluation of Junctionless Cylindrical Gate-All-Around FET for Low Power Applications. Semiconductor Science and Information Devices 2024, 5, 1–10. [Google Scholar] [CrossRef]

- Gnani, E.; Gnudi, A.; Reggiani, S.; Baccarani, G. Quasi-ballistic transport in nanowire field-effect transistors. IEEE Transactions on Electron Devices 2008, 55, 2918–2930. [Google Scholar] [CrossRef]

- Gnani, E.; Gnudi, A.; Reggiani, S.; Luisier, M.; Baccarani, G. Band effects on the transport characteristics of ultra scaled snw-fets. IEEE Transactions on Nanotechnology 2008, 7, 700–709. [Google Scholar] [CrossRef]

- Lenzi, M.; Palestri, P.; Gnani, E.; Reggiani, S.; Gnudi, A.; Esseni, D.; Baccarani, G. Investigation of the transport properties of silicon nanowires using deterministic and Monte Carlo approaches to the solution of the Boltzmann transport equation. IEEE Transactions on Electron Devices 2008, 55, 2086–2096. [Google Scholar] [CrossRef]

- Poli, S.; Pala, M. G.; Poiroux, T. Full quantum treatment of remote Coulomb scattering in silicon nanowire FETs. IEEE Transactions on Electron Devices 2009, 56, 1191–1198. [Google Scholar] [CrossRef]

- Colinge, J. P.; Gao, M. H.; Romano-Rodriguez, A; Maes, H.; Claeys, C. Silicon-on-insulator gate-all-around device Tech. Dig. IEDM, 1990 pp 595–8.

- Colinge, J. P.; Baie, X.; Bayot, V.; Grivei, E. A silicon-on-insulator quantum wire Solid State Electron 1996, 39, 49–51.

- Duarte, J. P.; Choi, S. J.; Moon, D. I.; Choi, Y. K. Simple analytical bulk current model for long-channel double-gate junctionless transistors IEEE Electron Device Lett. 2011, 32 704–6.

- Colinge, J. P. Nanowire Transistors Without Junctions Tyndall National Institute University College Cork. www.tyndall.ie.

- Chi-Woo Lee, Aryan Afzalian,Junctionless MuGFETs Tyndall National Institute, Lee Maltings, Prospect Row, Cork, Ireland.

- Riel, H.; Wernersson, L. E.; Hong, M.; del Alamo, J. A. "III–V compound semiconductor transistors—From planar to nanowire structures," MRS Bull., 2014 vol. 39, no. 8, pp. 668–677.

- Chang, E. Y.; Kuo, C. I.; Hsu, H. T.; Chiang, C. Y.; Miyamoto, Y. "InAs thin-channel high-electron-mobility transistors with very high current-gain cutoff frequency for emerging submillimeter-wave applications," Appl. Phys. Exp. 2013, vol. 6, no. 3, p. 034001, Mar.

- del Alamo, J. A. "Nanometre-scale electronics with III–V compound semiconductors," Nature, 2011, vol. 479, no. 7373, pp. 317–323, Nov.

- Nobrega, R.; Fonseca, Y.; A Costa, R.; Duarte, U. Comparative Study on the Performance of Silicon and III-V Nanowire Gate-All-Around Field-Effect Transistors for Different Gate Oxides. In Proceedings of the XIII Workshop on Semiconductors and Micro & Nano Technology, Brazil, 19–20 April 2018.

- Kumar, P.; Singh, S.; Singh, N.P.; Modi, B.; Gupta, N. Germanium v/s silicon Gate-all-around junctionless nanowire transistor. In Proceedings of the 2014 2nd International Conference on Devices, Circuits and Systems (ICDCS), Coimbatore, India, 6–8 March 2014; pp. 1–5.

- Arefín, U.A. Impact of Temperature on Threshold Voltage of Gate-All-Around Junctionless Nanowire Field-Effect Transistor. ULAB J. Sci. Eng. 2015, 6, 14–18. [Google Scholar]

- Ghosh, S.; Jana, A.; Agnihotri, A. K.; Kundu, S.; Das, D.; Sarkar, S. K. DC and analog/RF performance comparison of renovated GAA JLFET structures. In 2022 IEEE VLSI Device Circuit and System (VLSI DCS) 2022. (pp. 80–84). IEEE.

- Kamath, A.; Chen, Z. X.; Shen, N.; Li, X.; Singh, N.; Lo, G. Q.; Kwong, D. L. Junctionless CMOS transistors with independent double gates. International Journal of Information and Electronics Engineering 2013, 3, 13. [Google Scholar]

- Basu, S.; Singh, P. K.; Sze, P. W.; Wang, Y. H. AlGaAs/InGaAs metal-oxide-semiconductor pseudomorphic high-electron-mobility transistor with low temperature liquid phase deposited Al2O3 gate insulator. Journal of Applied Physics 2008, 104. [Google Scholar] [CrossRef]

- Han, M. H.; Chang, C. Y.; Jhan, Y. R.; Wu, J. J.; Chen, H. B.; Cheng, Y. C.; Wu, Y. C. Characteristic of p-type junctionless gate-all-around nanowire transistor and sensitivity analysis. Electron Device Letters, IEEE 2013, 34, 157–159. [Google Scholar] [CrossRef]

- Chau, R.; Datta, S.; Majumdar, A. Opportunities and challenges of III–V nanoelectronics for future high-speed, low-power logic applications, in Proc. IEEE Compound Semiconductor Integr. Circuit Symp., Oct./Nov. 2005, pp. 17–20.

- Baruah, R. K.; Paily, R. P. A Dual-Material Gate Junctionless Transistor With High-Spacer for Enhanced Analog Performance. IEEE Transactions on Electron Devices, 2014, 61, 123–128. [Google Scholar] [CrossRef]

- Lee, C. W.; Afzalian, A.; Yan, R.; Dehdashti, N.; Colinge, J. P. (2009). Junctionless MuGFETs. In Proceedings EUROSOI Conference, Vol. 195, pp. 21–22.

- Pearsall T. P.; Hirtz, J. P. "The carrier mobilities in Ga0.47In0.53As grown by organic-metallic CVD and liquid-phase epitaxy," J. Crystal Growth, vol. 54, no. 1, pp. 127–131 1981.

- Chau, R. et al., Benchmarking nanotechnology for high performance and low-power logic transistor applications, IEEE Trans. Nanotechnol. 2005, vol. 4, no. 2, pp. 153–158.

- Singh, P.; Singh, N.; Miao, J.; Park, W.T.; Kwong, D.L. Gate-all-around junctionless nanowire MOSFET with improved low-frequency noise behavior. IEEE Electron. Device Lett. 2011, 32, 1752–1754. [Google Scholar] [CrossRef]

- Song, Y.; Zhang, C.; Dowdy, R.; Chabak, K.; Mohseni, P. K.; Choi, W.; Li, X. III-V junctionless gate-all-around nanowire MOSFETs for high linearity low power applications. IEEE Electron Device Letters, (2014). 35, 324-326.

- Lee, C. W.; Ferain, I.; Afzalian, A.; Yan, R.; Akhavan, N. D.; Razavi, P.; Colinge, J. P. Performance estimation of junctionless multigate transistors. Solid-State Electronics 2010, 54, 97–103. [Google Scholar] [CrossRef]

- Rauly, E.; Iñiguez, B.; Flandre, D. Investigation of deep submicron single and double gate SOI MOSFETs in accumulation mode for enhanced performance, Electrochem. Solid-State Lett. 2001, 4, G28–G30. [Google Scholar] [CrossRef]

- Iñíguez, B.; Gentinne, B.; Dessard, V.; Flandre, D. A physically-based continuous model for accumulation-mode SOI pMOSFETs, IEEE Trans. Electron Devices, 1999, 46, 2295–2303. [Google Scholar] [CrossRef]

- Chattopadhyay, D.; Sutradhar, S. K.; Nag, B. R. Electron transport in direct-gap III–V ternary alloys, J. Phys. C, Solid State Phys. 1981, 14, 891–908. [Google Scholar] [CrossRef]

- Talukdar, A.; Raibaruah, A. K.; Sarma, K. C. D. Dependence of electrical characteristics of Junctionless FET on body material. Procedia computer science 2020, 171, 1046–1053. [Google Scholar] [CrossRef]

- Rout, S. P.; Dutta, P. Impact of high mobility III-V compound material of a short channel thin-film SiGe double gate junctionless MOSFET as a source. Engineering Reports 2020, 2, e12086. [Google Scholar] [CrossRef]

- Cho, S.; Park, S. H.; Park, B. G.; Harris, J. S. Silicon-compatible bulk-type compound junctionless field-effect transistor. In 2011 International Semiconductor Device Research Symposium (ISDRS) 2011, (pp. 1–2). IEEE.

| Parameters | For Cylindrical Gate-All-Around JLFET |

|---|---|

| Channel Material | Al0.30Ga0.60As, Aluminium Gallium Arsenide (in composite form) |

| Channel region with Doping Concentration | N-type – I019 cm-3 |

| Source region with Doping Concentration | N-type – I019 cm-3 |

| Drain region with Doping Concentration | N-type – I019 cm-3 |

| Gate material | P+ Polysilicon |

| Gate Workfunction | 5.4 eV |

| Oxide Permittivity | 3.9 |

| Channel Length | Ranges from 10 nm to 60 nm |

| Oxide Thickness | 2 nm (radius) |

| Semiconductor (Si-Substrate) Thickness | 10 nm (radius) |

| Device Length | 60 nm |

| Crystal structure | Zinc Blende |

| Number of atoms in 1 cm3 | (4.42-0.17x)·1022 |

| Debye temperature | 370+54x+22x2 K |

| Density | 5.32-1.56x g·cm-3 |

| Dielectric constant (static) | 12.90-2.84x |

| Dielectric constant (high frequency) | 10.89-2.73x |

| Effective electron mass (me) | 0.063+0.083x mo (x<0.45) |

| Density-of-states electron mass (mcd) | 0.85-0.14x mo (x>0.45) |

| Conductivity effective mass (mcc) | 0.26 mo (x>0.45) |

| Effective hole masses (mh) | 0.51+0.25x mo |

| Effective hole masses (mlp) | 0.082+0.068x mo |

| Electron affinity | 4.07-1.1x eV (x<0.45) |

| 3.64-0.14x eV (x>0.45) | |

| Lattice constant | 5.6533+0.0078xÅ |

| Breakdown field | ≈(4÷6) ·105 V/cm |

| Mobility electrons | |

| 0<x<0.45 | 8·103-2.2·104x+104·x2 cm2 V-1 s-1 |

| 0.45<x<1 | -255+1160x-720x2 cm2 V-1 s-1 |

| Mobility holes | 370-970x+740x2 cm2 V-1 s-1 |

| Diffusion coefficient electrons | |

| 0<x<0.45 | 200-550x+250x2 cm2/s |

| 0.45<x<1 | -6.4+29x-18x2 cm2/s |

| Diffusion coefficient holes | 9.2-24x+18.5x2 cm2/s |

| Electron thermal velocity | |

| 0<x<0.4 | (4.4-2.1x)·105 m/s |

| 0.45<x<1 | 2.3·105 m/s |

| Hole thermal velocity | (1.8-0.5x)·105 m/s |

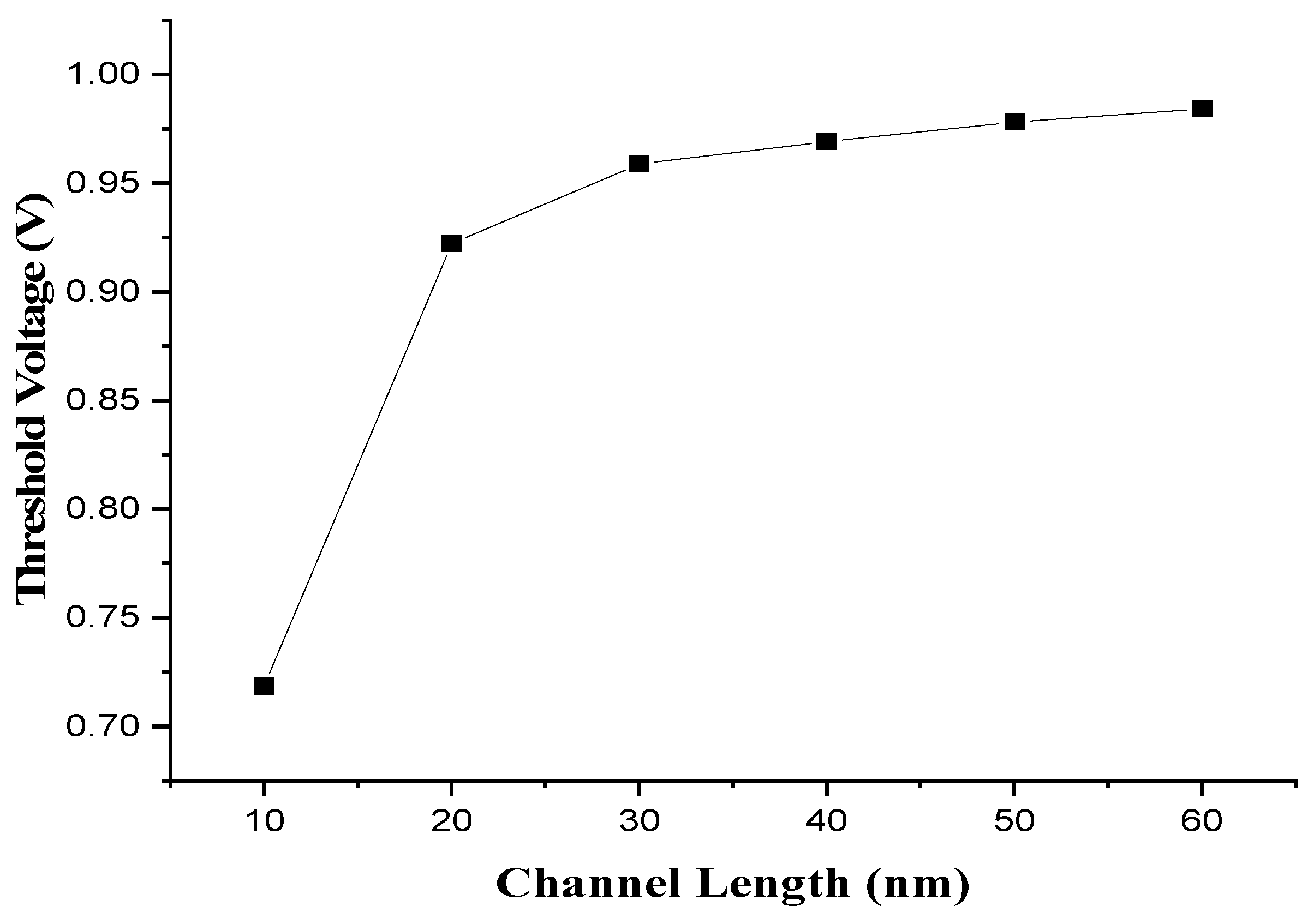

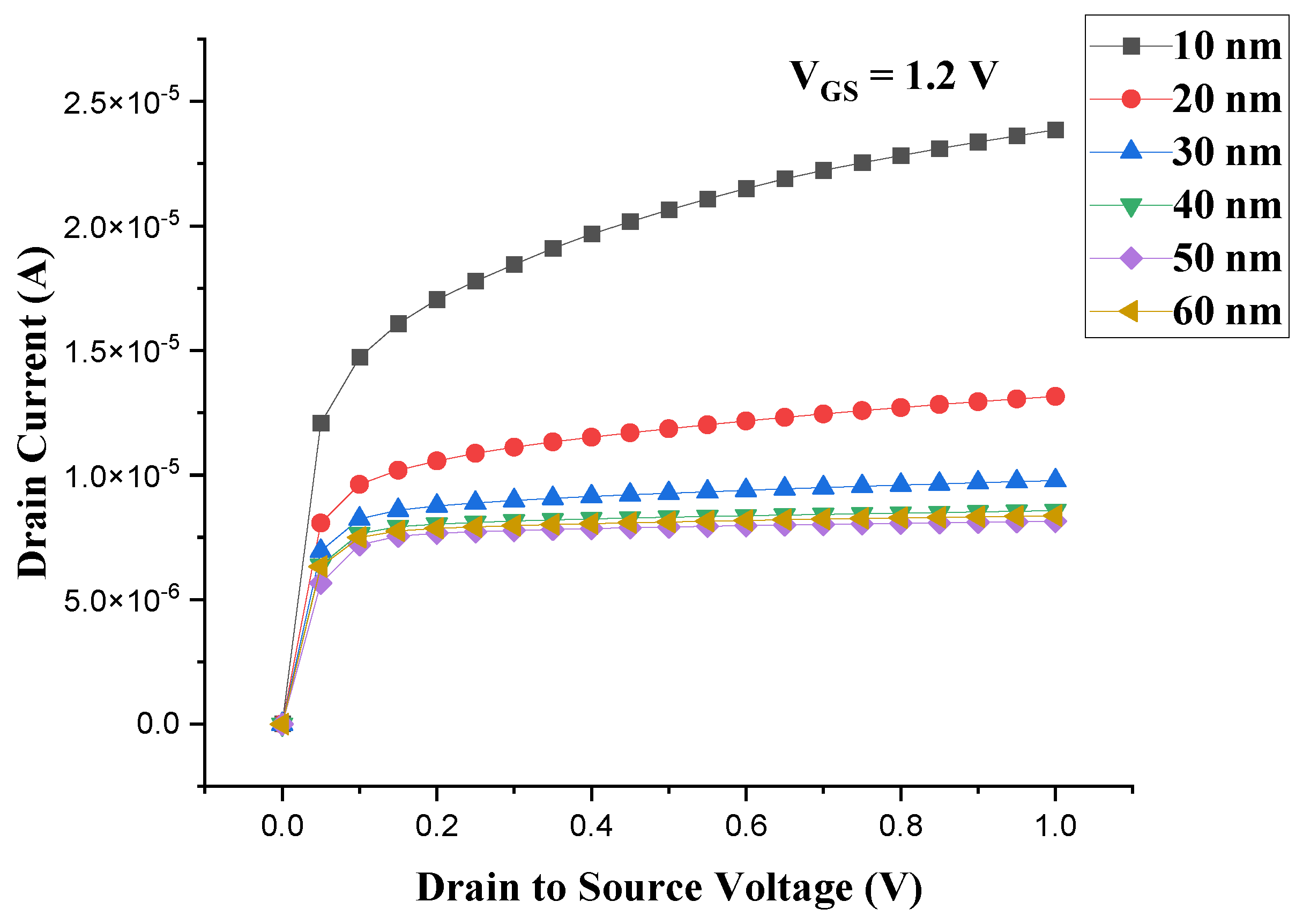

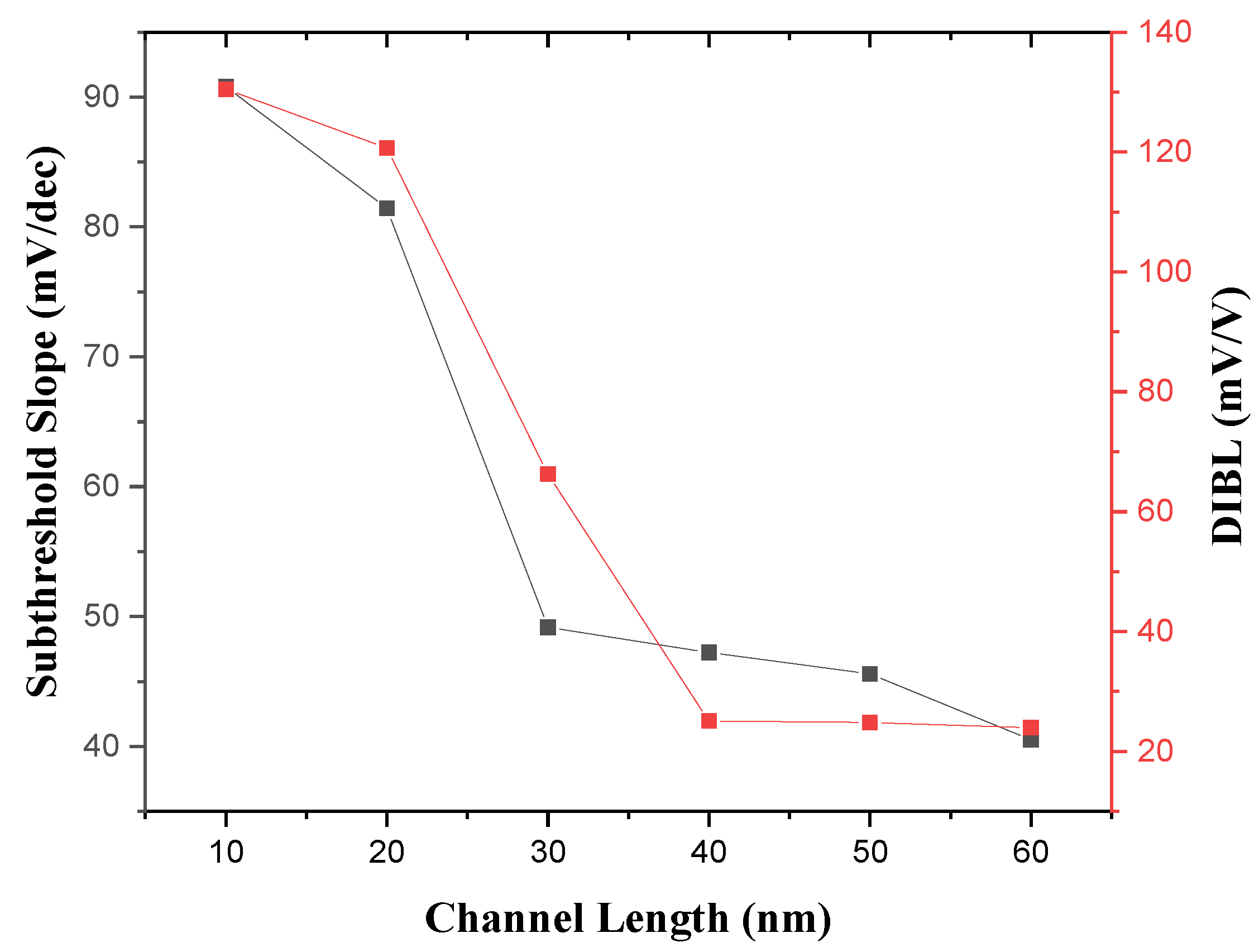

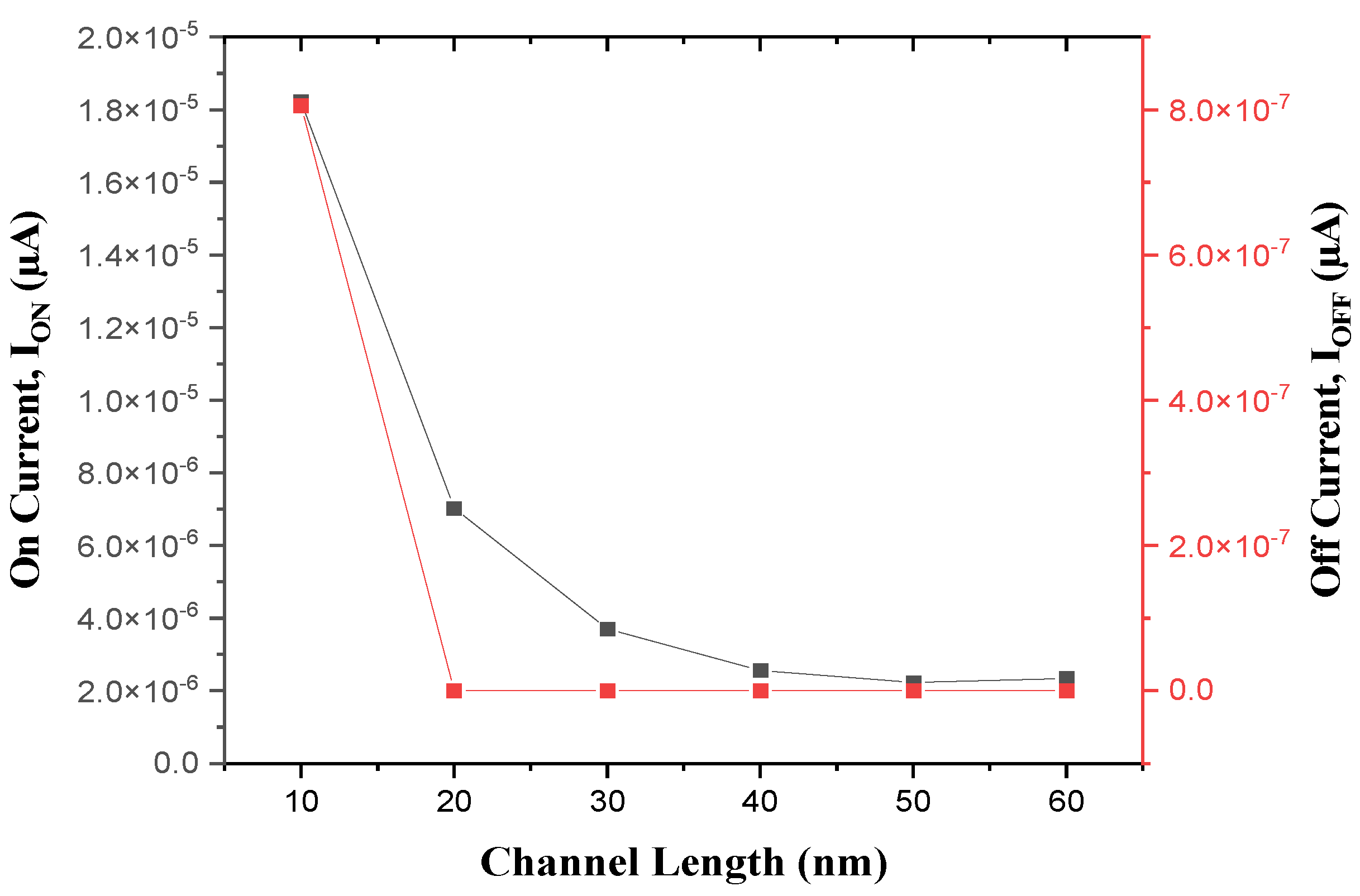

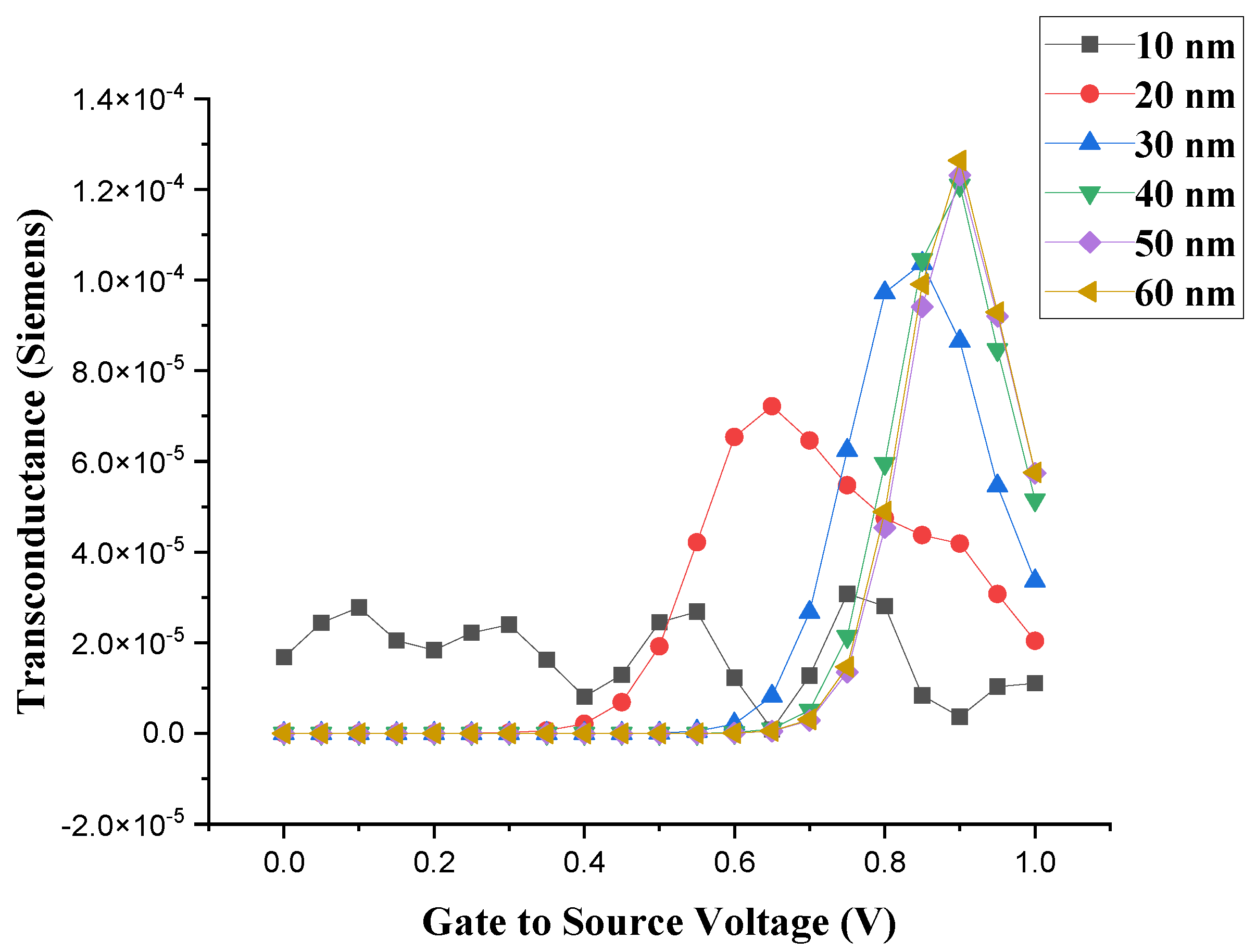

| Lg (nm) | Vth (V) | Saturation Slope (A) | Max. Drain Current (A) | SS (mV/dec) | DIBL (mV/V) | Ion (µA) | Ioff (µA) | Ion/Ioff |

|---|---|---|---|---|---|---|---|---|

| 10 | 0.71864309 | 4.8060692×10-6 | 2.38548734 ×10-5 |

90.811026 | 130.478984 | 1.82114482 ×10-5 |

8.0515476 ×10-7 |

22.61858 |

| 20 | 0.92221857 | 2.1114994 ×10-6 | 1.31566809×10-5 | 81.4501738 | 120.697472 | 7.02601295 ×10-6 |

3.0486378 ×10-14 |

230464043 |

| 30 | 0.95883678 | 8.447915 ×10-7 |

9.77385934×10-6 | 49.1701421 | 66.2491032 | 3.7020172 ×10-6 |

1.85712014 ×10-18 |

1.99341826×1012 |

| 40 | 0.9691365 | 4.629001 ×10-7 |

8.5672922 ×10-6 |

47.2267559 | 25.0701147 | 2.56180952 ×10-6 |

3.69007316 ×10-20 |

6.94243558×1013 |

| 50 | 0.97815102 | 4.1971784 ×10-7 |

8.33677822×10-6 | 45.5820223 | 24.8246716 | 2.22791721 ×10-6 |

1.77755482 ×10-21 |

1.25336062×1015 |

| 60 | 0.98420158 | 3.1932996 ×10-7 |

8.16522822×10-6 | 40.5020524 | 23.9363979 | 2.33849879 ×10-6 |

4.15367459 ×10-20 |

5.62995184×1013 |

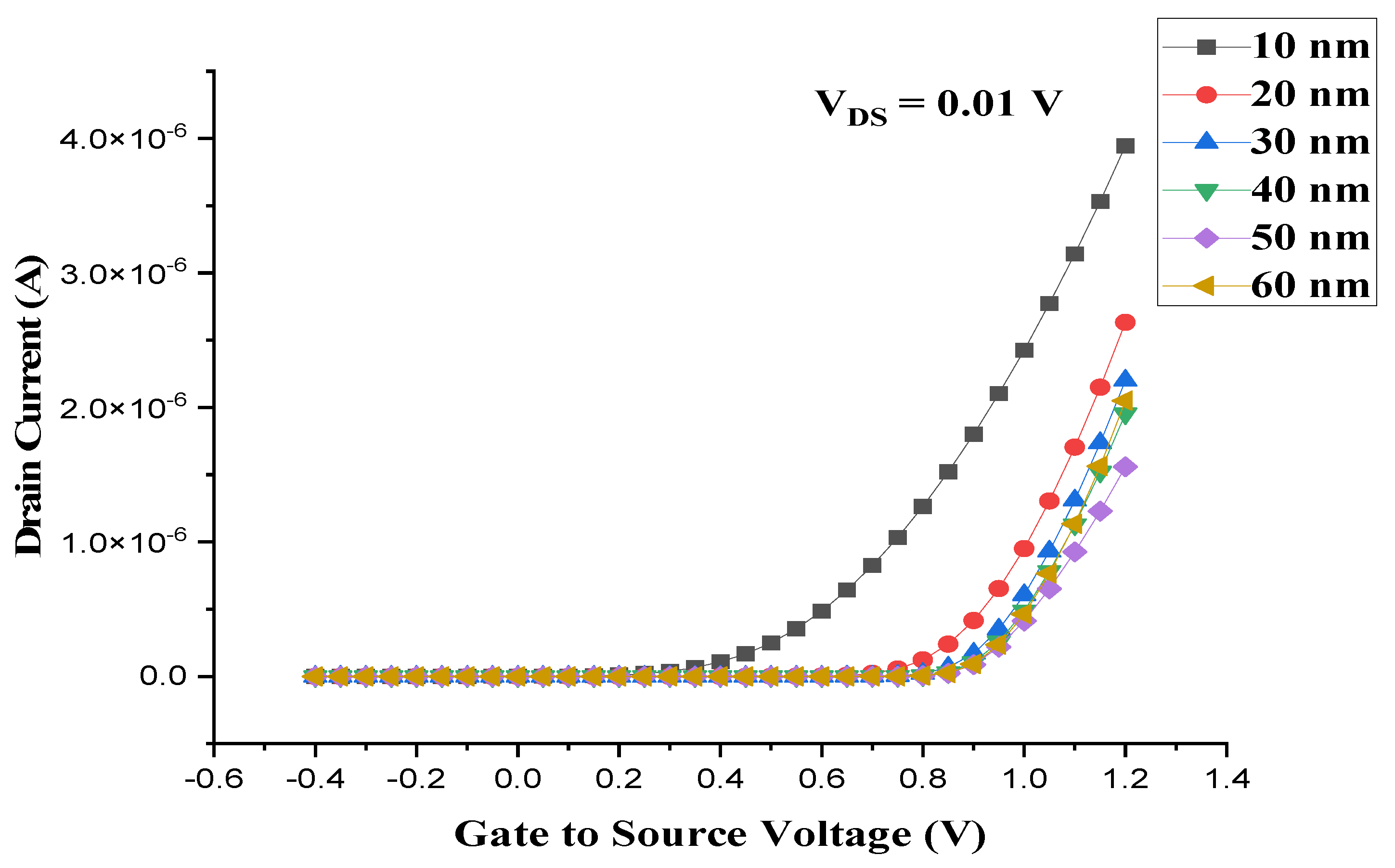

| Si and III-V Material | Vth (V) | Saturation Slope (A) | Max. Drain Current (A) | SS (mV/dec) | DIBL (mV/V) |

Ion (µA) | Ioff (µA) | Ion/Ioff |

|---|---|---|---|---|---|---|---|---|

| GaAs |

0.819608 | 6.41239 ×10-7 | 2.31345 ×10-5 |

64.47608 | 30.5962 | 12.7614 | 1.125467 ×10-9 |

1.133861 ×1010 |

| InP | 0.656255 | -3.1528 ×10-10 |

5.02586 ×10-6 | 66.8384 | 39.4156 | 4.28187 | 3.6750 ×10-5 |

116513.47 |

| AlGaAsP | 0.799256 | 1.01434 ×10-7 |

2.91153 ×10-6 |

64.44775 | 40.81138 | 1.61177 | 1.717025 ×10-10 |

9.386899 ×109 |

| GaN | 0.472639 | 3.99288 ×10-6 |

7.14924 ×10-5 |

68.34655 | 40.35768 | 4.91099 |

5.031638 ×10-3 |

9760.222 |

| InGaAsP | 0.656257 | -3.1528 ×10-10 |

5.02585 ×10-6 |

66.83845 | 39.41564 | 4.28188 | 3.675004 ×10-5 |

116513.47 |

| GaP | 0.552483 | 8.468 ×10-11 |

5.02435 ×10-6 |

67.84844 | 22.50066 | 4.42848 | 3.620443 ×10-4 |

12231.8586 |

| AlGaAs | 0.819837 | 6.4125 ×10-7 |

2.31344 ×10-5 |

64.47583 | 30.59605 | 1.27615 | 1.125457 ×10-9 |

1.133872 ×1010 |

| Al0.30Ga0.60As | 0.969136 | 4.6290 ×10-7 |

8.56729×10-6 | 47.22677 | 25.07014 | 2.56184 | 3.690073 ×10-14 |

6.942438 ×1013 |

| Al0.20Ga0.80As | 0.908568 | 5.19404×10-7 | 1.29049×10-5 | 47.30019 | 28.52392 | 5.42004 | 1.260631 ×10-18 |

4.299456 ×1012 |

| Device Architectures |

Authors | Materials | Lg (nm) |

SS (mV/dec) |

DIBL (mV/V) |

Ion (µA) | Ioff (µA) | Ion/Ioff |

|---|---|---|---|---|---|---|---|---|

| Cylindrical Gate-all-around JLFET (This work) | P. Srivastava et al. | GaAs |

40 | 64.47608 | 30.5962 | 12.7614 | 1.125467 ×10-9 |

1.133861 ×1010 |

| Cylindrical Gate-all-around JLFET (This work) | P. Srivastava et al. | Al0.30Ga0.60As | 40 | 47.22677 | 25.07014 | 2.56184 | 3.690073 ×10-14 |

6.942438 ×1013 |

| Cylindrical Gate-all-around JLFET (This work) | P. Srivastava et al. | Al0.20Ga0.80As | 40 | 47.30019 | 28.52392 | 5.42004 | 1.260631×10-18 | 4.299456 ×1012 |

| Symmetric Double Gate JLFET | Talukdar et al. [52] | GaAs | 30 | 65 | - | - | - | - |

| SiGe Double Gate Junctionless MOSFET | Rout et al. [53] |

GaSb | 20 | 59.78 | - | - | - | 7.52 ×1013 |

| Compound JLFET | Cho et al. [54] |

GaAs | 40 | 90 | - | - | - | About 108 |

Disclaimer/Publisher's Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).