Submitted:

25 October 2024

Posted:

28 October 2024

Read the latest preprint version here

Abstract

Keywords:

1. Introduction

- Chapter 2 - ’Domain Overview,’ introduces the reader to the mission of computers as the object of the study, provides an overview of the real-time operation systems (RTOS) usage challenges, and describes tools and needs of energy-saving solutions for embedded mission computers;

- Chapter 3 - ’Materials And Methods’ describes the platform for conducting the study experiment, defines a system model in the look of a power state machine, and describes the exact way of measuring reactivity and power consumption of different modes of operation;

- Chapter 4 - ’Results’ provides the obtained experiment results;

- Chapter 5 - ’Discussion’ describes and presents the obtained results applied to the proposed system model;

- Chapter 6 - ’Conclusion’ concludes the article by describing the novelty of the research and its further development.

2. Domain Overview

- Select an appropriate ready-to-use avionics platform (including a mission computer);

- Use microcontroller-specific vendor toolchain;

- Ensure that a real-time operation system is in place and can be easily adapted to the selected computation platform;

- Design and validate the required for the flight mission business logic (i.e. what exactly a UAV shall do).

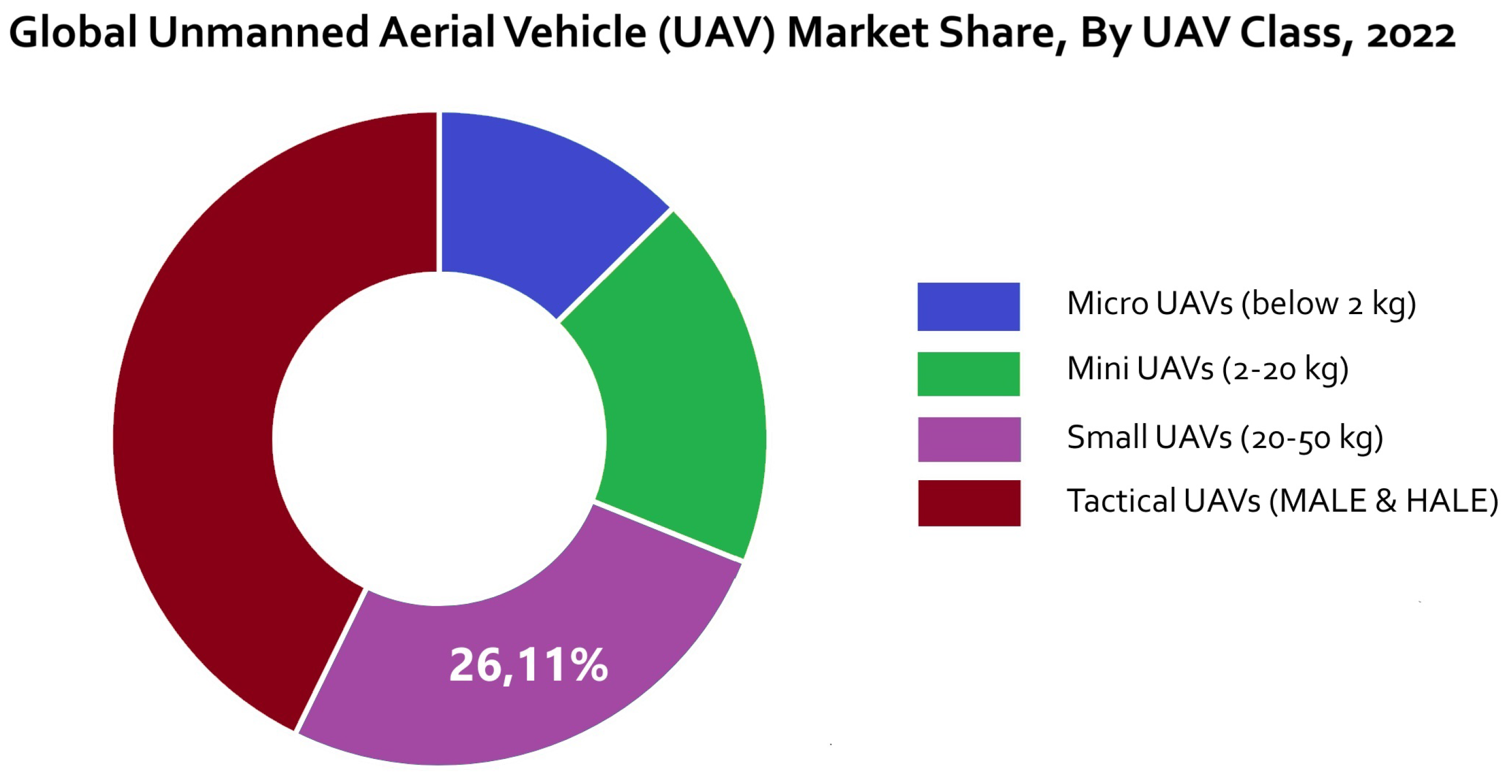

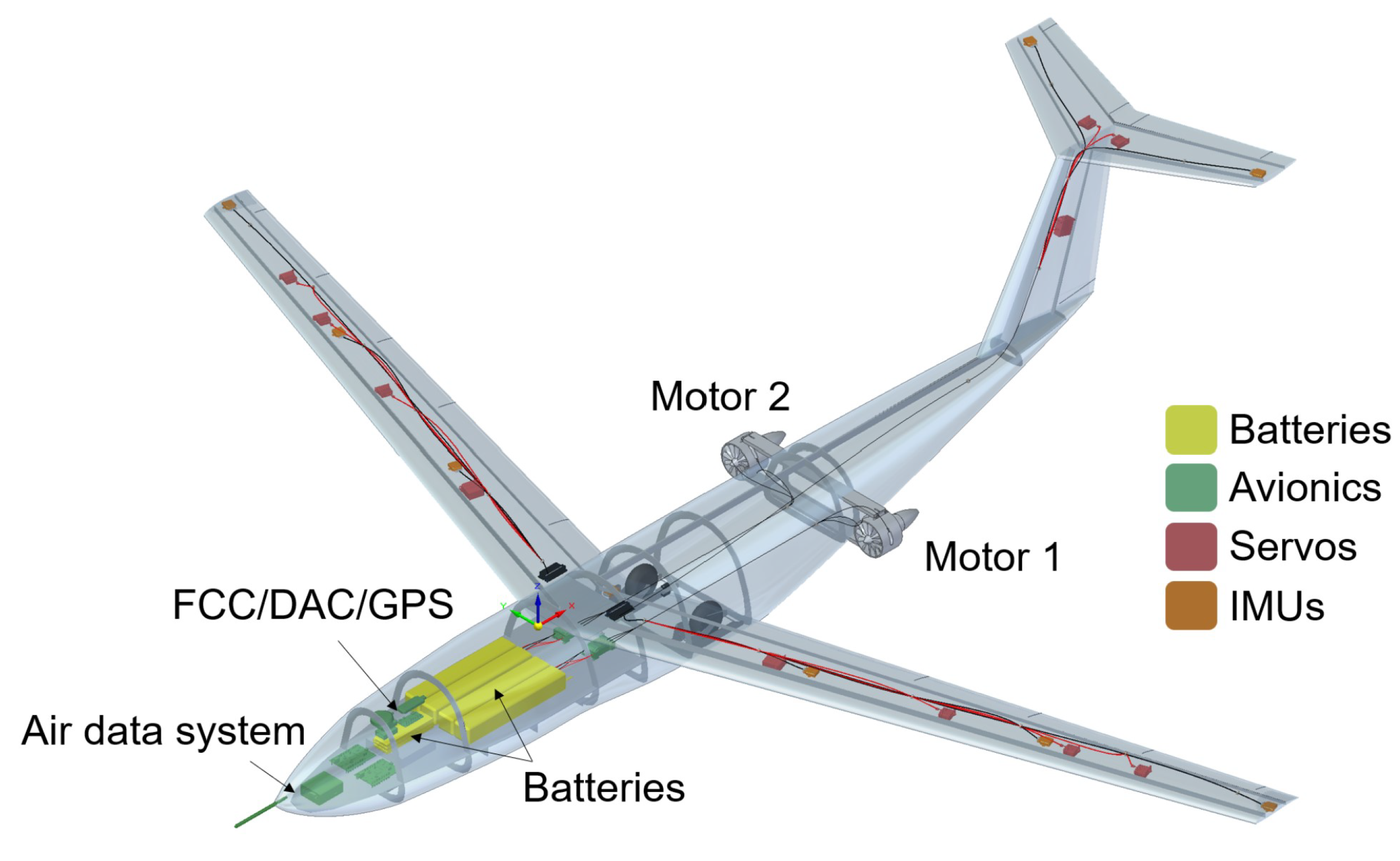

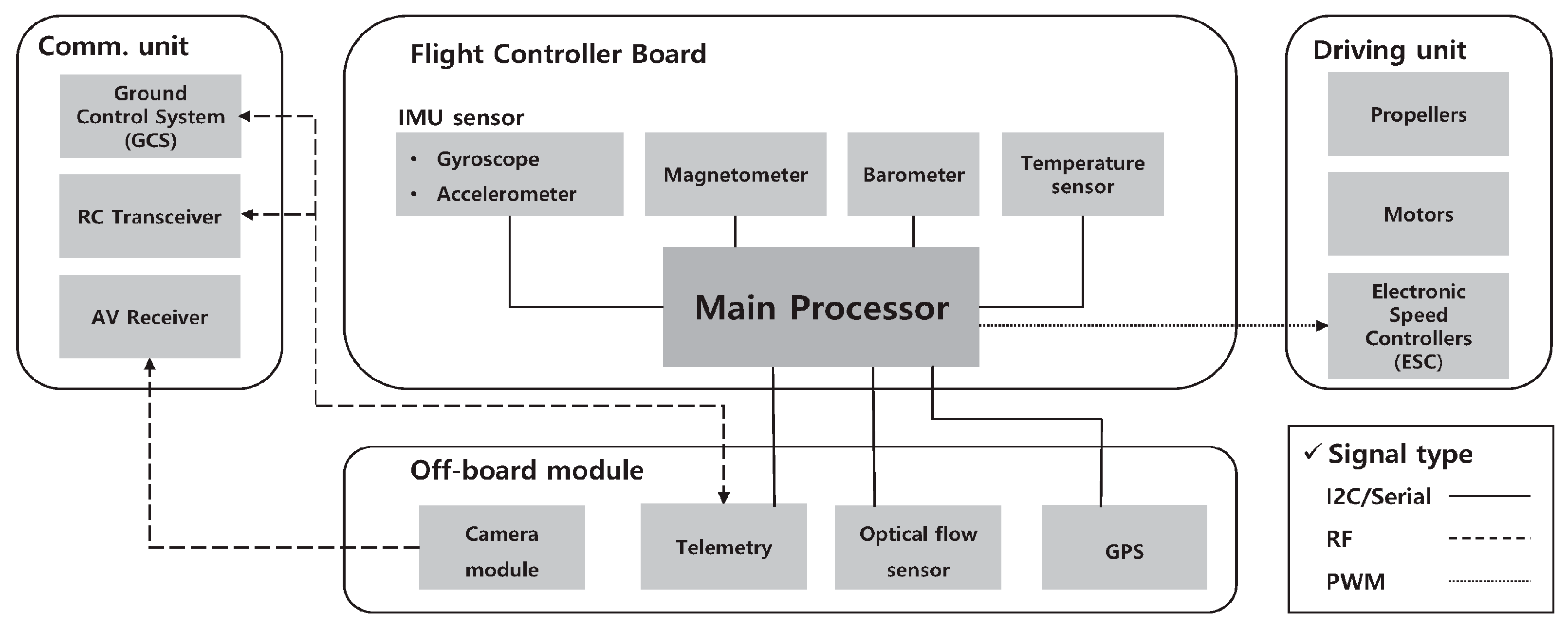

2.1. UAV Avionics and Mission Computers

- Mission computer (often called an on-board computer or flight controller board);

- Navigation and orientation system (GNSS and GPS);

- Sensors board + sensors;

- Remote control and telemetry system (Communication unit);

- Energy and propulsion system (Driving unit);

- Payload (sometimes called an off-board module).

2.2. Problems and Researches in the Field of Mission Computers

2.3. Real-Time Systems and Typical Scheduling Algorithms

- by execution reason: periodic and sporadic tasks;

- by constraint nature: tasks with hard or soft deadlines.

- static priority assignment in reverse order of known task periods - Rate-monotonic scheduling (RMS);

- dynamic priority scheduling, where the highest priority is assigned to the task with the nearest execution deadline – Earliest Deadline First (EDF).

- inflexibility, as the scheduler does not actually react to external world events and works exclusively on timer interrupts;

- difficulty in scheduling sporadic tasks based on the minimum possible period of external events;

- very large size of the schedule table with appropriate ratios between task periods.

- If all scheduled time constraints of all jobs for all tasks can be met using EDF, use EDF and finish. If not, then go to Step 2.

- Sort the jobs of all tasks according to the criterion of the number of time constraints of jobs that are still allowed to be violated for the planning time interval. Class "0" will include all tasks that do not allow any misses. Class "1" will include those that can violate the time constraint once. Example: if () for a task is equal to (2, 4), then it is allowed to violate the time constraint of 2 jobs out of 4 consecutive jobs, so the task can fall into classes 0, 1, 2 depending on the number of jobs already missed.

- Use EDF first for class 0, then for class 1, etc.

2.4. Methods of Energy Consumption Management

- Methods of dynamic voltage and frequency scaling (DVFS) and power-aware scheduling;

- Use of low power consumption modes, called Power Mode Management (PMM) or Dynamic Power Management (DPM);

- Microarchitectural techniques for energy conservation in individual components, such as memory where the computational context is stored in memory during total or partial processor shutdown;

- Use of non-traditional computers, such as DSP or GPU FPGA. This method is suitable for computationally intensive tasks where traditional general-purpose processors perform worse (mW/MIPS).

- real-time constraints;

- constraints on the energy consumption of the computer;

- software methods for ensuring fault tolerance.

- development of scheduling algorithms that take into account the probability of failures to minimize the active time of tasks and their total probability of failures while maintaining schedulability;

- analysis of the impact of various fault tolerance strategies (re-execution, checkpoints, N-modular redundancy (NMR)) on scheduling. In particular, the integration of different approaches and their optimization to improve schedulability and compliance with requirements for failure probability;

- application of the mixed-criticality concept to make systems compatible with industry standards and quantify the probability of transition to high criticality mode;

- analysis of trade-offs between energy consumption management (DVFS), thermal effects, resistance to various types of failures, and real-time requirements;

- improvement of system software reliability, such as scheduler and failure detection mechanisms;

- use of probabilistic information about execution time to calculate a more accurate estimate of failure probability;

- consideration of other failure models, such as (k, n), approximate computations, and malicious failures.

- "Soft-error" or "soft fault" - a single-event upset (SEU), temporary distortion of a bit value in memory or processor register caused by external factors that do not lead to permanent hardware damage;

- "Hard-error" or "hard fault" - permanent damage to a hardware component caused by wear or degradation of materials due to prolonged operation or, for example, radiation exposure in space use. Such errors are classified as single-event latchups (SEL).

- Wake-up delays characterize the time required for full recovery of the processor from sleep mode. They can be measured by determining the time interval from the moment of the interrupt request to the first useful command in the interrupt handler;

- break-even time is an integral characteristic. The processor must spend the minimum amount of time in low-power consumption mode to compensate for the energy and time costs of transitioning to this mode and back. Break-even time is the sum of wake-up and transition delays, which characterize the time costs necessary for the processor to transition from active state to sleep mode.

- procrastination delays, when some algorithms deliberately postpone the execution of tasks to increase the duration of the idle period and more efficiently use low power consumption modes. These delays are carefully calculated so as not to violate the time constraints of tasks;

- scheduling delays - the time required to make decisions about changing the power consumption mode and rescheduling tasks;

- delays associated with calculating optimal moments for transitioning to sleep mode and waking up. Some algorithms perform complex calculations to determine these moments, which can introduce additional delays;

- early completion delays, which create additional space for energy saving but require dynamic rescheduling.

2.5. Overview of Existing Methods for Evaluating Performance and Energy Efficiency of Embedded Systems

- Most existing benchmarks are focused on performance evaluation, while energy efficiency of calculations is critically important for satellite systems due to strict power constraints;

- Requirements for large memory volumes or use of external files. Some benchmarks require access to the file system, which can be problematic for embedded systems with limited memory resources;

- Lack of open source code or requirement of paid subscription. For example, EEMBC benchmarks require a paid subscription to access test loads.

3. Materials and Methods

3.1. Planning the Experiment

3.2. Limitations and Assumptions

- The supply voltage of the microcontroller is nominal and equal to 3.3 Volts. It is the most reliable supply voltage for the electronics components on the mission computer and allows the best resistance to one-time failures and electromagnetic interference (EMI). There is a power consumption dependence over the supply voltage, but this is not the subject of this research;

- The priorities of the performed tasks are assigned according to the classical theory of Lew and Leyland, called RMS (rate-monotonic scheduling). In this case, each task periodic and characterized by two numbers:where - is the maximum time required for the task execution and is the repetition period of the task.

- A set of N tasks to be performed:is always formed in such a way that they meet the sufficient condition of scheduling tasks of hard real-time systems formulated by Liu and Leyland [26]:

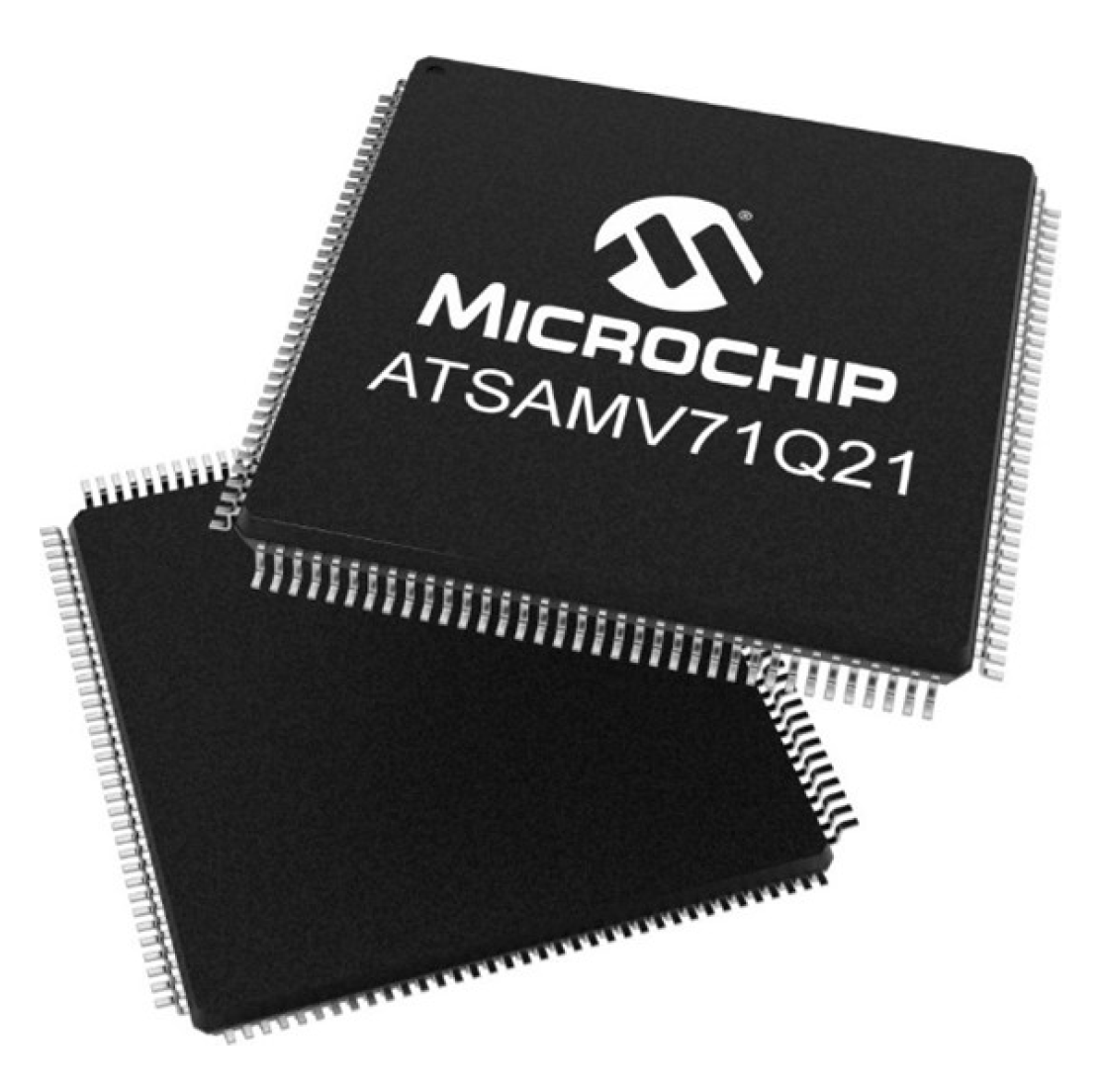

- The limit on the size of the system tick, which determines the frequency of interruptions from the system timer, is obtained from the FreeRTOS documentation, taking into account the limitations of the MPLAB X IDE development environment for the Atmel ATSAMV71 microcontroller:

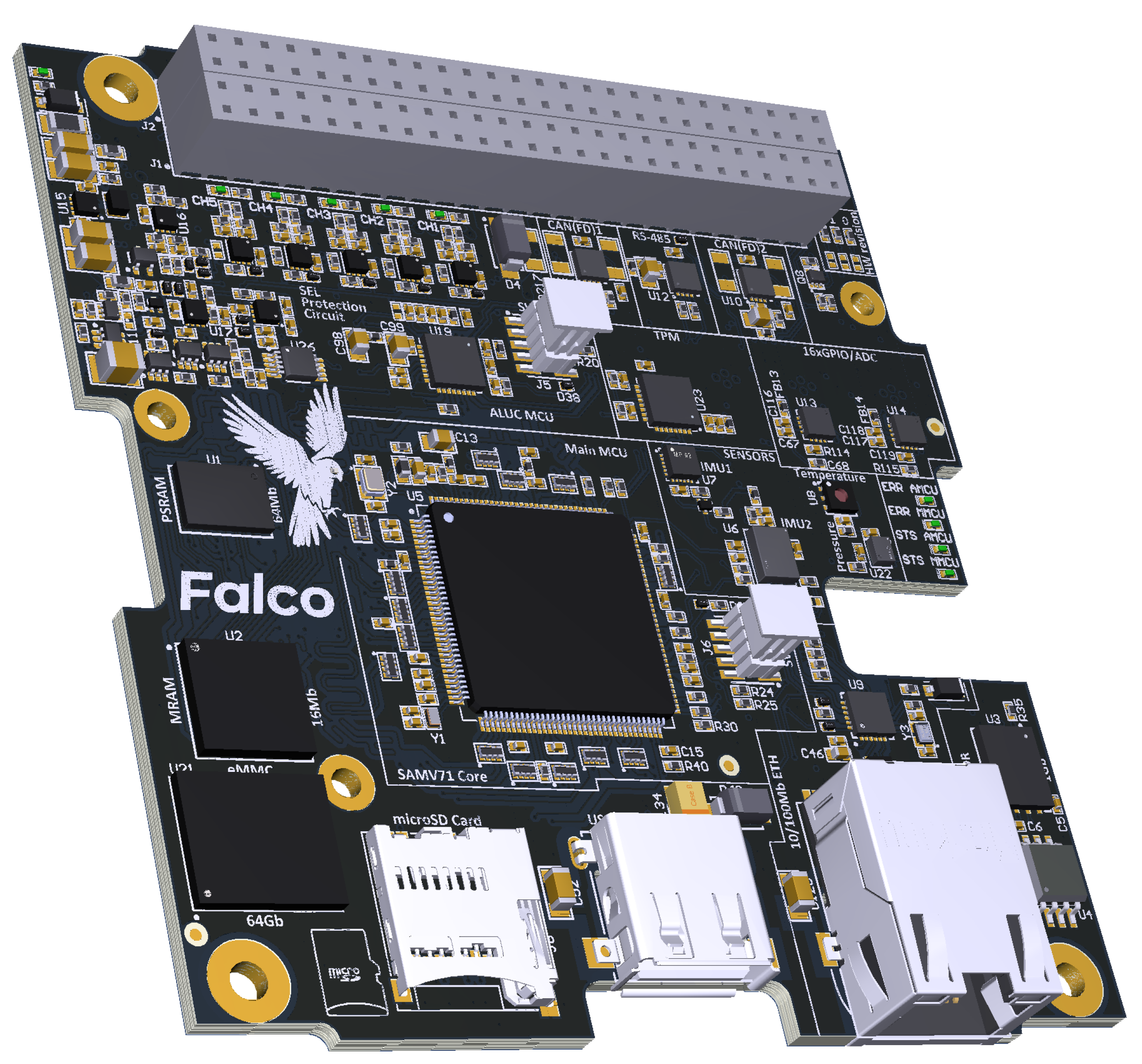

- The limits on the microcontroller clock frequency are determined based on the technical documentation for the ATSAMV71 microcontroller, hardware clock configuration of the ’Boryviter 0.1’ mission computer and form the following set:

3.3. Experiment Plan

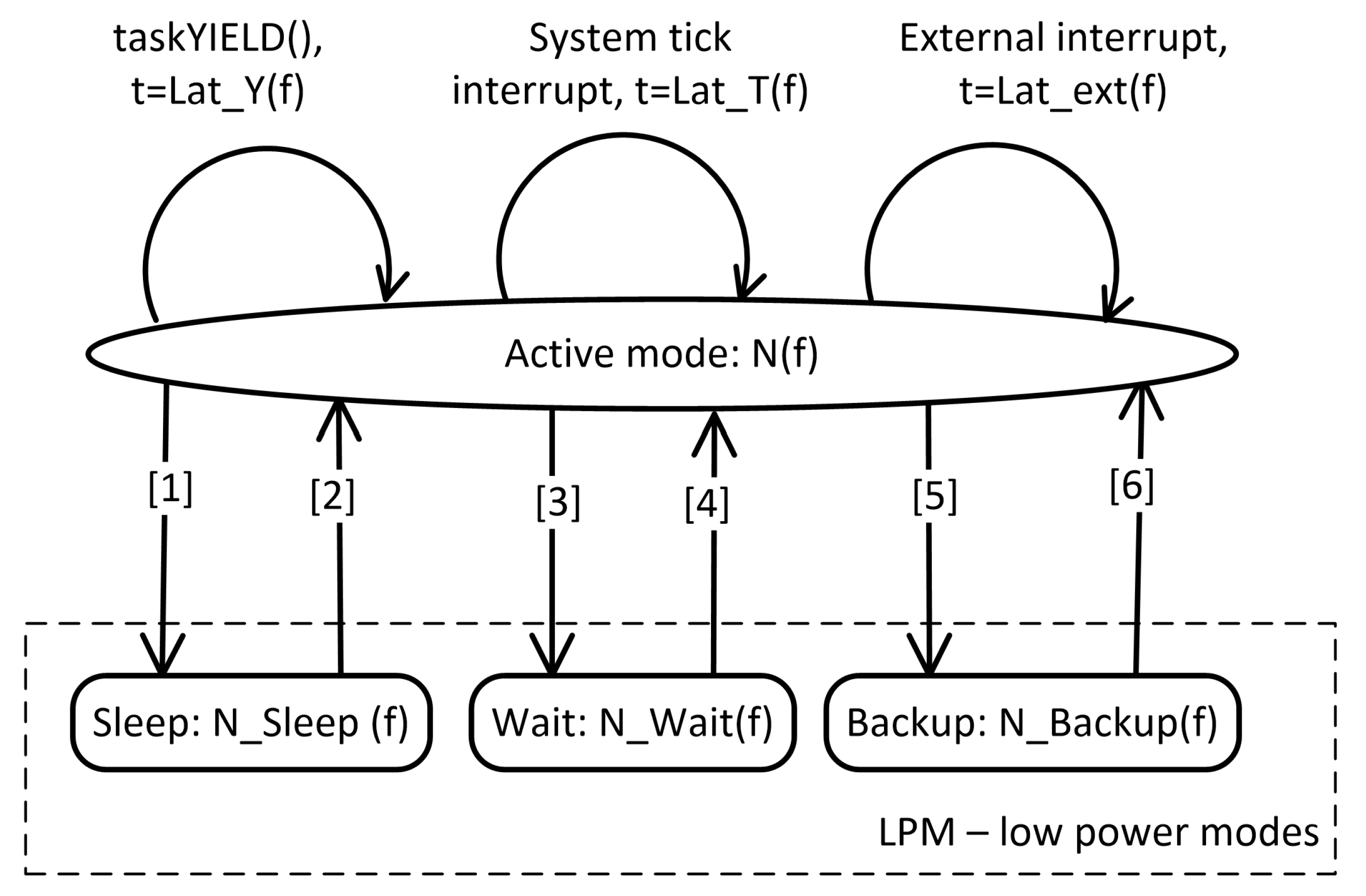

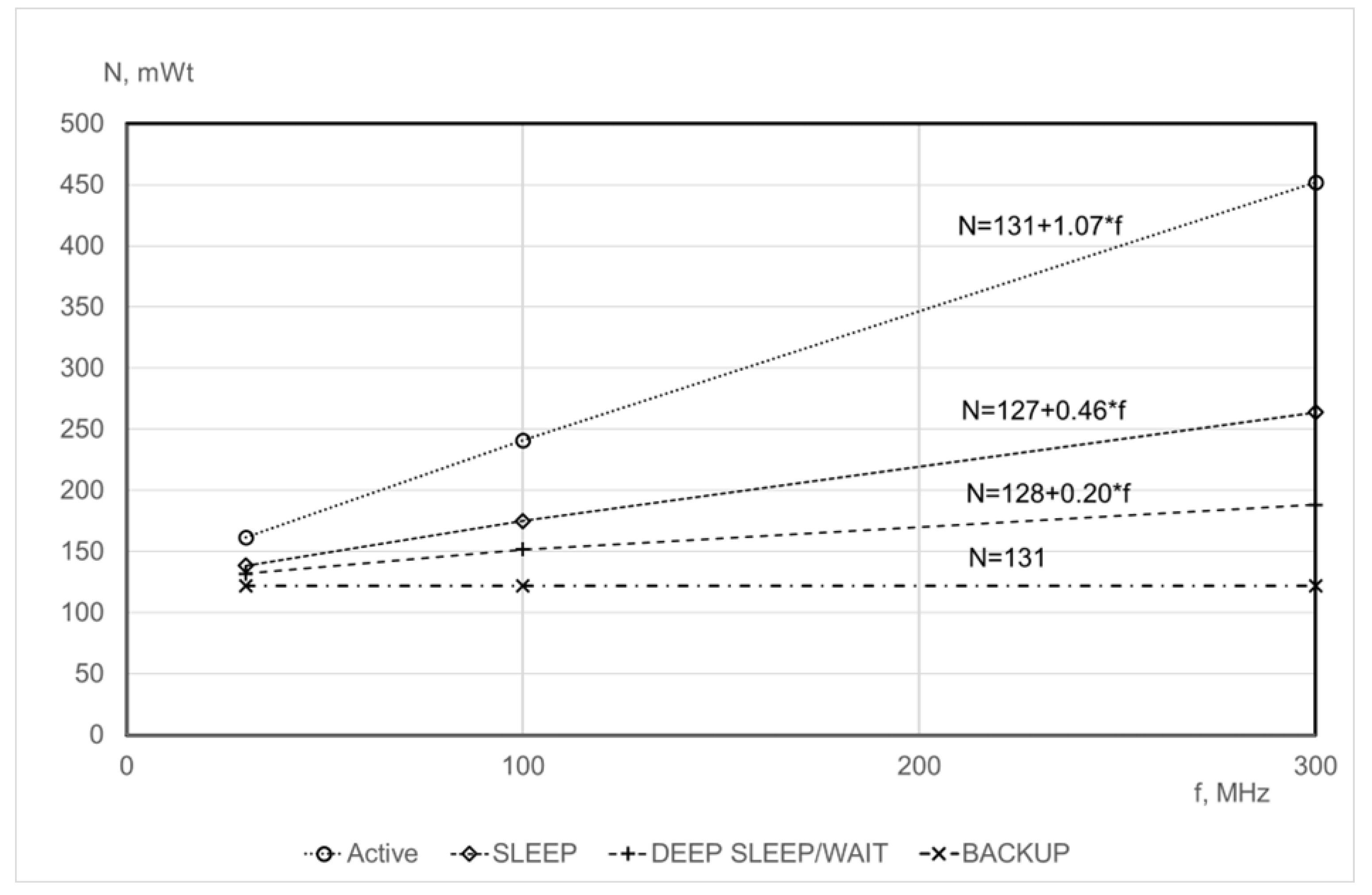

- The dependence of energy consumption on frequency. Dependencies of the consumed electric power on the processor clock frequency N(f) must be determined for each operating mode m. The set of possible modes includes the active mode and power saving modes:

-

Time spent by the operating system to perform functions related to rescheduling and dispatching tasks. These events could originate from forced software requests for rescheduling, system timer interrupts due to the next system tick, or external unplanned interrupt triggering OS synchronization facility – Mutexes, Semaphores, Event Groups, and Queues. Here are the definitions of the events identified for the experiment:

- (a)

- Forced software re-scheduling. The FreeRTOS taskYIELD() function is the basic function of cooperative dispatching. It immediately causes rescheduling, forcing the scheduler to check if another task is ready for execution. If such a task exists and has a higher or equal priority than the current one, a context switch to this task will be performed. Unlike external or system tick interrupts, taskYIELD() does not rely on hardware interrupts. Instead, it is a software mechanism in which the running task voluntarily yields execution, allowing other tasks to run. As a result, the taskYIELD() function represents a cooperative approach to multitasking, where tasks manage their own execution time, while external interrupts and system tick interrupts are part of a preemptive system where the OS can forcefully manage task execution based on real-time events and regular scheduling needs. The time required to perform the function is denoted by: ;

- (b)

- System timer interrupt. The processor time spent processing interruptions from the system timer depends on the clock frequency of the computing platform. It characterizes the operating system’s overhead for working in the preemptive multitasking mode. System tick interrupts occur regularly, triggering the OS to perform tasks such as updating the system time, managing the scheduling process, and potentially preempting the current task if necessary. The time required to perform the function is denoted by: ;

- (c)

- External or peripheral interrupt. The time of the system and call of the interrupt service routine (ISR) is the time from the moment of the occurrence of the external or peripheral interrupt to the time of execution of the first command of the interrupt handler. The time required to perform the function is indicated by . When an external interrupt occurs, the Interrupt Service Routine (ISR) handler or the first-level interrupt handler (FLIH) is triggered immediately. This mechanism forces the OS to temporarily stop the current process, handle the interrupt, and then return to the interrupted task or switch to a different task based on priority. It is important to mention that freeRTOS is a very low-footprint RTOS, and in reality, the context of the ISR handler and the rest of the RTOS context are not very closely coupled. In other words, the IRQ handling is like a regular blocking function with an asynchronous call and a primitive calculation context preservation that heavily leans on ARM Cortex M core capabilities.

-

The time spent entering and leaving the low power mode (LPM): The time required to enter and leave a low-power mode will define how much energy can be saved and how bad system reactivity will be decreased. According to the power state-machine definition, two transitions shall be assessed:

- (a)

- Entering. As entering a LPM requires a specific amount of instructions - its time shall be properly measured. Only specific processor peripherals shall be shut off depending on the exact LPM. No memory preservation actions are required.

- (b)

- Leaving. The exit from an LPM requires more sophisticated actions. As some of the LPM modes shut off the internal frequency generator or switch it to the low-power one, a specific stabilization time is required before any processor instruction can be executed.

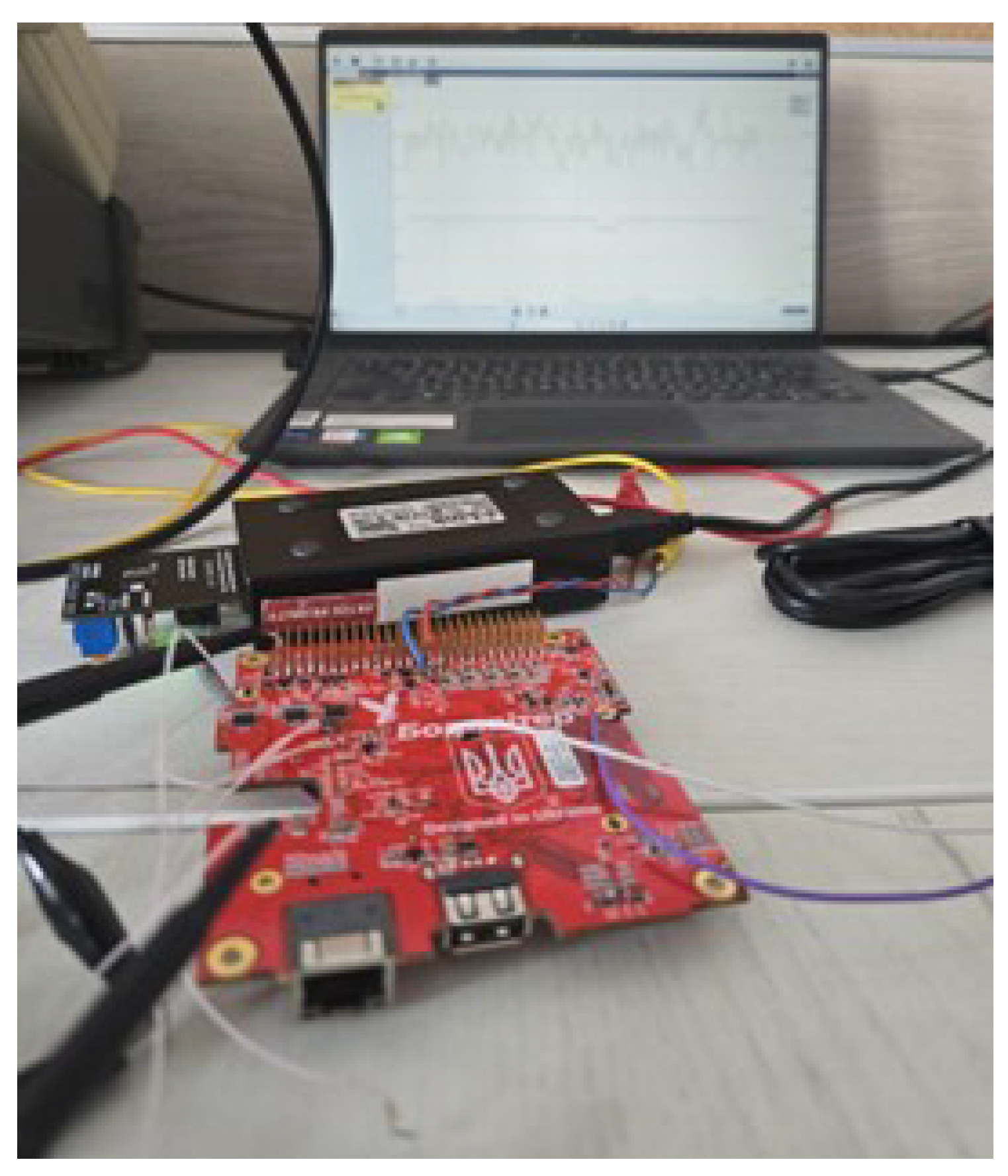

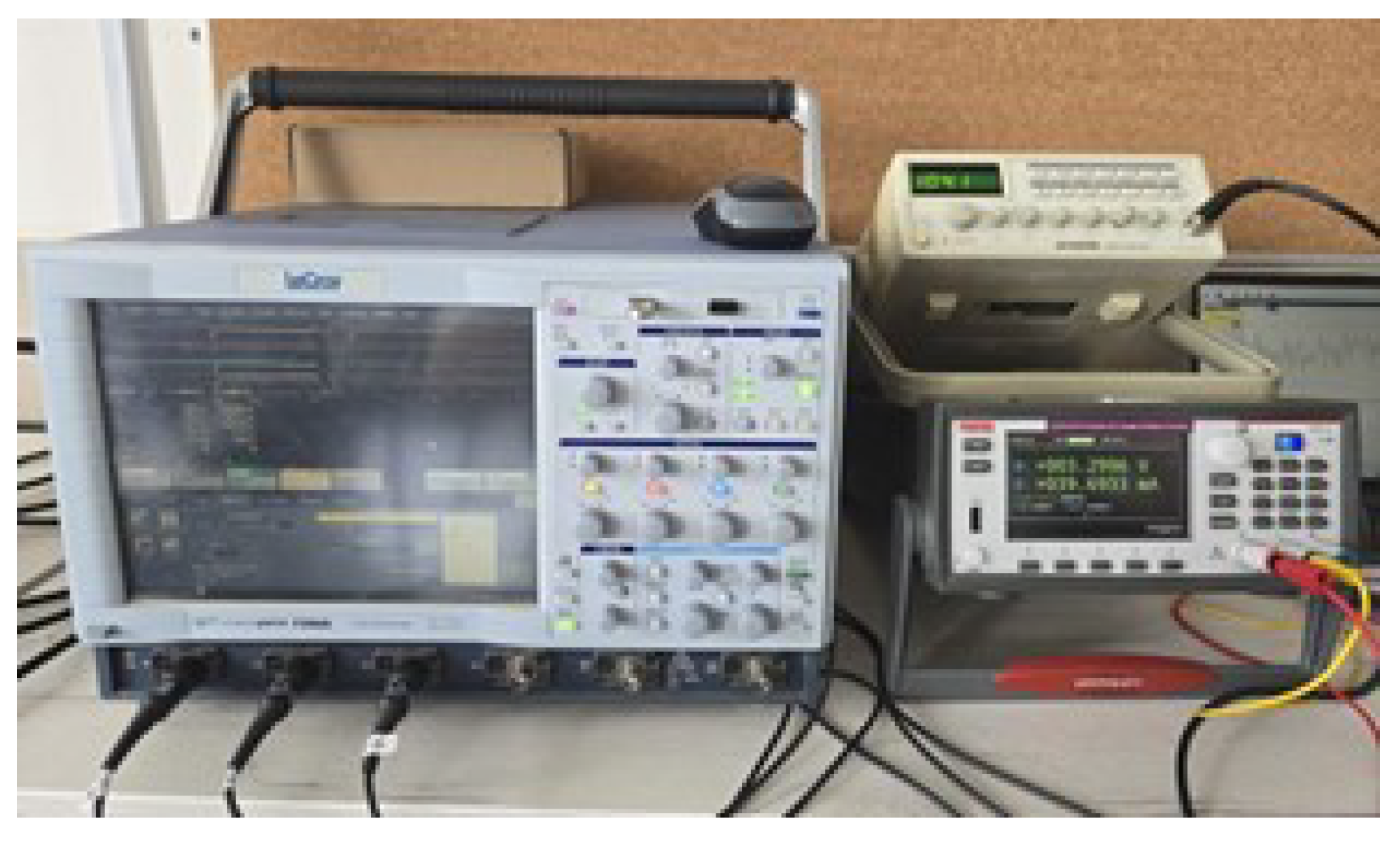

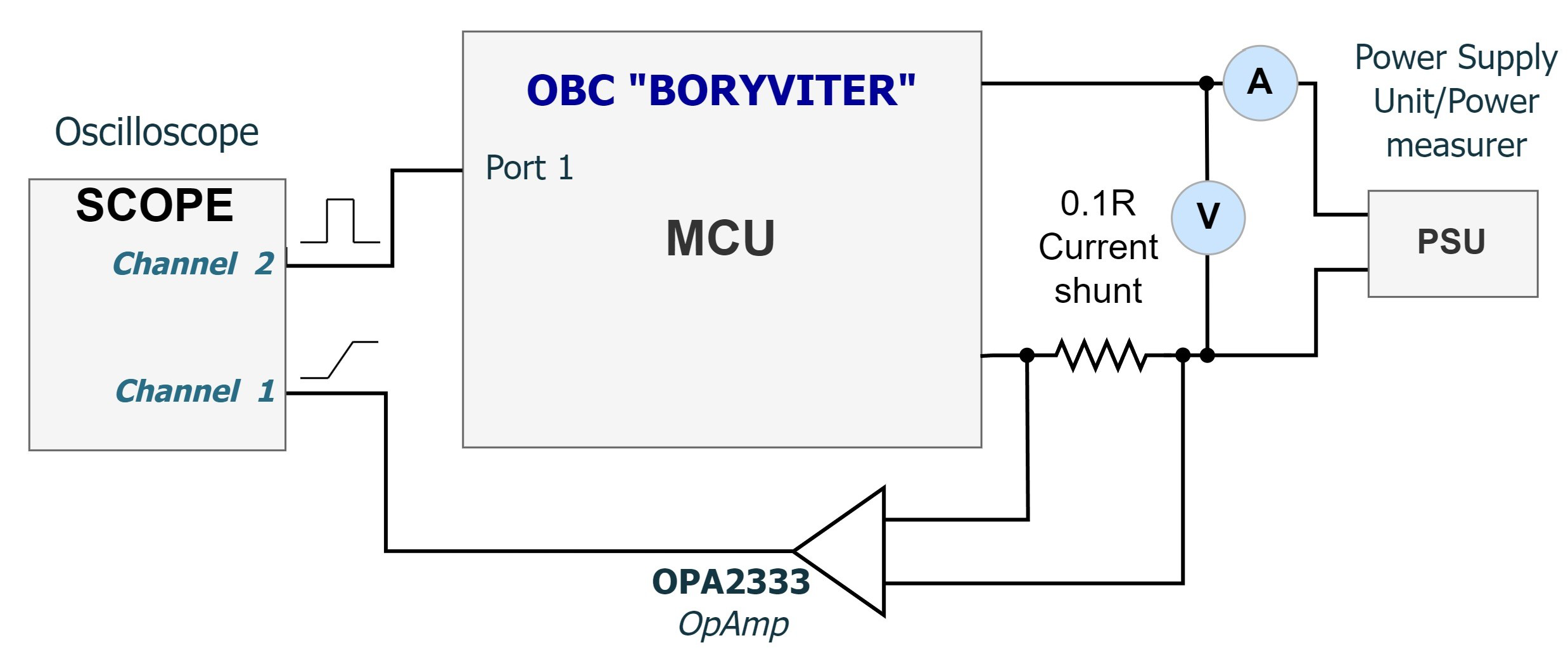

3.4. Measurement Technique

- the square wave generator - GW Instek GFG-8219A that generates external interrupt signals with a given period;

- the high-precision power supply unit and power meter - Keithley 2281S-20-6 that measures the electric energy consumed. It guarantees the accuracy of the measurements (the measurement error of the time interval is no worse than 15 ms, and the error of the electric power measurement does not exceed 0.0001 W;

- the multi-channel storage oscilloscope - LeCroy WavePro 7200A provides the measurement of the time interval between two events: an externally generated interrupt signal from a square wave generator and the first command of the interrupt handler, which is a change of the state of a predefined port - Port 1, to the opposite. Since the command to change the port is atomic, that is, it is executed in one computing cycle in the RISC architecture, the time to change the state of the port can be considered insignificant;

- A hand-modified ’Boryviter 0.1’ mission computer where the oscilloscope is connected to the two GPIO outputs (via flying wires) and to the signal generator.

- The high-precision power supply unit and power meter - Keithley 2281S-20-6 was used to measure the electric power consumed;

- A multi-channel oscilloscope – Siglent SDS1204X-E measures the trigger event between the processor command “go to the low-power mode” and the current consumption response of the microcontroller;

- A modified ’Boryviter 0.1’ mission computer where the oscilloscope is connected to the output of the power-monitor operational amplifier, to ensure proper signal linearity and low noise.

- To obtain dependencies of energy consumption on the frequency in the available modes of operation of the microcontroller in the stationary mode of operation, it is enough to set one of the four operating modes (Active, Sleep, Wait, and Backup) and record the electric power consumption by the Keithley 2281S-20-6 power measurement unit;

-

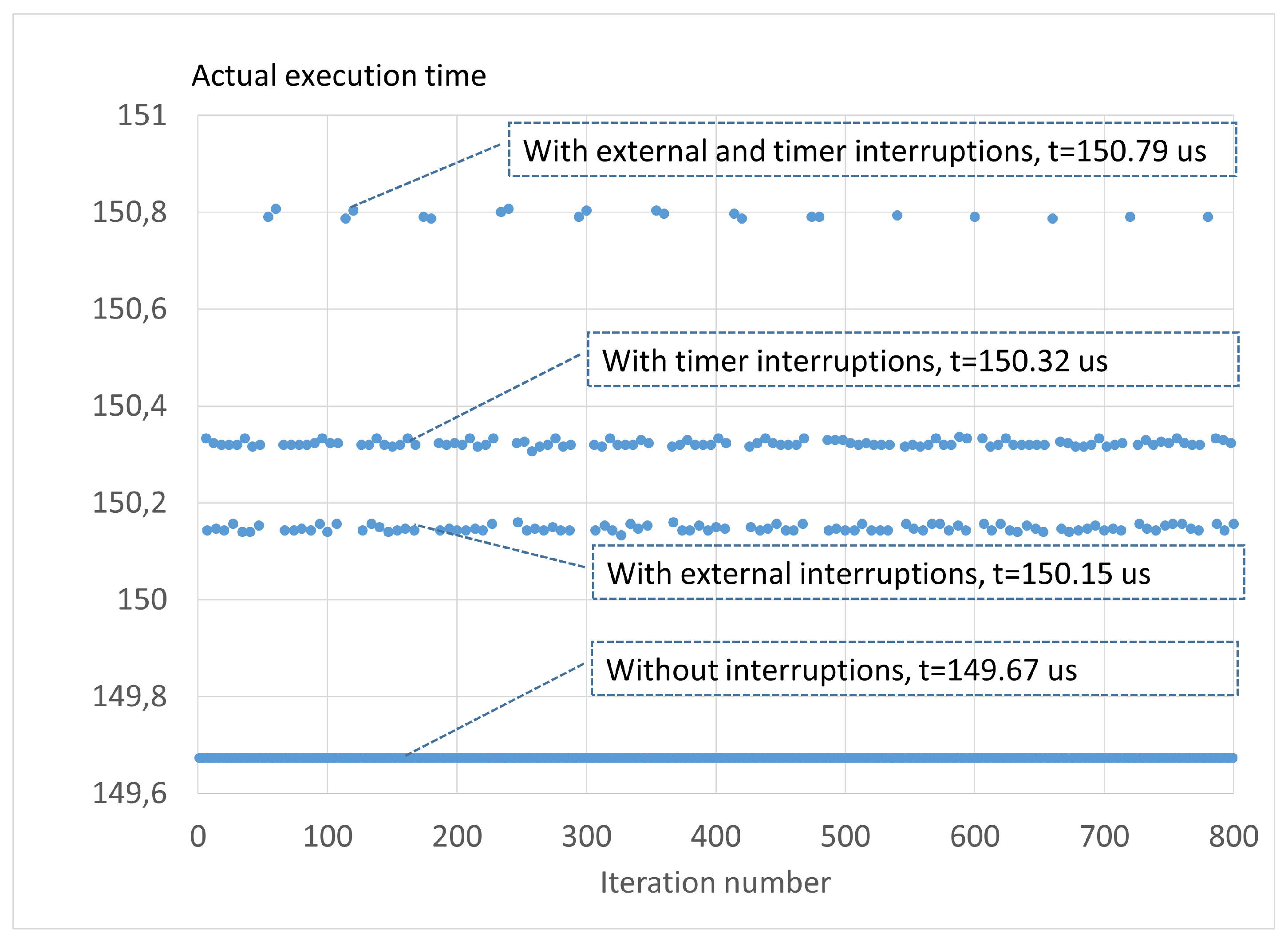

Time spent by the operating system to perform functions related to the rescheduling and dispatching tasks is measured as follows:To estimate the pre-emptive dispatching time, we measured the execution time of the simple pre-defined calculation algorithm with the known execution time for each CPU frequency. For reliable results, a set of 1000 measurements were executed. It is expected that due to the overhead required for handling external interrupts and interrupts from the system timer, some iterations of the known algorithm will take longer. Suppose that the frequency of the external interrupt differs by one and a half to two times from the frequency of the system timer, and the execution time of one iteration is 20-30 percent of the value of the system tick. In that case, we will get the following dependence of the execution time on the iteration number (Figure 11). If the frequencies of interruptions (external and from the system timer) differ by 1.5-2 times, then it is very easy to distinguish their influence on the general graph: it is enough to count the number of measurements that got on the corresponding shelves.The results of measurements of the actual execution time of each iteration are distributed on four shelves, depending on whether the cycle was interrupted for processing interruptions. These shelves correspond to the following situations:

- there are no interruptions;

- an interrupt from the system timer occurred;

- an external interrupt occurred;

- the iteration was interrupted twice by the system timer and externally.

The following algorithm was performed for each CPU frequency to estimate the cooperative dispatch time.The program first accumulates an array of data about the execution time of the mutex ’take’ operation. The FreeRTOS is configured to have only one single task, which blocks and releases the mutex, and then records the time required to perform these two operations in the array.In the second stage, several tasks are created, which block the mutex in a loop, record the time and task number in the logEntries shared array, release the mutex, and then call system function taskYIELD() to transfer control to other tasks. These tasks work in parallel, creating conditions for estimating the overhead of switching between tasks. A hardware timer measures the time of operations with a resolution equal to 66,66 ns. The logEntries array stores the execution time of the operations and the task number, which enables the analysis of the results after the program is executed.Conditional Transition between Stages: The second stage begins after completing the first one, ensuring the correctness of the accumulated data. -

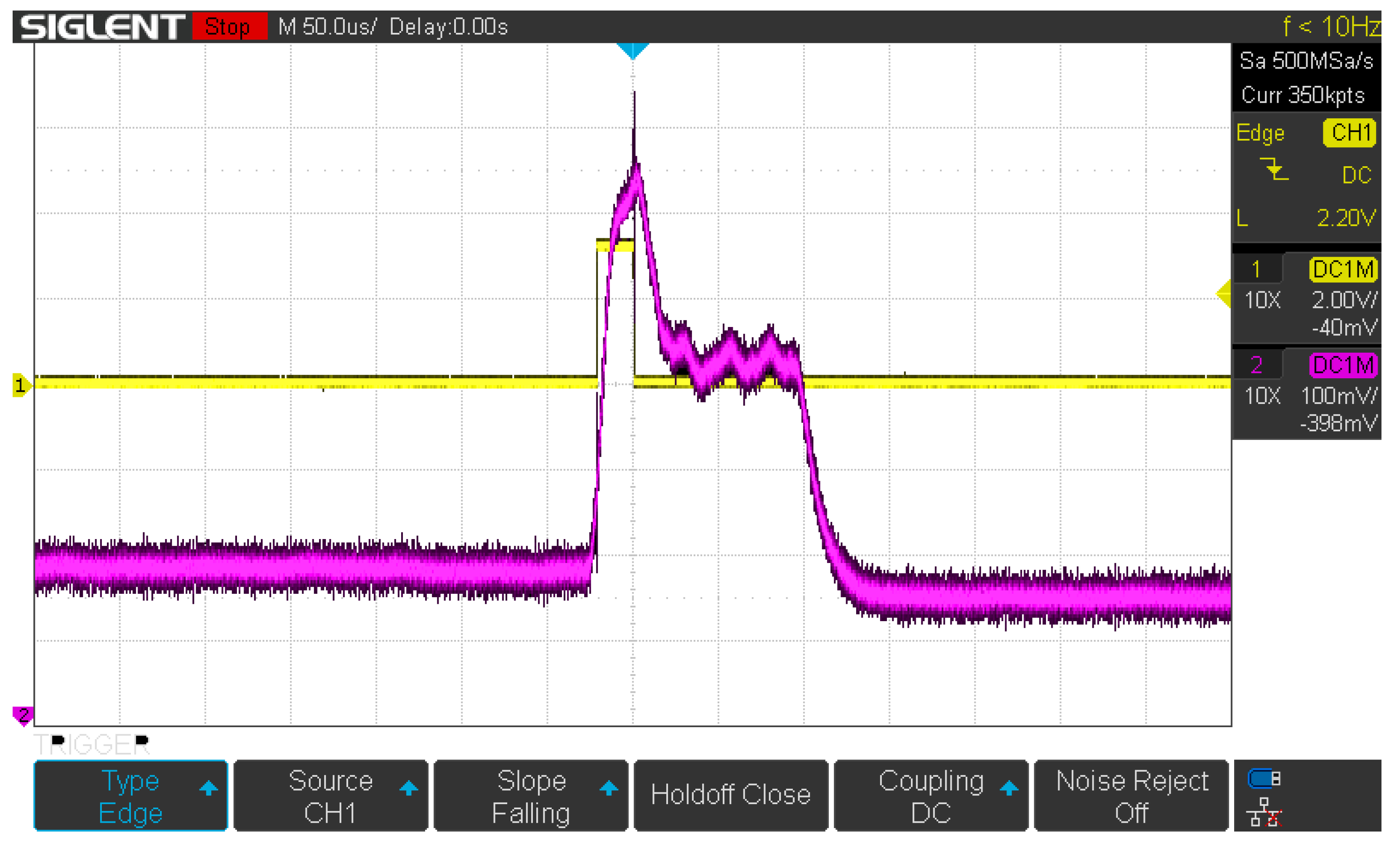

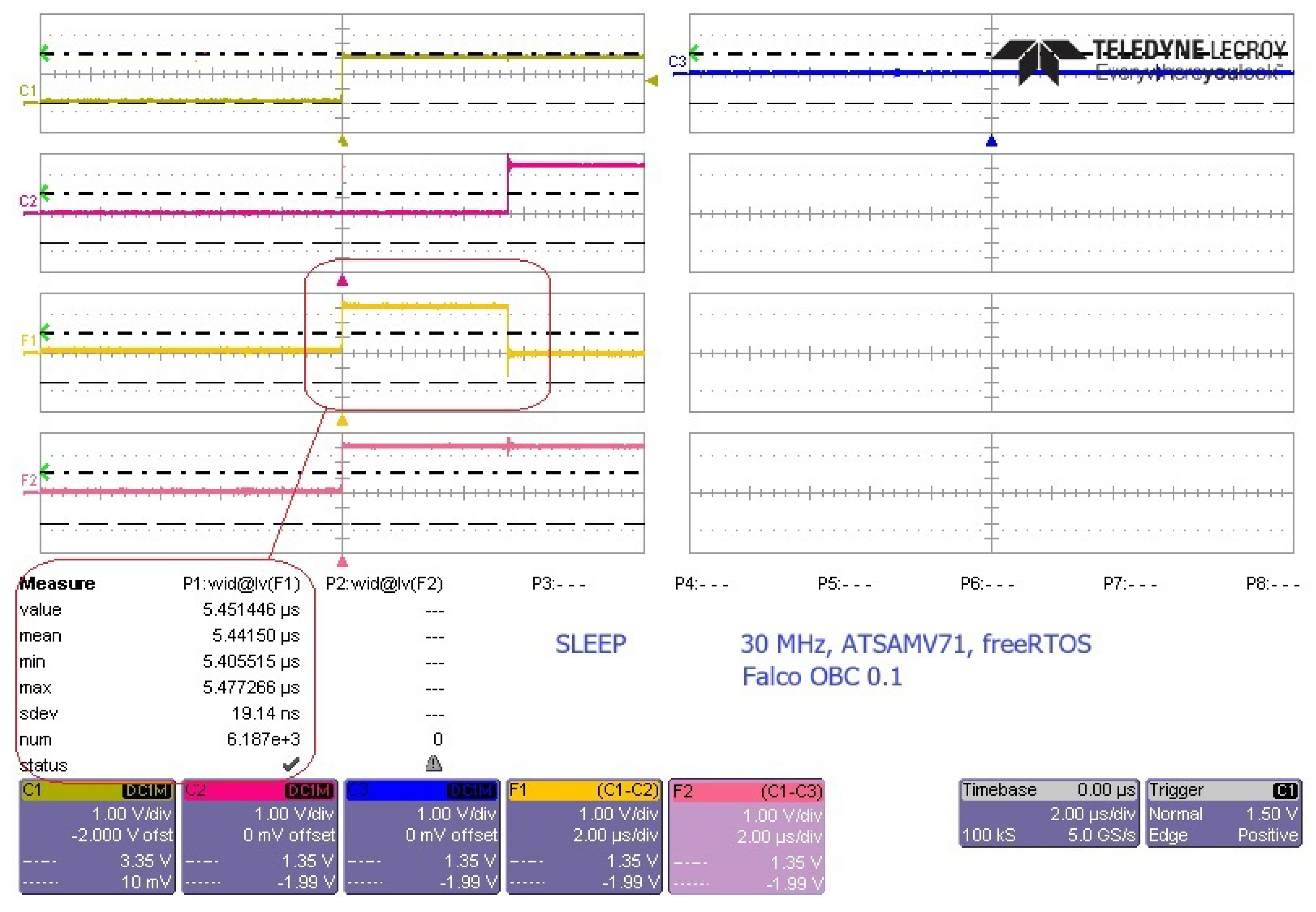

The time spent entering and leaving low-power modes (LPM). According to the processor datasheet, the ’Wait’, ’Sleep’, and ’Backup’ modes require a specific microcontroller shutdown technique that, in return, requires a waiting loop to ensure that all peripherals are safely turned off. However, the ’Backup’ mode, as the most ’deep’ power saving mode, can be exited only if a processor resets. To measure it, it is necessary to apply external devices because when the processor is turned off, and the peripheral shut-off process has been initiated, it is impossible to get information on when exactly the core has stopped working. The time for the transitions [1], [3], [5] in Figure 6 can only be determined using an external oscilloscope since the program is not executed in energy-saving modes. In this case, the actual time of entering the low-power modes can be assessed by the drop in the supply current consumption and, thus, registered with the oscilloscope:

- Step 1. The test software toggles the output GPIO port state. This allows to trigger the connected oscilloscope;

- Step 2. Based on the triggered event of entering the LPM, the second channel of the connected oscilloscope, which is connected to the operational amplifier, registers the current consumption drop;

- Step 3. By calculating the time difference between the triggered event in Step 1 and the current drop event in Step 2, the time required to enter an LPM is obtained.

The exit time measurement technique for the transitions [2], [4], [6] in Figure 6 is also rather hard to do. Still, with the essence of having an external interrupt wake the processor up, it is pretty straightforward to measure the time difference between the external interrupt signal from the signal generator and the output pin toggle of the microcontroller.However, as the most ’deep’ power saving mode, the’ Backup’ mode can be exited only during a processor reset. For this specific case, the test software was modified so that the specific pin toggle was the first operation from the start of the software. The exit from the LPM heavily depends on the particular LPM and how it implements the microcontroller peripheral shutdowns. If the Sleep and Wait modes are relatively straightforward to measure, as both allow them to return to the ’before the LPM’ computation context, the Backup mode is more nontrivial. The exit from the Backup mode requires a RESET vector entrance, which means that the microcontroller software starts from scratch. This behavior requires a more complex software architecture for implementation and typically requires an external NVRAM that could be used as context memory.So, we used two different test software scenarios to measure exit from LPM modes. For both scenarios, the external interrupt from the signal generator was used. That signal triggers the connected oscilloscope to capture the GPIO pin toggle as the first operation after the microcontroller is ready to execute the next command on the program counter (PC).-

Scenario 1 – Sleep and Wait modes:

- -

- Step 1. The wakeup source is configured to react on the external interrupt from the GPIO pin connected to the signal generator;

- -

- Step 2. The external signal generator is set to generate 10 Hz square pulses;

- -

- Step 3. The interrupt handler is done in a way that the first thing it does is the appointed GPIO pin toggle;

- -

- Step 4. The time difference between the rising edge of the square pulse from the signal generator and the rising edge at the output GPIO pin could be considered the wakeup time.

-

Scenario 2 - Backup mode:

- -

- Step 1. The wakeup source is configured to react on the external interrupt from the GPIO pin connected to the signal generator;

- -

- Step 2. The external signal generator is set to generate 10 Hz square pulses;

- -

- Step 3. As the microcontroller shall undergo a reset vector, the GPIO pin toggle was done as the very first operation in the main() function, right after the GPIO configuration. As the test software didn’t contain any major variables, the time for initialization of the “.bss” section can be neglected;

- -

- Step 4. The time difference between the rising edge of the square pulse from the signal generator and the rising edge at the output GPIO pin could be considered the wakeup time.

4. Results

4.1. The Dependence of Energy Consumption on the Operating Frequency

4.2. Time Spent by the Operating System to Perform Functions Related to the Rescheduling and Dispatching Tasks

4.3. The Time Spent Entering and Leaving the Low Power Modes (LPM)

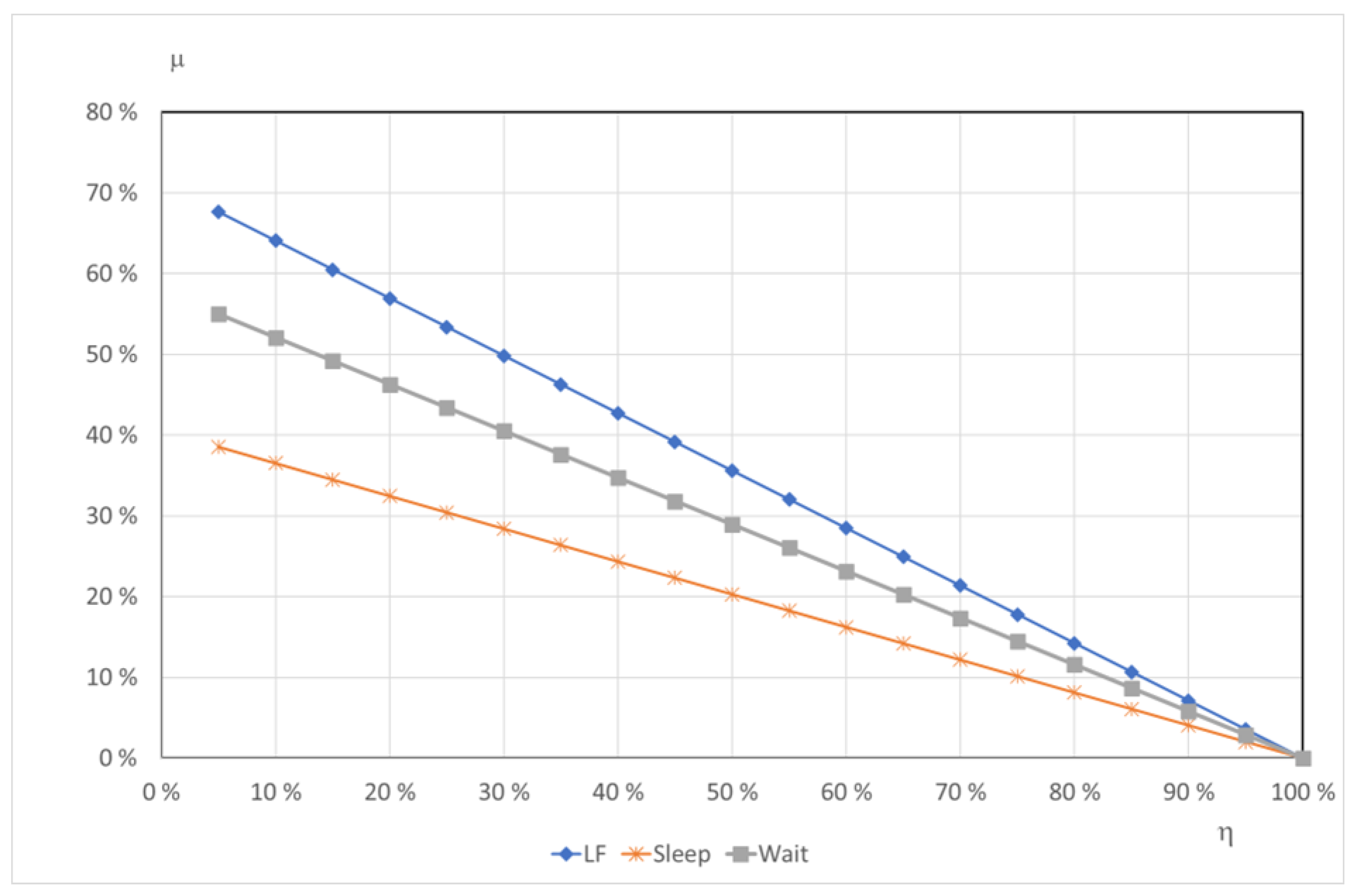

5. Discussion

- dependence of power consumption on clock frequency for active mode and low-power modes;

- overhead costs of the operating system to support multitasking, namely delays in the execution of operations of the scheduler and dispatcher of the operating system for the implementation of cooperative and preemptive dispatching;

- break-even and wake-up times when using low-power modes.

- to ensure that it is functioning energy-efficiently, i.e., spending only a minimum of electrical energy on its operation;

- to guarantee that the required amount of computational work will be completed within the established time frame;

- to ensure that the reaction time to external events will not exceed the established and required by the end-application (mission) limits.

- set the clock frequency of the processor, which will be sufficient to guarantee the specified limits;

- apply a software solution to enable one of the existing low-power modes.

6. Conclusions

- consumed electrical energy in the active mode and power-saving modes of the on-board computer;

- time spent by the operating system to perform functions related to rescheduling and dispatching tasks. We have considered all three possible cases when the OS performs rescheduling and dispatching: cooperative dispatching, crowding out dispatching after an interrupt from the system timer, and external interrupts;

- time spent on entering the energy-saving mode and returning to the active mode after an external event (interruption) that requires the system to wake up.

- The task of finding compromises between reactivity and power consumption of the on-board computer is formulated through a representation in the form of a system model - power state machine;

- The developed technique for measuring the time spent pushing dispatching after an interruption from the system timer and processing an external interruption allows you to quickly and accurately determine these costs;

- The proposed time measurement technique for cooperative dispatching is also fast and accurate; besides, it is well-scalable, as it allows us to figure out the system’s behavior with an arbitrary number of tasks.

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Mueller, M.M.; Dietenberger, S.; Nestler, M.; Hese, S.; Ziemer, J.; Bachmann, F.; Leiber, J.; Dubois, C.; Thiel, C. Novel UAV Flight Designs for Accuracy Optimization of Structure from Motion Data Products. Remote Sensing 2023, 15. [Google Scholar] [CrossRef]

- IAMD Centre of Excellence. The Evolving UAS Threat: Lessons from the Russian-Ukrainian War Since 2022 on Future Air Defence Challenges and Requirements, 2024. Last accessed 8 September 2024, https://iamd-coe.org/wp-content/uploads/2024/02/The-Evolving-UAS-Threat-Lessons-from-the-Russian-Ukrainian-War-Since-2022-on-Future-Air-Defence-Challenges-and-Requirements.pdf.

- Rabiu, L.; Ahmad, A.; Gohari, A. Advancements of Unmanned Aerial Vehicle Technology in the Realm of Applied Sciences and Engineering A Review. Journal of Advanced Research in Applied Sciences and Engineering Technology 2024, 40, 74–95. [Google Scholar] [CrossRef]

- Telli, K.; Kraa, O.; Himeur, Y.; Ouamane, A.; Boumehraz, M.; Atalla, S.; Mansoor, W. A Comprehensive Review of Recent Research Trends on Unmanned Aerial Vehicles (UAVs). Systems 2023, 11. [Google Scholar] [CrossRef]

- Aabid, A.; Parveez, B.; Parveen, N.; Khan, S.; Raheman, M.A.; Zayan, M.; Ahmed, O. Reviews on Design and Development of Unmanned Aerial Vehicle (Drone) for Different Applications. Journal of Mechanical Engineering Research and Developments 2022, 45, 53–69. [Google Scholar]

- Fortune.com. Unmanned Systems / Unmanned Aerial Vehicle (UAV) Market, 2024. Last accessed 28 August 2024, https://www.fortunebusinessinsights.com/industry-reports/unmanned-aerial-vehicle-uav-market-101603.

- Owaid, S.; Miry, A.; Salman, T. Survey on UAV Communications: Systems, Communication Technologies, Networks, Application. University of Thi-Qar Journal for Engineering Sciences 2023, 13, 136–145. [Google Scholar] [CrossRef]

- Jiang, Y.; Xu, X.X.; Zheng, M.Y.; Zhan, Z.H. Evolutionary computation for unmanned aerial vehicle path planning: a survey. Artificial Intelligence Review 2024, 57. [Google Scholar] [CrossRef]

- Ahmed, F.; Jenihhin, M. A Survey on UAV Computing Platforms: A Hardware Reliability Perspective. Sensors 2022, 22, 6286. [Google Scholar] [CrossRef]

- Kumar, P.; Manoj, N.; Sudheer, N.; Bhat, P.; Arya, A.; Sharma, R. UAV Swarm Objectives: A Critical Analysis and Comprehensive Review. SN Computer Science 2024, 5. [Google Scholar] [CrossRef]

- Saravanakumar, Y.N.; Sultan, M.T.H.; Shahar, F.S.; Giernacki, W.; Łukaszewicz, A.; Nowakowski, M.; Holovatyy, A.; Stępień, S. Power Sources for Unmanned Aerial Vehicles: A State-of-the Art. Applied Sciences 2023, 13. [Google Scholar] [CrossRef]

- Liubimov, O.; Turkin, I. Optimizing the CubeSat On-Board Computer Power Consumption Under Hard Real-Time Constraints. Integrated Computer Technologies in Mechanical Engineering - 2023; Nechyporuk, M., Pavlikov, V., Krytskyi, D., Eds.; Springer Nature Switzerland: Cham, 2024; pp. 404–414. [Google Scholar]

- Liubimov, O.; Liubimov, M. USE OF OPEN-SOURCE COTS/MOTS HARDWARE AND SOFTWARE PLATFORMS FOR THE BUILD UP OF THE CUBESAT NANOSATELLITES. Journal of Rocket-Space Technology 2023, 31, 138–147. [Google Scholar] [CrossRef]

- Microchip. COTS-to-Radiation-Tolerant and Radiation-Hardened Devices, 2019. Last accessed 28 June 2023, https://www.microchip.com/en-us/solutions/aerospace-and-defense/products/microcontrollers-and-microprocessors/cots-to-radiation-tolerant-and-radiation-hardened-devices.

- Siewert, S.; Rocha, K.; Butcher, T.; Pederson, T. Comparison of Common Instrument Stack Architectures for Small UAS and CubeSats. 2021 IEEE Aerospace Conference (50100), 2021, pp. 1–17. [CrossRef]

- NASA.gov. State-of-the-Art Small Spacecraft Technology: Small Spacecraft Systems Virtual Institute., 2023. Last accessed 28 August 2024, https://www.nasa.gov/smallsat-institute/sst-soa.

- Microchip. ATSAMV71Q21 Microprocessor Page, 2020. Last accessed 28 June 2023, https://www.microchip.com/en-us/product/ATSAMV71Q21.

- Maltezos, E.; Karagiannidis, L.; Douklias, T.; Dadoukis, A.; Amditis, A.; Sdongos, E. Preliminary design of a multipurpose UAV situational awareness platform based on novel computer vision and machine learning techniques. 2020 5th South-East Europe Design Automation, Computer Engineering, Computer Networks and Social Media Conference (SEEDA-CECNSM), 2020, pp. 1–8. [CrossRef]

- Zhao, X.; Zhou, S.; Lei, L.; Deng, Z. Siamese Network for Object Tracking in Aerial Video. 2018 IEEE 3rd International Conference on Image, Vision and Computing (ICIVC), 2018, pp. 519–523. [CrossRef]

- Zhu, P.; Wen, L.; Du, D.; Bian, X.; Fan, H.; Hu, Q.; Ling, H. Detection and Tracking Meet Drones Challenge. IEEE Transactions on Pattern Analysis and Machine Intelligence 2022, 44, 7380–7399. [Google Scholar] [CrossRef] [PubMed]

- Cai, Y.; Zhang, E.; Qi, Y.; Lu, L. A Review of Research on the Application of Deep Reinforcement Learning in Unmanned Aerial Vehicle Resource Allocation and Trajectory Planning. 2022 4th International Conference on Machine Learning, Big Data and Business Intelligence (MLBDBI), 2022, pp. 238–241. [CrossRef]

- Chodnicki, M.; Siemiatkowska, B.; Stecz, W.; Stępień, S. Energy Efficient UAV Flight Control Method in an Environment with Obstacles and Gusts of Wind. Energies 2022, 15. [Google Scholar] [CrossRef]

- Myasischev, A. Creation of a Rotor-Type UAV with Flight Controllers, Based On a ATmega2560 and STM32f405 Microprocessors. International Journal of Emerging Trends & Technology in Computer Science 2020. [Google Scholar] [CrossRef]

- Jr., R.L.B.; Canham, T.K.; Watney, G.J.; Reder, L.J.; Levison, J.W. Jr., R.L.B.; Canham, T.K.; Watney, G.J.; Reder, L.J.; Levison, J.W. F Prime: An Open-Source Framework for Small-Scale Flight Software Systems. Proceedings of SSC-18-XII-04 32nd Annual AIAA/USU Conference on Small Satellites;, 2018; pp. 110–119.

- Liubimov, O.; Turkin, I.; Pavlikov, V.; Volobuyeva, L. Agile Software Development Lifecycle and Containerization Technology for CubeSat Command and Data Handling Module Implementation. Computation 2023, 11. [Google Scholar] [CrossRef]

- Liu, C.L.; Layland, J.W. Scheduling Algorithms for Multiprogramming in a Hard-Real-Time Environment. J. ACM 1973, 20, 46–61. [Google Scholar] [CrossRef]

- Zhang, F.; Burns, A. Schedulability Analysis for Real-Time Systems with EDF Scheduling. IEEE Transactions on Computers 2009, 58, 1250–1258. [Google Scholar] [CrossRef]

- Bernat, G.; Burns, A.; Liamosi, A. Weakly hard real-time systems. IEEE Transactions on Computers 2001, 50, 308–321. [Google Scholar] [CrossRef]

- Choi, H.; Kim, H.; Zhu, Q. Job-Class-Level Fixed Priority Scheduling of Weakly-Hard Real-Time Systems. 2019 IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS), 2019, pp. 241–253. [CrossRef]

- Shi, J.; Ueter, N.; Chen, J.J.; Chen, K.H. Average Task Execution Time Minimization under (m, k) Soft Error Constraint. 2023 IEEE 29th Real-Time and Embedded Technology and Applications Symposium (RTAS), 2023, pp. 1–13. [CrossRef]

- Adam, G.K. Timing and Performance Metrics for TWR-K70F120M Device. Computers 2023, 12. [Google Scholar] [CrossRef]

- RaspberryPi. RP2040 Microprocessor Page, 2020. Last accessed 28 June 2023, https://www.raspberrypi.com/products/rp2040/.

- Mittal, S. A survey of techniques for improving energy efficiency in embedded computing systems. International Journal of Computer Aided Engineering and Technology 2014, 6, 440–459. [Google Scholar] [CrossRef]

- Widhalm, D.; Goeschka, K.M.; Kastner, W. Undervolting on wireless sensor nodes: a critical perspective. Proceedings of the 23rd International Conference on Distributed Computing and Networking; Association for Computing Machinery: New York, NY, USA, 2022. [Google Scholar] [CrossRef]

- Reghenzani, F.; Guo, Z.; Fornaciari, W. Software Fault Tolerance in Real-Time Systems: Identifying the Future Research Questions. ACM Comput. Surv. 2023, 55. [Google Scholar] [CrossRef]

- Kim, B.; Yang, H. Reliability Optimization of Real-Time Satellite Embedded System Under Temperature Variations. IEEE Access 2020, 8, 224549–224564. [Google Scholar] [CrossRef]

- IEC-61508. IEC 61508 Ed. 2.0 en:2010 CMV, Functional Safety Of Electrical/Electronic/Programmable Electronic Safety-Related Systems - Parts 1 To 7 Together With A Commented Version (See Functional Safety And IEC 61508), 2021. Last accessed 26 Aug 2023, https://webstore.ansi.org/standards/iec/iec61508eden2010cmv.

- ISO-26262. ISO 26262-6:2018, Road vehicles — Functional safety — Part 6: Product development at the software level, 2018. Last accessed 26 Aug 2023, https://www.iso.org/standard/68388.html.

- Zidar, J.; Matic, T.; Aleksi, I.; Hocenski, Z. Dynamic Voltage and Frequency Scaling as a Method for Reducing Energy Consumption in Ultra-Low-Power Embedded Systems. Electronics 2024, 13. [Google Scholar] [CrossRef]

- Oliveira, G.; Lima, G. Scheduling and energy savings for small scale embedded FreeRTOS-based real-time systems. Design Automation for Embedded Systems 2023, 27, 1–27. [Google Scholar] [CrossRef]

- Musaddiq, A.; Zikria, Y.B.; Hahm, O.; Yu, H.; Bashir, A.K.; Kim, S.W. A Survey on Resource Management in IoT Operating Systems. IEEE Access 2018, 6, 8459–8482. [Google Scholar] [CrossRef]

- FreeRTOS.org. Low Power Support: Tickless Idle Mode, 2024. Last accessed 15 August 2024, https://www.freertos.org/Documentation/02-Kernel/02-Kernel-features/07-Lower-power-support.

- Simonovic, M.; Saranovac, L. Power management implementation in FreeRTOS on LM3S3748. Serbian Journal of Electrical Engineering 2013, 10, 199–208. [Google Scholar] [CrossRef]

- Bambagini, M.; Marinoni, M.; Aydin, H.; Buttazzo, G. Energy-Aware Scheduling for Real-Time Systems: A Survey. ACM Trans. Embed. Comput. Syst. 2016, 15. [Google Scholar] [CrossRef]

- de Melo, A.C.C.P.; Café, D.C.; Alves Borges, R. Assessing Power Efficiency and Performance in Nanosatellite Onboard Computer for Control Applications. IEEE Journal on Miniaturization for Air and Space Systems 2020, 1, 110–116. [Google Scholar] [CrossRef]

- Poovey, J.A.; Conte, T.M.; Levy, M.; Gal-On, S. A Benchmark Characterization of the EEMBC Benchmark Suite. IEEE Micro 2009, 29, 18–29. [Google Scholar] [CrossRef]

- Iqbal, S.M.Z.; Liang, Y.; Grahn, H. ParMiBench - An Open-Source Benchmark for Embedded Multiprocessor Systems. IEEE Computer Architecture Letters 2010, 9, 45–48. [Google Scholar] [CrossRef]

- Zoni, D.; Galimberti, A.; Fornaciari, W. A Survey on Run-time Power Monitors at the Edge. ACM Comput. Surv. 2023, 55. [Google Scholar] [CrossRef]

- Kluge, F.; Rochange, C.; Ungerer, T. EMSBench: Benchmark and Testbed for Reactive Real-Time Systems. Leibniz Transactions on Embedded Systems 2017, 4, 02:1–02:23. [Google Scholar] [CrossRef]

- Dobija, K. Countering Unmanned Aerial Systems (UAS) in Military Operations. Safety & Defense 2023, 9, 74–82. [Google Scholar] [CrossRef]

- Liubimov, O. Falco Engineering, 2024. Last accessed 28 Aug 2024, https://www.falco.engineering/.

- Fayyad-Kazan, H.; Perneel, L.; Timmerman, M. Benchmarking the Performance of Microsoft Hyper-V server, VMware ESXi and Xen Hypervisors. Journal of Emerging Trends in Computing and Information Sciences 2013, 4, 922–933. [Google Scholar]

| MCU Family | Memories | Temperature | Voltage | Low Power Modes |

|---|---|---|---|---|

| ATSAMV7x (Cortex-M7) | F=2Mb, R=384 Kb | -40/+125 | 1.8-3.6 Vdc | Sleep, Wait, Backup |

| PIC32CZ (MIPS) | F=2Mb, R=512 Kb | -40/+105 | 2.5-3.6 Vdc | Sleep, Wait, Backup |

| PIC32MX (MIPS) | F=512Kb, R=128 Kb | -40/+105 | 2.3-3.6 Vdc | Sleep, Idle |

| STM32H7 (Cortex-M7) | F=1Mb, R=564 Kb | -40/+125 | 1.62-3.6 Vdc | Sleep, Stop, Standby |

| STM32F7 (Cortex-M7) | F=2Mb, R=512 Kb | -40/+105 | 1.7-3.6 Vdc | Sleep, Stop, Standby |

| iMX.RT1024 (Cortex-M7) | F=4Mb, R=256 Kb | -40/+105 | 3.0-3.6 Vdc | LPR (24 MHz), Sleep |

| Frequency, MHz | taskYield() latency , uS | System tick interrupt latency , uS | External interrupt latency , uS | Capturing and releasing non-blocking mutexes latency, uS |

|---|---|---|---|---|

| 30 | 7,27 | 4,02 | 6,42 | 7,73 |

| 100 | 2,16 | 1,23 | 1,95 | 2,34 |

| 300 | 0,72 | 0,47 | 0,65 | 0,78 |

| Mode | Sleep, uS | Wait, uS | Backup, uS | |||

|---|---|---|---|---|---|---|

| Frequency | Wake-up delays | break-even time | Wake-up delays | break-even time | Wake-up delays | break-even time |

| 30 MHz | 5 | 45 | 1800 | 1950 | 5000 | 6500 |

| 100 MHz | 1,7 | 31 | 1228 | 1388 | 5000 | 6500 |

| 300 MHz | 0,6 | 21 | 105 | 255 | 5000 | 6500 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).