1. Introduction

Modern industrial systems make it possible to produce in large volumes PCBs that meet the strictest requirements for their reliability. But there are also a number of companies, including our department, for which the manufacture of PCBs is not their primary activity. Companies of such format are various design-centers of electronics as it is easier, faster and cheaper to make prototypes on their own manufacturing line. It is typical for these companies to have equipment with not high accuracy characteristics, but does this mean that high-precision and high-reliability boards are not available for production on it? What can be done when designing boards to be able to produce PCBs on affordable equipment?

The creation of modern electronic equipment is tightly linked to the development of new methods of PCB manufacturing. At present, the electronics industry is moving in the direction of increasing performance and functionality. At the same time, the requirements to the mass and dimension parameters of the produced equipment are getting more and more complicated. Increasing integration of integrated circuits leads to higher density of leads on the package, which drives the search for new design solutions in their layout [

1,

2,

3].

To increase the functions of the device while maintaining its size, it is necessary to increase the density of the PCB interconnections, which involves increasing the number of PCB layers and, accordingly, the number of vias. The main obstacle to increasing the interconnection density is large annular rings of vias, as they reduce the trace space on PCB [

4,

5]. The greater the errors in the dimensional alignment of the interconnections, the larger the contact pads are required to ensure that the drill hits them reliably when obtaining the vias [

6,

7]. Therefore, at present, the actual issue is to determine the reliability of the vias at the design stage, depending on its parameters and on the PCB manufacturing process. Currently, two main approaches of reliability estimation can be highlighted [

8]: probabilistic-statistical and physico-chemical.

In the first approach (probabilistic-statistical) the main index of reliability is failure rate, which is determined on the statistical data [

9,

10,

11,

12]. However, as the reliability of electronics elements increases, the processes of determining reliability metrics through reliability tests become ineffective. Verification by tests of such reliability indexes for an acceptable time interval is an extremely time-consuming and costly process, since it requires involvement in the experiment of a huge number of samples of electronic devices.

The second approach (physico-chemical or physics of failures) is related to the research of the causes and processes that cause failures of electronic devices. Mechanisms of typical failures are identified, on the basis of which models of failures are developed, taking into account the influence not only of operating time, but also of design and manufacturing factors, state of production, influence of external impacts [

8,

13,

14]. The results of researches in this direction give an opportunity to develop methods of engineering calculations, allowing already at the stage of designing: to optimize designs of electronic devices by reliability criterions, to reasonably formulate requirements to the material and manufacturing equipment, to predict reliability metrics. However, the physical and chemical processes that cause failures of electronic devices are very complex and the number of parameters that must be taken into account is large.

This research proposes another approach to reliability evaluation in relation to the above-described ones. Its core is to formulate an analytical model to calculate the probability of manufacturing a printed circuit board that conforms to current design and acceptance standards, such as IPC-6012B [

15] and IPC-A-600G [

16]. Thus, the standards specify specific quantitative criteria for PCBs. However, depending on the complexity of the design and process, these dimensions may not be sufficient to evaluate the ability to reliably manufacture a PCB. The model (

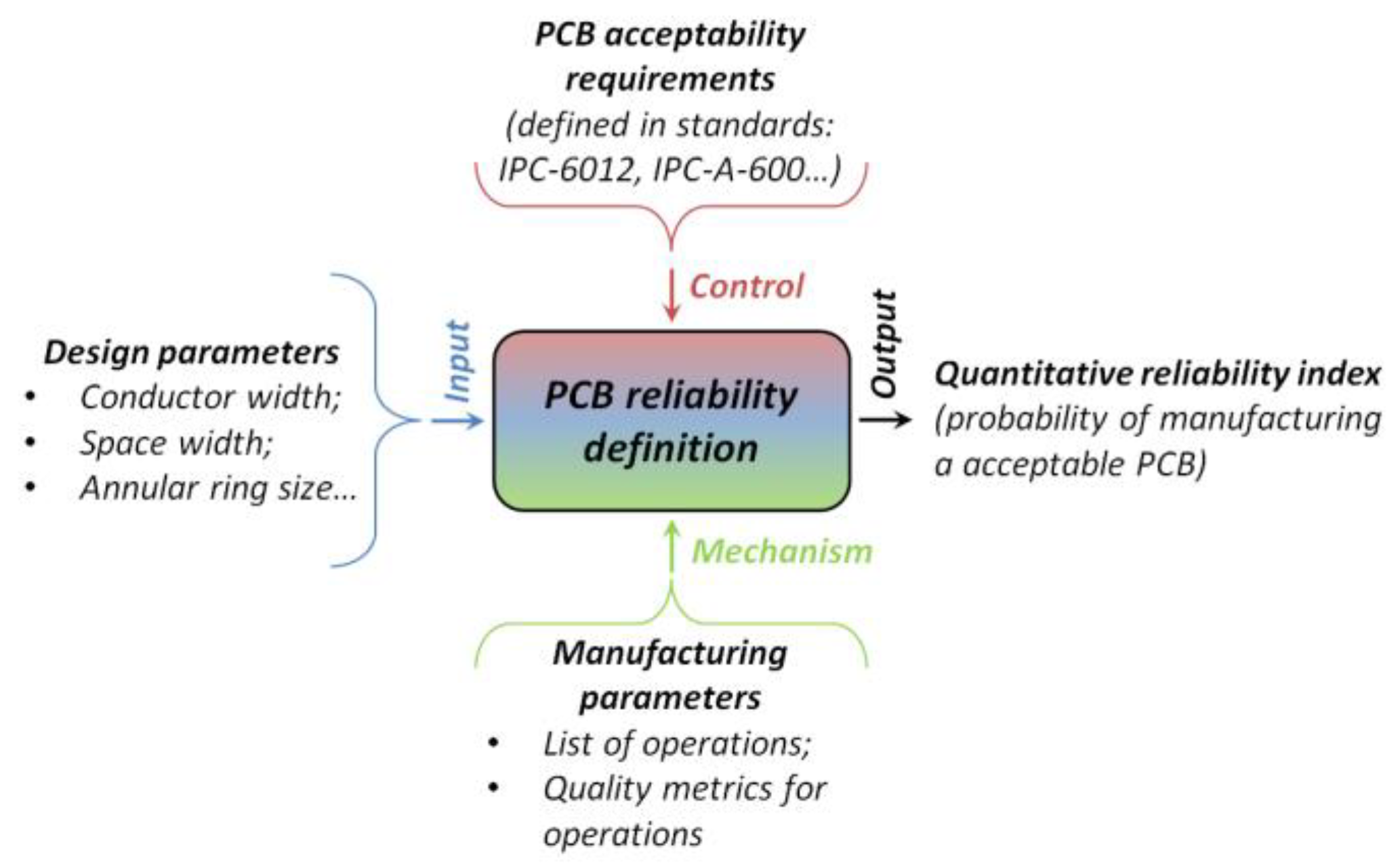

Figure 1) proposes the definition of relations between the given design rules of electronic device (input), the characteristics of the manufacturing process (mechanism) and the requirements of existing standards (control), in order to calculate the probability of producing an acceptable product (output). Thus, the resulted probability is a quantitative value reflecting indirectly the reliability of the product.

Thus, it is proposed to use the described approach to determine the probability of making an acceptable via. This will make it possible already at the design stage to assess the risks of obtaining defective products and to change the PCB design or choose another production facility for manufacturing.

2. Materials and Methods

2.1. Determination of Vias Requirements

The standards IPC-6012B [

15] and IPC-A-600G [

16] are define different reliability classes for PCBs: class 3 for aerospace electronics, class 2 for industrial equipment, and class 1 for consumer equipment. Each class has different requirements. The requirements of standards for supported holes are chosen as the basis for forming the criteria for assessing the acceptability of the vias [

16]:

Class 3: «Holes are not centered in the lands, but annular ring measures 0.05 mm or more»;

Class 2: «90° breakout or less»;

Class 1: «180° breakout or less».

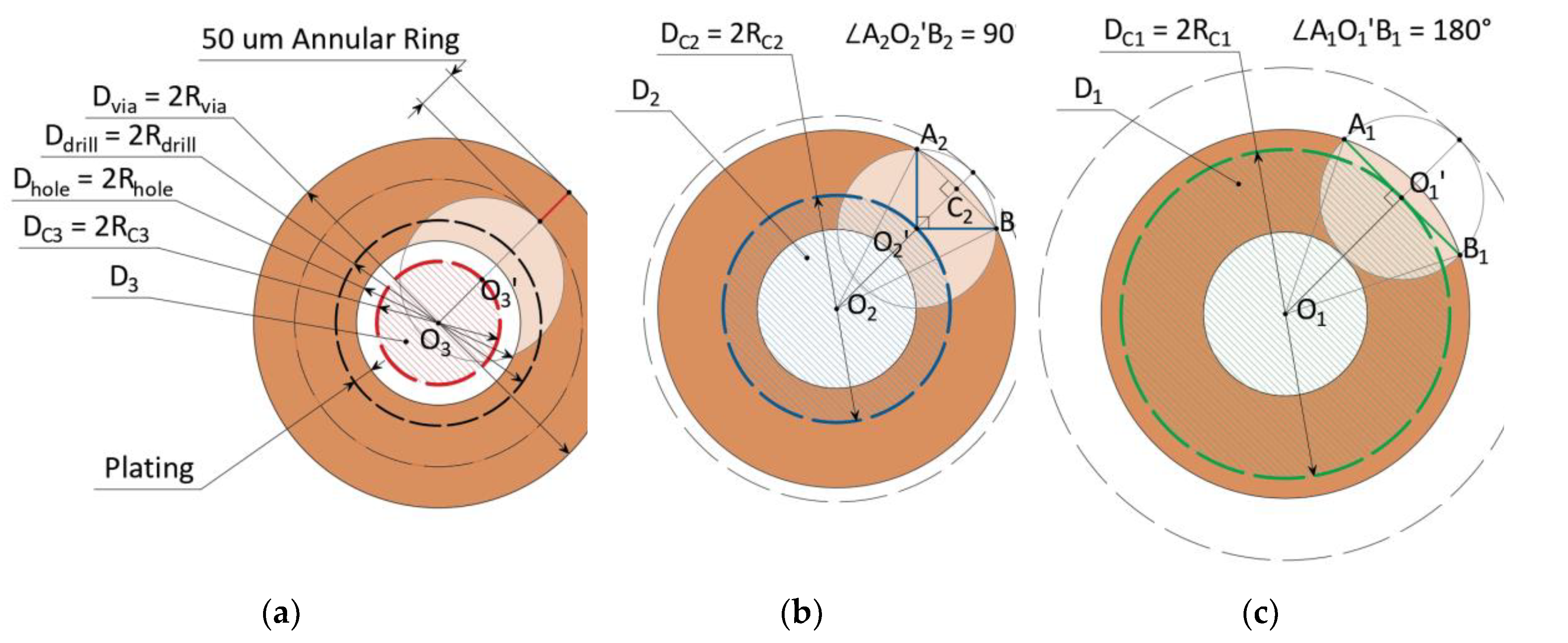

The presented limitations are difficult to use to assess the possibility of manufacturing an acceptable PCB. Therefore, based on the requirements, we will determine the numerical value of the permissible offset of the hole center relative to the center of the contact pad (

Figure 2).

– diameter of the via or plated through-hole pad;

– diameter of the drilled hole;

– diameter of the drilled hole with plating;

, , – areas of permissible hole center offset for the corresponding reliability classes;

, , – diameter of the permissible hole center misalignment area for the corresponding reliability classes.

So, for PCBs to meet the requirements of reliability class 3 it is necessary that the minimum size of the annular ring is not less than 50 µm, then the maximum offset of the hole center

is determined by the Equation (1):

In order to meet reliability class 2 requirements, the hole is allowed to extend beyond the contact pad, but the arc of the circumference of the hole extending beyond the contact pad must be less than 90°. To determine the maximum offset of the hole center

we consider triangle

: by the requirement

is straight and its sides

. Then,

and angles

,

are straight. Now we consider triangle

: since

is straight, the maximum offset of the hole center

is determined by Equation (2):

The requirements of reliability class 1 are similar to those of class 2, but allow for an arc of less than 180°. Similar to the previous cases, determine the maximum offset of the hole center relative to the center of the contact pad. In triangle

:

and

, then

is the height of triangle

and

is straight. Therefore, the maximum offset of the hole center

is determined by Equation (3):

Thus, the probability of compliance of the manufactured contact pad with a certain reliability class can be interpreted as the probability of falling inside the area of permissible offset of the hole center during drilling.

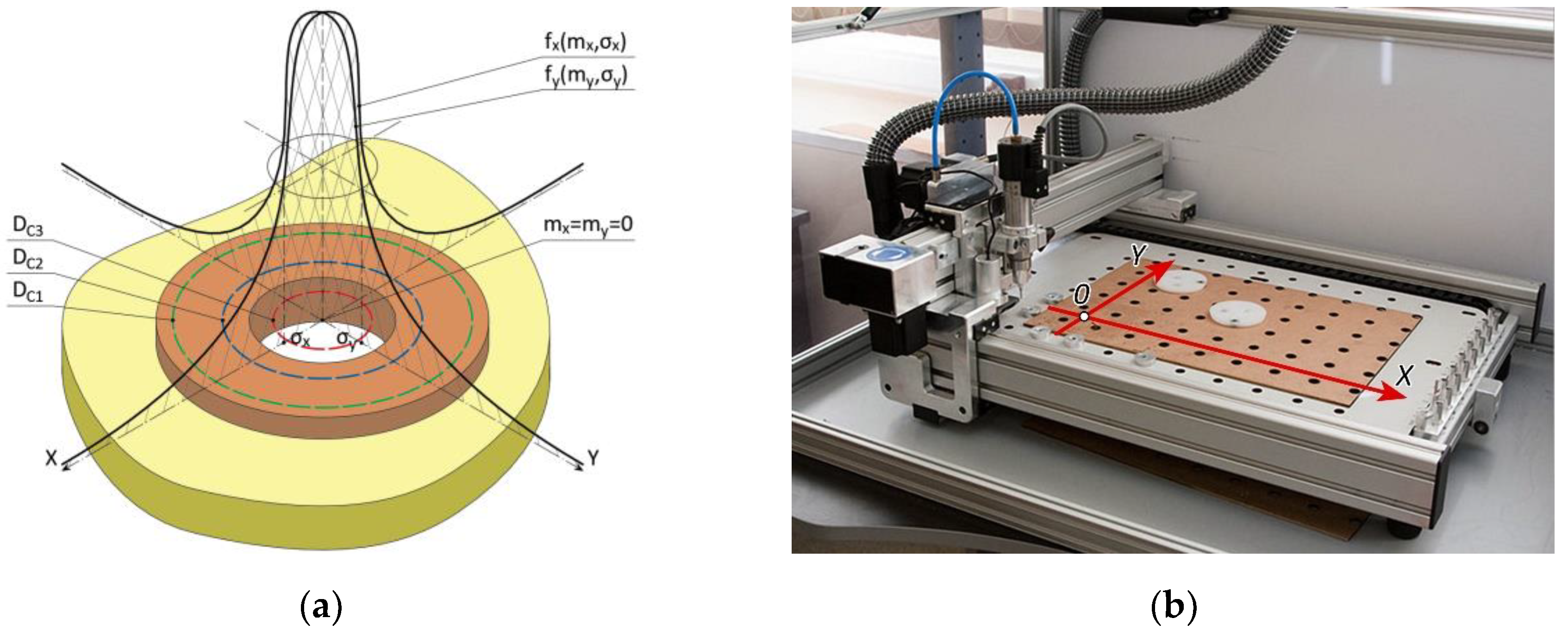

2.2. Formalization of the Drilling Process using Elements of Probability Theory

Consider the drilling process, the accuracy of which is mainly determined by the accuracy of the numerically controlled machine (CNC). In this case, there is a law of distribution of random variables in the plane. To determine the type of distribution law, we introduce additional assumptions and restrictions (

Figure 3a):

The distribution law contains two independent components

and

, which are directional to the movement directions of the spindle on the coordinate table (

Figure 3b) and obey the normal distribution law, i.e.,

,

;

The mathematical expectations of the distribution laws and are 0 and coincide with the center of the contact site: ;

The standard deviations of the distribution laws are equal to each other: .

Thus, the distribution density function of the system of random variables

will take the form (4), and the probability of hitting the hole center in the area of acceptable offset of the hole center relative to the center of the contact pad

will be determined by the Equation (5) [

17].

Since the area

is a circle, it is reasonable to switch from the rectangular coordinate system to the polar coordinate system (6). The Jacobian of the transformation is equal to r. Then the density function and probability will be determined by equations (7) and (8), respectively.

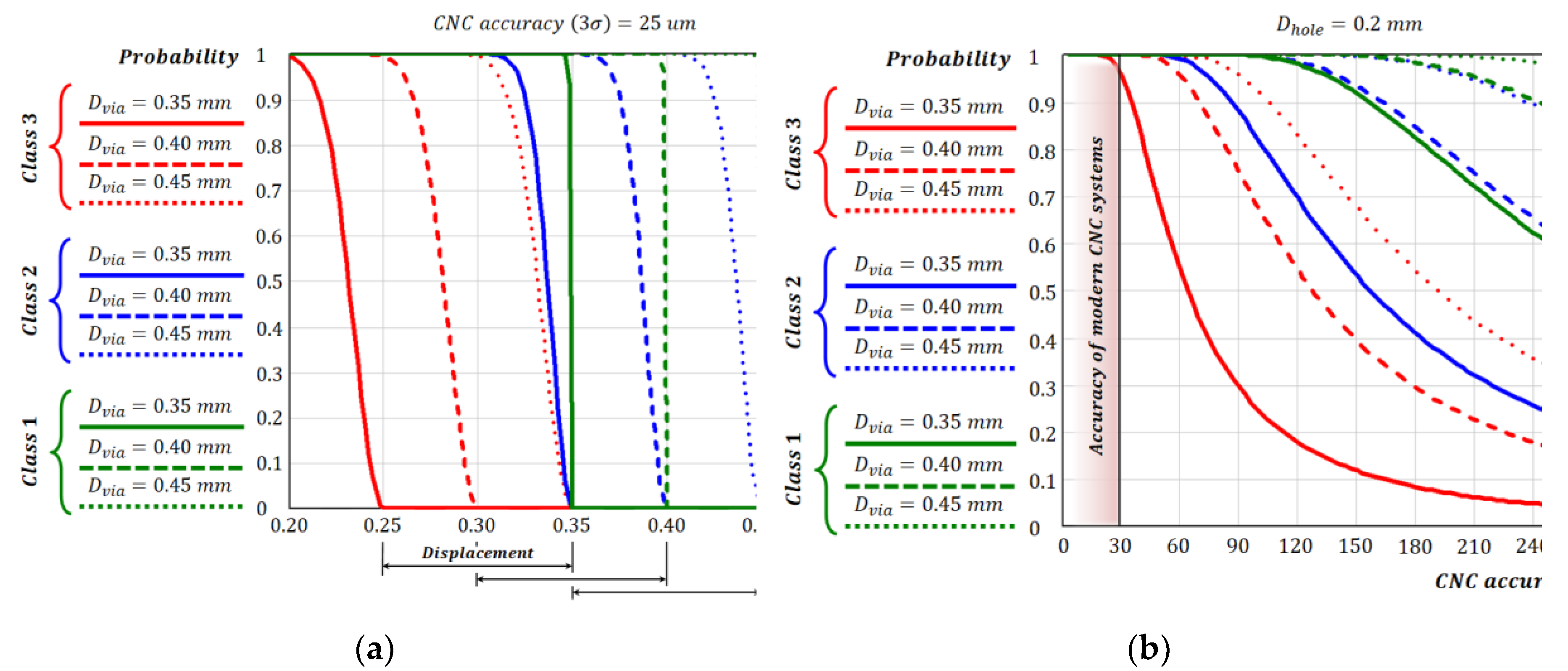

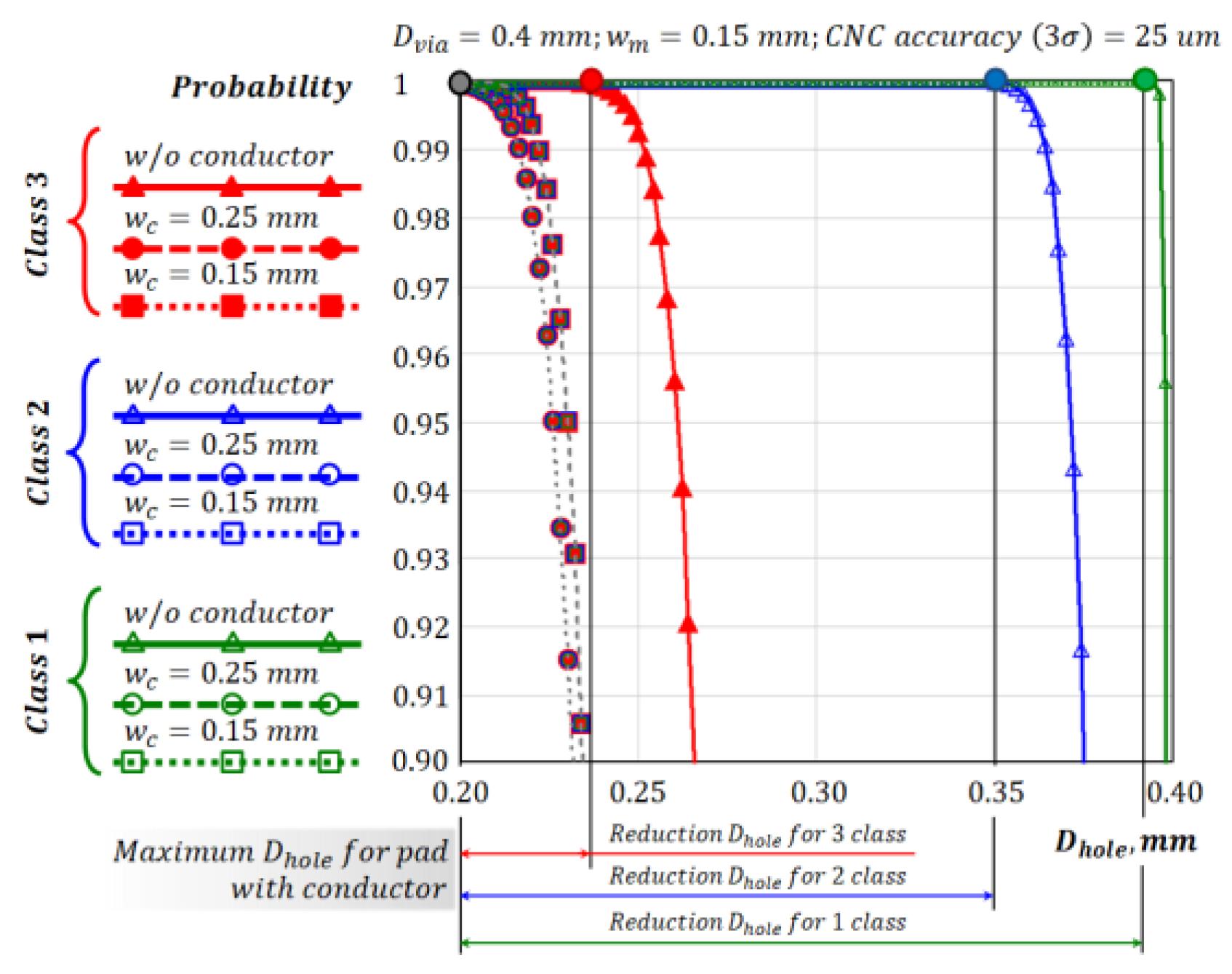

2.3. Investigation of Probability Curves for Manufacturing an Acceptable Contact Pad

Using Equation (8), we obtained curves that shows the probability of manufacturing an acceptable contact pad, depending on the CNC machine accuracy and the diameter of the hole (

Figure 4). By the accuracy of the CNC machine, we will mean the maximum value of deviation of coordinates of the input hole from the set by the program, which is equal to

. In the example we based on the manufacturing capabilities of the printed circuit board manufacturer JLCPCB [

18]:

is 0.4 mm and

is 0.2 mm. Also, in the example the accuracy parameter is taken for a Bungard CCD CNC machine (

) [

19].

On the precision side of the CNC machine, it can be seen (

Figure 4a) that reducing the reliability class will have little effect on contact pad manufacturing, as existing modern systems have a precision of about 25 µm or less, and significant differences begin at a precision later than this value.

On the other hand, from the graph of the dependence of the probability on the hole diameter (

Figure 4b) we can say that a given reliability class, as well as the size of the contact pad, largely affect the probability of acceptable manufacturing. The reliability class determines the slope of the characteristic, while the diameter of the contact pad determines the bias. In this case, the bias between the results of different classes with the same diameter is due to the need for a 50 µm annular ring for reliability class 3.

The presented dependencies describe an abstract element as a nonfunctional contact pad [

7], since it considers only the contact pad to which no conductor is connected. However, the location where the contact pad is connected to the conductor can significantly reduce the reliability of the PCB when the hole is shifted to that side. It determines the importance of considering in the model (8) the influence of the conductor on the probability of manufacturing a standard-compliant result.

3. Results

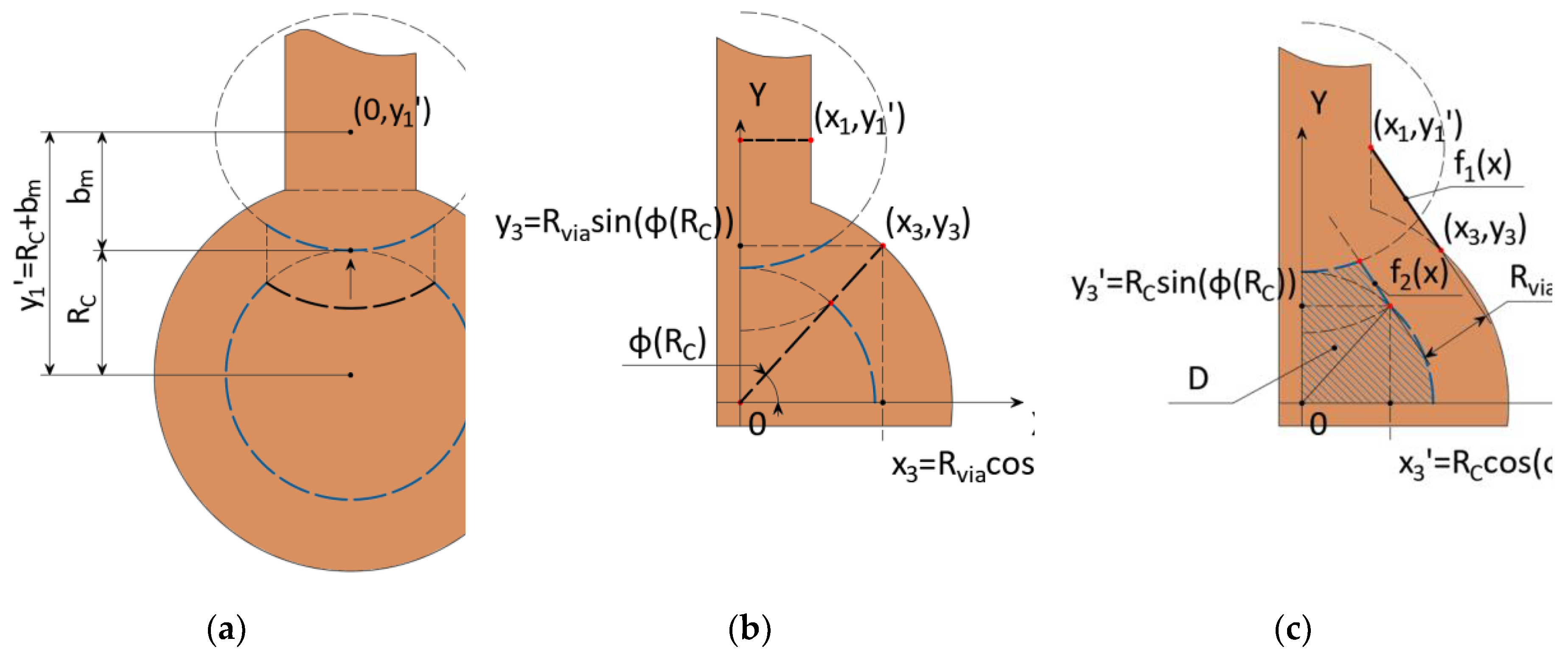

3.1. Functional Description of the Contact Pad with a Connected Conductor

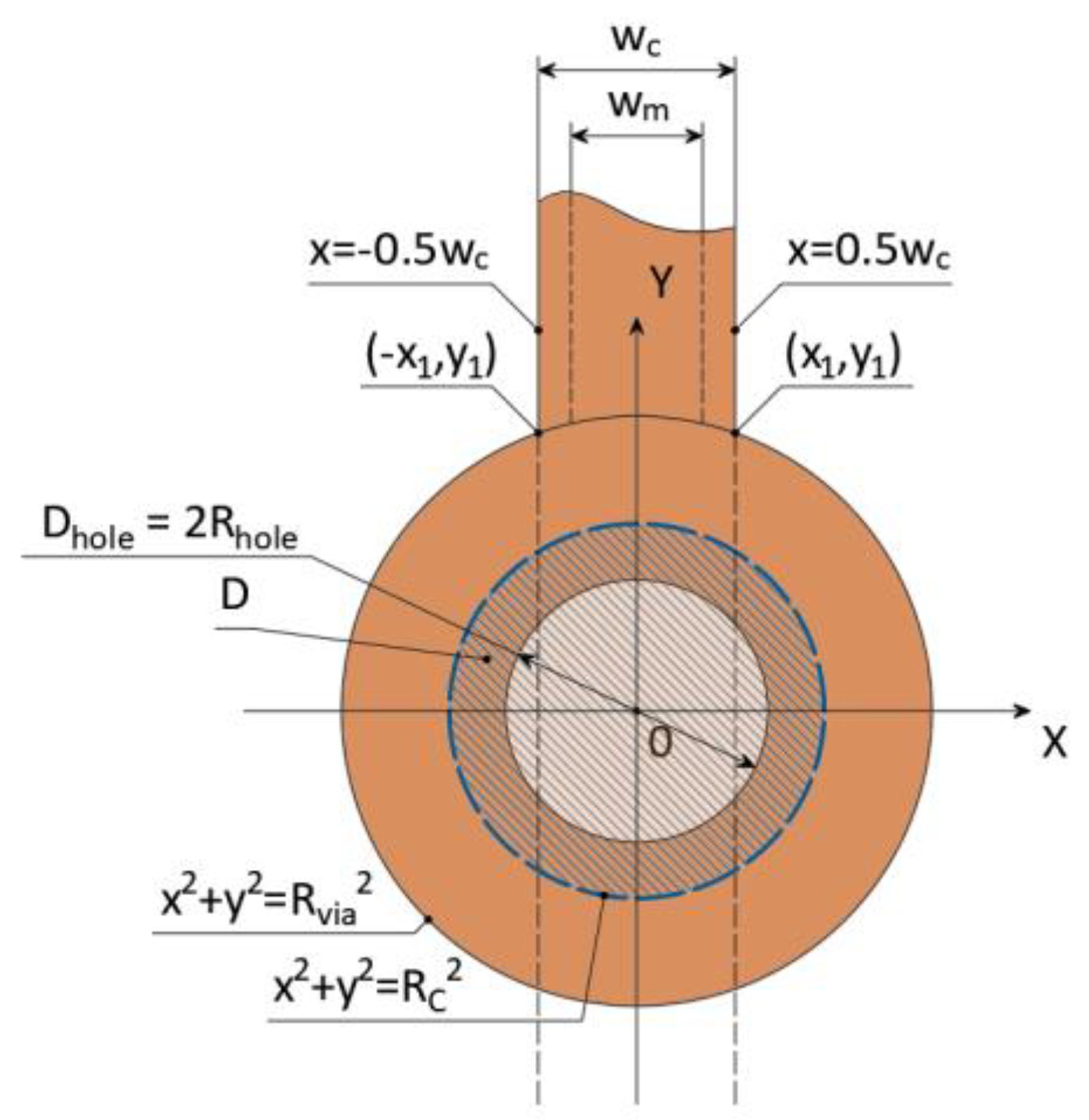

Let us consider a contact pad with a conductor connected to it from on upper side (

Figure 5). We introduce an additional restriction: the conductor is connected to the center of the contact pad without horizontal displacement, i.e., the figure is symmetrical about the

axis.

– radius of the via or plated through-hole pad;

– radius of the drilled hole with plating;

– radius of permissible hole center offset (boundary line of the area, depending on the selected reliability class);

– conductor width;

– minimum allowable conductor width.

We determine the points of the intersection of the contact pad and the conductor edges by solving the system of equations (9)–(11). As a result, we obtain the coordinates and . Also, from the solution of the system follows the restriction on the radius of the pad: .

3.2. Determination of the Permissible Offset Area of a Hole with a Connected Conductor

To determine the probability of manufacturing a pad with a conductor, it is necessary to consider an additional requirement of the standard [

16]: conductor to land junction area should not be less than 80% of the minimum conductor width

for PCBs of the reliability classes 3 and 2, and 70% for the class 1. For simplicity, we will further consider the conductor to land junction area should not be less than 100% of the minimum conductor width

. This simplification should not affect the overall appearance of the resulting model. In any case, to account for this condition, we can completely replace the minimum conductor width

with

, where is the

coefficient of permissible conductor width reduction (0.8 for class 3, 0.7 for classes 2 and 1).

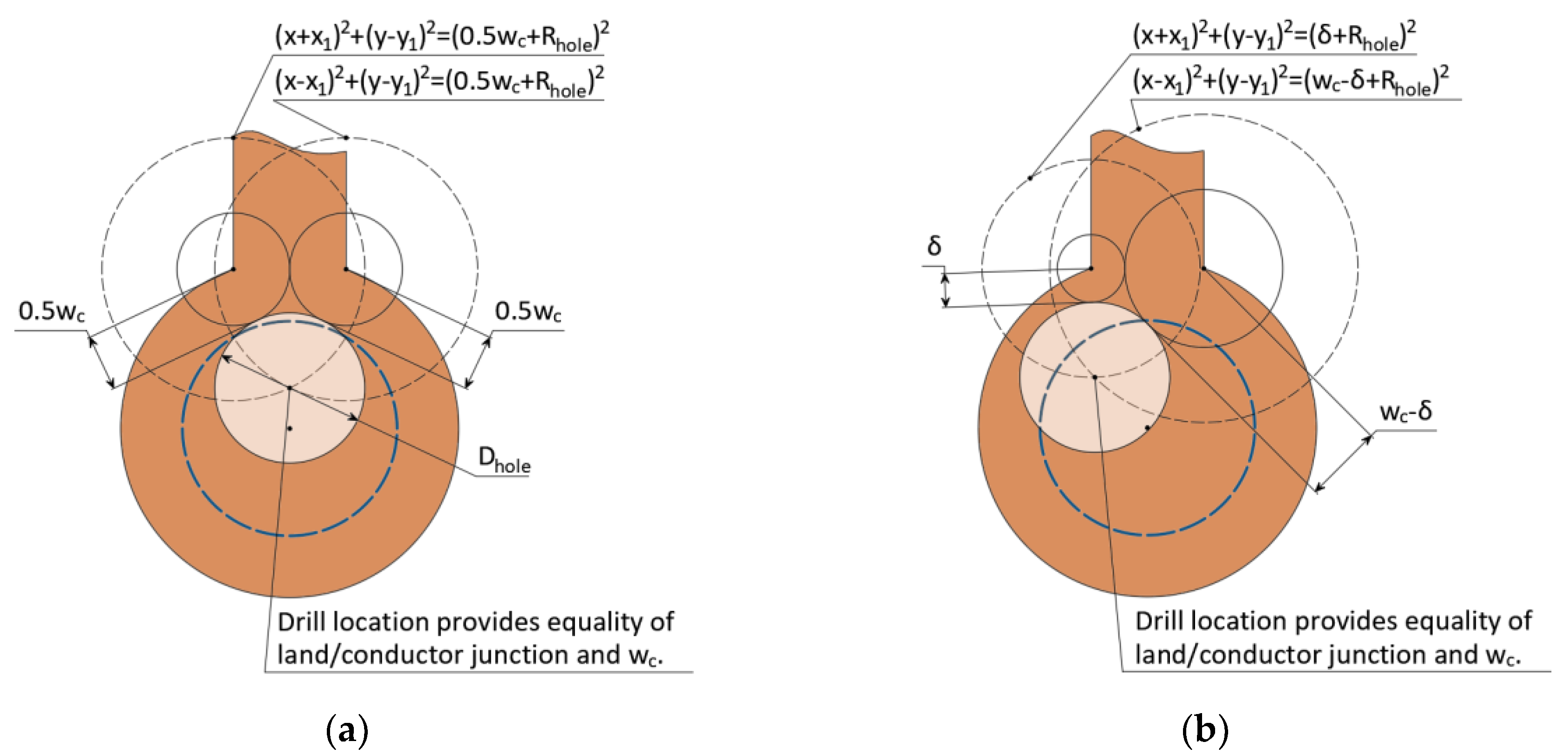

To provide a given requirement, it is necessary to determine the boundary curve on which the center of the hole can be placed. To do this we find partial solutions on the basis of which we build a general one. We assume that the conductor width

is equal to the minimum conductor width

given in the design. One solution is the symmetrical case (

Figure 6a), when a conductor with a width of

remains to the left and right of the hole. This case corresponds to the lower intersection of circles with radius

and centers at points

or solution of the system of equations (13). Let us extend the case to the general one (

Figure 6b): for this purpose, we take the left circle with radius

and the right one with radius

with limits on parameter

:

. Then the system (13) will take the form (14).

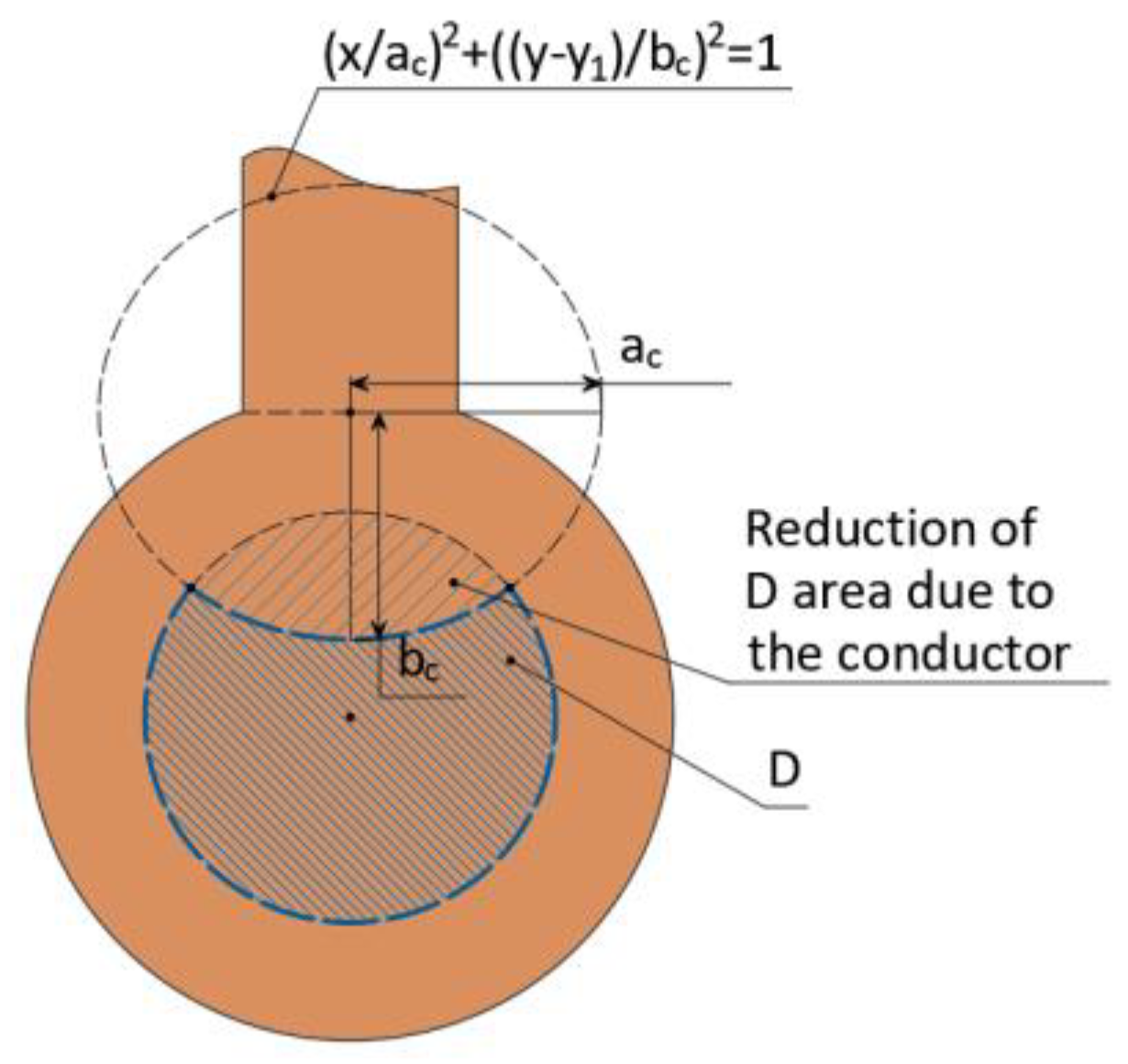

The solution of the system of equations (14) can be represented as the lower half of an ellipse described by Equation (15). The conclusion of the equation of the ellipse and the values of its semi-axes is described in

Appendix A.

Then, the offset area

of the hole will have the form shown in the

Figure 7 and consist parts of a circle with radius

(12) and an ellipse (15) with semi-axes

and

. The

Figure 7 allows visual estimation of the reduction of the

area due to the connection of the conductor to the contact pad.

However, it is not always the case that the tracing of a PCB is performed by traces of the minimum permissible width. We use a similar approach to determine the curve bounding the offset area of the hole considering the conductor, provided that the conductor width

is greater than

. To do this, it is necessary to determine the lower intersection of the circles with radii

,

and with centers in points

(

Figure 8a).

In this case, the system of equations (14) is transformed to the form (16), and the solution of the system will be defined by formula (17). The derivation of the equation of the ellipse and the values of its semi-axes is described in

Appendix B. In this case, the case

can be considered as a boundary. Given this condition, the solution (17) transforms to (15), corresponding to the maximum area of the ellipse and the maximum constraint on the area

(

Figure 8b).

Based on the resulting equations of curves (12) and (17) limiting the area

in conductor to land junction area, we form the integration limits for calculating the probability of producing an acceptable contact pad. Since according to the IPC-A-600G standard [

16] the conductor to land junction area is a 90° sector of the contact pad located near the conductor, we introduce an additional restriction on the size of the ellipse (17): it must not contain the center of the contact site, i.e.,

. Then, the area

in the 3-rd and 4-th quadrants of the coordinate plane will not change, which allows us further to consider only the 1-st and 2-nd quadrants. Also, because of the symmetry of the figure vertically with respect to the axis

, further we will consider only the first quadrant (

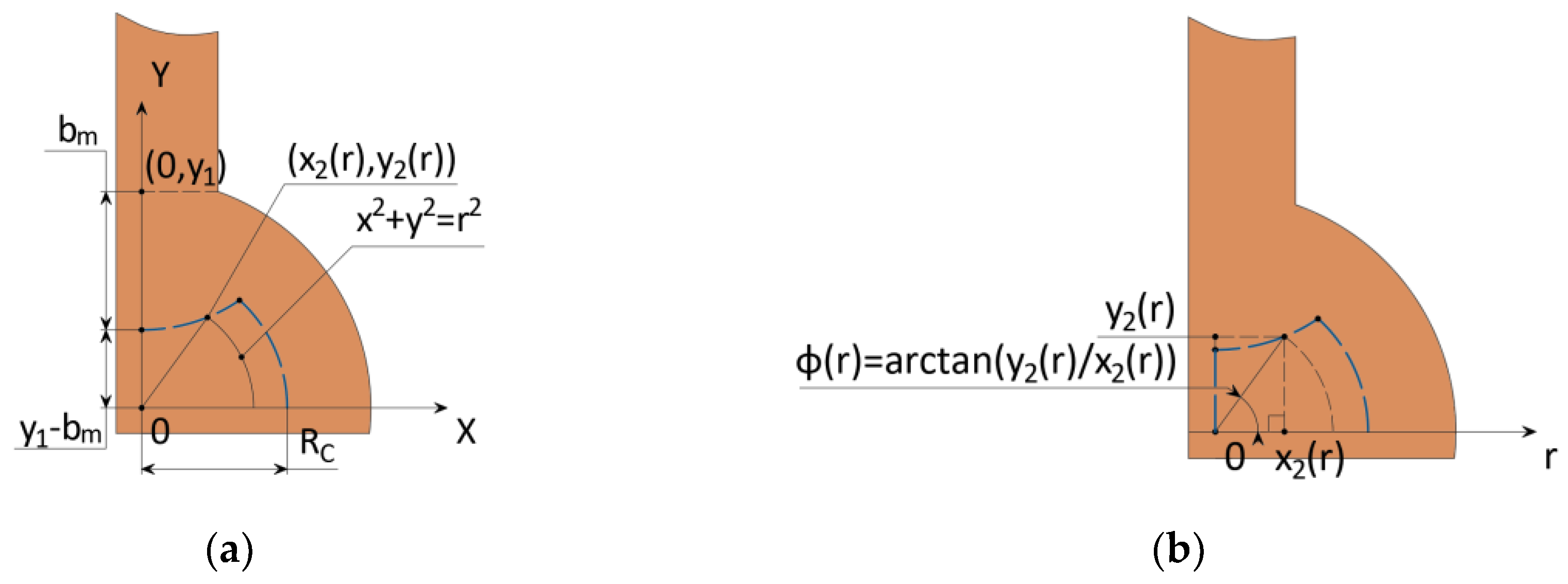

Figure 9a).

To determine the change of area

, it is necessary to find the intersection of ellipse (17) and a circle with varying radius

and center matching the center of the pad. It is described by the system of equations (18). The solution to the system of equations (18) is a point

, moving along the ellipse (17) depending on the parameter

(

Figure 9a). Knowing the coordinates of this point, we can determine the dependence of the angle on the position vector

(

Figure 9b), which determines the upper limit of integration of

area.

The partial solution of the system (18) describing the lower right intersection of the circle and the ellipse is defined by Equation (19):

It is also necessary to determine the value of the function

in the limits:

. Since in this case the entire sector from 0 to

is included in area

, then

. Then, the dependence

will be determined by Equation (20). The expression of the function

is described in

Appendix C.

Now, the probability of hitting the center of the hole in area

will consist of the probability of hitting the lower half of the circle

, which is equivalent to half the probability obtained by Equation (8) and twice the probability of hitting the area bounded by the function

, which is defined by Equation (21):

3.3. Modeling a Contact Pad with a Connected Conductor

Based on Equation (21) we plot the curves describing the probability of manufacturing a pad that complies with the standard depending on the diameter of the hole (

Figure 10), or it is equivalent to increasing the diameter of the contact pad while maintaining the diameter of the hole. From the graph we can conclude that the connection of the conductor significantly reduces the allowable hole diameter for all reliability classes. Thus, the reduction of requirements for PCBs of the reliability classes 2 and 1 relative to the 3 class becomes negligible (the requirements of the classes 1 and 2 are almost equivalent to the class 3). From the illustrated example, it can be seen that the addition of a conductor limits the maximum hole diameter to 0.2 mm (0.4 mm via diameter) for all reliability classes.

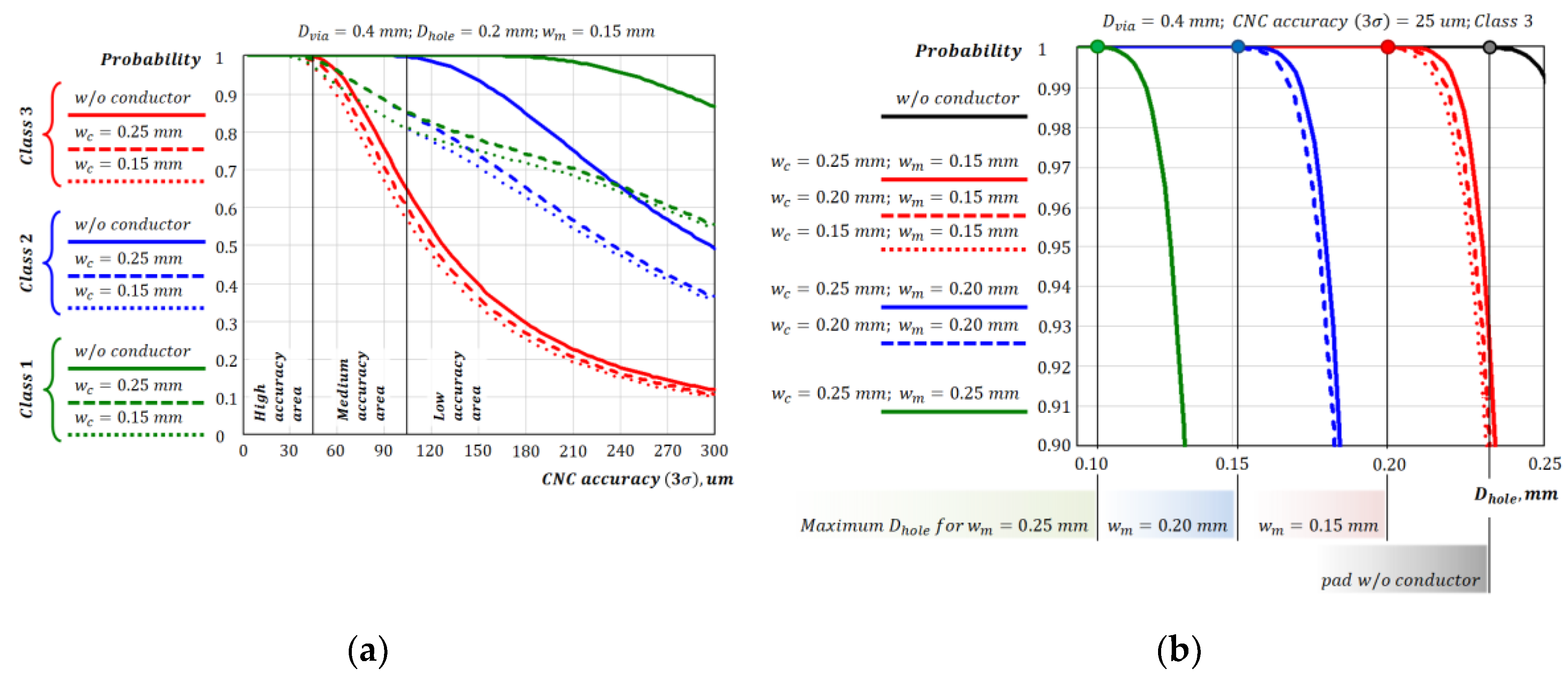

Let's evaluate the effect of CNC machine precision and conductor parameters on the probability of producing a standard-compliant pad (

Figure 11). Since in both cases the type of characteristic will be influenced by a large number of contact pad parameters, we will highlight common properties.

From the side of the influence of the CNC machine accuracy on the probability, the following conclusions can be made (

Figure 11a):

In the high-precision section (up to 45 µm), the probability is independent of the reliability class.

At the section with medium accuracy (from 45 to 105 µm) the differences between the curves begin. The probability for the 1 and 2 class boards is higher than for the 3 class boards, but between them their probability is almost the same. This suggests that the area is large enough to significantly reduce the probability of acceptable manufacturing.

At the low-precision section (from 105 µm), the difference between the 1 and 2 reliability classes becomes significant. At this section, conductor to land junction area has already influenced the resulting probability and the behavior of the curves becomes similar to the case of a nonfunctional contact pad, i.e., the probability is mainly determined by the size of the pad.

From the influence of the conductor parameters (

Figure 11b) we can see that increasing the required minimum conductor width

significantly reduces the probability of making a good contact pad, and increasing the conductor width

relative to the minimum

increases the slope of the curves.

Thus, the resulting model (21) allows us to analytically determine the probability of manufacturing a contact pad corresponding to a given reliability class, depending on the design parameters of the PCB: the width of the conductor (minimum acceptable and used ), hole diameter and the diameter of the pad . Also takes into account the peculiarities of the manufacturing process, described by the accuracy of the drilling operation.

3.4. Algorithm for Determining the Parameters of a Teardrops

To ensure that the designed layout complies with the standards, it is possible to use teardrop-shaped contact pads, which have an extension at conductor to land junction area, and they are actively used now. However, there are currently no rules for the design of teardrops. On the one hand, a teardrop that is too large will take up a lot of trace space. On the other hand, too small a teardrop will not give a positive effect. Let's form the following criterion for an optimal teardrop for contact pad: the probability of manufacturing a pad with teardrop should be equal to the probability of manufacturing a contact pad without a conductor connected to it. To make the pad with teardrop comply with the formed criterion, the following algorithm is proposed (

Figure 12).

The algorithm consists of the next steps:

Vertical displacement of the ellipse bounding the area

, so that it intersects with the circle

at only one point

(

Figure 12a). Then the center of the ellipse must have the coordinates

.

Determining the points on the conductor and the contact pad through which the teardrop’s line will pass (

Figure 12b). The first point lying on the line of the conductor must belong to the horizontal line

, since, given the displacement of the ellipse, this line is the boundary between the conductor and the contact pad. That is, the first point has coordinates

. We define the second point as the intersection point of the circle

and the line passing through the center of the coordinates and the intersection point of the circle

and the ellipse centered at

. That is, the second point will have the coordinates

.

Definition of the equation of the line

(22) forming the drop, as well as the line

closing the area

(

Figure 12c). Let us introduce the assumption that the latter line is also a line (23), which is parallel to line

(22) and passes through point

of the intersection of the circle

and the ellipse with center at

. In reality, this is true only for the class 3 of reliability, and when forming this line for the 2 and 1 classes it is necessary to use the conditions of the IPC-A-600G standard [

16], which were described earlier. However, this would complicate the appearance of the curve, while insignificantly changing the

area. It can be assumed that the straight line is a stricter criterion for limiting the area

, because the arc of the hole that extends beyond the contact area will always be smaller than the reliability class specified.

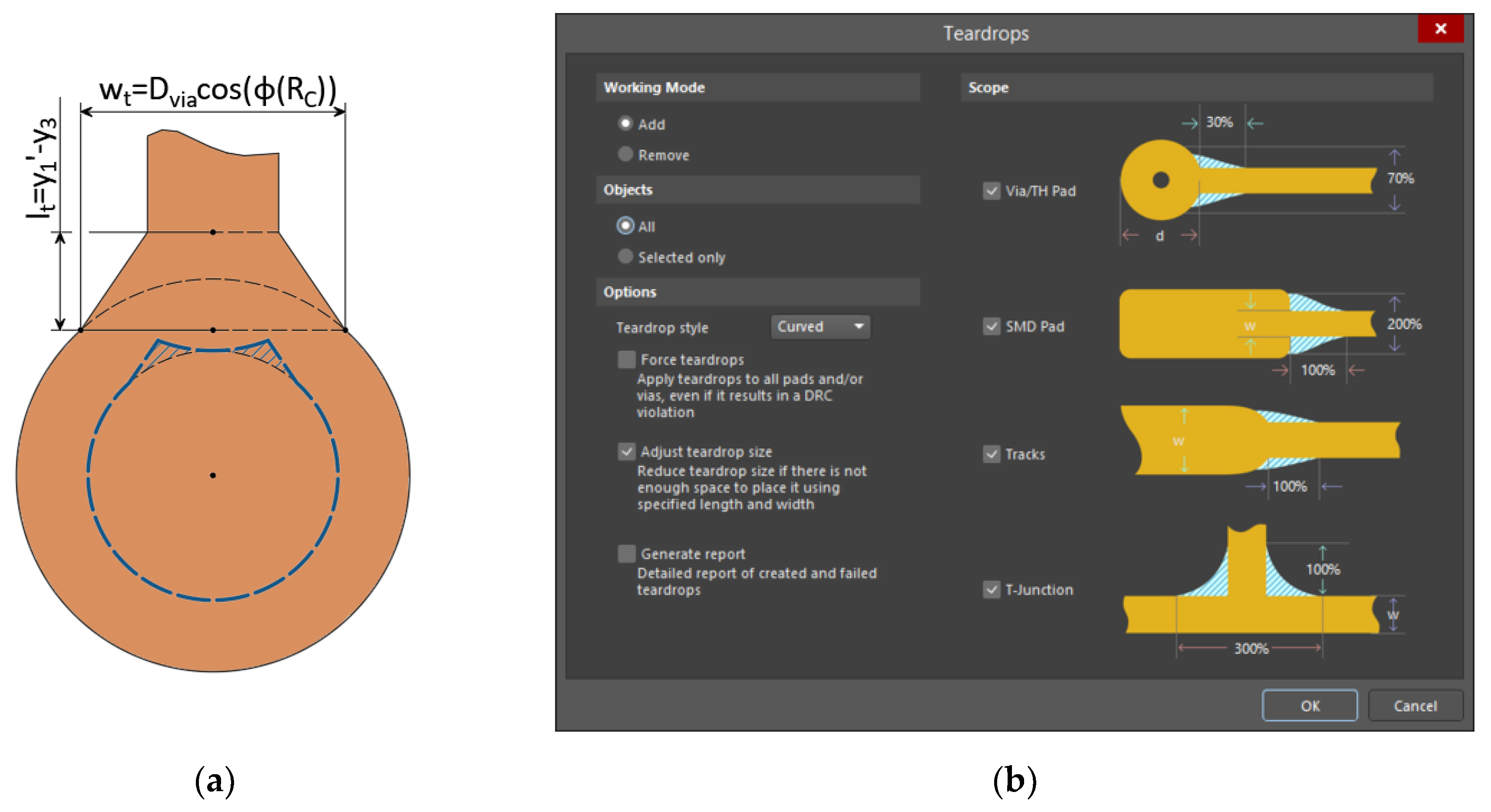

Thus, the resulting teardrop shape should provide the same or higher probability of acceptable fabrication compared to no conductor connection (

Figure 13a). Sections that extend

larger than the circle of radius

will not contribute significantly to the increase in probability because of the shape of the density function of the distribution law. On the other hand, excluding these areas requires the construction of a more complex teardrop shape. Therefore, given the small area of the areas, we can neglect them and assume that the contact site satisfies the optimality condition formed above.

Let's define the parameters of the teardrop, with which it can be more conveniently described. For example, the computer-aided design (CAD) system Altium Designer [

20] uses its length and width as a percentage of the pad diameter

(

Figure 13b). Then, the absolute and relative parameters of the teardrop will be determined by equations (24) and (25), respectively.

4. Discussion

The developed model has a lot of limitations and assumptions, the analysis of which will make it possible to determine the issues of model development that need to be solved:

Limitations of the distribution law: in the work it is assumed that the mathematical expectation is 0 and the standard deviation of hole drilling is considered constant and depends only on the accuracy parameter of hole drilling, which is declared by the manufacturer in the machine documentation. However, in reality, these characteristics are more difficult to determine, for example, the mathematical expectation will depend on the coordinates of the hole (with increasing distance from the origin of coordinates error can accumulate), and also possible change in parameters during operation due to wear of equipment.

From the manufacturing point of view, the model needs to be extended, because now it takes into account only the influence of the drilling operation. For example, during the PCB manufacturing process, etching of conductors inevitably results in lateral subtraction of the conductors, which will reduce the size of the contact pad and the size of the area of permissible hole offset

, respectively [

21]. In addition, the model does not consider displacement the layers of the PCB caused by deformation during their manufacturing.

5. Conclusions

At present, the obtained model shows the opportunity to determine the probability of manufacturing an acceptable contact pad according to the given design parameters and manufacturing process specifications, i.e., it is a quantitative criterion for evaluating the quality of a PCB. However, it also allows us to solve the opposite problem: determining the design parameters for a given probability and the characteristics of the manufacturing process or determining the necessary production line for the manufacture of an electronic device.

Also, the need for modernization of PCB CAD systems has been identified, namely, adding the possibility to create separate classes for teardrops, which is currently missing (for example, in Altium Designer CAD all drop contact pads are defined by one rule). It is necessary because the parameters of a drop contact pad depend on topology parameters, which can differ greatly within the same PCB (e.g., for signal and power traces). The addition of separate teardrop classes will increase the density of interconnects without compromising the reliability.

In future the obtained analytical model can be used as a criterion for quantitative assessment of printed circuit board quality, and its use in development process will allow to define necessary parameters of PCB design depending on manufacturing parameters of drilling operation and device reliability class.

Supplementary Materials

Not applicable.

Author Contributions

Conceptualization, M.A.K.; methodology, F.V.V.; software, M.A.K; validation, F.V.V. and O.V.Kh.; formal analysis, M.A.K.; investigation M.A.K.; resources, O.V.Kh.; data curation, O.V.Kh.; writing—original draft preparation, M.A.K.; writing—review and editing, F.V.V. and O.V.Kh.; visualization, M.A.K. and O.V.Kh.; supervision, F.V.V.; project administration F.V.V.; funding acquisition, O.V.Kh. All authors have read and agreed to the published version of the manuscript.

Funding

This work was supported financially by the Russian Science Foundation under the Scientific Project No. 23-29-10204.

Data Availability Statement

Data is contained within the article or supplementary material.

Acknowledgments

Not applicable.

Conflicts of Interest

The authors declare no conflict of interest.

Appendix A: Determining the Equation of the Curve Limiting the Permissible Offset of the Hole Center Relative to the Center of the Pad in the Conductor to Land Junction Area for the Case Where the Conductor Width is Equal to the Minimum Possible

To determine the type of curve limiting the acceptable offset of the hole center relative to the center of the contact pad in the conductor to land junction area for the case of equality of the conductor width to the minimum possible, it is necessary to solve the system of equations (A1):

Both equations in the system (A1) are expressed relative to

. Let us equate their right-hand sides to each other, square them, and substitute

(A2):

Divide the summands with and without the variable

(A3):

Expand the difference squares in both parts of the equation and express the function

(A4):

Find the definition area of the function

(A5):

Substitute the resulting function

into one of the original equations (A1) and obtain the result (A6):

Consider separately the expression under the square root of the function (A6) and transform it to the form (A7):

Thus, we can derive the solution of the system (A1) in the parametric form (A8):

From Equation (A4) we find the dependence

(A9):

Substitute

into one of the equations of system (A1) to obtain Equation (A10):

Consider separately the expression under root of Equation (A10) and transform it to the form (A11):

Consider the coefficient at

in Equation (A11) and determine that it is zero (A12):

Then Equation (A10) will take the form (A13):

Perform the following transformations (A14):

Thus, the solution of the system (A1) belongs to the equation of the ellipse (A15):

The obtained solution also has an additional restriction: only the lower half of the ellipse corresponds to the solution of the original system of equations (A1). The upper half of the ellipse is not a solution, since it appeared forcedly when squaring the original equation of the system (A1).

Appendix B: Determining the Curve Equation Limiting the Acceptable Offset of the Hole Center Relative to the Center of the Contact Pad in in the Conductor to Land Junction Area for the Case of Inequality of the Conductor Minimum Width

To determine the type of curve limiting the acceptable offset of the hole center relative to the center of the contact pad in in the conductor to land junction area, it is necessary to solve the system of equations (A16) for the case of inequality of the conductor width as minimum as possible.

Both equations are expressed relative to

. Equate their right sides to each other, squared, and substitute

(A17):

Divide the summands with and without the variable

(A18):

Expand the difference squares in both parts of the equation and express the function

(A19):

Also express the function

and find the range of the function (A20):

Substitute this function

into one of the original equations (A16) to obtain expression (A21):

Consider separately the expression under square root of Equation (A21) and obtain the following result (A22):

Perform substitutions (A23):

Then expression (A22) will take the form (A24):

Determine the components at powers of

(A25):

Then the original expression (A24) can be represented as an ellipse with semi-axes

and

(A26):

Similarly, to the case considered in

Appendix A, the solution of the original system (A16) is satisfied only by the lower half of the ellipse.

Appendix C: Derivation of the Function Limiting the Integration Area when Considering the "Conductor—Contact Pad" System

In order to determine the function limiting the integration region

, it is necessary to solve the system of equations (A27):

Let's express

from the upper equation of the system and substitute it in the lower one (A28):

Solve the resulting Equation (A30):

Consider separately the expression under square root in the function

(54) and transform it to the form (A31):

Then

, given that we are looking only for the lower intersection, converts to the form (A32):

Substitute the function

into the upper equation of system (C1) to obtain

(A33):

Thus, the function

will be equal to (A34):

References

- Medvedev, A.M. Electronic components and mounting substrates. Continuous integration. Components and technologies 2006, 12, 124–134. [Google Scholar]

- Busurin, V.I., Korobkov, K.A., Shleenkin, L.A., Makarenkova, N.A. Compensation Linear Acceleration Converter Based on Optical Tunneling. In Proceedings of the 2020 27th Saint Petersburg International Conference on Integrated Navigation Systems (ICINS), Saint Petersburg, Russia, 25–27 May 2020, pp. 1–4. [CrossRef]

- Busurin, V.I., Korobkov, V.V., Korobkov, K.A., Koshevarova, N.A. Micro-Opto-Electro-Mechanical System Accelerometer Based on Coarse-Fine Processing of Fabry–Perot Interferometer Signals. Measurement Techniques 2021, 63, pp. 883–890. [CrossRef]

- Vanсov, S., Khomutskaya, O. A method for increasing the reliability of obtaining holes in printed circuit boards. In Proceedings of the 2021 International Conference on Electrotechnical Complexes and Systems (ICOECS), Ufa, Russia, 16–18 November 2021, pp. 513–515.

- Khomutskaya, O., Vanсov, S., Korobkov, M., Medvedev, A. The method of automated evaluation of the deformation of the printed circuit board. In Proceedings of the 2021 International Conference on Electrotechnical Complexes and Systems (ICOECS),Ufa, Russia, 16 – 18 November 2021, pp. 510–512. pp. 510–512.

- Vantsov, S.V. , Vasil’ev, F.V., Medvedev, A.M., Khomutskaya, O. Quasi-Determinate Model of Thermal Phenomena in Drilling Laminates. Russian Engineering Research 2018, 38, 1074–1076. [Google Scholar] [CrossRef]

- Vantsov, S.V. Vantsov, S.V., Vasil’ev, F.V., Medvedev, A.M., Khomutskaya, O.V. Influence of Nonfunctional Contact Pads on Printed-Circuit Performance. Russian Engineering Research 2020, 40, pp. 442–445. [CrossRef]

- Vasilyev, F. Physical Reliability of Electronics, Moscow Aviation Institute (National Research University): Moscow, Russia, 2022, p.160.

- Amosov, A.G. , Golikov, V.A., Kapitonov, M.V., Vasilyev, F.V., Rozhdestvensky, O.K. Engineering and Analytical Method for Estimating the Parametric Reliability of Products by a Low Number of Tests, Inventions 2022, 7(1), p.24. [CrossRef]

- Cherkasov, K. Cherkasov, K., Meshkov, S., Makeev, M., Ivanov, Yu., Shashurin, V., Tsvetkov, Yu., Khlopov., B. Computer statistical experiment for analysis of resonant-tunneling diodes I-V characteristics. International Scientific Conference Energy Management of Municipal Facilities and Sustainable Energy Technologies EMMFT 2018 2018, 983. pp. 626-634. [CrossRef]

- Makeev, M.O. , Sinyakin, V.Y., Meshkov, S.A. Reliability prediction of resonant tunneling diodes and non-linear radio signal converters based on them under influence of temperature factor and ionizing radiations, Advances in the Astronautical Sciences 2020, 170, pp. 655–664.

- Makeev, M.O.; Sinyakin, V.; Meshkov, S.A. Reliability prediction of radio frequency identification passive tags power supply systems based on A3B5 resonant-tunneling diodes. In Proceedings of the 2018 International Russian Automation Conference (RusAutoCon 2018), Sochi, Russia, 09–16 September 2018, pp. 1–5. pp. 1–5. [CrossRef]

- Medvedev, A., Vasilyev, F., Sokolsky, M. Testing of hidden defects in interconnections. Amazonia Investiga 2019, 8(22), pp. 746–756.

- Korobkov, M., Vasilyev, F., Mozharov, V. A Comparative Analysis of Printed Circuit Boards with Surface-Mounted and Embedded Components under Natural and Forced Convection. Micromachines 2022, 13, 634, p.11. [CrossRef]

- IPC-6012B Qualification and Performance Specification for Rigid Printed Boards.

- IPC–A–600G. Acceptability of Printed Boards.

- Ventzel, E.S. Probability Theory, 6th ed.; Vyssh. shk.: Moscow, Russia, 1999; p. 576. [Google Scholar]

- PCB Manufacturing & Assembly Capabilities. Available online: https://jlcpcb.com/capabilities/pcb-capabilities (accessed on 26 February 2023).

- Bungard CCD/ATC machining center. Available online: https://www.protehnology.ru/obrabatyvaushiy-centr-bungard-elektronik-bungard-ccdatc (accessed on 07 May 2023).

- Teardrops. Available online: https://www.altium.com/ru/documentation/altium-designer/pcb-dlg-teardropoptionsformteardrops-ad/?version=22 (accessed on 26 February 2023).

- Vasilyev F., Isaev V., Korobkov M. The influence of the PCB design and the process of their manufacturing on the possibility of a defect-free production. Przeglad Elektrotechniczny 2021, 97(3), pp. 91-96.

Figure 1.

IDEF0 top-level diagram of the proposed method of reliability assessment.

Figure 1.

IDEF0 top-level diagram of the proposed method of reliability assessment.

Figure 2.

Determination of the area of permissible displacement of the hole center relative to the center of the contact pad according to IPC-A-600G [

16]: (

a) For 3 reliability class; (

b) For 2 reliability class; (

c) For 1 reliability class.

Figure 2.

Determination of the area of permissible displacement of the hole center relative to the center of the contact pad according to IPC-A-600G [

16]: (

a) For 3 reliability class; (

b) For 2 reliability class; (

c) For 1 reliability class.

Figure 3.

Formalization of the drilling process: (a) Probability characteristics of hitting the contact pad during drilling; (b) Coordinate field of a Bungard CCD CNC machine.

Figure 3.

Formalization of the drilling process: (a) Probability characteristics of hitting the contact pad during drilling; (b) Coordinate field of a Bungard CCD CNC machine.

Figure 4.

Probability of making an acceptable contact pad: (a) Depending on the precision of the CNC machine; (b) Depending on the diameter of the hole.

Figure 4.

Probability of making an acceptable contact pad: (a) Depending on the precision of the CNC machine; (b) Depending on the diameter of the hole.

Figure 5.

Design parameters of the contact pad.

Figure 5.

Design parameters of the contact pad.

Figure 6.

Permissible location of the hole for the case when the conductor width is equal to the minimum acceptable (): (a) The hole center is located on the symmetry axis; (b) The hole center is located asymmetrically.

Figure 6.

Permissible location of the hole for the case when the conductor width is equal to the minimum acceptable (): (a) The hole center is located on the symmetry axis; (b) The hole center is located asymmetrically.

Figure 7.

Constraint on the offset area of the hole including the conductor ().

Figure 7.

Constraint on the offset area of the hole including the conductor ().

Figure 8.

Permissible location of the hole for the case when the width of the conductor is greater than the minimum acceptable (): (a) Particular case of the hole position; (b) Changes in the area with relation to the case when .

Figure 8.

Permissible location of the hole for the case when the width of the conductor is greater than the minimum acceptable (): (a) Particular case of the hole position; (b) Changes in the area with relation to the case when .

Figure 9.

Changing the area of acceptable offset of the hole center: (a) Determining the intersection of the circle (12) with the ellipse (17); (b) Determining the function in the polar coordinate system.

Figure 9.

Changing the area of acceptable offset of the hole center: (a) Determining the intersection of the circle (12) with the ellipse (17); (b) Determining the function in the polar coordinate system.

Figure 10.

Probability of manufacturing an acceptable pad depending on the diameter of the hole, taking into account the connected conductor (overlapping curves of different reliability classes are marked in gray).

Figure 10.

Probability of manufacturing an acceptable pad depending on the diameter of the hole, taking into account the connected conductor (overlapping curves of different reliability classes are marked in gray).

Figure 11.

Probability of making an acceptable pad considering the connected conductor: (a) Depending on the accuracy of the CNC machine; (b) Depending on the diameter of the hole.

Figure 11.

Probability of making an acceptable pad considering the connected conductor: (a) Depending on the accuracy of the CNC machine; (b) Depending on the diameter of the hole.

Figure 12.

Stages of constructing a teardrop: (a) Shift of the ellipse limiting the area ; (b) Determination of key points; (c) Drawing lines.

Figure 12.

Stages of constructing a teardrop: (a) Shift of the ellipse limiting the area ; (b) Determination of key points; (c) Drawing lines.

Figure 13.

The shape of the

area of the pad with teardrop and its construction parameters: (

a) Length and width of the teardrop; (

b) Teardrop parameters, defined in Altium Designer [

20].

Figure 13.

The shape of the

area of the pad with teardrop and its construction parameters: (

a) Length and width of the teardrop; (

b) Teardrop parameters, defined in Altium Designer [

20].

Figure 14.

Construction of teardrops: solid red color indicates areas of 3 class, blue – for 2 class, green – for 1 class; dashed line indicates increase of area after changing the form of the pad.

Figure 14.

Construction of teardrops: solid red color indicates areas of 3 class, blue – for 2 class, green – for 1 class; dashed line indicates increase of area after changing the form of the pad.

Table 1.

Teardrop parameters.

Table 1.

Teardrop parameters.

| Reliability class |

Teardrop

parameter |

=0.15 mm |

=0.20 mm |

=0.15 mm |

| 3 |

Length, , %

(, mm) |

21

(0.08) |

15

(0.06) |

7

(0.03) |

Width, , %

(, mm) |

78

(0.31) |

75

(0.30) |

70

(0.28) |

| 2 |

Length, , %

(, mm) |

44

(0.18) |

41

(0.16) |

35

(0.14) |

Width, , %

(, mm) |

87

(0.35) |

87

(0.35) |

87

(0.35) |

| 1 |

Length, , %

(, mm) |

55

(0.22) |

52

(0.21) |

48

(0.19) |

Width, , %

(, mm) |

83

(0.33) |

84

(0.34) |

85

(0.34) |

Table 2.

Required accuracy of the CNC machine, μm.

Table 2.

Required accuracy of the CNC machine, μm.

| Reliability class |

=0.15 mm) |

=0.20 mm) |

=0.25 mm) |

With teardrop |

| 3 |

30 |

32 |

37 |

45 |

| 2 |

30 |

32 |

37 |

102 |

| 1 |

30 |

32 |

37 |

152 |

|

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).