Submitted:

14 April 2023

Posted:

14 April 2023

You are already at the latest version

Abstract

Keywords:

1. Introduction

-

development of NN technology for cryptographic data protection;development of the structure of the system of NN cryptographic protection and real-time data transmission;development of components of onboard systems of NN cryptographic encryption-decryption of data;implementation of the specialized hardware components of NN cryptographic data encryption on FPGA.

2. Related Works

3. The development of NN technology for cryptographic data protection

3.1. Structure of NN technology of cryptographic data protection

-

research and development of theoretical foundations of neuro-like cryptographic data protection;research and development of new algorithms and structures of neuro-like encryption and decryption of data focused on modern element base;modern element base with the ability to program the structure;means for automated design of software and hardware.

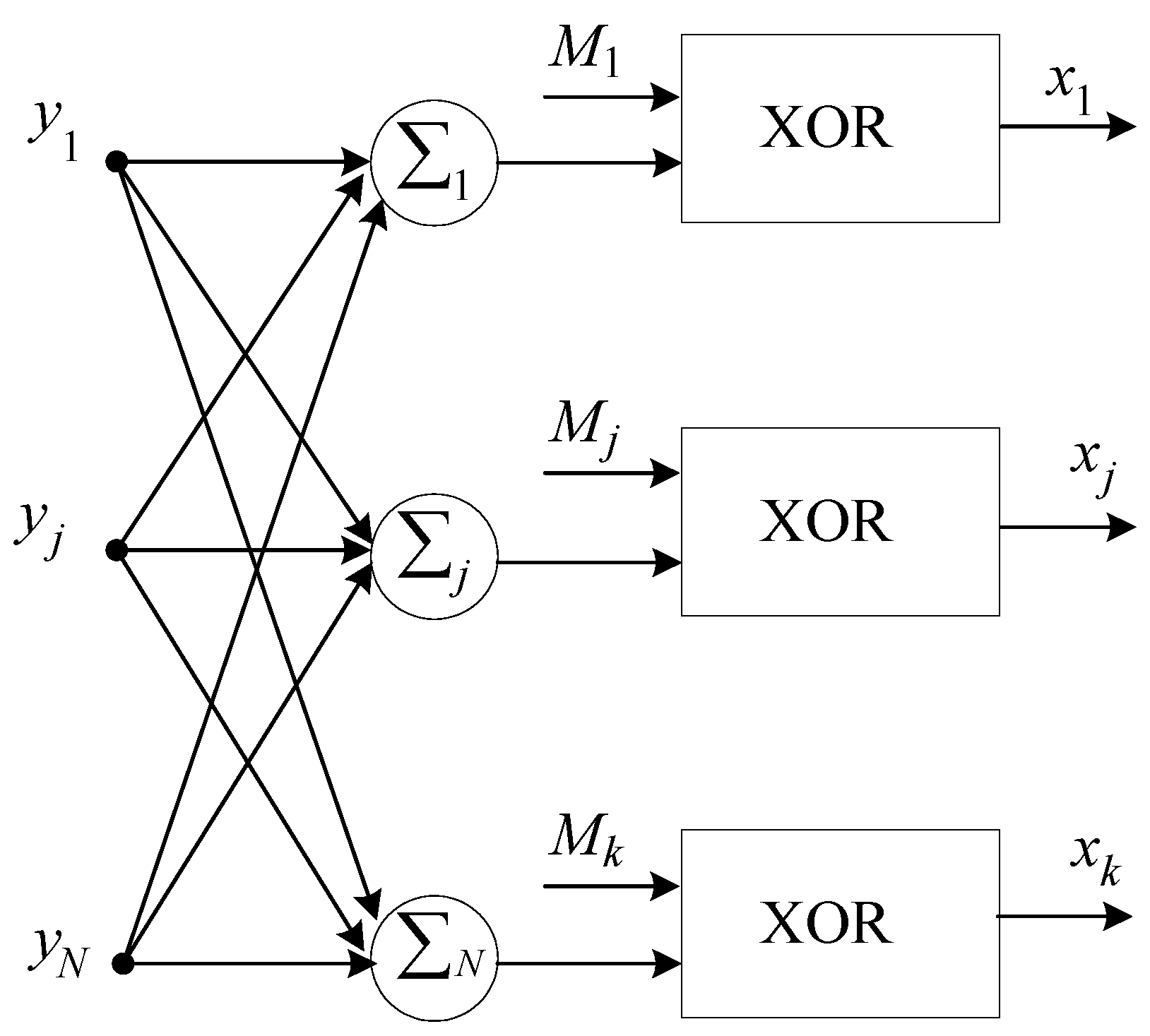

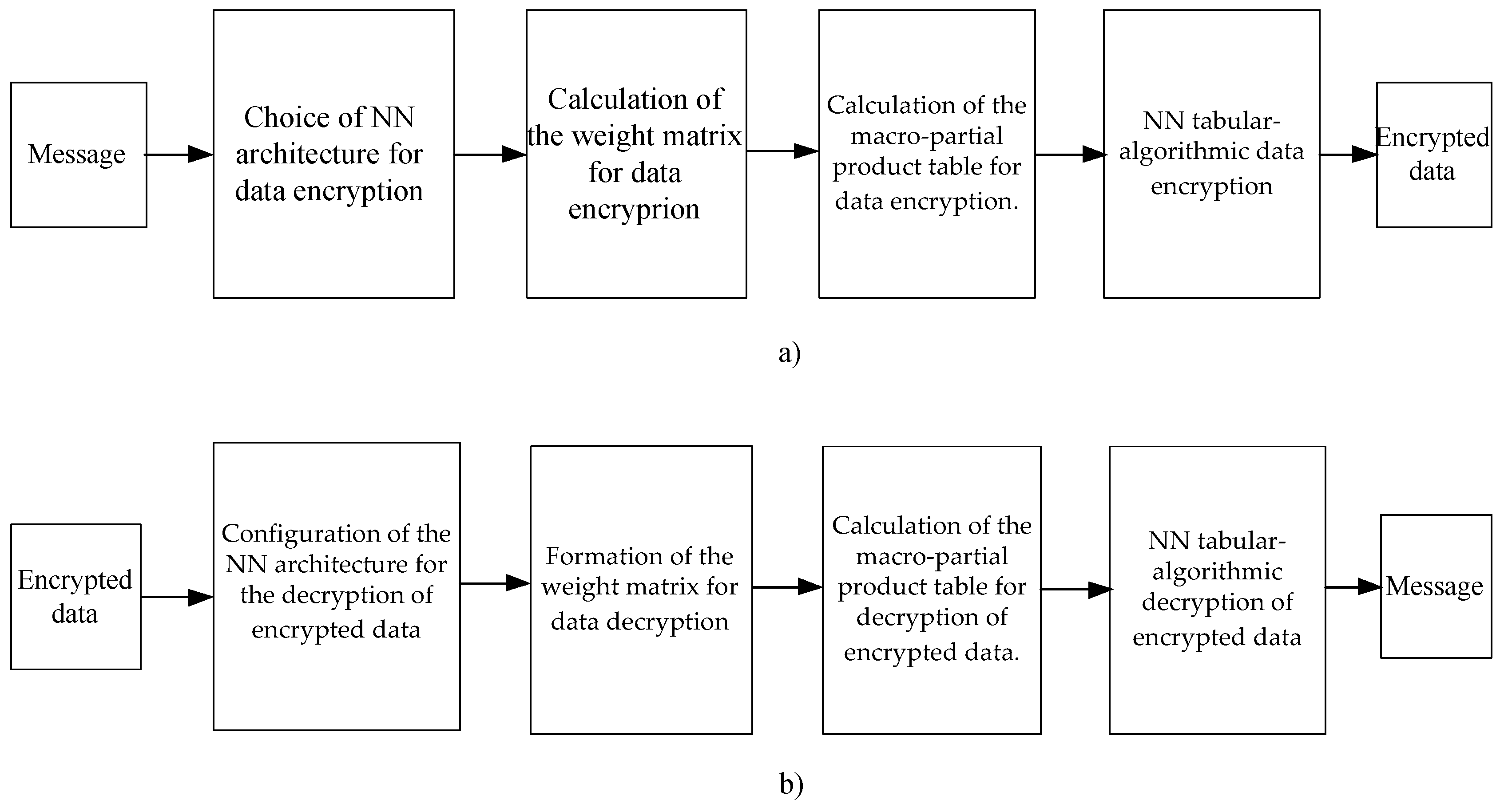

3.2. Main stages of NN encryption

-

defining the largest common order of weights ;calculation of the order difference for each weight coefficient: ;shift the mantissa to the right by a difference of orders ;calculation of macro-partial product for the case when ;determining the number of overflow bits q in the macro-partial product for the case when ;obtaining scalable mantissas by shifting them to the right by the number of overflow bits;adding to the largest common order of weight the number of overflow bits q, as per formula .

-

define the greatest order ;for each encrypted data calculate the difference between the orders ;by performing shift of the mantissa to the right by the difference of orders we obtain mantissa of the encrypted data reduced to the greatest common order.

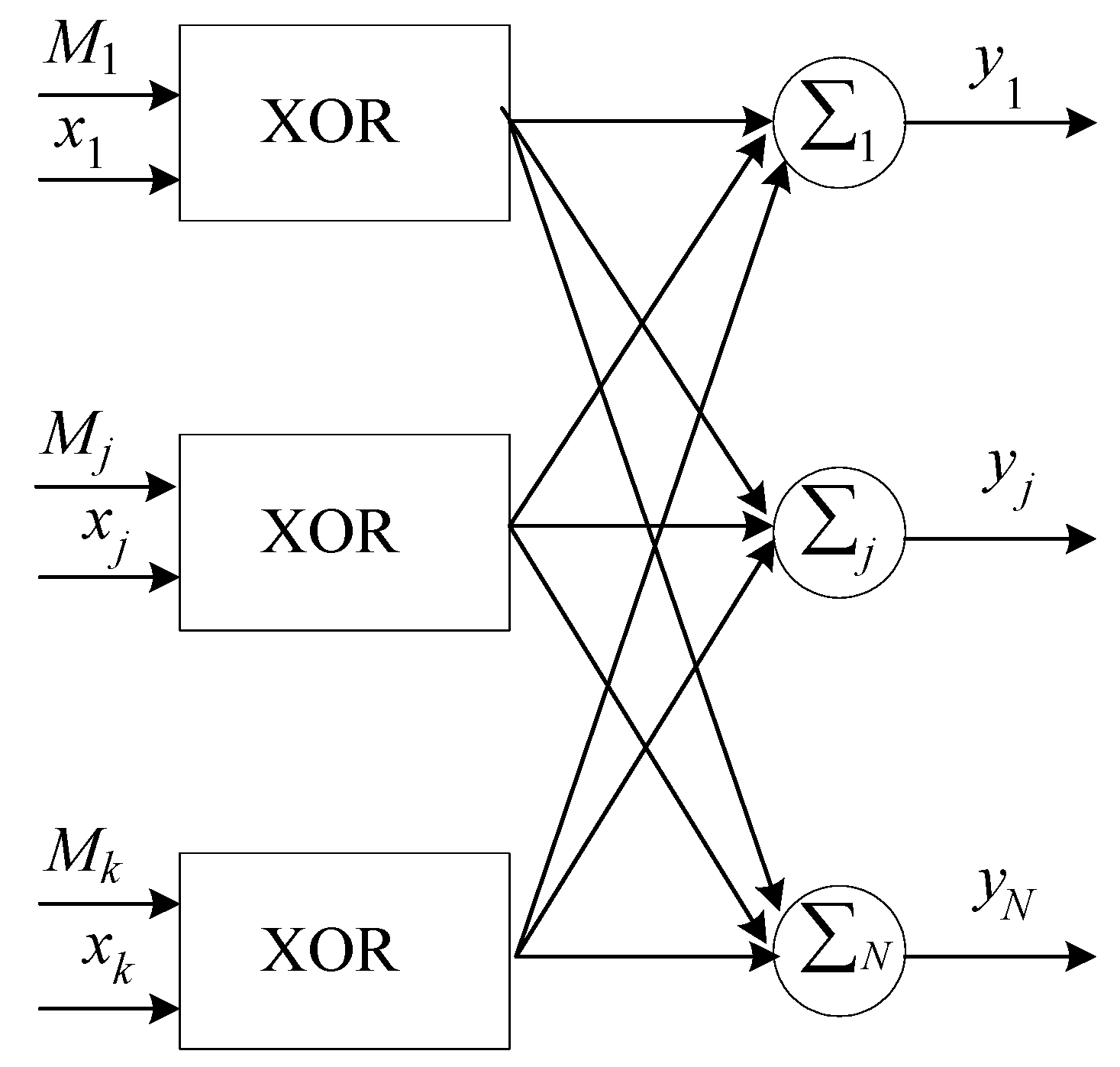

3.3. The main stages of NN cryptographic data decryption

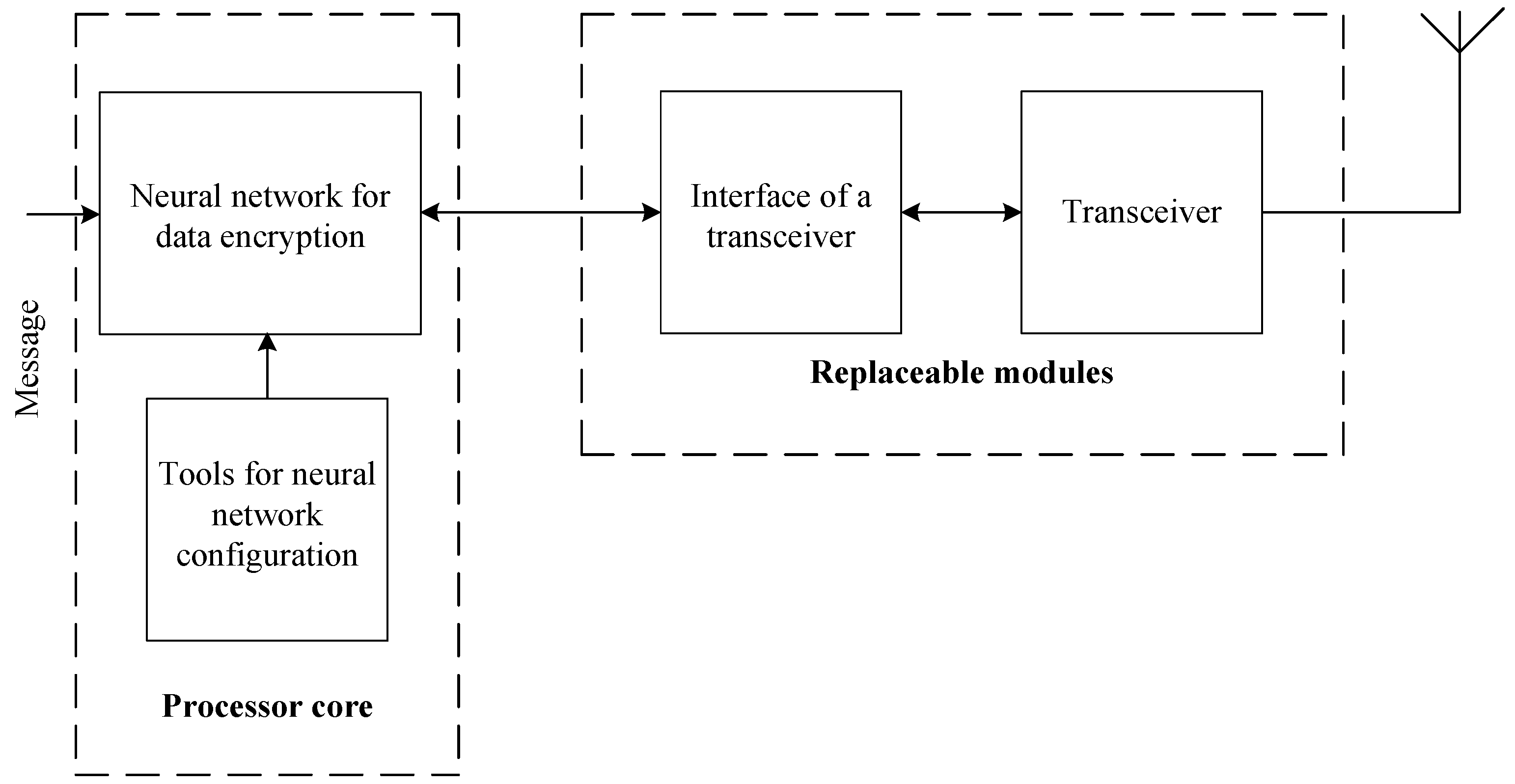

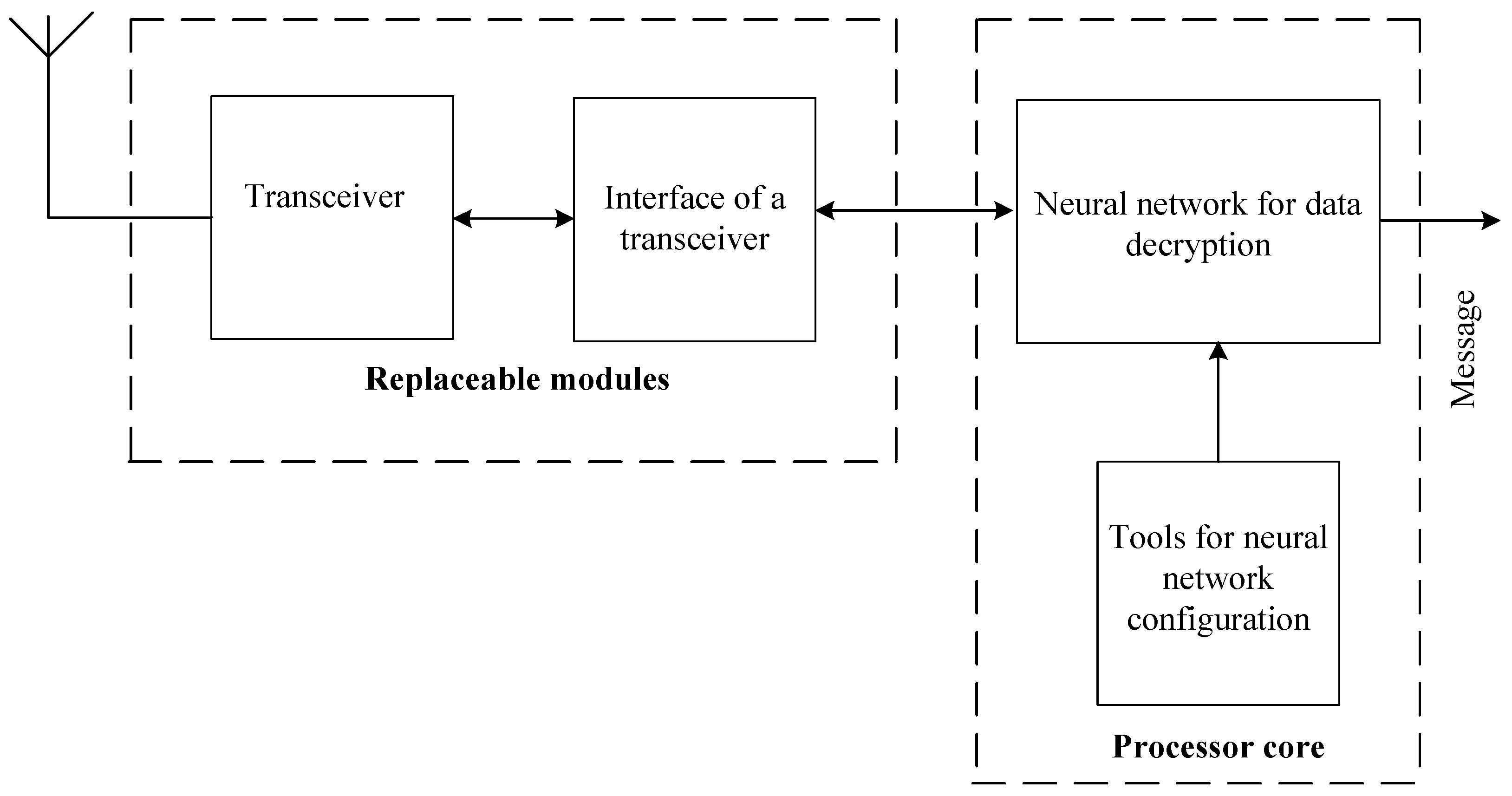

4. The structure of the system for NN cryptographic data protection and transferring in real-time mode

-

research and development of theoretical foundations of NN cryptographic data encryption and decryption;development of new tabular-algorithmic algorithms and structures for NN cryptographic data encryption and decryption;modern element base, development environment and computer-aided design tools.

-

changeable composition of the equipment, which foresees the presence of the processor core and replaceable modules, with which the core adapts to the requirements of a particular application;modularity, which involves the development of system components in the form of functionally complete devices;pipeline and spatial parallelism in data encryption and decryption;

- the openness of the software, which provides opportunities for development and improvement, maximising the use of standard drivers and software;

- specialising and adapting hardware and software to the structure of tabular algorithms for encrypting and decrypting data;

- the programmability of hardware module architecture through the use of programmable logic integrated circuits.

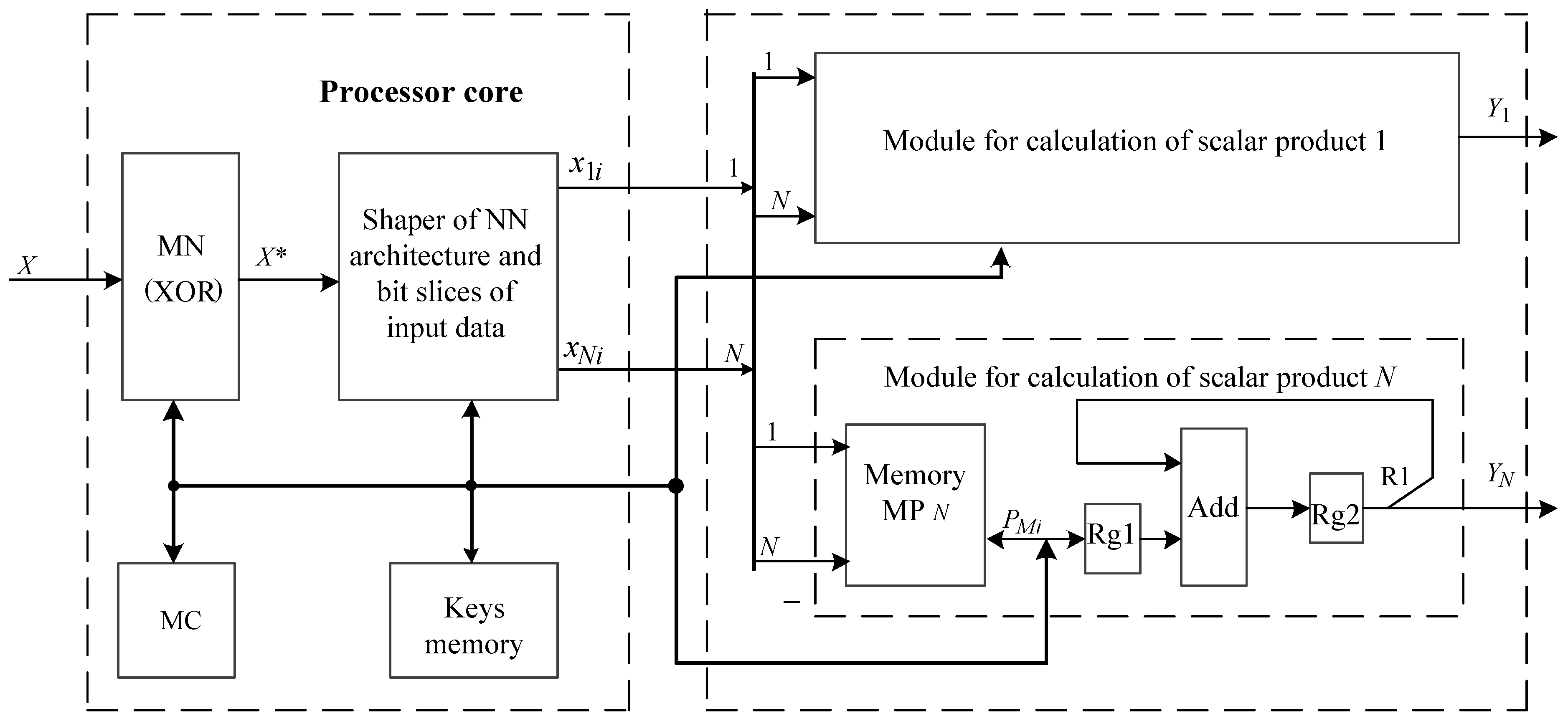

5. Development of the components of the onboard system for NN cryptographic data encryption and decryption

5.1. Development of the structure of the components for NN cryptographic data encryption and decryption

-

to develop an algorithm for the onboard system of NN encryption-decryption of data and present it in the form of a specified flow graph;to design the structure of the onboard system for NN data encryption-decryption with the maximum efficiency of equipment use, taking into account all the limitations and providing real-time data processing;to determine the main characteristics of neural elements and carry out their synthesis;to choose exchange methods, determine the necessary connections and develop algorithms for exchange between system components;to determine the order of implementation in time of NN data encryption-decryption processes and develop algorithms for their management.

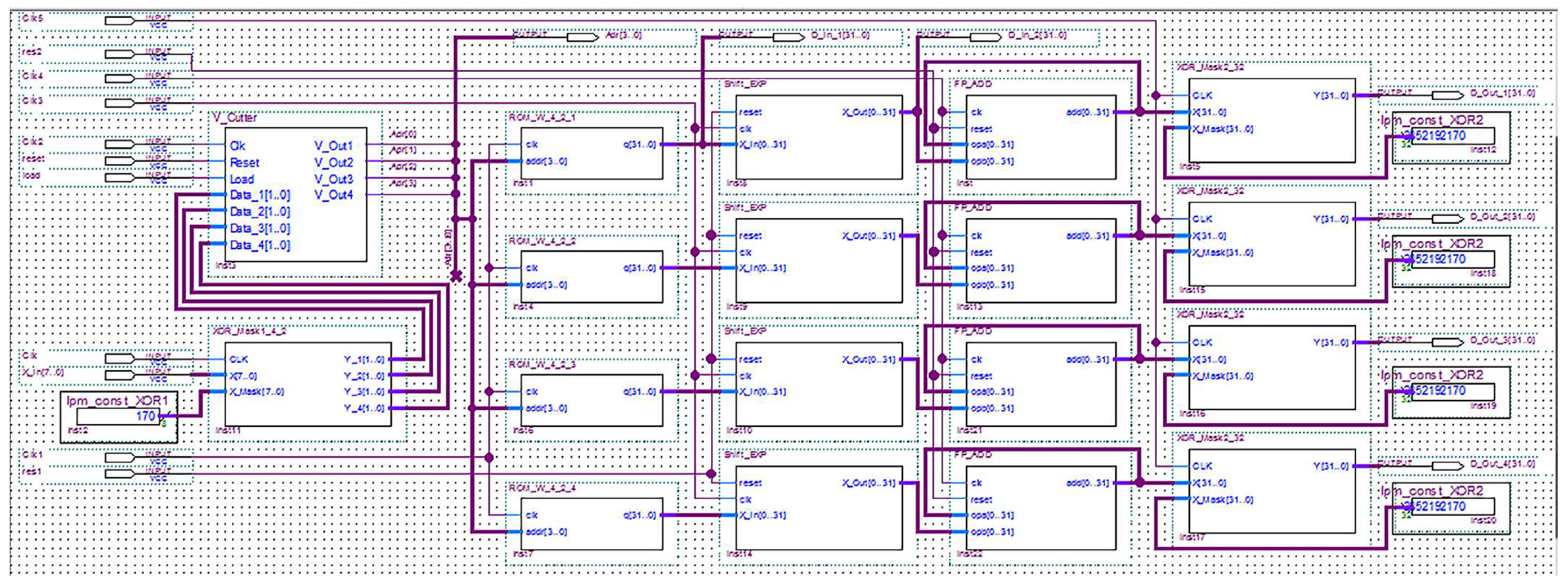

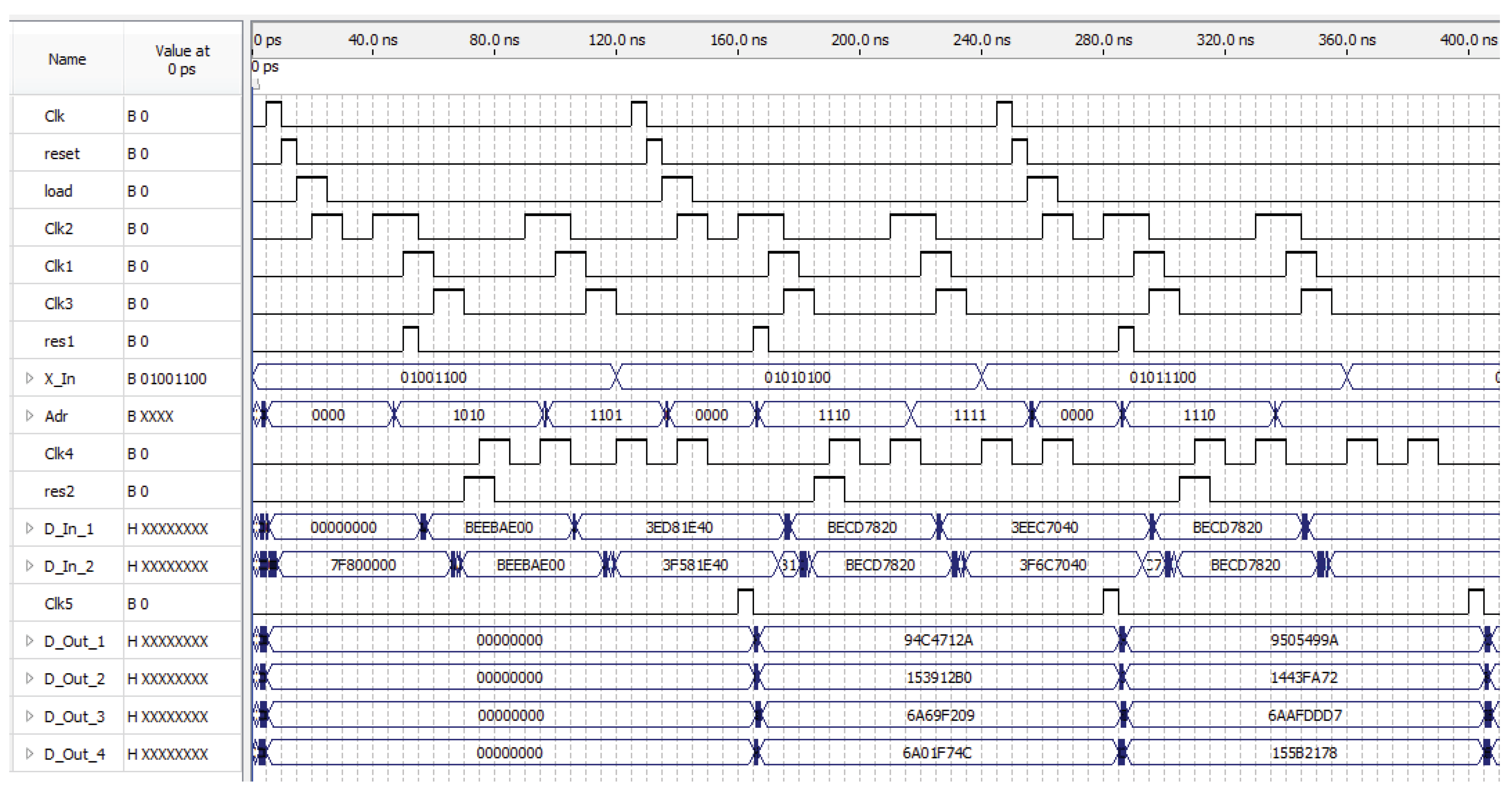

5.2. Implementation of the specialized hardware components of NN cryptographic data encryption on FPGA

6. Conclusions

Author Contributions

Conflicts of Interest

References

- Han, B.; Qin, D.; Zheng, P.; Ma, L.; Teklu, M.B. Modeling and performance optimization of unmanned aerial vehicle channels in urban emergency management. ISPRS Int. J. Geo-Inf. 2021, 10, 478. [Google Scholar] [CrossRef]

- Śledź, S.; Ewertowski, M.W.; Piekarczyk, J. Applications of unmanned aerial vehicle (UAV) surveys and Structure from Motion photogrammetry in glacial and periglacial geomorphology. Geomorphology 2021, 378, 107620. [Google Scholar] [CrossRef]

- Zhang, C.; Zou, W.; Ma, L.; Wang, Z. Biologically inspired jumping robots: A comprehensive review. Robotics Auton. Syst. 2020, 124, 103362. [Google Scholar] [CrossRef]

- Weng, Z.; Yang, Y.; Wang, X.; Wu, L.; Hua, S.; Zhang, H.; Meng, Z. Parentage analysis in giant grouper (epinephelus lanceolatus) using microsatellite and SNP markers from genotyping-by-sequencing data. Genes 2021, 12, 1042. [Google Scholar] [CrossRef] [PubMed]

- Boreiko, O.; Teslyuk, V.; Zelinskyy, A.; Berezsky, O. Development of models and means of the server part of the system for passenger traffic registration of public transport in the “smart” city. EEJET 2017, 1, 40–47. [Google Scholar] [CrossRef]

- Kim, K.; Kang, Y. Drone security module for UAV data encryption. In Proceedings of the 2020 International Conference on Information and Communication Technology Convergence (ICTC), Jeju, Korea (South); 2020; pp. 1672–1674. [Google Scholar] [CrossRef]

- Samanth, S.; K V, P.; Balachandra, M. Security in Internet of Drones: A Comprehensive Review. Cogent Engineering 2022, 9, 2029080. [Google Scholar] [CrossRef]

- Kong, P.-Y. A survey of cyberattack countermeasures for unmanned aerial vehicles. IEEE Access 2021, 9, 148244–148263. [Google Scholar] [CrossRef]

- Shafique, A.; Mehmood, A.; Elhadef, M.; Khan, K.H. A lightweight noise-tolerant encryption scheme for secure communication: An unmanned aerial vehicle application. PLOS ONE 2022, 17, e0273661. [Google Scholar] [CrossRef]

- Verma, A.; Ranga, V. Security of RPL based 6LoWPAN Networks in the Internet of Things: A Review. IEEE Sensors J. 2020, 20, 5666–5690. [Google Scholar] [CrossRef]

- Morales-Molina, C.D.; Hernandez-Suarez, A.; Sanchez-Perez, G.; Toscano-Medina, L.K.; Perez-Meana, H.; Olivares-Mercado, J.; Portillo-Portillo, J.; Sanchez, V.; Garcia-Villalba, L.J. A Dense Neural Network Approach for Detecting Clone ID Attacks on the RPL Protocol of the IoT. Sensors 2021, 21, 3173. [Google Scholar] [CrossRef]

- Sohaib, O.; Hussain, W.; Asif, M.; Ahmad, M.; Mazzara, M. A PLS-SEM neural network approach for understanding cryptocurrency adoption. IEEE Access 2020, 8, 13138–13150. [Google Scholar] [CrossRef]

- Holovatyy, A.; Łukaszewicz, A.; Teslyuk, V.; Ripak, N. Development of AC Voltage Stabilizer with Microcontroller-Based Control System. In Proceedings of the 2022 IEEE 17th International Conference on Computer Sciences and Information Technologies (CSIT); Institute of Electrical and Electronics Engineers, 2022; pp. 527–530. [Google Scholar] [CrossRef]

- Grodzki, W.; Łukaszewicz, A. Design and manufacture of unmanned aerial vehicles (UAV) wing structure using composite materials. Materialwissenschaft und Werkstofftechnik 2015, 46, 269–278. [Google Scholar] [CrossRef]

- Łukaszewicz, A.; Szafran, K.; Jóźwik, J. CAx techniques used in UAV design process. In Proceedings of the 2020 IEEE 7th International Workshop on Metrology for AeroSpace (MetroAeroSpace); 2020; pp. 95–98. [Google Scholar] [CrossRef]

- Łukaszewicz, A.; Skorulski, G.; Szczebiot, R. The main aspects of training in the field of computer aided techniques (CAx) in mechanical engineering. In Proceedings of the 17th International Scientific Conference on Engineering for Rural Development, Jelgava, Latvia, 23–25 May 2018; pp. 865–870. [Google Scholar] [CrossRef]

- Łukaszewicz, A.; Miatluk, K. Reverse Engineering Approach for Object with Free-Form Surfaces Using Standard Surface-Solid Parametric CAD System. Solid State Phenomena 2009, 147–149, 706–711. [Google Scholar] [CrossRef]

- Miatliuk, K.; Łukaszewicz, A.; Siemieniako, F. Coordination method in design of forming operations of hierarchical solid objects. In Proceedings of the 2008 International Conference on Control, Automation and Systems, ICCAS 2008; pp. 2724–2727. [CrossRef]

- Puchalski, R.; Giernacki, W. UAV Fault Detection Methods, State-of-the-Art. Drones 2022, 6, 330. [Google Scholar] [CrossRef]

- Zietkiewicz, J.; Kozierski, P.; Giernacki, W. Particle swarm optimisation in nonlinear model predictive control; comprehensive simulation study for two selected problems. International Journal of Control 2021, 94, 2623–2639. [Google Scholar] [CrossRef]

- Kownacki, C.; Ambroziak, L. Adaptation Mechanism of Asymmetrical Potential Field Improving Precision of Position Tracking in the Case of Nonholonomic UAVs. Robotica 2019, 37, 1823–1834. [Google Scholar] [CrossRef]

- Kownacki, C.; Ambroziak, L.; Ciężkowski, M.; Wolniakowski, A.; Romaniuk, S.; Bożko, A.; Ołdziej, D. Precision Landing Tests of Tethered Multicopter and VTOL UAV on Moving Landing Pad on a Lake. Sensors 2023, 23, 2016. [Google Scholar] [CrossRef]

- Basri, E.I.; Sultan, M.T.H.; Basri, A.A.; Mustapha, F.; Ahmad, K.A. Consideration of Lamination Structural Analysis in a Multi-Layered Composite and Failure Analysis on Wing Design Application. Materials 2021, 14, 3705. [Google Scholar] [CrossRef] [PubMed]

- Al-Haddad, L.A.; Jaber, A.A. An Intelligent Fault Diagnosis Approach for Multirotor UAVs Based on Deep Neural Network of Multi-Resolution Transform Features. Drones 2023, 7, 82. [Google Scholar] [CrossRef]

- Yang, J.; Gu, H.; Hu, C.; Zhang, X.; Gui, G.; Gacanin, H. Deep Complex-Valued Convolutional Neural Network for Drone Recognition Based on RF Fingerprinting. Drones 2022, 6, 374. [Google Scholar] [CrossRef]

- Holovatyy, A.; Teslyuk, V.; Lobur, M.; Sokolovskyy, Y.; Pobereyko, S. Development of Background Radiation Monitoring System Based on Arduino Platform. International Scientific and Technical Conference on Computer Science and Information Technologies 2018, 121–124. [Google Scholar] [CrossRef]

- Holovatyy, A.; Teslyuk, V.; Lobur, M.; Szermer, M.; Maj, C. Mask Layout design of single-and double-arm electrothermal microactuators. In Proceedings of the 2016 XII International Conference on Perspective Technologies and Methods in MEMS Design (MEMSTECH); 2016; pp. 28–30. [Google Scholar] [CrossRef]

- Volna, E.; Kotyrba, M.; Kocian, V.; Janosek, M. Cryptography Based On Neural Network. In Proceedings of the 26th European Conference on Modeling and Simulation (ECMS 2012), Koblenz, Germany, 29 May–1 June 2012; European Council for Modeling and Simulation. Troitzsch, K.G., Moehring, M., Lotzmann, U., Eds.; pp. 386–391. [Google Scholar] [CrossRef]

- Shihab, K. A backpropagation neural network for computer network security. Journal of Computer Science 2006, 2, 710–715. [Google Scholar] [CrossRef]

- Sagar, V.; Kumar, K. A symmetric key cryptographic algorithm using counter propagation network (CPN). In Proceedings of the 2014 ACM International Conference on Information and Communication Technology for Competitive Strategies, (ICTCS’14), Udaipur Rajasthan India, 14–16 November 2014. [Google Scholar] [CrossRef]

- Arvandi, M.; Wu, S.; Sadeghian, A.; Melek, W.W.; Woungang, I. Symmetric cipher design using recurrent neural networks. In Proceedings of the IEEE International Joint Conference on Neural Networks; 2006; pp. 2039–2046. [Google Scholar] [CrossRef]

- Tsmots, I.; Tsymbal, Y.; Khavalko, V.; Skorokhoda, O.; Teslyuk, T. Neural-like means for data streams encryption and decryption in real time. In Proceedings of the 2018 IEEE Second International Conference on Data Stream Mining & Processing (DSMP), Lviv, Ukraine, 21–25 August 2018; pp. 438–443. [Google Scholar] [CrossRef]

- Scholz, M.; Fraunholz, M.; Selbig, J. Nonlinear principal component analysis: neural network models and applications. In Principal Manifolds for Data Visualization and Dimension Reduction; Lecture Notes in Computational Science and Engineering; Gorban, A.N., Kégl, B., Wunsch, D.C., Zinovyev, A.Y., Eds.; Springer: Berlin/Heidelberg, Germany, 2008; Volume 58. [Google Scholar] [CrossRef]

- Rabyk, V.; Tsmots, I.; Lyubun, Z.; Skorokhoda, O. Method and Means of Symmetric Real-time Neural Network Data Encryption. In Proceedings of the 2020 IEEE 15th International Scientific and Technical Conference on Computer Sciences and Information Technologies (CSIT 2020); 2020; Volume 1, pp. 47–50. [Google Scholar] [CrossRef]

- Chang, A.X.M.; Martini, B.; Culurciello, E. Recurrent Neural Networks Hardware Implementation on FPGA. arXiv 2015. [Google Scholar] [CrossRef]

- Nurvitadhi, E.; et al. Can FPGAs beat GPUs in accelerating next-generation deep neural networks? In Proceedings of the 2017 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays, Monterey, California, USA, 22–24 February 2017; pp. 5–14. [Google Scholar] [CrossRef]

- Misra, J.; Saha, I. Artificial neural networks in hardware: A survey of two decades of progress. Neurocomputing 2010, 74, 239–255. [Google Scholar] [CrossRef]

- Guo, K.; et al. From model to FPGA: Software-hardware co-design for efficient neural network acceleration. In Proceedings of the 2016 IEEE Hot Chips 28 Symposium (HCS); 2016; pp. 1–27. [Google Scholar] [CrossRef]

- Ovtcharov, K.; et al. Accelerating Deep Convolutional Neural Networks Using Specialized Hardware. Microsoft Research Whitepaper. 2016. Available online: https://www.microsoft.com/en-us/research/wp-content/uploads/2016/02/CNN20Whitepaper.pdf (accessed on 29 April 2022).

- Wang, Y.; Xu, J.; Han, Y.; Li, H.; Li, X. DeepBurning: automatic generation of FPGA-based learning accelerators for the neural network family. In Proceedings of the 53rd Annual Design Automation Conference (DAC’16), Association for Computing Machinery, New York, NY, USA; Article 110. pp. 1–6. [CrossRef]

- Nurvitadhi, E.; Sheffield, D.; Sim, J.; Mishra, A.; Venkatesh, G.; Marr, D. Accelerating Binarized Neural Networks: Comparison of FPGA, CPU, GPU, and ASIC. In Proceedings of the 2016 International Conference on Field-Programmable Technology (FPT); 2016; pp. 77–84. [Google Scholar] [CrossRef]

- Yayik, A.; Kutlu, Y. Neural Network Based Cryptography. Neural Network Worldc 2014, 24, 177–192. [Google Scholar] [CrossRef]

- Govindu, G.; Zhuo, L.; Choi, S.; Prasanna, V. Analysis of high-performance floating-point arithmetic on FPGAs. In Proceedings of the 18th International Parallel and Distributed Processing Symposium (IPDPS 2004), Santa Fe, New Mexico, USA, 26–30 April 2004; p. 149. [Google Scholar] [CrossRef]

- Holovatyy, A.; Teslyuk, V.; Lobur, M. VHDL-AMS model of delta-sigma modulator for A/D converter in MEMS interface circuit. In Proceedings of the 2015 XI International Conference on Perspective Technologies and Methods in MEMS Design (MEMSTECH); 2015; pp. 55–57. [Google Scholar] [CrossRef]

- Holovatyy, A.; Lobur, M.; Teslyuk, V. VHDL-AMS model of mechanical elements of MEMS tuning fork gyroscope for the schematic level of computer-aided design. In Proceedings of the 2008 International Conference on Perspective Technologies and Methods in MEMS Design; 2008; pp. 138–140. [Google Scholar] [CrossRef]

- Electronic components database. Available online: https://www.digchip.com/datasheets/parts/datasheet/033/EP3C16F484C6.php (accessed on 29 April 2022).

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).