Submitted:

23 April 2026

Posted:

27 April 2026

You are already at the latest version

Abstract

Keywords:

1. Introduction

2. The Main Recommendations for Building a GaAs Op-Amp Based on an "Folded" Cascode

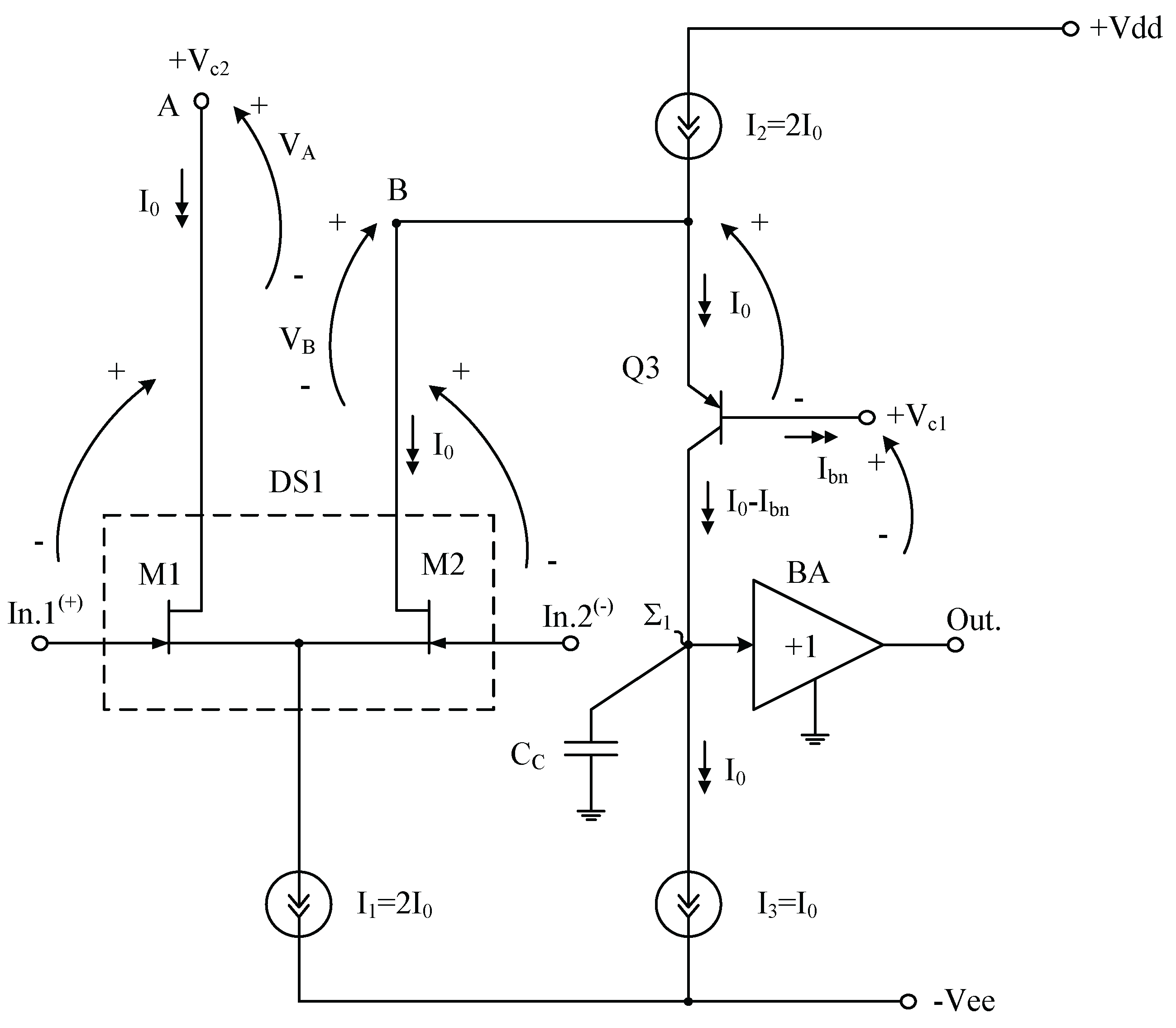

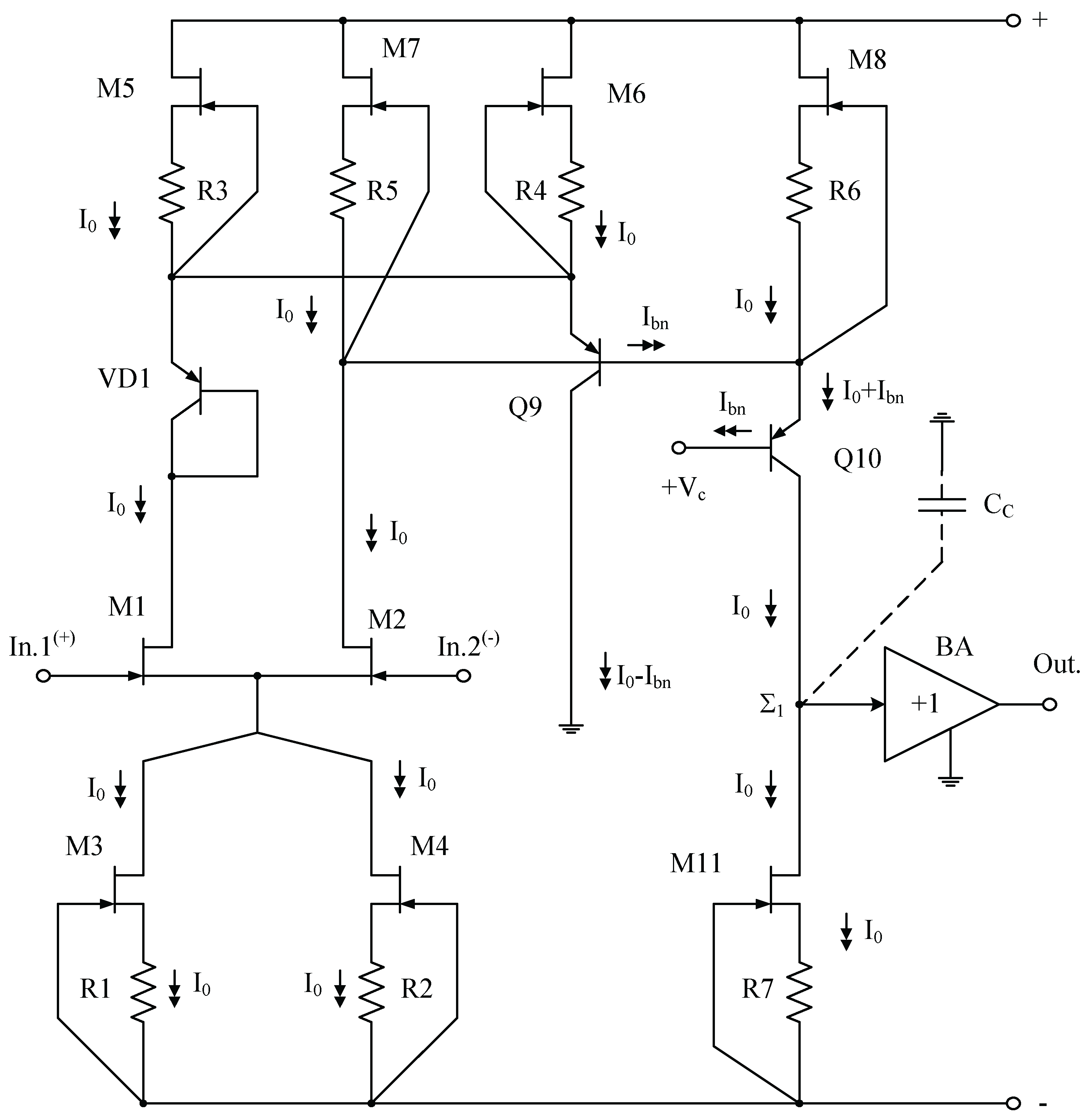

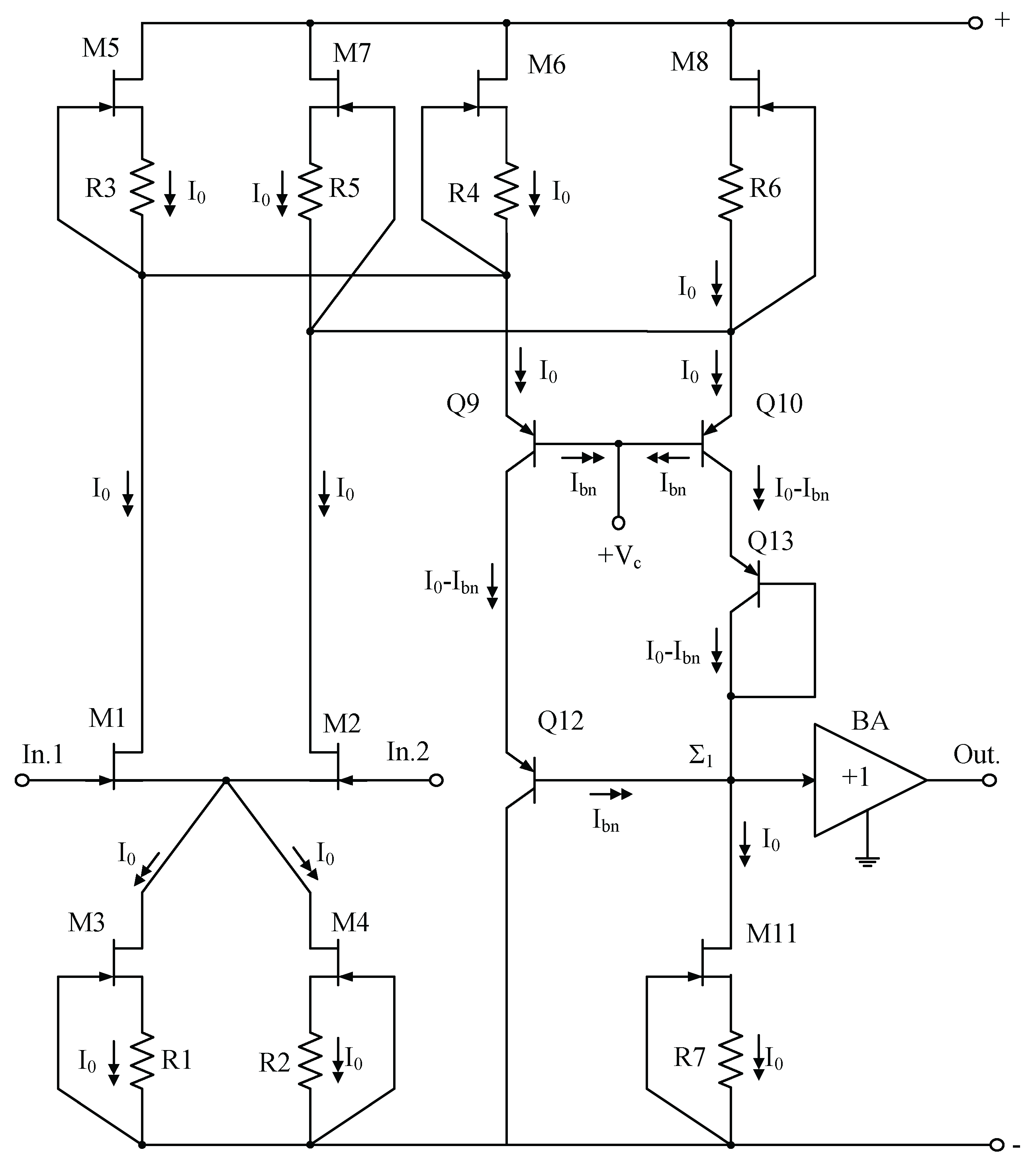

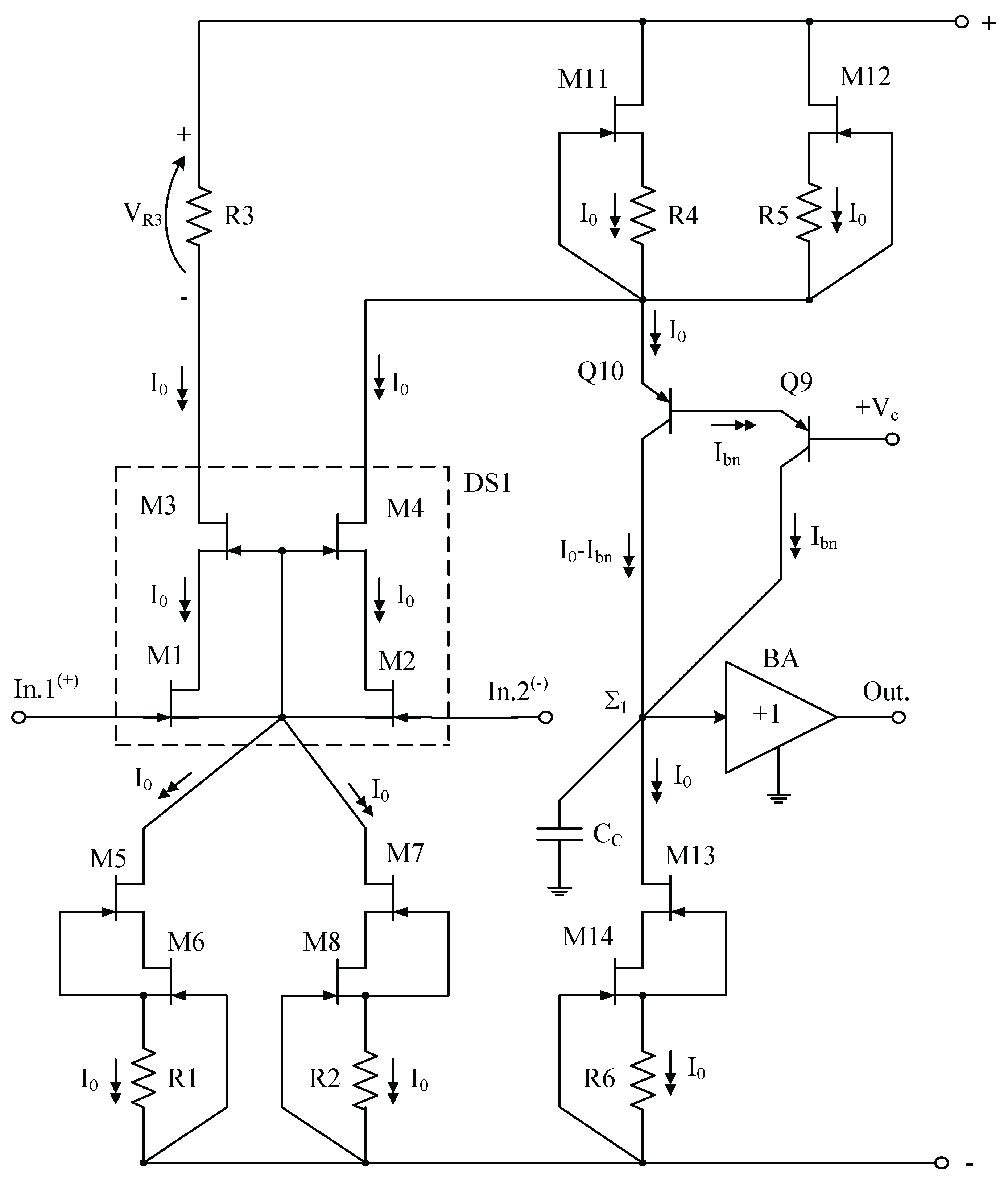

3. The First Practical Circuit of a GaAs Op-Amp is Shown in Figure 5

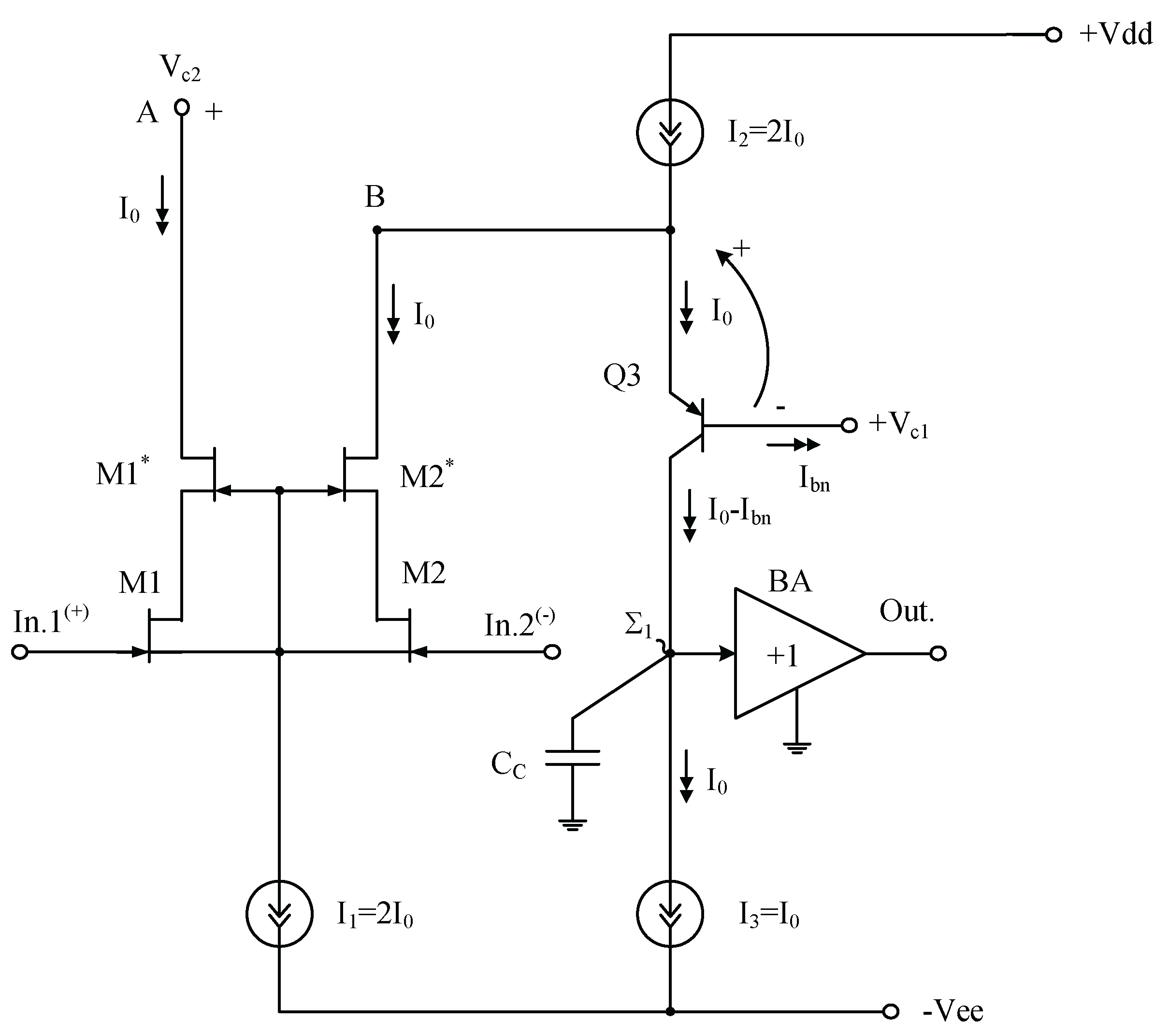

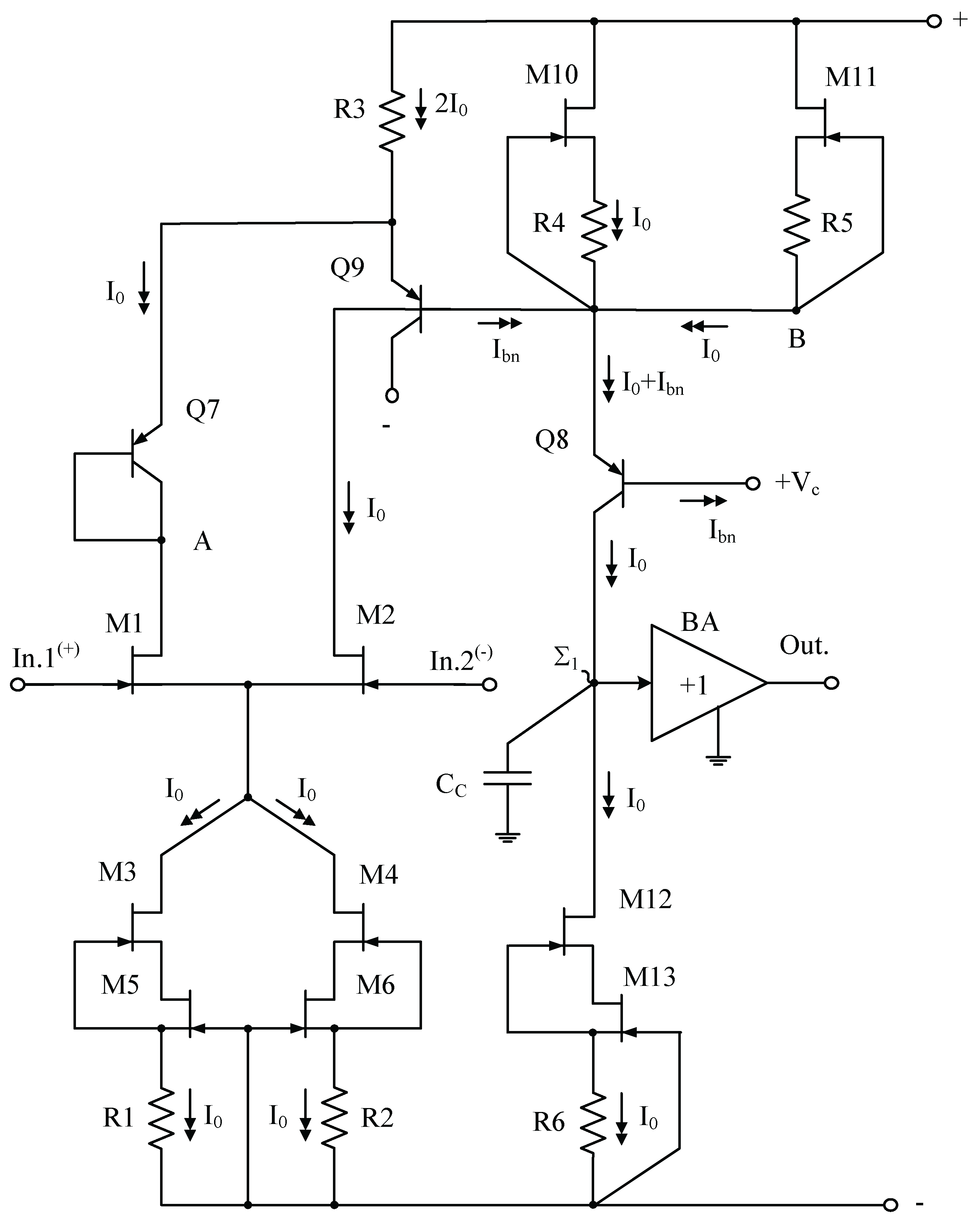

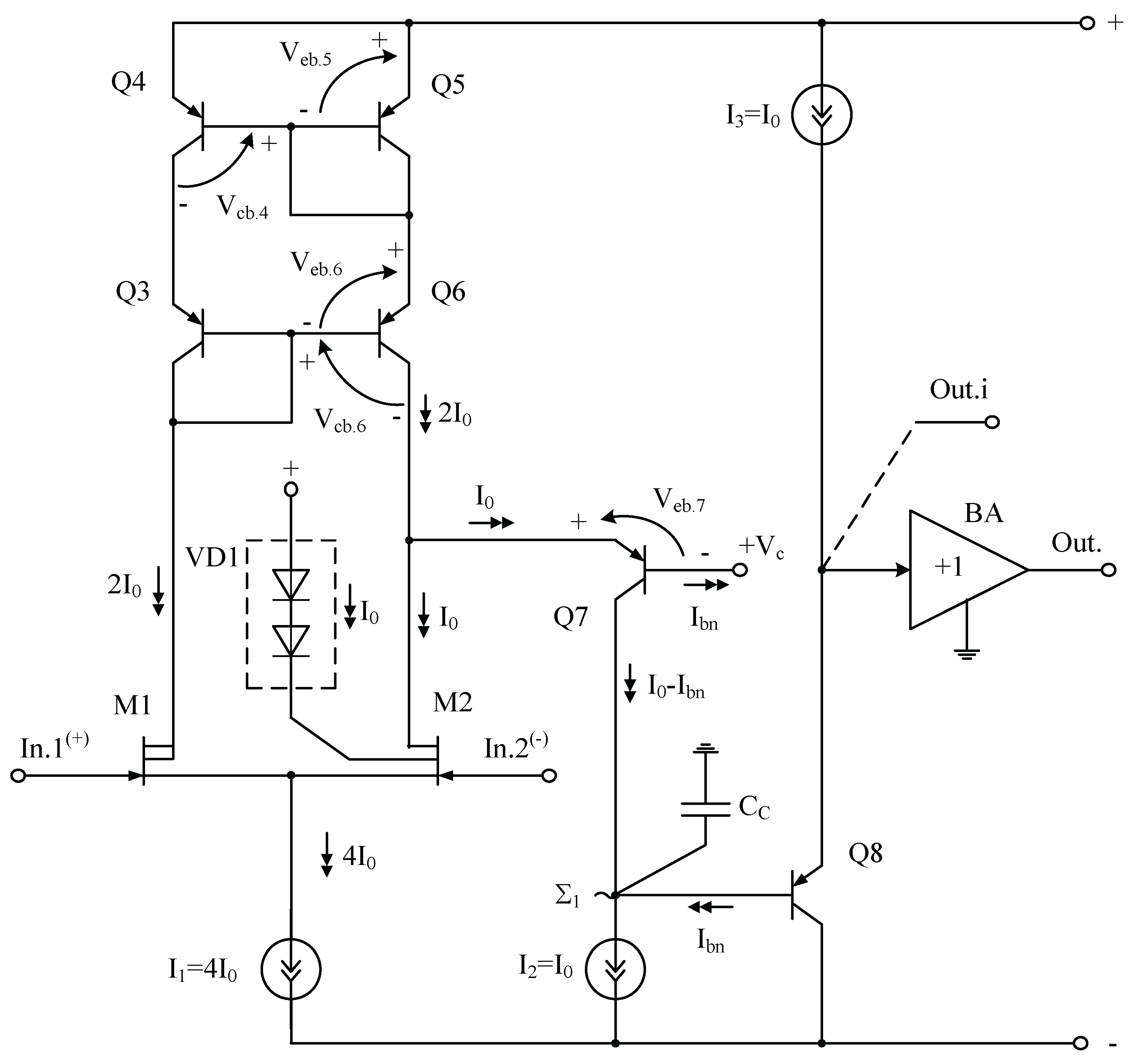

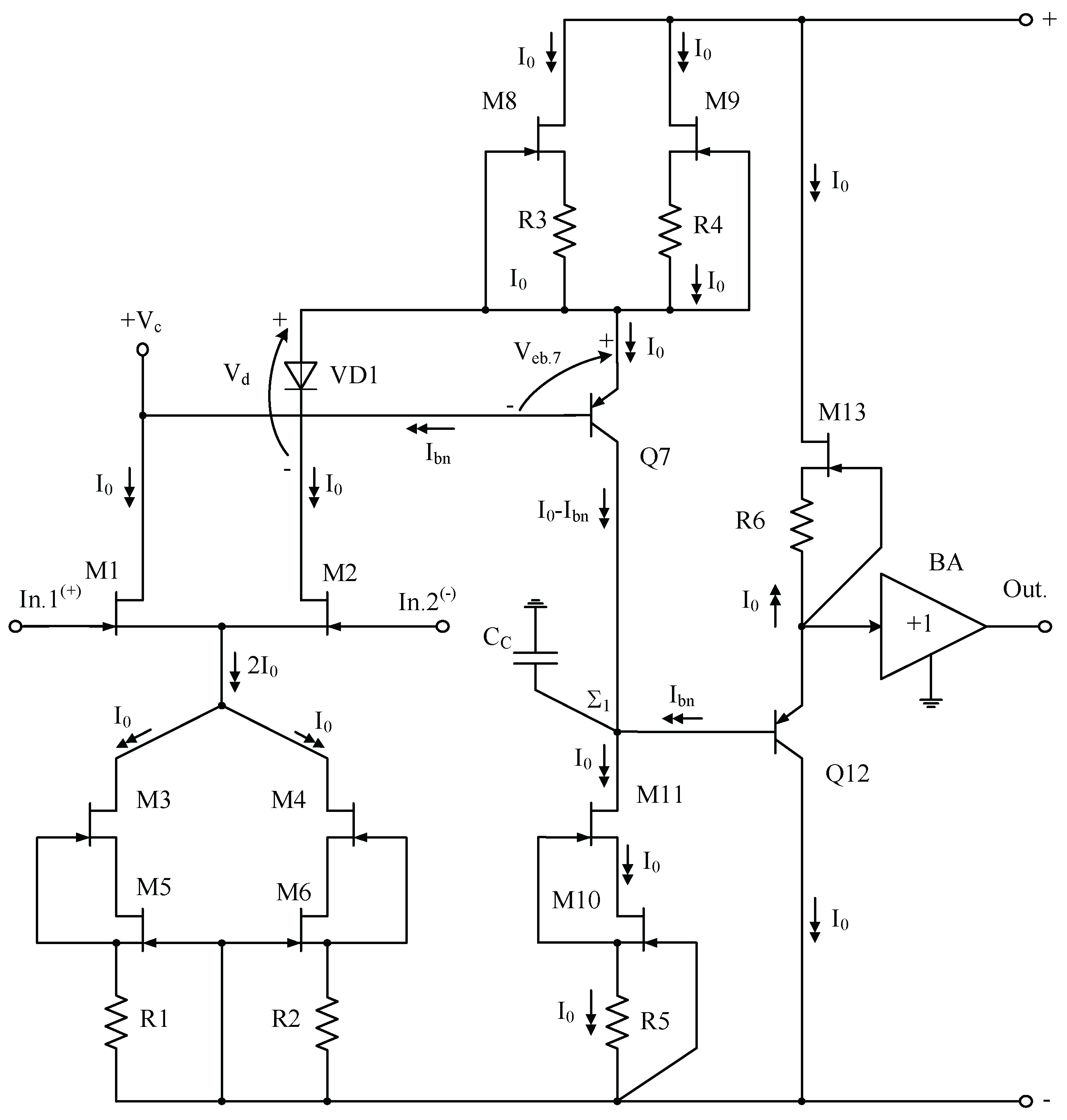

4. The Second Practical Scheme of GaAs op-amp is Shown in Figure 6

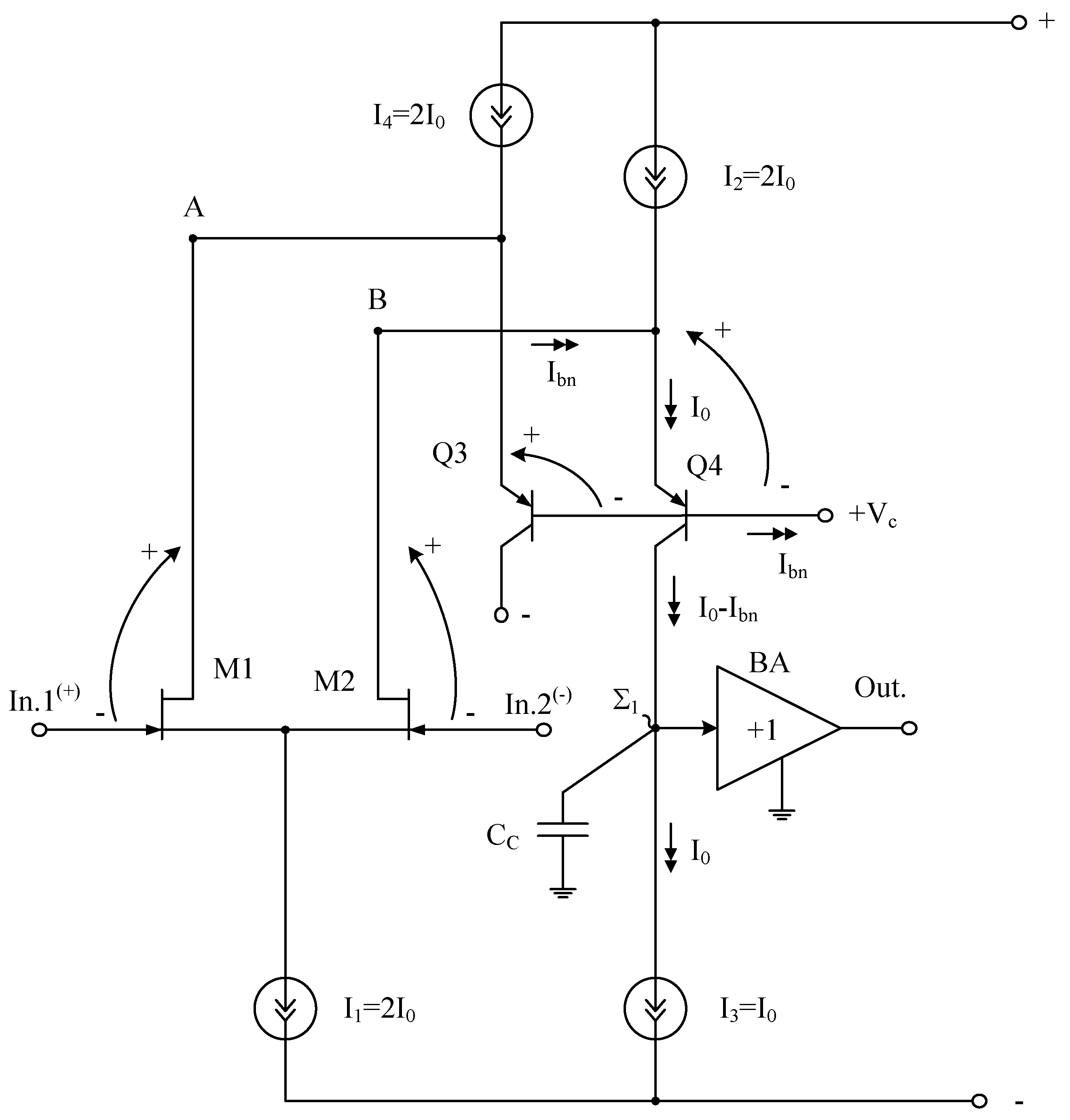

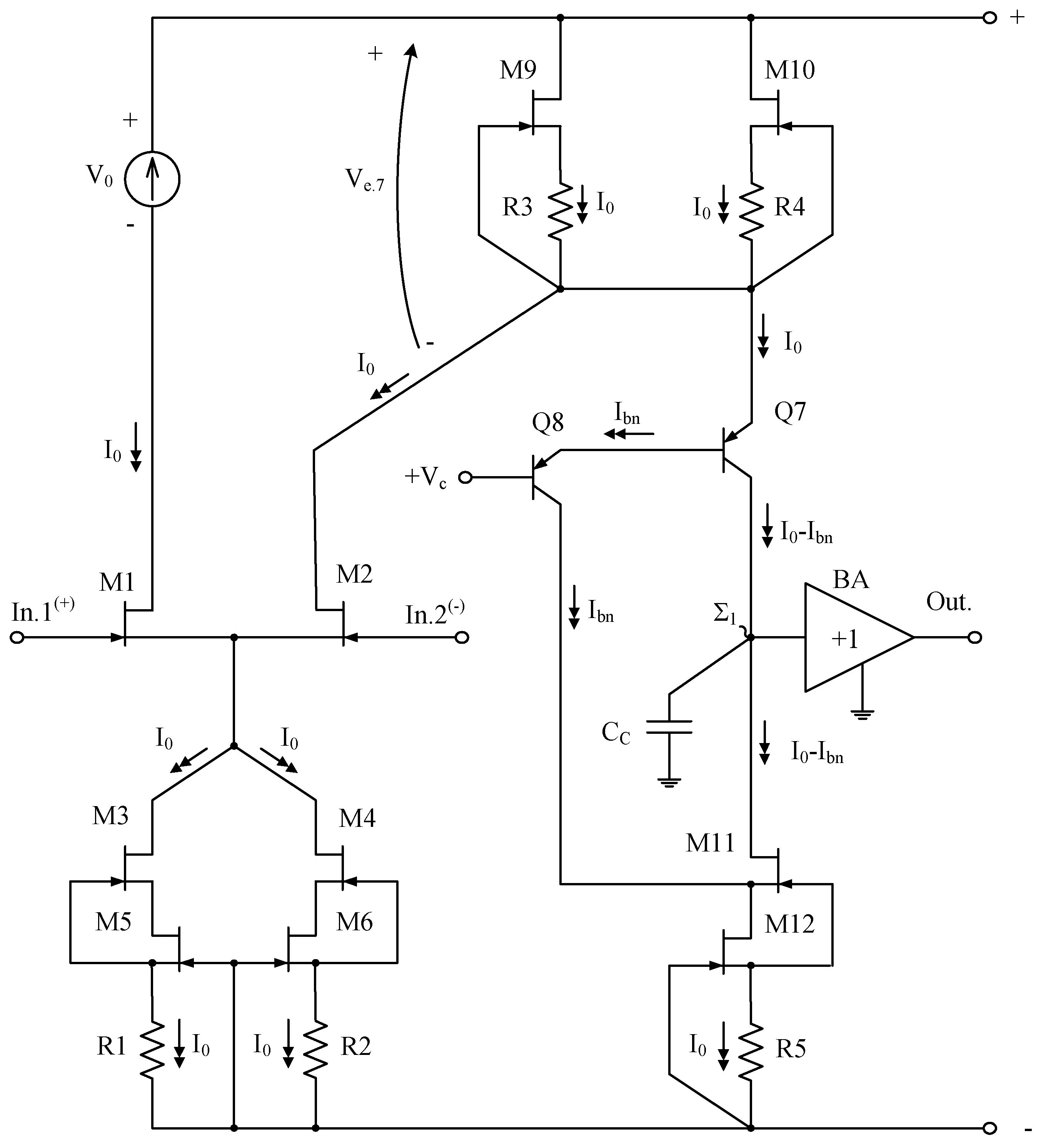

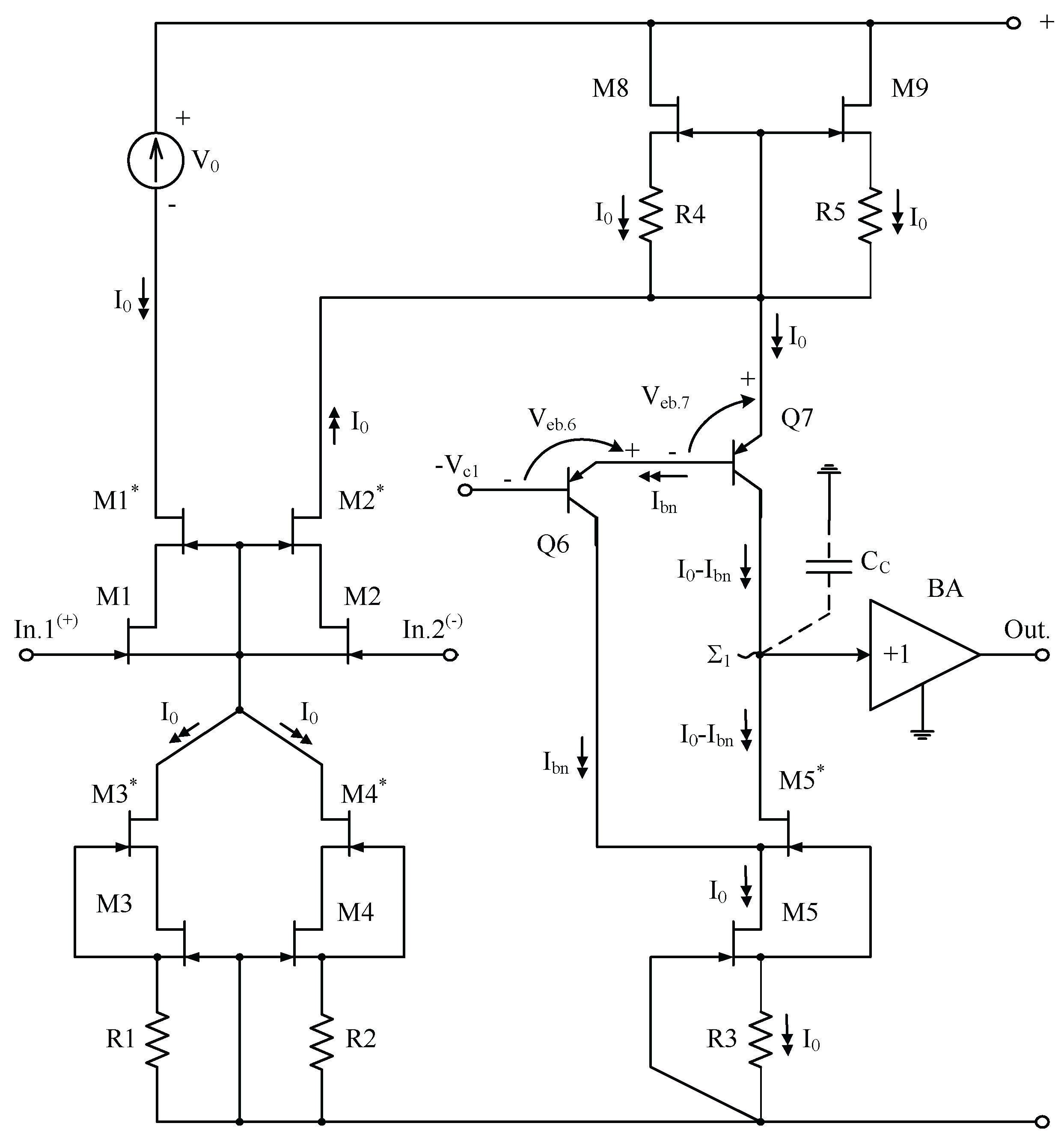

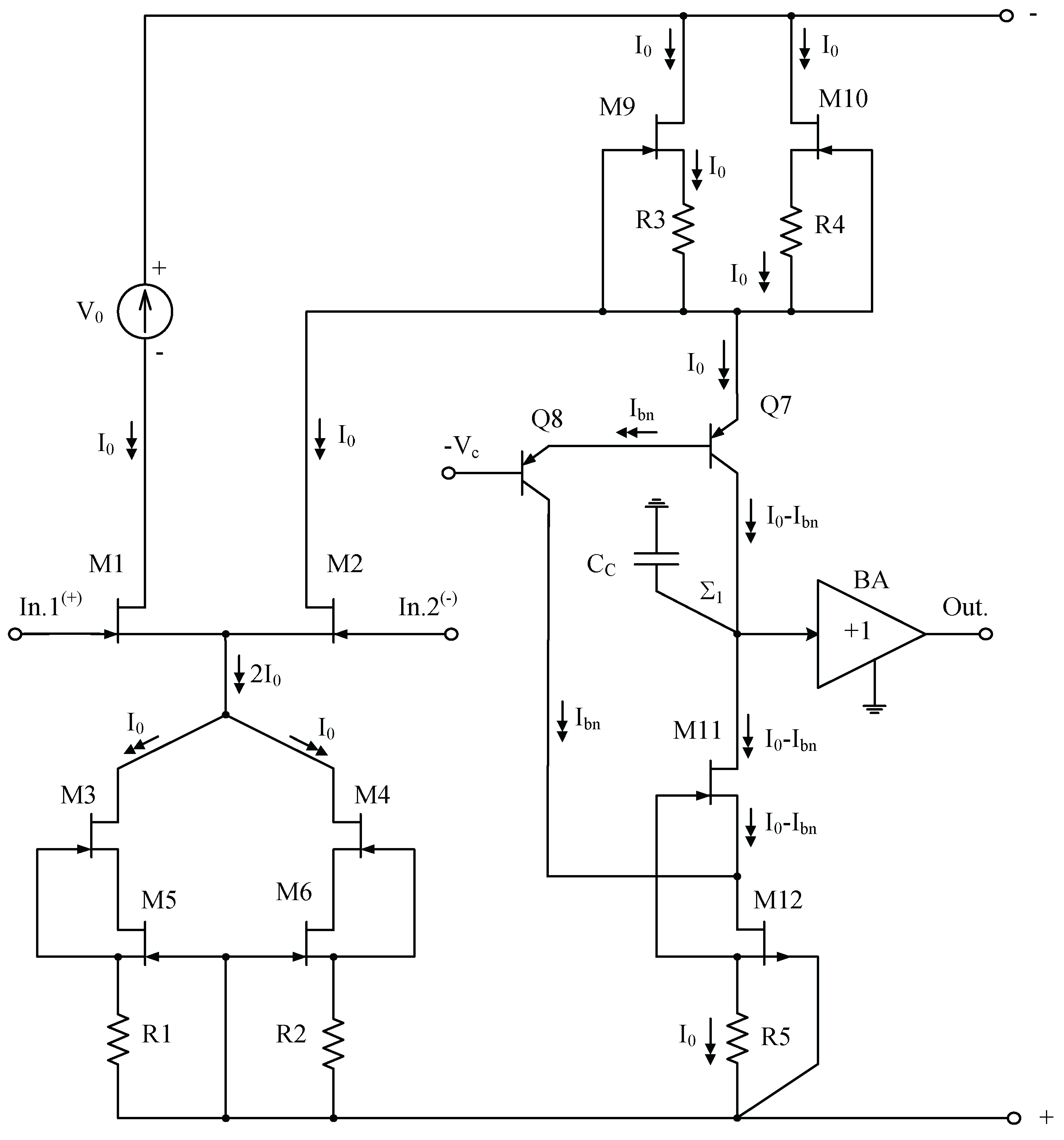

5. The Third Practical Scheme of GaAs Op-Amp is Shown in Figure 7

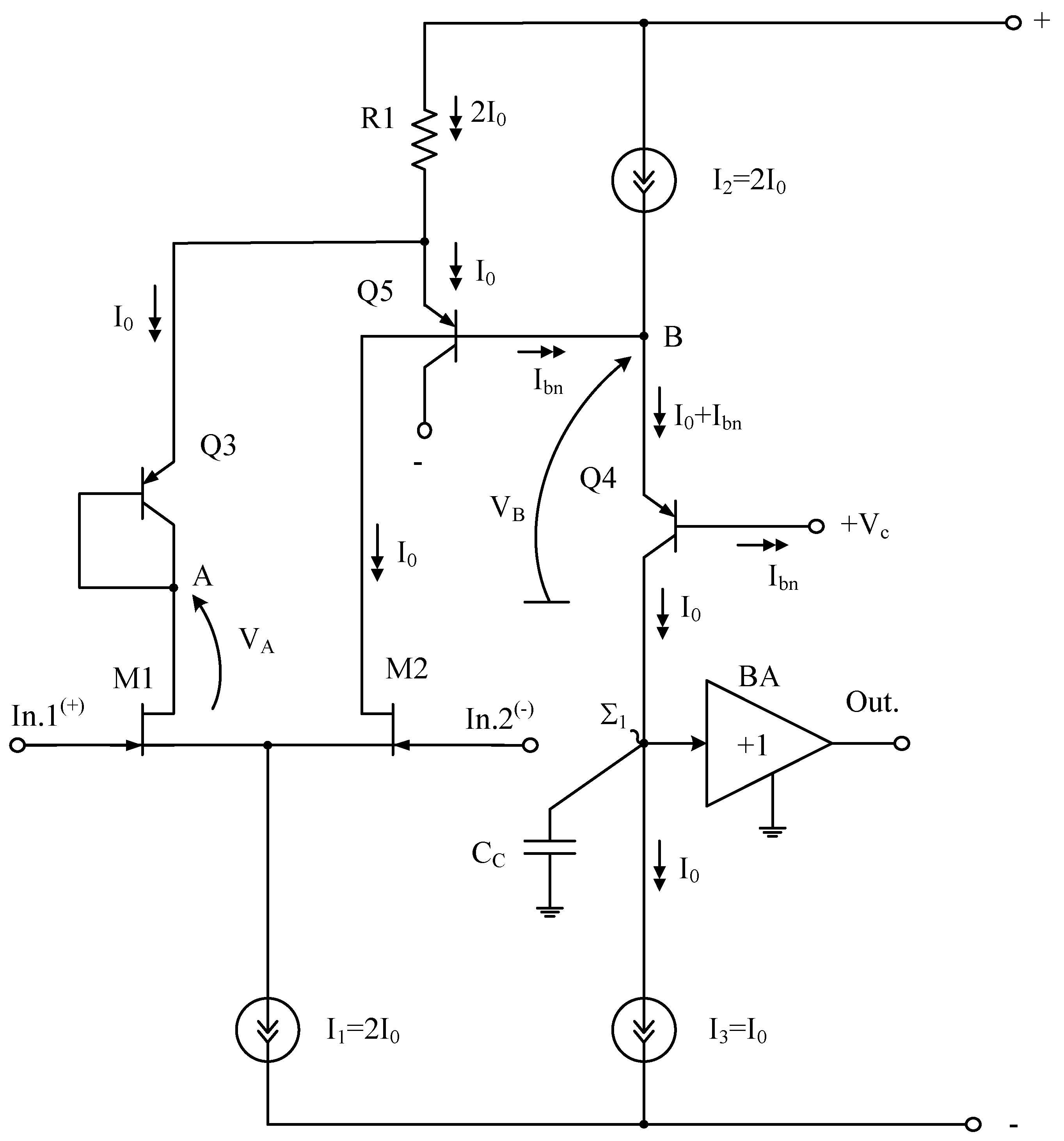

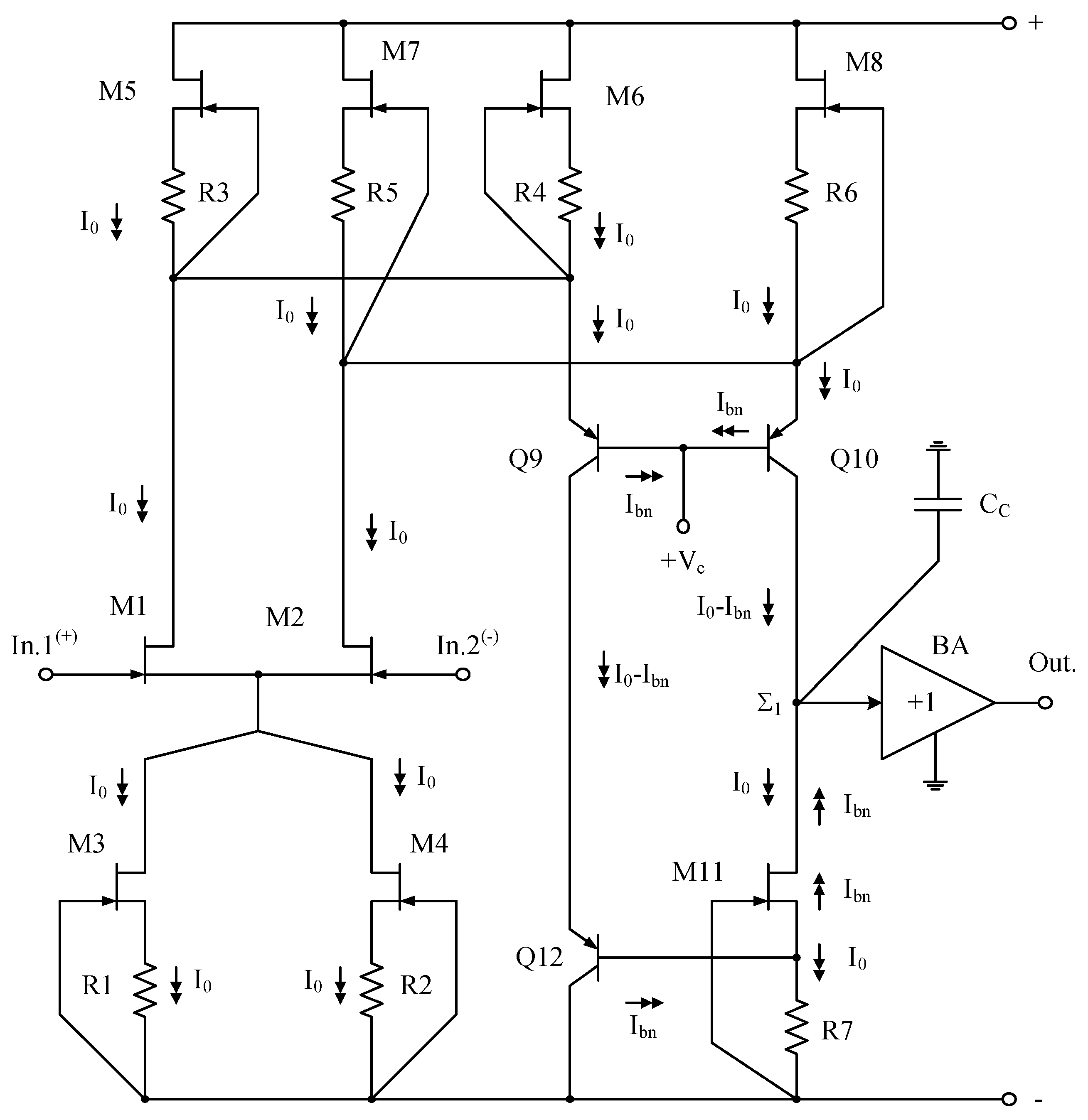

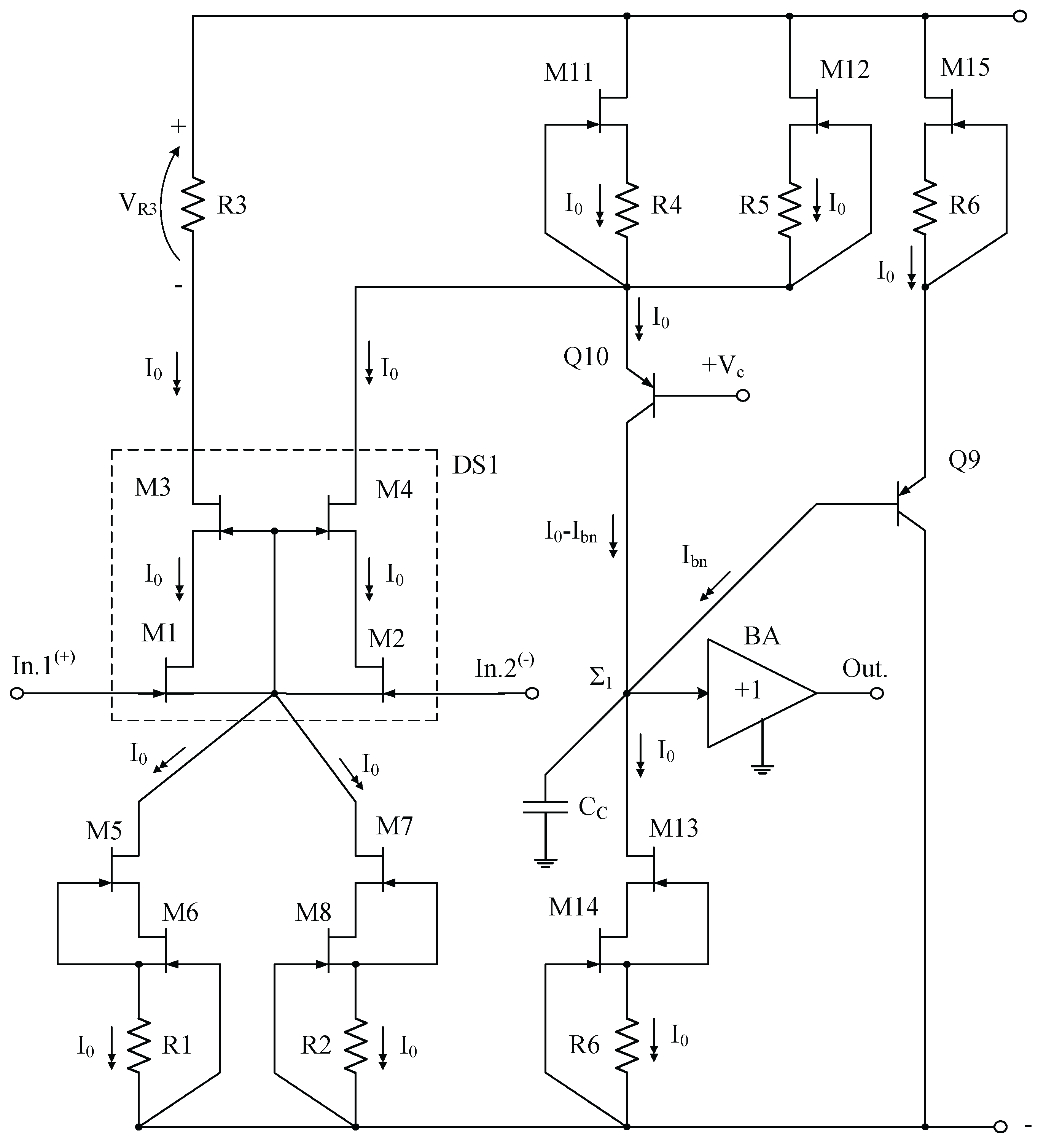

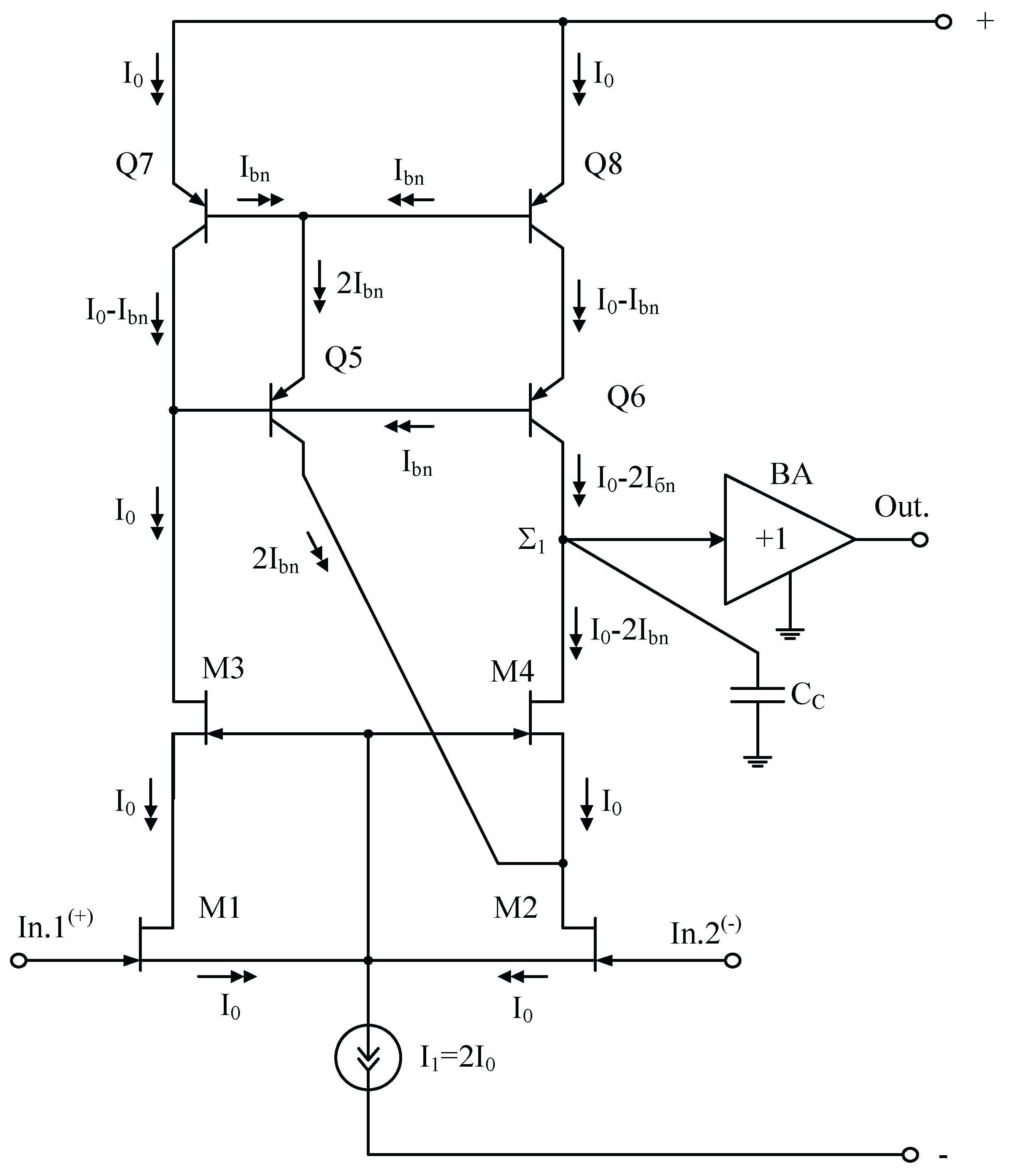

6. The Fourth Practical Scheme of GaAs op-amp is Shown in Figure 8

7. The Fifth Practical Scheme of GaAs Op-Amp is Shown in Figure 9

8. The Sixth Practical Scheme of GaAs Op-Amp is Shown in Figure 10

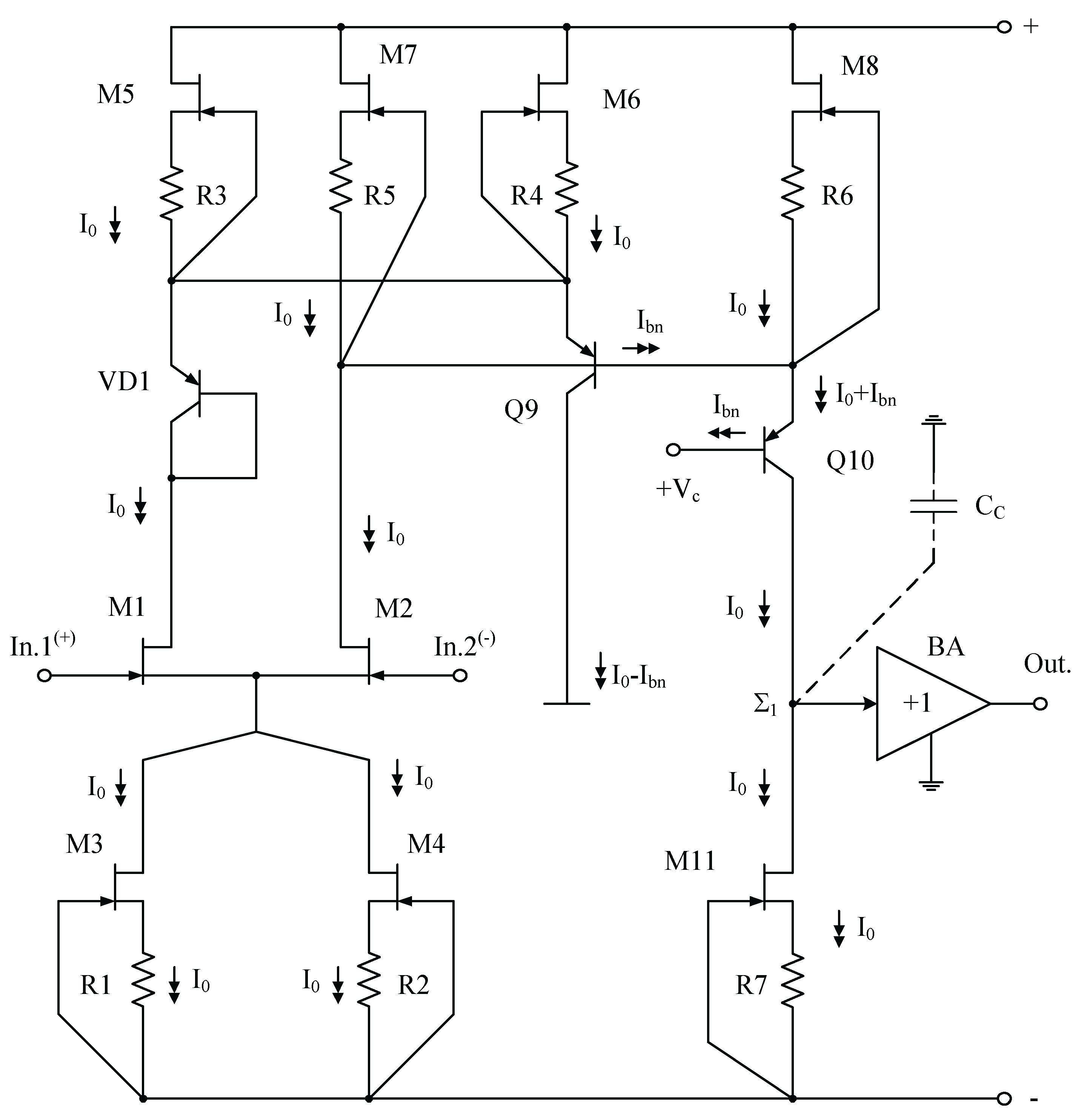

9. The Seventh Practical Scheme of GaAs is Shown in Figure 11

10. The Eighth Practical Scheme of GaAs Op-Amp is Shown in Figure 12

11. The Ninth Practical Scheme of GaAs Op-Amp is Shown in Figure 13

12. The Tenth Practical Scheme of GaAs Op-Amp is Shown in Figure 14

13. The Eleventh Practical Scheme of GaAs Op-Amp Figure 15

14. The Twelfth Practical Scheme of GaAs Op-Amp is Shown in Figure 16

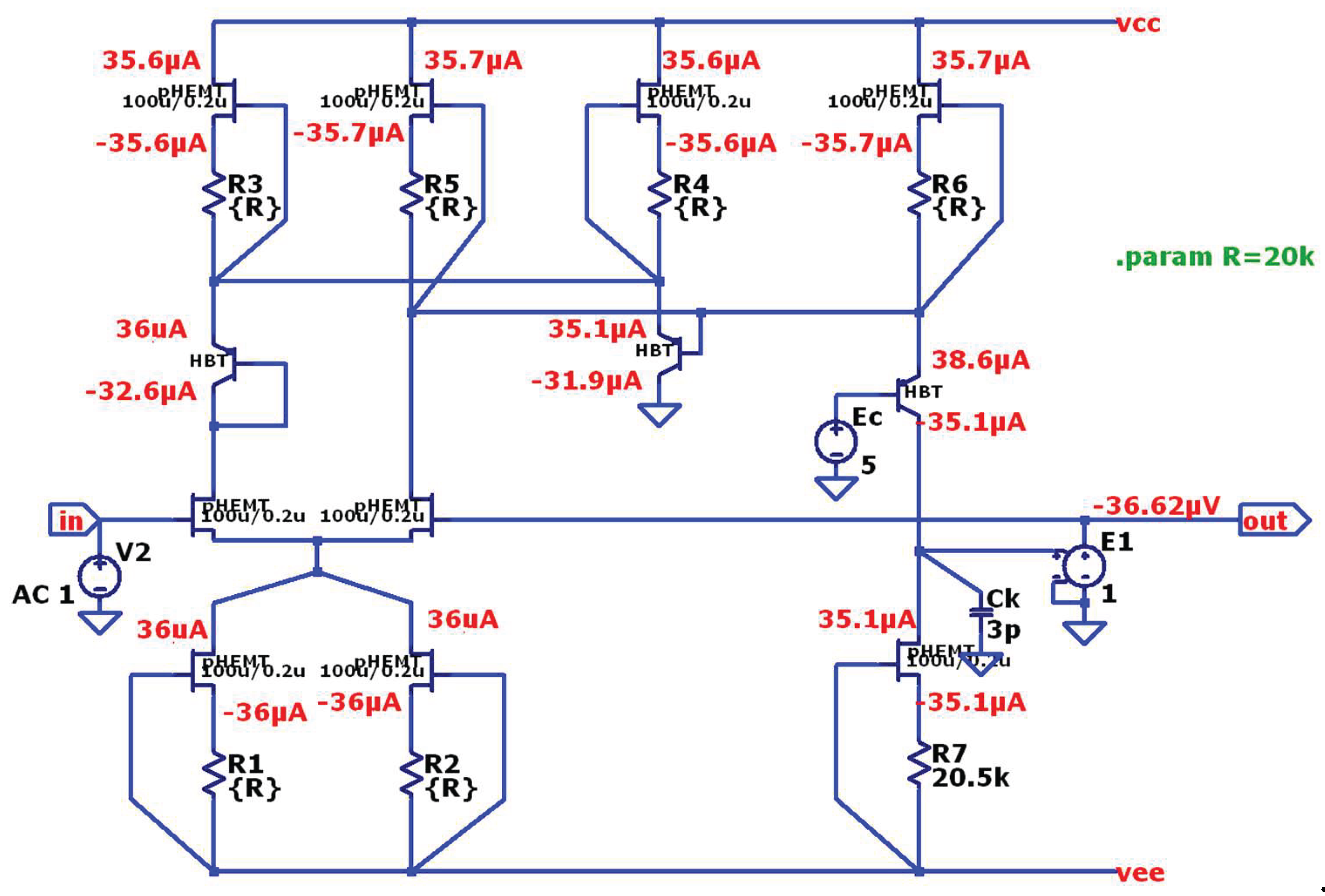

15. An Example of a GaAs Op-Amp Computer Simulation Based on an "Folded" Cascade

16. Conclusion

References

- Riazantsev, V.; et al. High-Speed Operational Amplifiers Based on GaAs Technology for RF Applications. IEEE Transactions on Microwave Theory and Techniques, 2023. [Google Scholar]

- Panda, S. K.; et al. Low-Noise GaAs-Based Operational Amplifier Design for Space Applications. J. Electron. Mater. 2023, vol. 52(no. 5). [Google Scholar]

- Alim, M. A.; et al. Performance Analysis of GaAs vs. Silicon in Operational Amplifier Design. Int. J. Electron. Commun. Eng. 2022, vol. 15(no. 2). [Google Scholar]

- Razavi. “Design of Analog CMOS Integrated Circuits,” in, 2nd ed.; McGraw-Hill, 2014. [Google Scholar]

- Soltani, et al. High-Speed Operational Amplifier for 5G RF Front-End Circuits. IEEE J. Solid-State Circuits 2020, vol. 55(no. 3), 789–798. [Google Scholar]

- Talegaonkar, M.; et al. Challenges in Designing High-Speed CMOS Op-Amps at Sub-90nm Nodes. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), 2021; pp. 1–4. [Google Scholar]

- Fresina, M. Trends in GaAs HBTs for wireless and RF. 2011 IEEE Bipolar/BiCMOS Circuits and Technology Meeting - BCTM; LOCATION OF CONFERENCE, United StatesDATE OF CONFERENCE; pp. 150–153.

- Zampardi, P.J.; Sun, M.; Cismaru, C.; Li, J. Prospects for a BiCFET III-V HBT Process. 2012 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS); LOCATION OF CONFERENCE, USADATE OF CONFERENCE; pp. 1–3.

- Liu, W.; Hill, D.; Costa, D.; Harris, J. High-performance microwave AlGaAs-InGaAs Pnp HBT with high-DC current gain. IEEE Microw. Guid. Wave Lett. 1992, 2, 331–333. [Google Scholar] [CrossRef] [PubMed]

- Peatman, W.; et al. InGaP-Plus™: advanced GaAs BiFET technology and applications. CS MANTECH Conference, 2007; pp. 243–246. [Google Scholar]

- Dvornikov, O. V.; Pavlyuchik, A. A.; Prokopenko, N. N.; Chekhovsky, V. A. “Unified circuit design solutions for analog gallium arsenide chips,” in Izvestiya vuzov. Electronics (in Russian). 2022, Vol. 27(No. 4), 475–488. [Google Scholar] [CrossRef]

- Morris, F. J.; et al. Integrated circuit composed of group III-V compound field effect and bipolar semiconductors. US Patent 5068756, 26 Nov 1991. [Google Scholar]

- Chang, Mau-Chung F.; et al. Planar HBT-FET Device. US Patent 5250826, 5 Oct 1993. [Google Scholar]

- Yang, J.; Morris, F.; Plumton, D.; Jeffrey, E. GaAs BIJFET technology for linear circuits. 11th Annual Gallium Arsenide Integrated Circuit (GaAs IC) Symposium, LOCATION OF CONFERENCE, United StatesDATE OF CONFERENCE.

- Plumton, L.; et al. Method to integrate HBTs and FETs. US Patent 5077231, 31 Dec 1991. [Google Scholar]

- Dvornikov, O.; Pavluchik, A.; Prokopenko, N.; Tchekhovski, V.; Kunts, A.; Chumakov, V.; Mnipi. Probl. Adv. Micro-Nanoelectron. Syst. Dev. 2021. [CrossRef]

- Borkar; Shekhar, Y.; et al. Transistor group mismatch detection and reduction. in Patent US 6272666, 7 Aug 2001. [Google Scholar]

- Hart; Michael, L.; et al. Method and apparatus for compensating for process variations. in Patent US 7453311, 18 Nov 2008. [Google Scholar]

- Horowitz, P.; Hill, W. “The Art of Electronics,” in Third Edition; Cambridge University Press, 2015; p. 1225. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2026 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license.