Submitted:

08 April 2026

Posted:

10 April 2026

You are already at the latest version

Abstract

Keywords:

1. Introduction

2. Materials and Methods

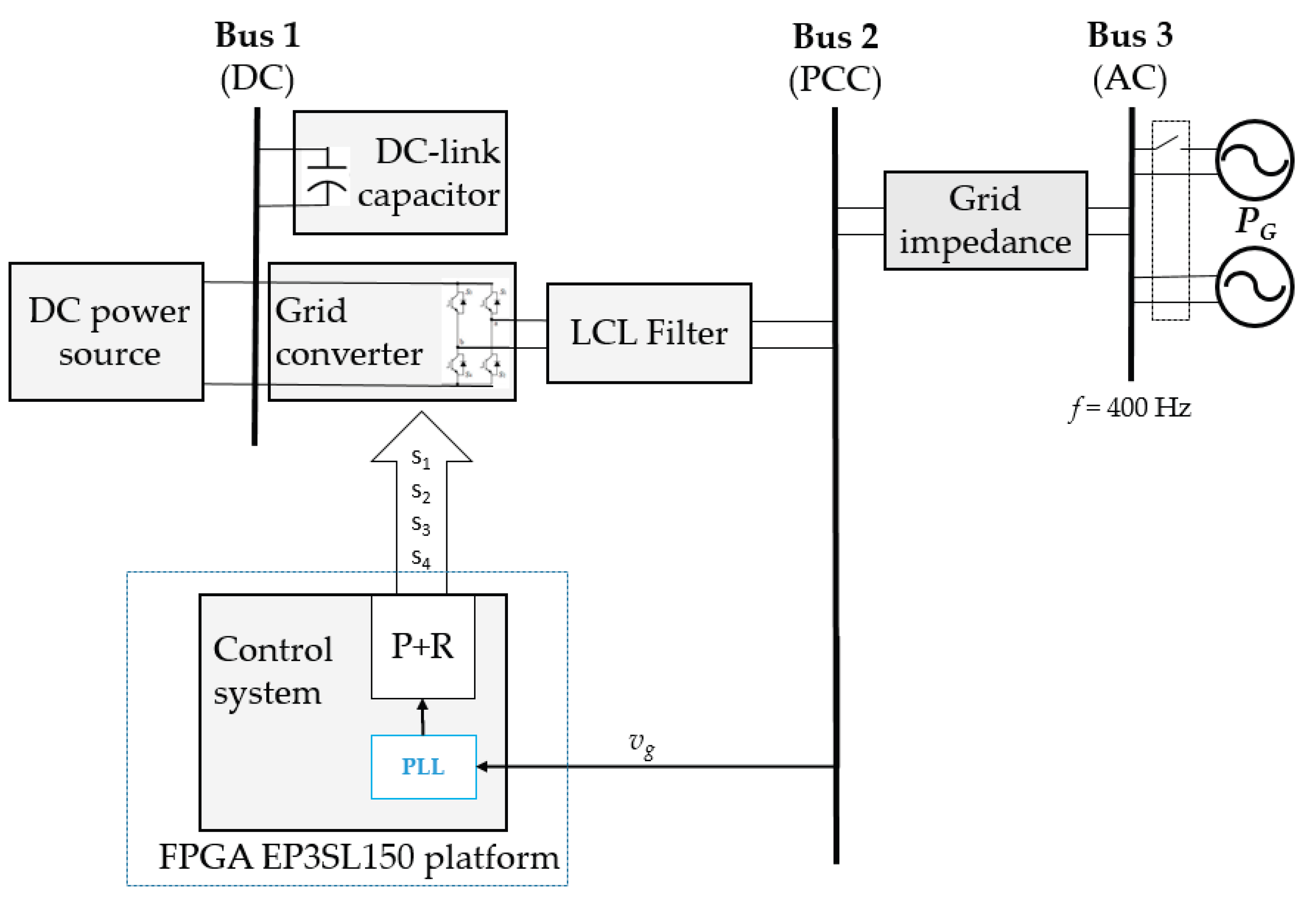

2.1. System Overview

2.2. Onboard 400 Hz Power System Characteristics

2.3. Adaptive Power Control Structure

2.4. Role of the Adaptive PLL in the Control Loop

2.5. Adaptive Characteristics of the Control Loop

- Unitary rotation which preserves magnitude .

- Phase error encoding with small deviations of θ[n] from the true phase lead to q[n] ≈ A[n]·(θtrue[n]—θ[n]).

- Noise attenuation: harmonics and high-frequency noise project onto both d[n] and q[n]; subsequent filtering isolates the fundamental.

- Aliasing: fs must satisfy the Nyquist criterion for the highest frequency component, including harmonics.

- Integrator resolution: θ[n+1] = θ[n] + ω[n]·Ts requires fixed-point or floating-point representation; saturation or modulo arithmetic may be necessary.

- Delay: each block introduces one-sample delay; cumulative delay affects convergence time and must be considered in kω selection.

2.6. Adaptive Frequency Estimation

- Sampling and Quantization: q[n] must be computed with sufficient resolution; insufficient word length can introduce limit cycles and fixed-point implementation typically must uses 16–24 bits, with scaling to maintain numerical stability.

- Integrator Design: saturation or modulo arithmetic is essential to prevent overflow during large frequency excursions.

- Time-Delay Effects: each block introduces a one-sample delay; careful selection of kω and kff compensates for this.

- Fixed-point scaling —kω, kff, and Ts must be choose to maximize resolution and avoid overflow.

- Pipeline structure — d–q transformation, q[n] computation, Δω[n] update, and ω[n+1] integration can be parallelized in FPGA.

- Lookup tables for sine/cosine — minimizes computational cost for θ[n] updates.

- Latency minimization — critical for high-frequency signals (>10 kHz), can be achieved by fully combinatorial logic for d–q transformation.

2.7. Phase Tracking

2.8. Amplitude Estimation

2.9. Stability Considerations

2.10. Linearization Around Equilibrium

2.11. Stability Criterion

3. Implementation on FPGA

- Orthogonal signal generation

- Park transformation

- Phase detector

- Adaptive frequency estimation block

- Phase accumulator

- Amplitude estimator

- Sinusoidal signal reconstruction

- Fixed-point representation: d[n], q[n], A[n], Δω[n], and θ[n] can be represented with 16–24 bits to balance precision and hardware resources.

- Discrete integrators: implemented using accumulators; saturation logic ensures safety.

- Lookup tables for sin/cos: θ[n] to sin/cos conversion is implemented via LUTs, avoiding expensive real-time computations.

- Parallel processing: all blocks can operate concurrently for minimal latency, crucial for 10 kHz sampling rates.

4. Simulation and Experimental Validation

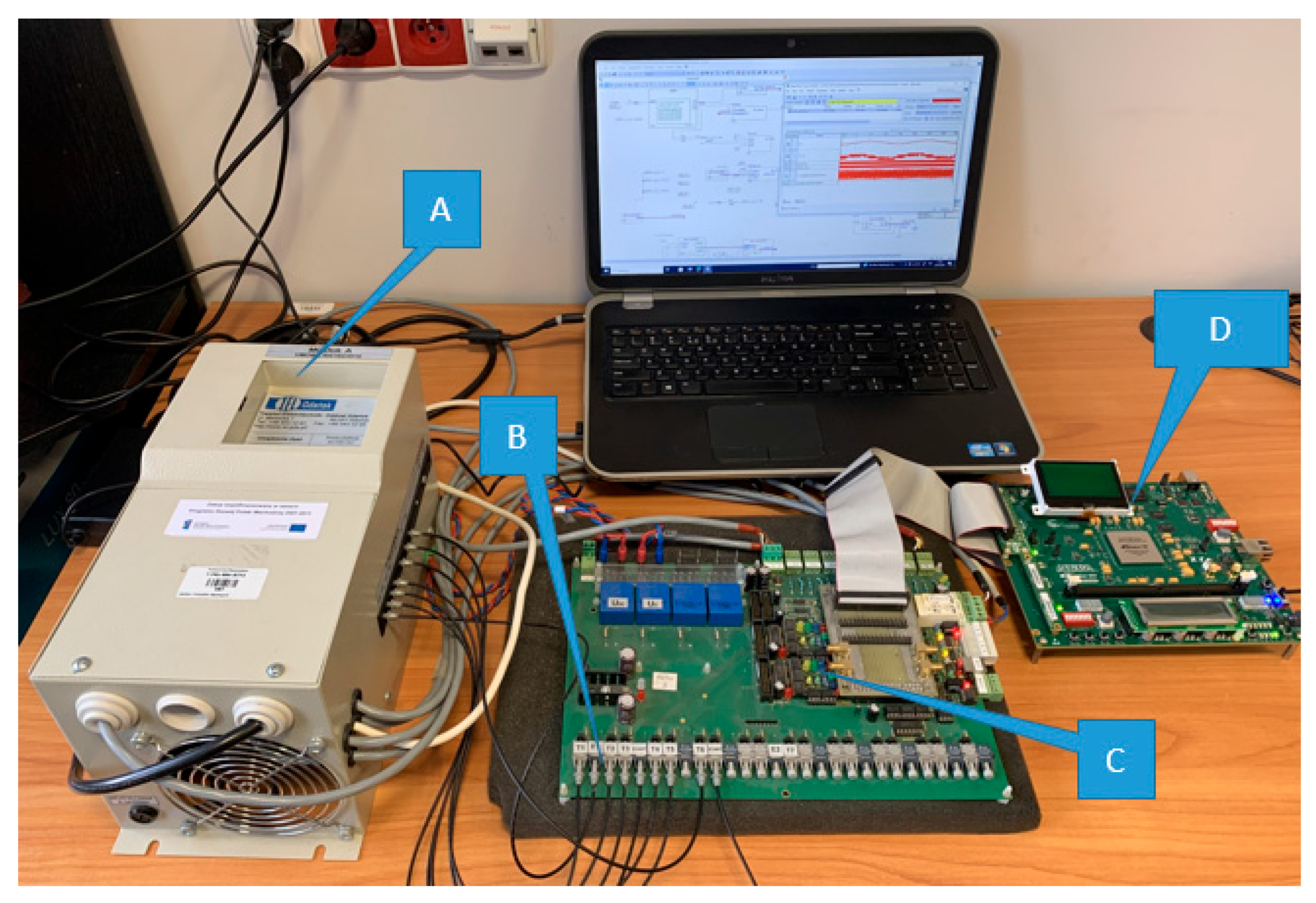

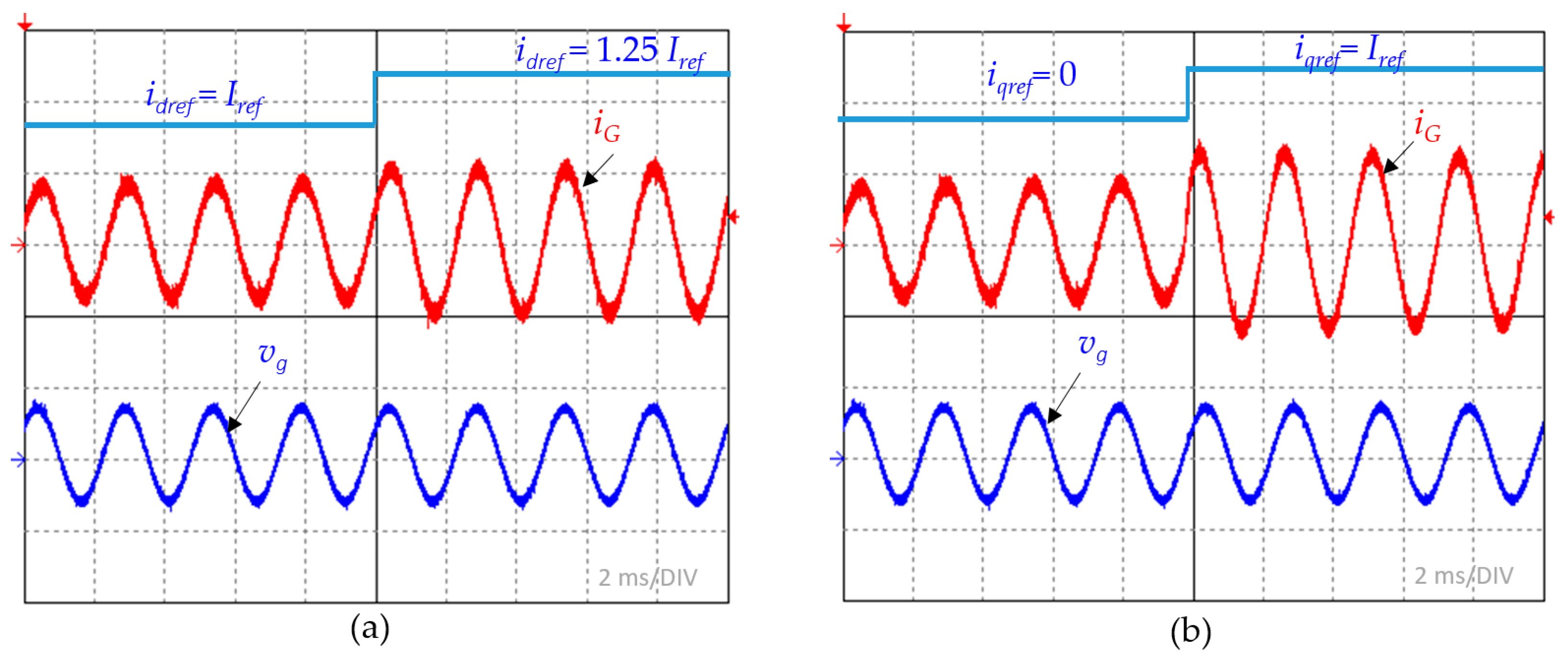

4.1. Test Setup

- frequency step response

- frequency ramp tracking

- harmonic distortion robustness

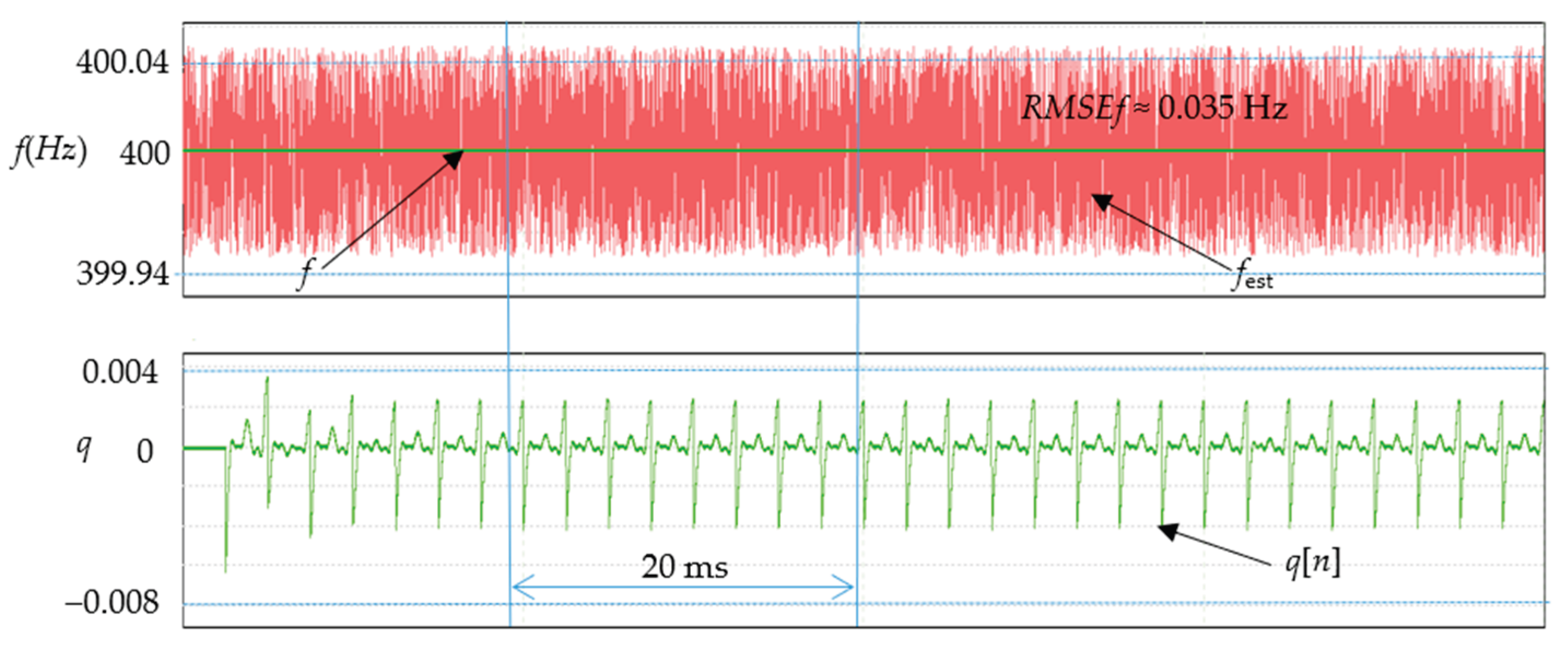

- noise robustness

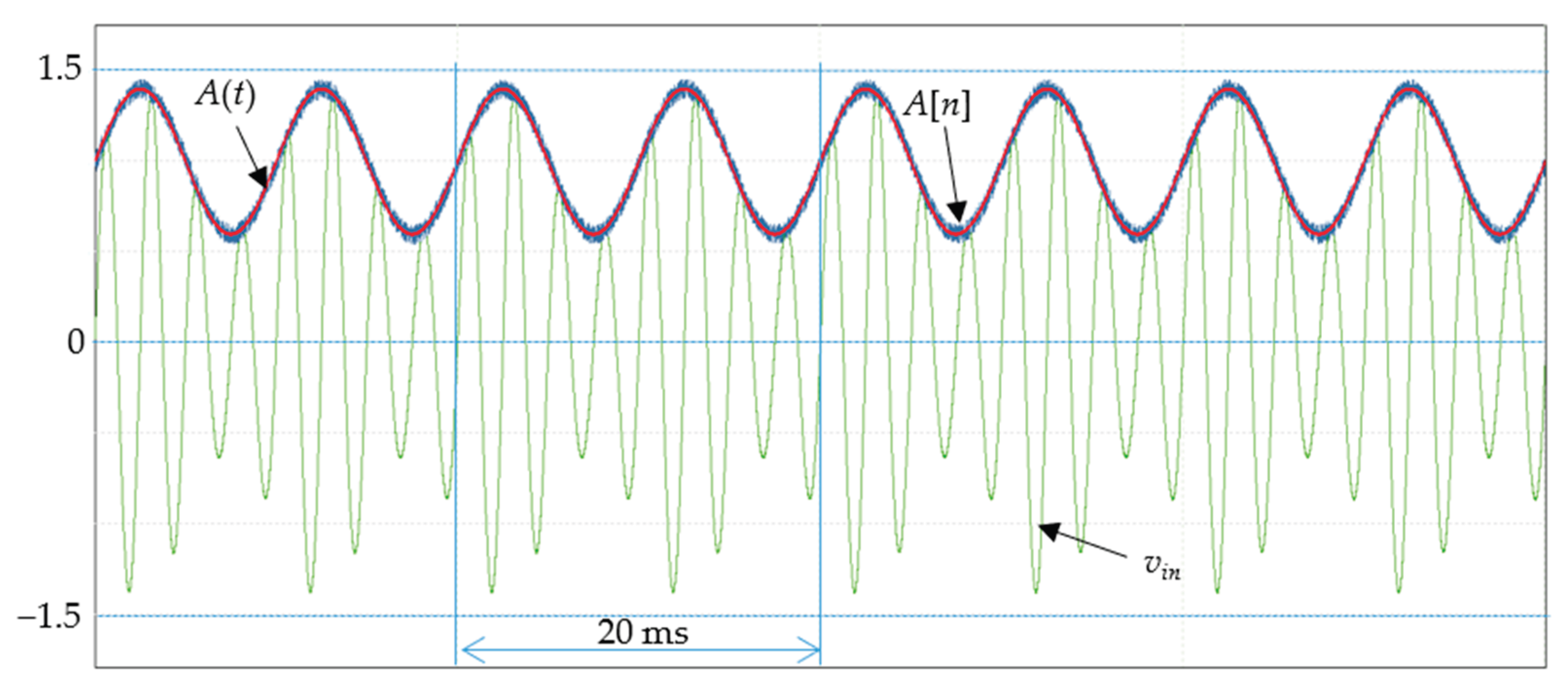

- amplitude variation tracking

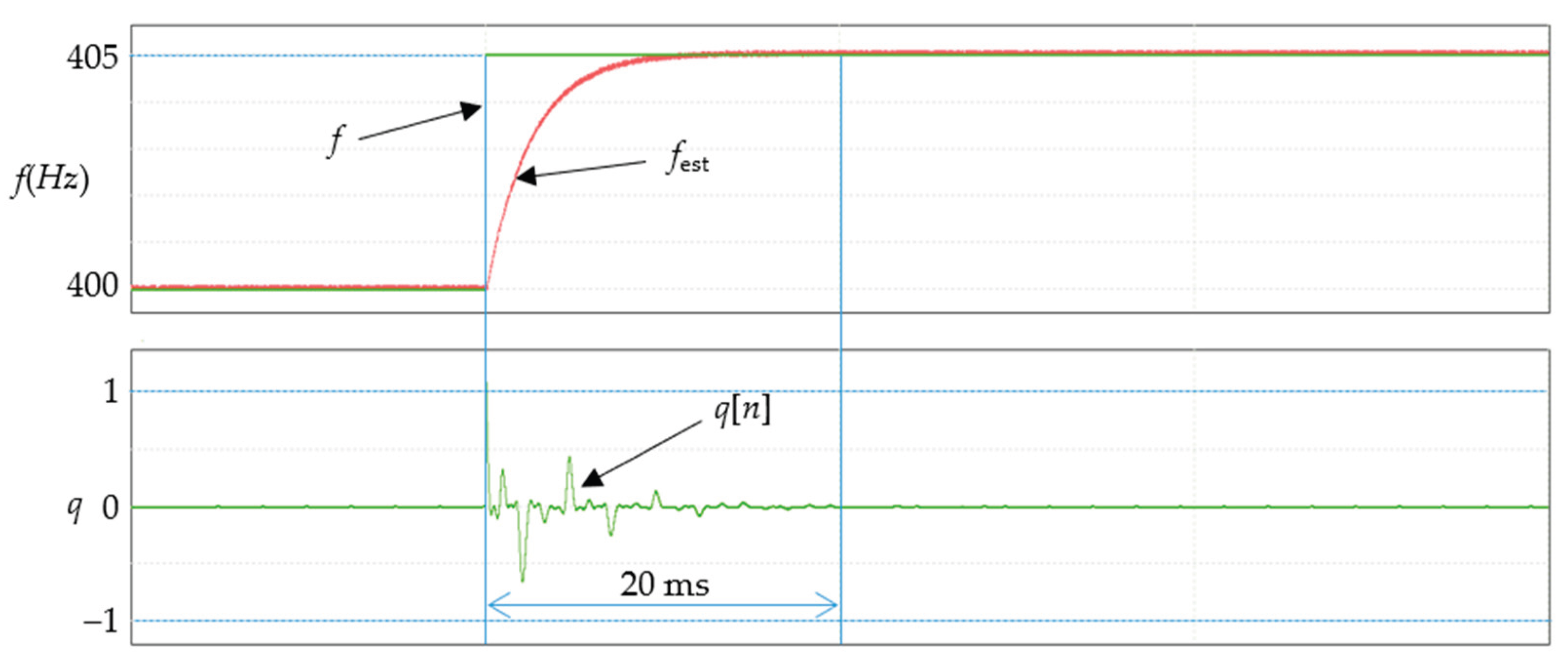

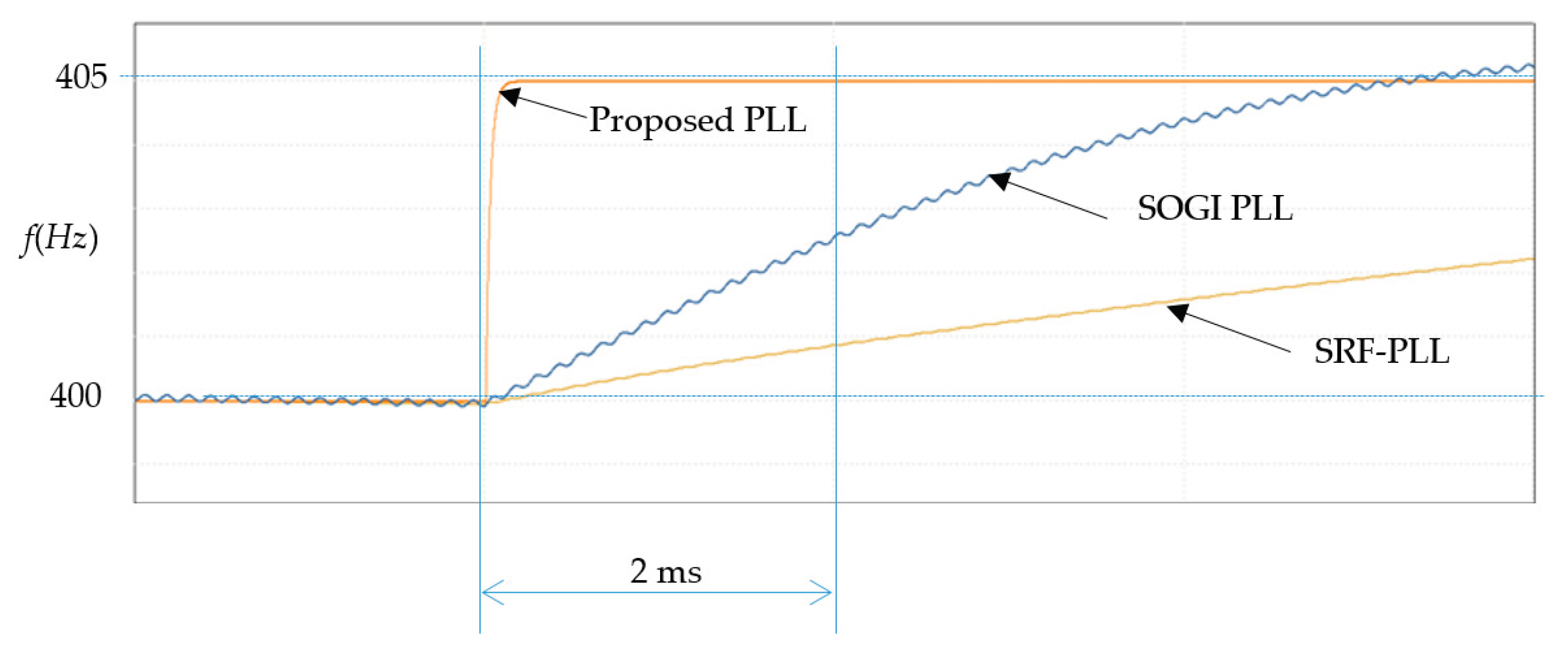

4.2. Frequency Step Response

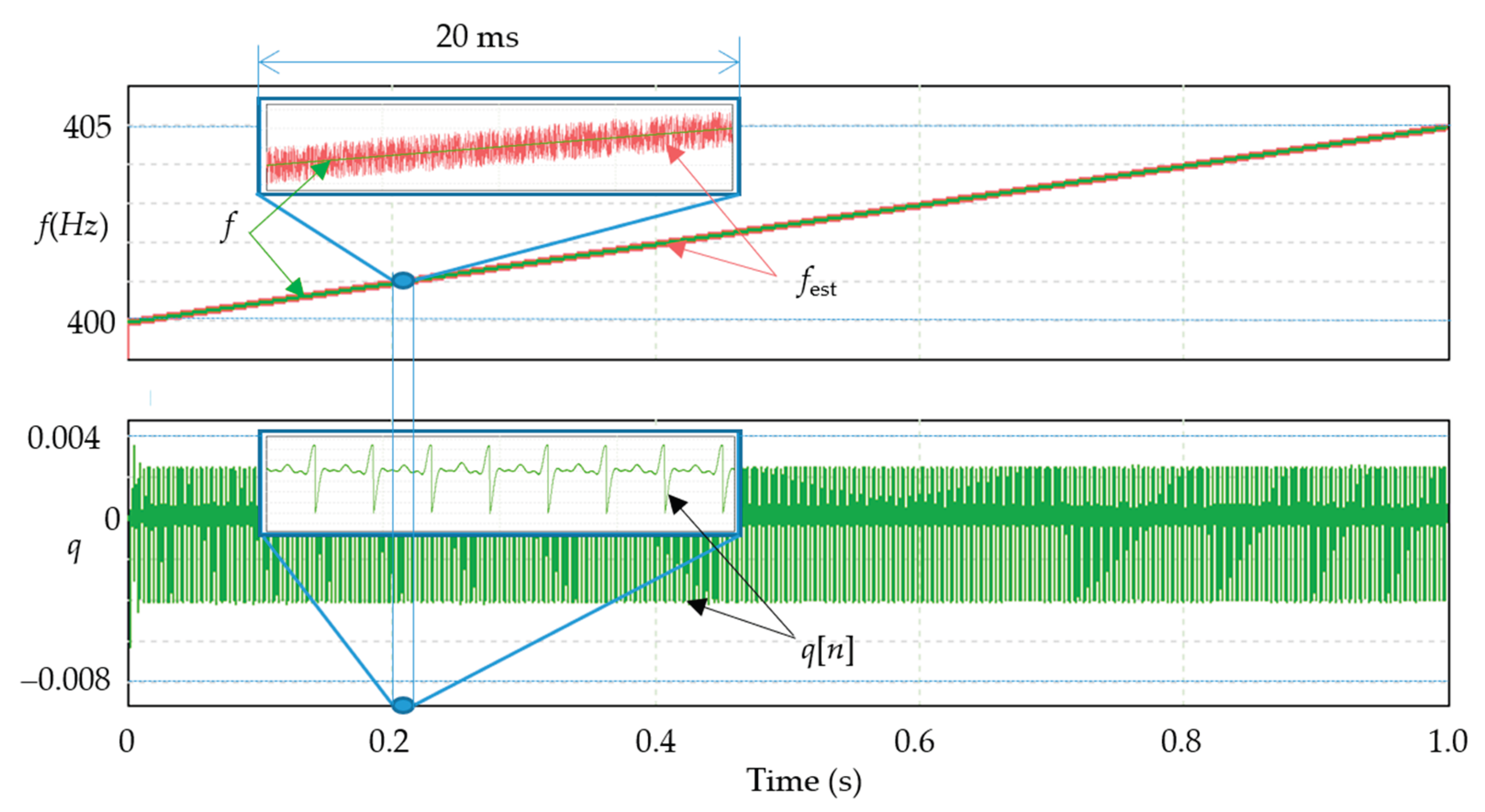

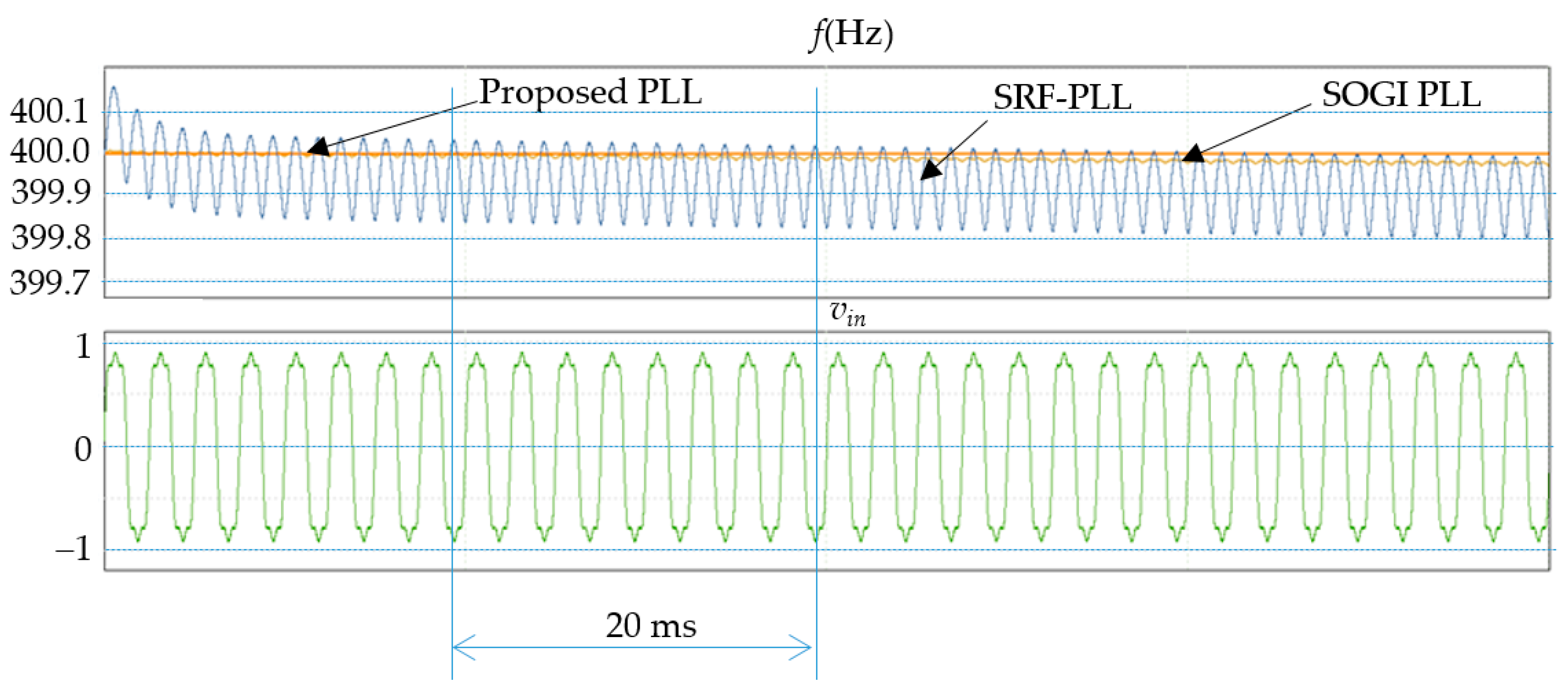

4.3. Frequency Ramp Tracking

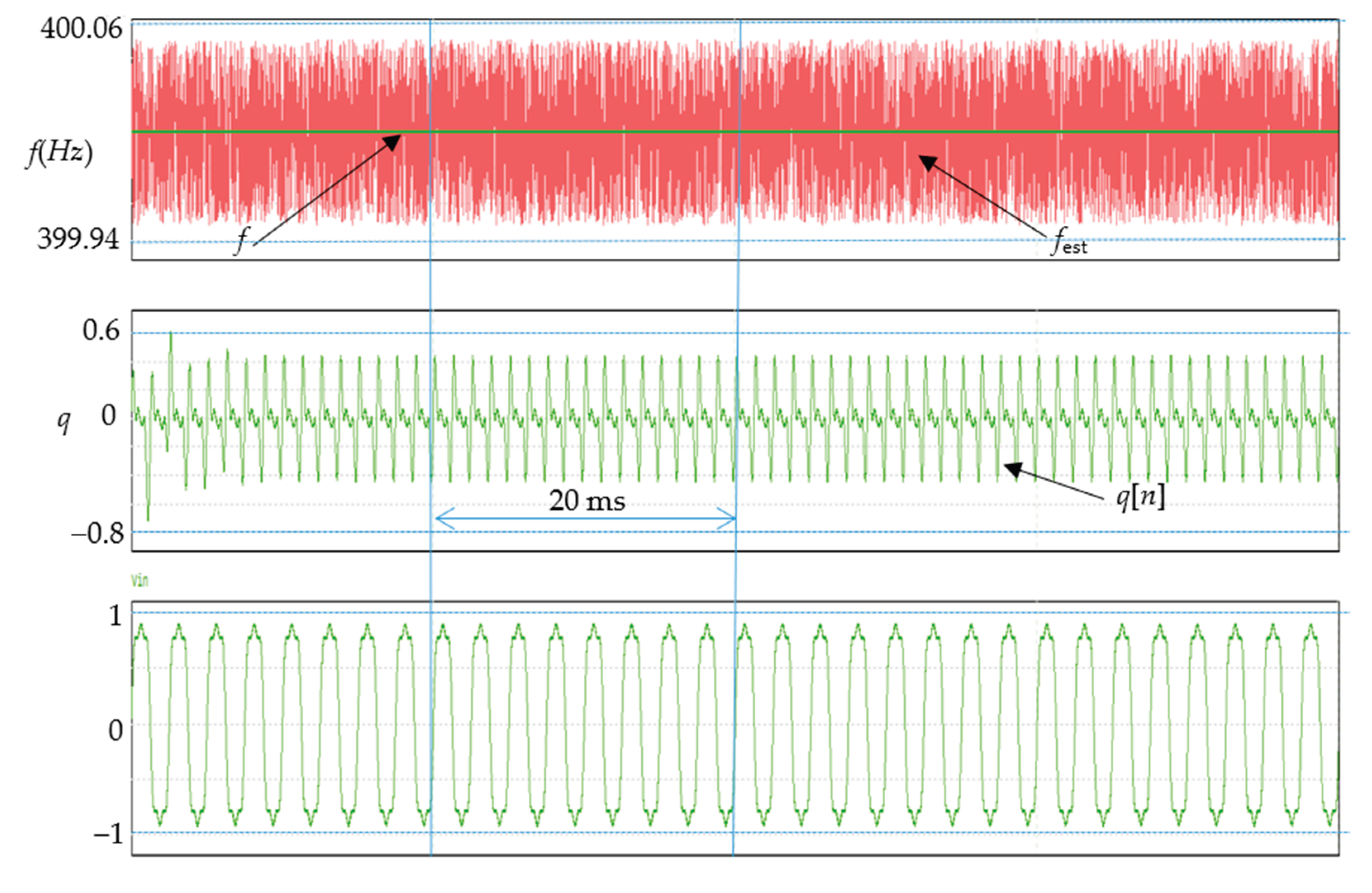

4.4. Harmonic Distortion Test

4.5. Noise Robustness

4.6. Amplitude Variation Tracking

4.7. Discussion

4.8. Comparison with Conventional PLL Methods

- the synchronous reference frame PLL (SRF-PLL)

- the second-order generalized integrator PLL (SOGI-PLL)

| Parameter | Value |

|---|---|

| Sampling frequency | 10 kHz |

| Nominal frequency | 400 Hz |

| Frequency step | 400 to 405 Hz |

| Noise level | 30 dB SNR |

| Harmonic distortion | 20% third harmonic |

- frequency settling time

- maximum overshoot

- steady-state frequency error

- robustness to harmonic distortion.

4.9. Hardware Tests

Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Sarlioglu, B.; Morris, C.T. More Electric Aircraft: Review, Challenges, and Opportunities for Commercial Transport Aircraft. IEEE Trans. Transp. Electrif. 2015, 1, 54–64. [Google Scholar] [CrossRef]

- Millar, K.; Fong, K.; Alzola, R.; Norman, P.; et al. System Wide Reliability Impact of Power Converters in More-Electric Aircraft Applications. SAE Tech. Pap. 2023, 2023-01-0991. [Google Scholar] [CrossRef]

- Martínez-Heredia, J.; et al. Impact of Aircraft Electrification on Onboard Systems and Energy Requirements. arXiv 2026, arXiv:2603.09918. [Google Scholar]

- Emadi, A.; Ehsani, M. Aircraft Power Systems: An Overview. IEEE Trans. Aerosp. Electron. Syst. 2001, 37, 1123–1133. [Google Scholar] [CrossRef]

- Guerrero, J.M.; Vasilakos, A.V.; Blaabjerg, F.; Teodorescu, R. Control of Power Converters in Microgrids: A Review. IEEE Trans. Ind. Electron. 2020, 67, 8383–8398. [Google Scholar]

- Golestan, S.; Guerrero, J.M.; Vasquez, J.C. Three-Phase PLLs for Grid-Connected Power Converters: A Review. IEEE Trans. Power Electron. 2021, 36, 1391–1405. [Google Scholar]

- Rocabert, J.; Luna, A.; Blaabjerg, F.; Rodríguez, P. Control of Power Converters in AC Microgrids: A Review. IEEE Trans. Ind. Electron. 2020, 67, 9071–9082. [Google Scholar] [CrossRef]

- Teodorescu, R.; Liserre, M.; Rodríguez, P. Grid Converters for Photovoltaic and Wind Power Systems, 2nd ed.; Wiley: Hoboken, NJ, USA, 2020. [Google Scholar]

- Guerrero, J.M.; Loh, P.C.; Lee, T.L.; Chandorkar, M. Advanced Control of Power Converters Using Resonant Controllers for AC Signal Tracking. IEEE Trans. Ind. Electron. 2021, 68, 4025–4035. [Google Scholar]

- Golestan, S.; Monfared, M.; Guerrero, J.M.; Vasquez, J.C. A Review of Adaptive Control and Synchronization Methods for Grid-Connected Converters. Energies 2021, 14, 625. [Google Scholar] [CrossRef]

- Chishti, M.A.; Li, Y.W.; Blaabjerg, F. A Review on Resonant Controllers for Grid-Connected Converters: Theory and Applications. Energies 2022, 15, 1345. [Google Scholar] [CrossRef]

- Bouchareb, F.; Gaillard, A.; Varnier, C. Model Predictive Control for Power Electronics: A Review and Perspectives. Energies 2020, 13, 6489. [Google Scholar]

- Rodríguez, J.; Kouro, S.; Wu, B.; Bernet, S.; Young, H.A. State of the Art of Finite Control Set Model Predictive Control in Power Electronics. IEEE Trans. Ind. Inform. 2021, 17, 1–10. [Google Scholar] [CrossRef]

- Maksimović, D.; Erickson, R.W. Digital Control of Power Electronics Converters. IEEE Trans. Power Electron. 2020, 35, 1–15. [Google Scholar]

- Liu, Y.; Wang, X.; Loh, P.C. Advanced Control Strategies for Grid-Connected Converters: A Review on Synchronization and Adaptive Techniques. IEEE Access 2022, 10, 1–18. [Google Scholar]

- Sun, J.; Freitas, W.; Miao, Z. Power System Stability and Control under High-Frequency Conditions in Electrified Transportation Systems. IEEE Trans. Transp. Electrif. 2020, 6, 1–12. [Google Scholar]

- Albuquerque, J.; Cardoso, A.J.M.; Simoes, M.G. Control of Power Converters for Aircraft Electrical Systems: Challenges and Solutions. IEEE Trans. Aerosp. Electron. Syst. 2021, 57, 1–11. [Google Scholar]

- Haykin, S. Adaptive Filter Theory, 5th ed.; Pearson: Upper Saddle River, NJ, USA, 2013. [Google Scholar]

- Khalil, H.K. Nonlinear Systems, 3rd ed.; Prentice Hall: Upper Saddle River, NJ, USA, 2002. [Google Scholar]

| Method | Complexity | Accuracy | Noise rejection | Covergence |

|---|---|---|---|---|

| LPF on d[n] | Low | Moderate | Good | Moderate |

| Variable step-size LPF | Medium | High | Very good | Fast |

| Magnitude-based | High | Very High | Excellent | Moderate |

| Adaptive multi-rate | High | High | Very good | Very fast |

| Method | Settling time | Overshoot | Frequency error |

|---|---|---|---|

| SRF-PLL | Highest | Moderate | Very small |

| SOGI-PLL | Medium | Small | Very small |

| Proposed Method | Lowest | Very small | Very small |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2026 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license.