Submitted:

02 February 2026

Posted:

03 February 2026

You are already at the latest version

Abstract

Keywords:

1. Introduction

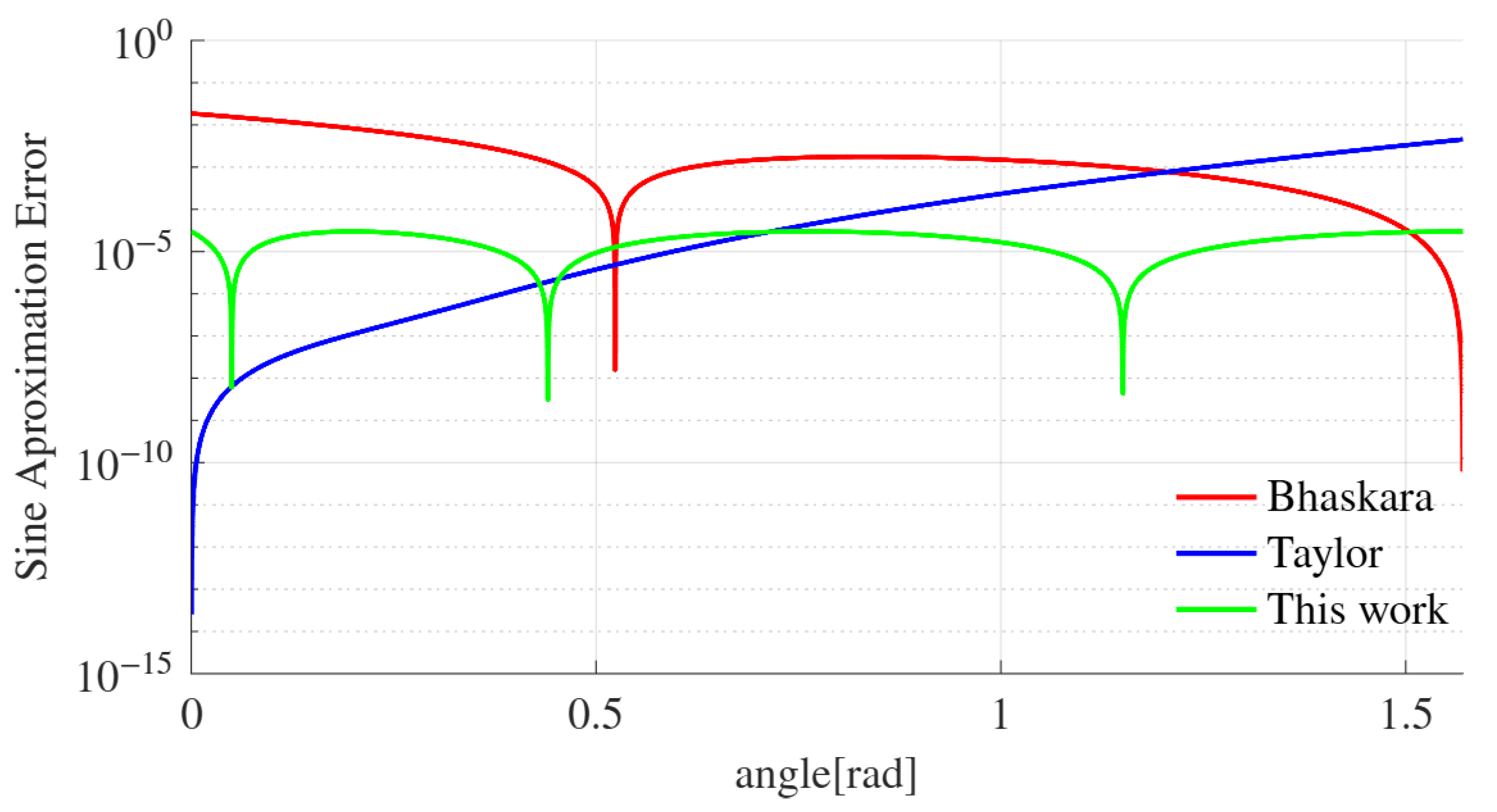

2. Background

2.1. Digital Synthesis of Sinusoidal Waves

2.2. Polynomial Approximation of Cosine Using Horner’s Polynomial Scheme

| Algorithm 1:Iterative Horner approximation algorithm |

whiledo

end while

|

2.3. Symmetry Around and Quadrant Orientation

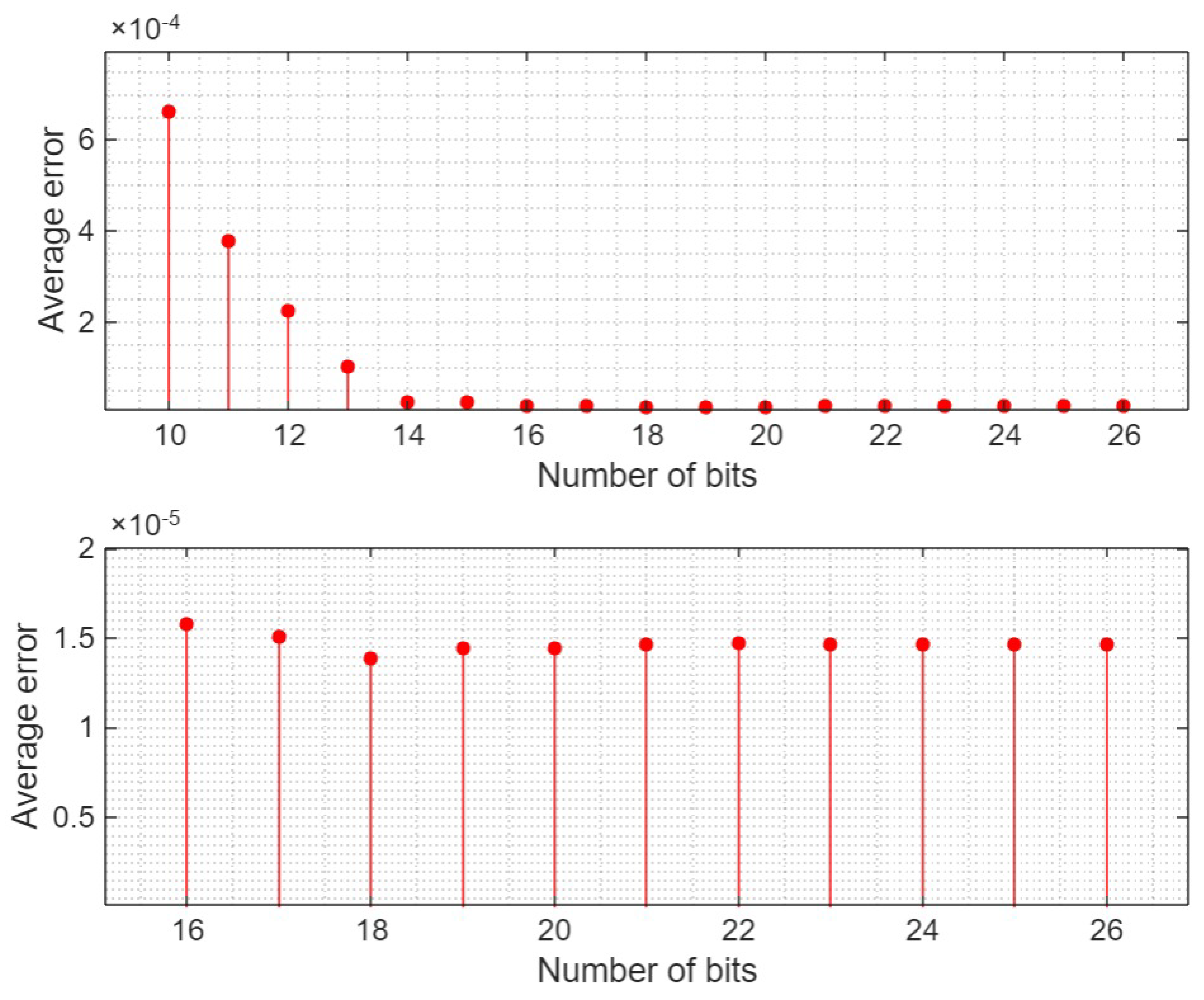

2.4. Number Format and Precision

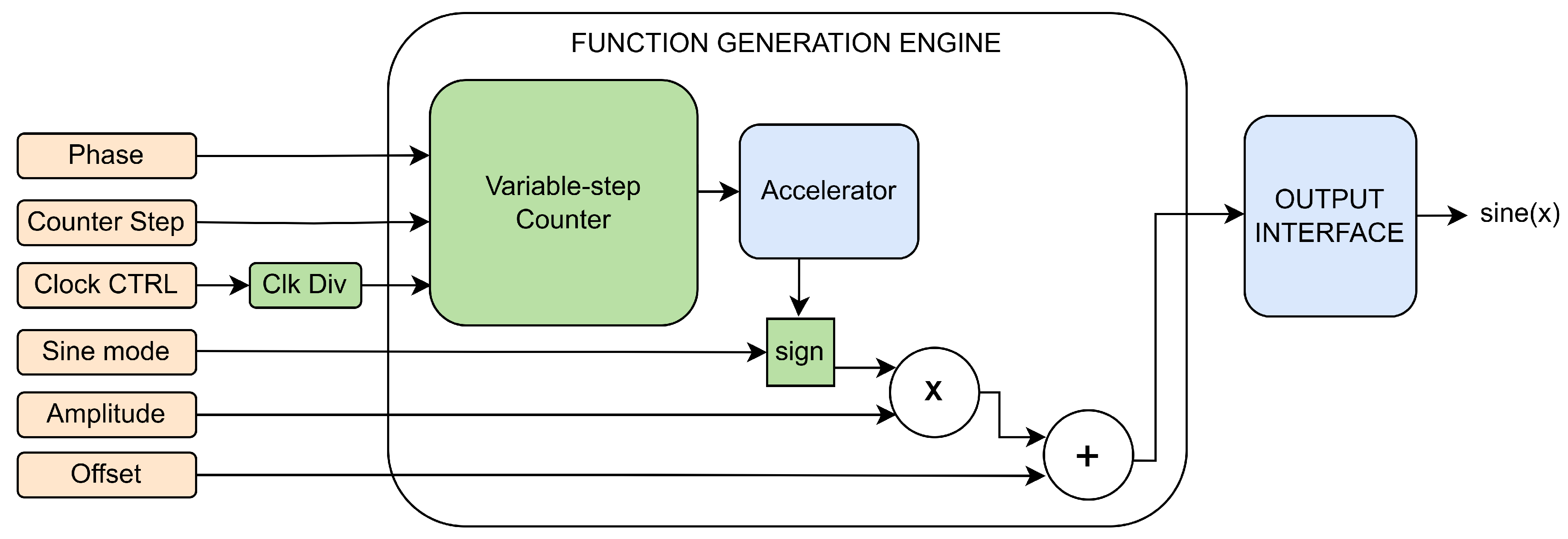

3. Proposed Cosine Synthesizer Based on Horner Polynomial Scheme

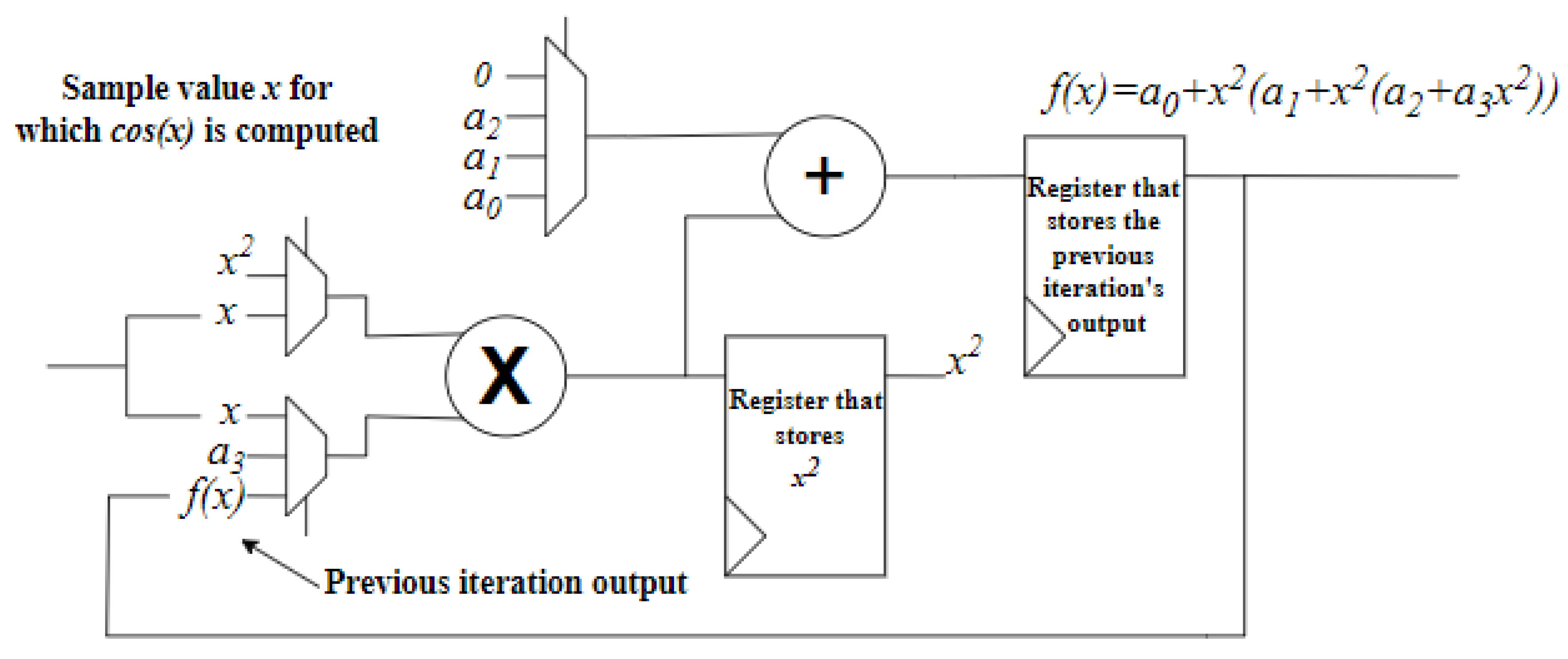

3.1. The Cosine Synthesizer Core

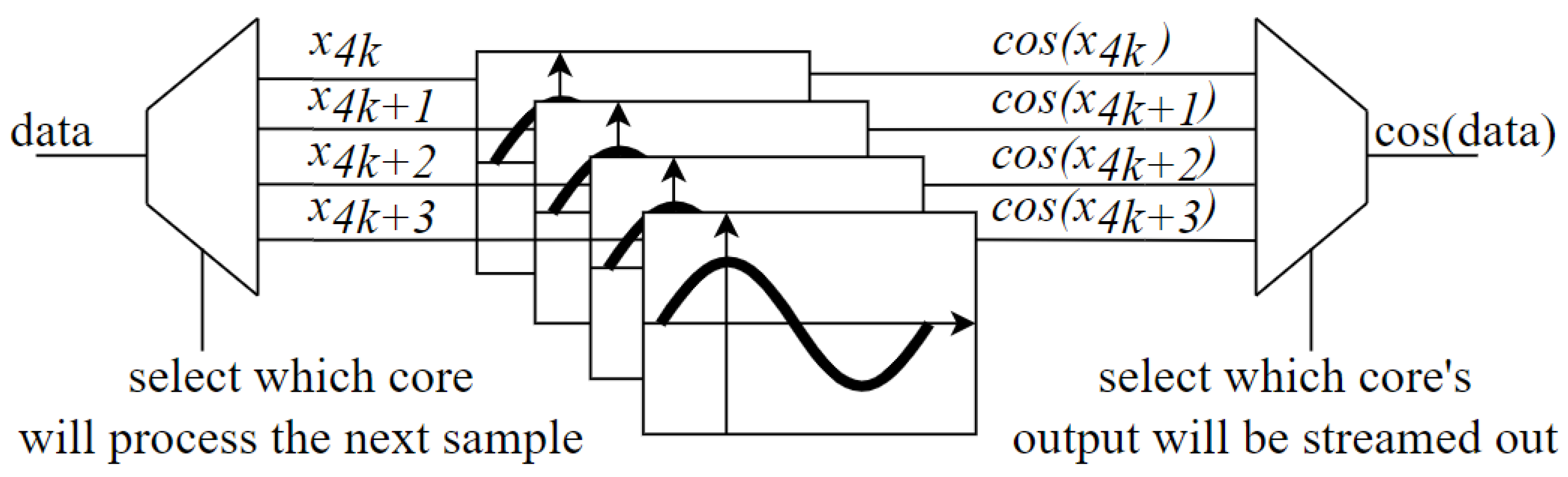

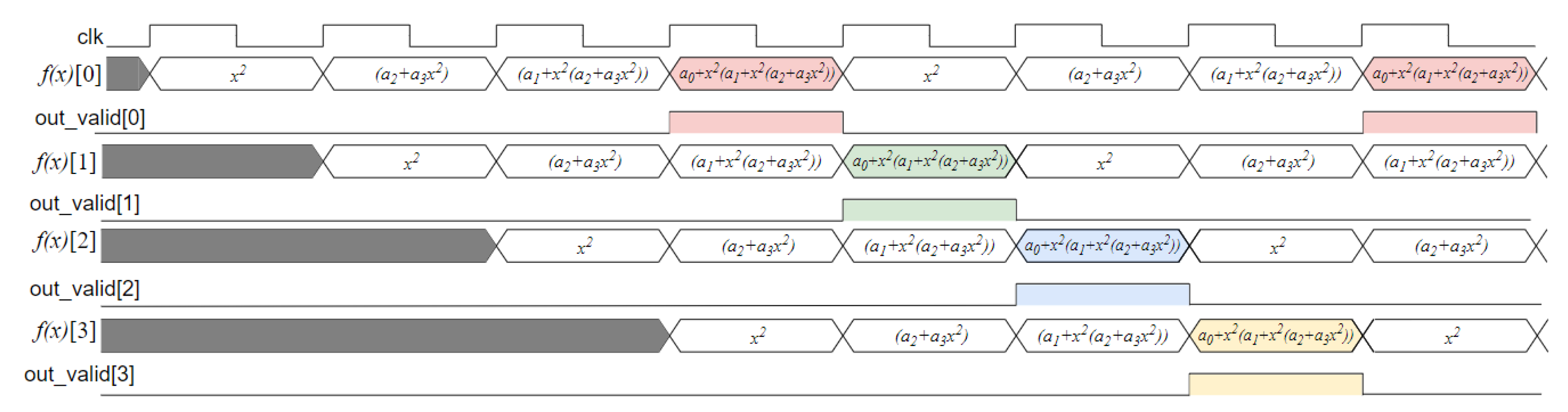

3.2. Interleaving Cosine Synthesizer Cores

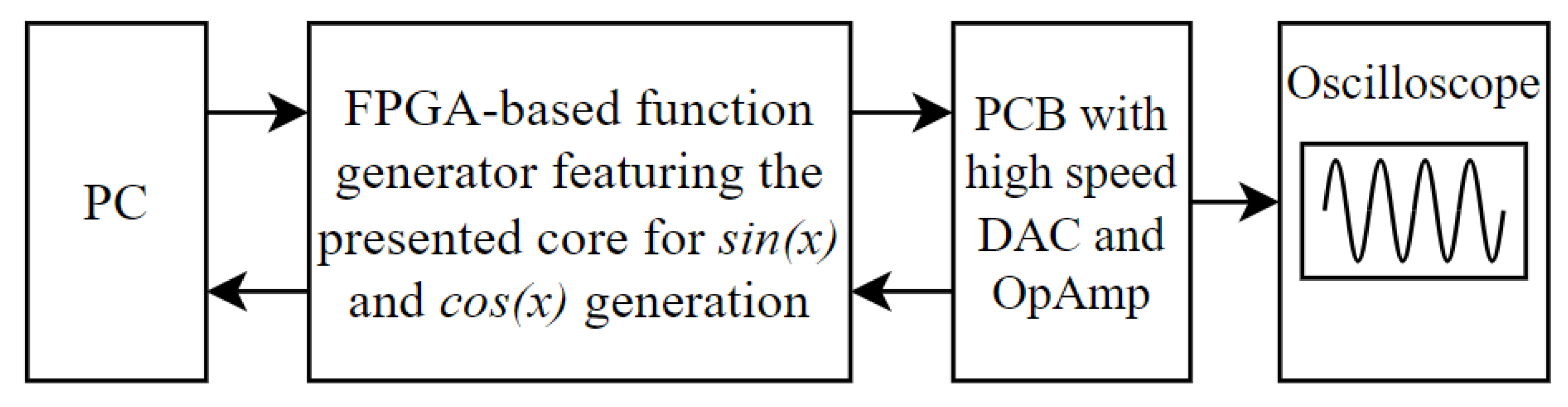

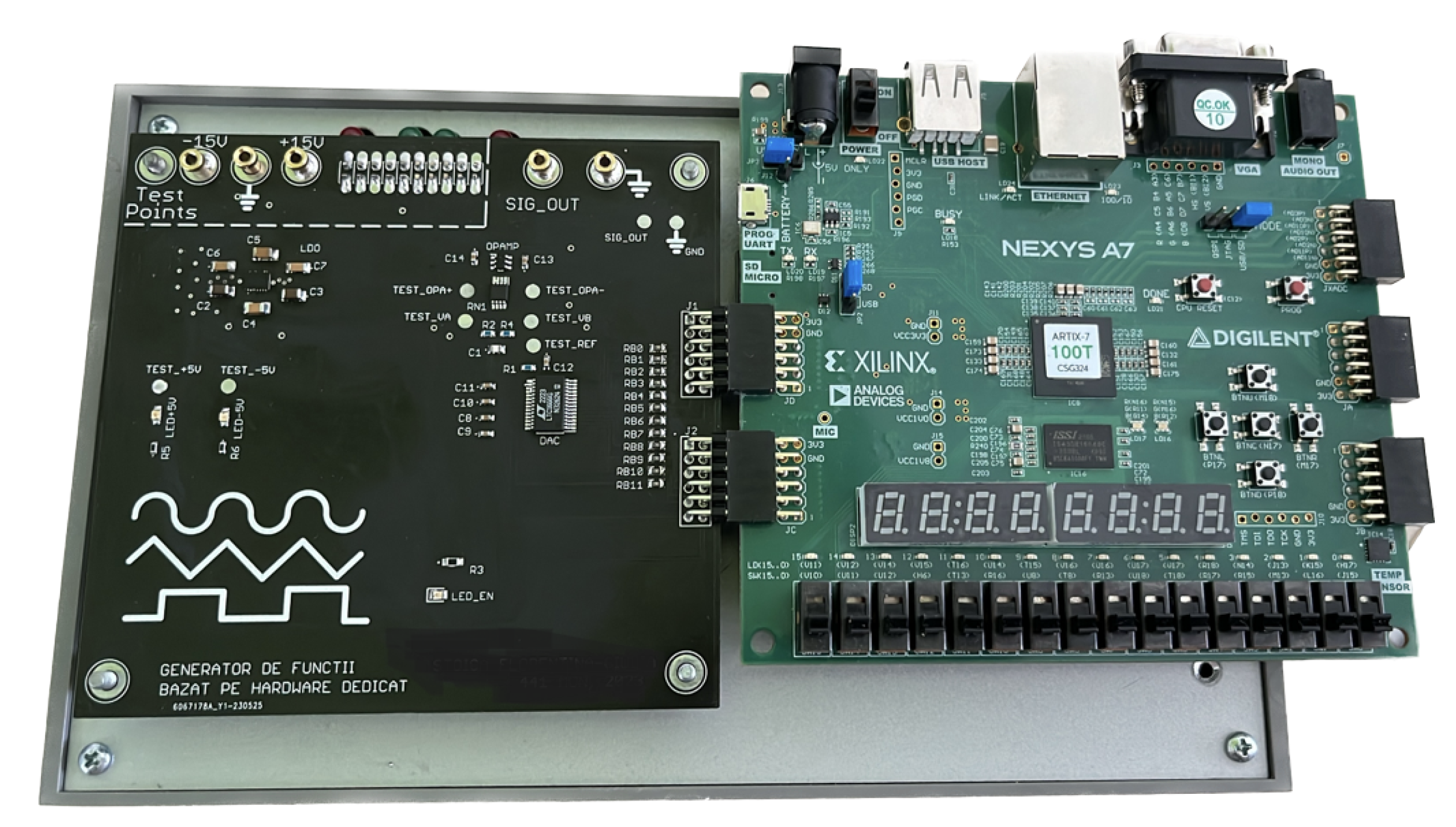

4. Validation Environment

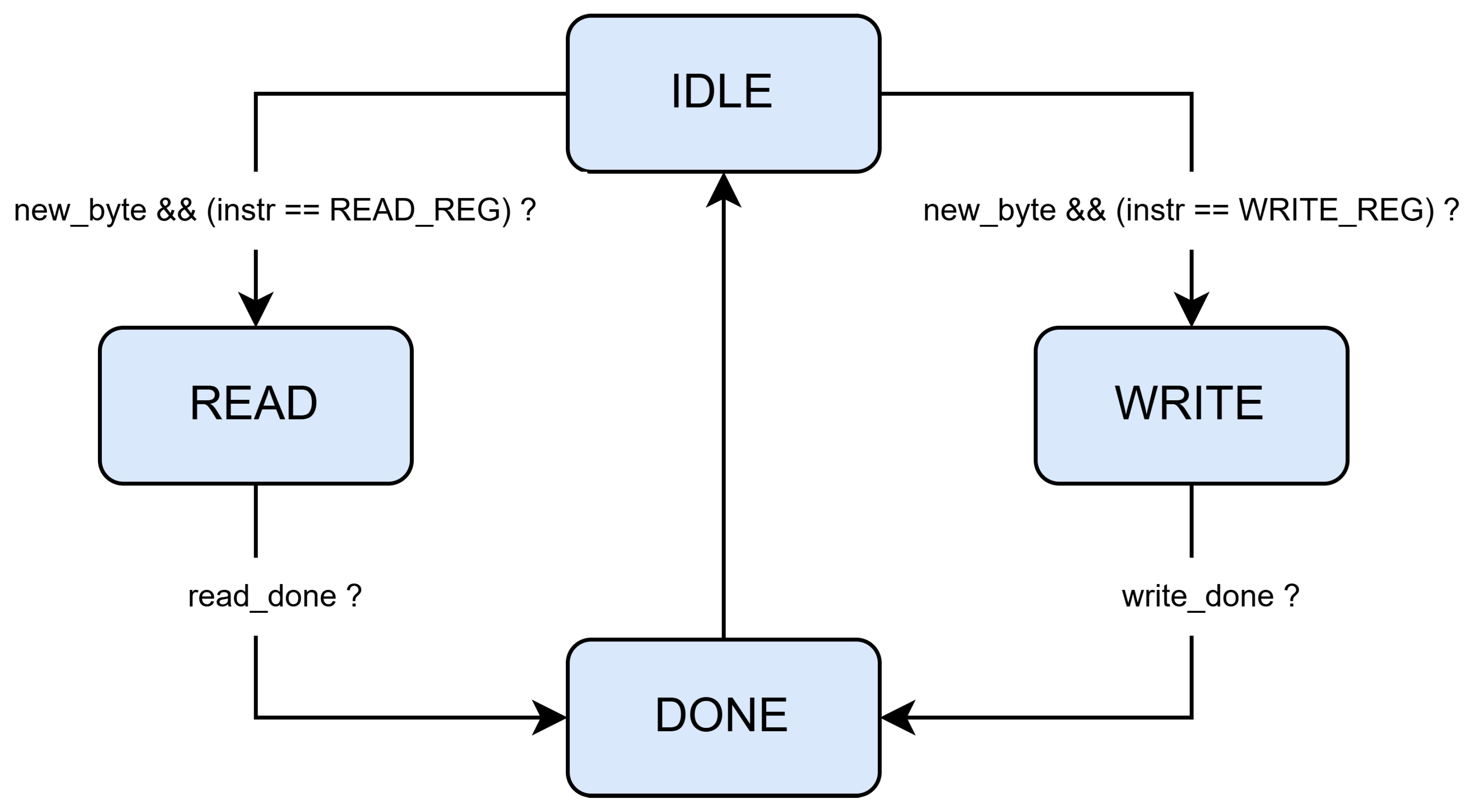

4.1. PC Custom Communication Interface

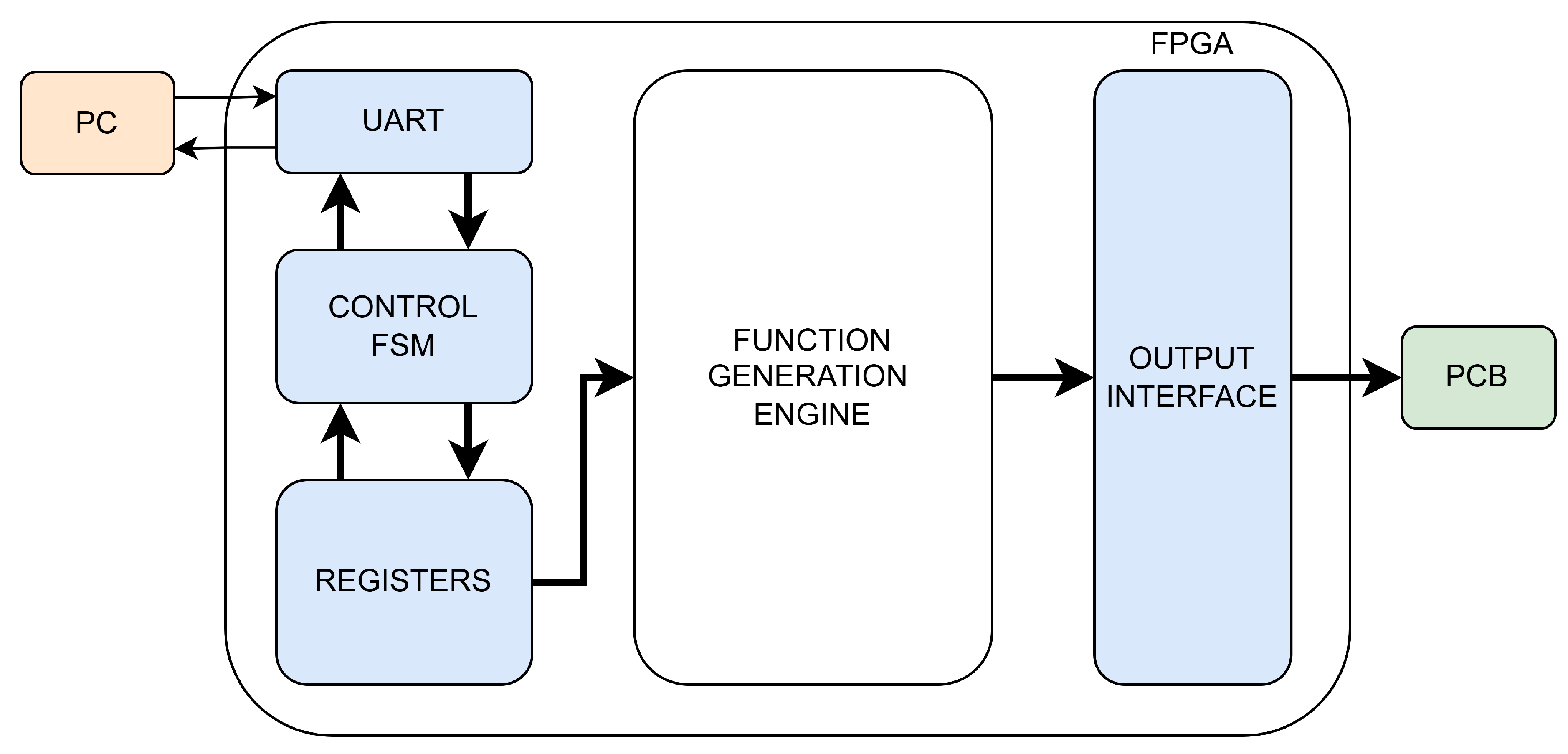

4.2. FPGA IPs

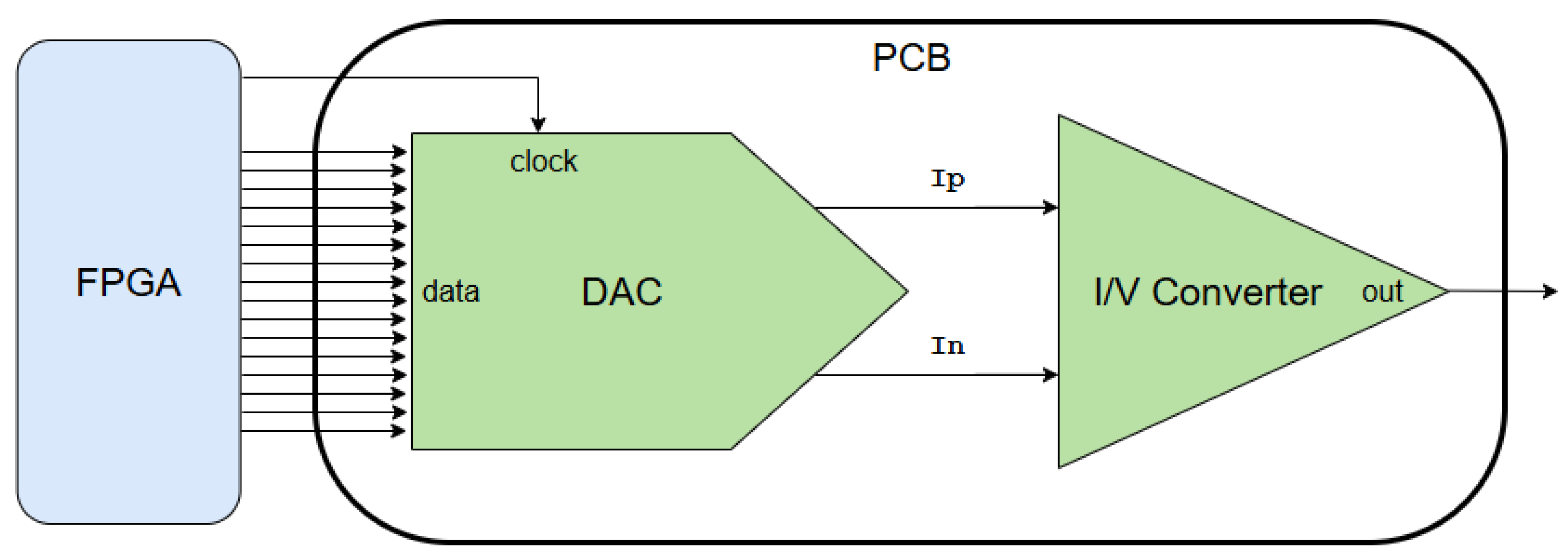

4.3. The Custom High Speed DAC Board

5. Results

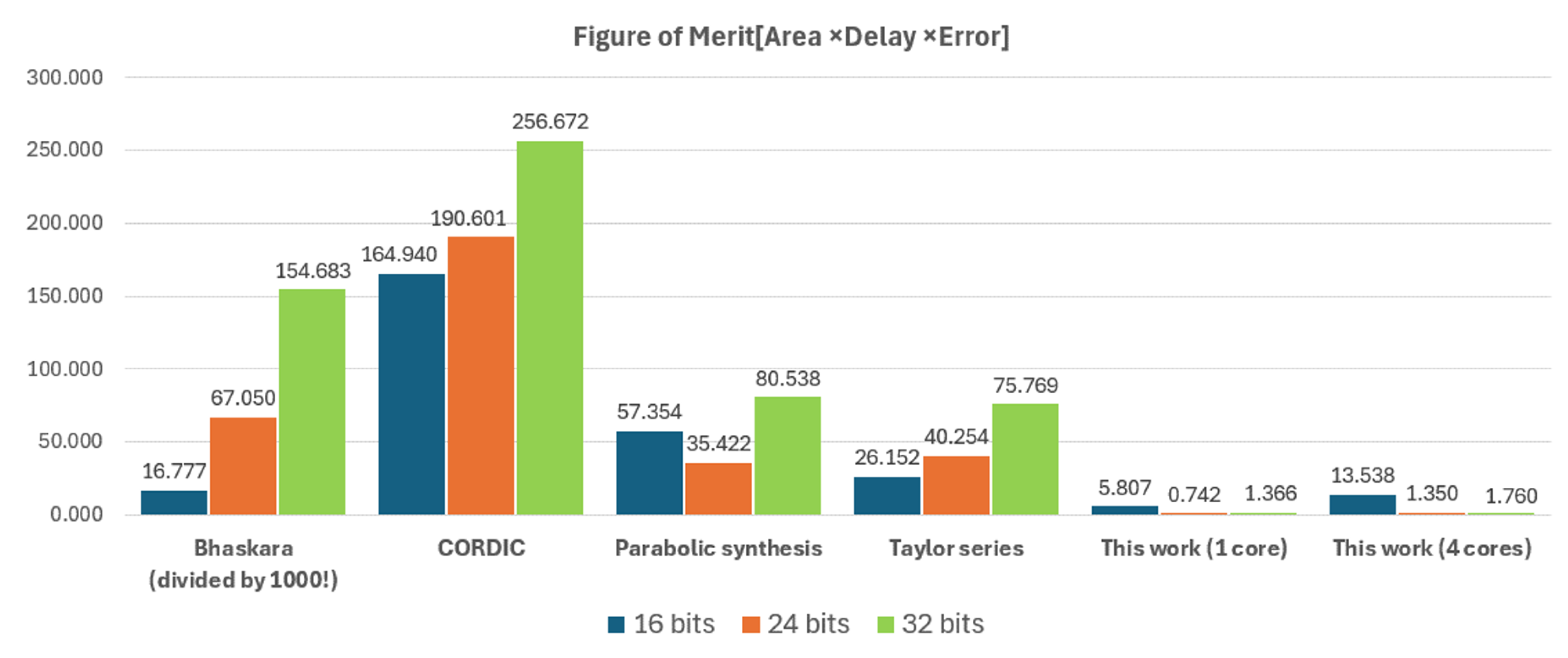

5.1. Implementation Results

- Single-Core Latency: To ensure a fair comparison of throughput, the delay component for our single-core synthesizer was multiplied by four, reflecting its four-cycle latency to produce a new sample.

- CORDIC Reference: The speed for the CORDIC algorithm was not benchmarked in [10] due to its variable latency. Therefore, we conservatively used its minimum (best-case) delay value for this FoM calculation as a reference point.

- Visual Scaling: In Figure 11, the FoM for the Bhaskara implementation was scaled down by a factor of 1000. This was necessary for visual clarity to prevent its significantly larger value from obscuring the comparison between the other, more efficient designs.

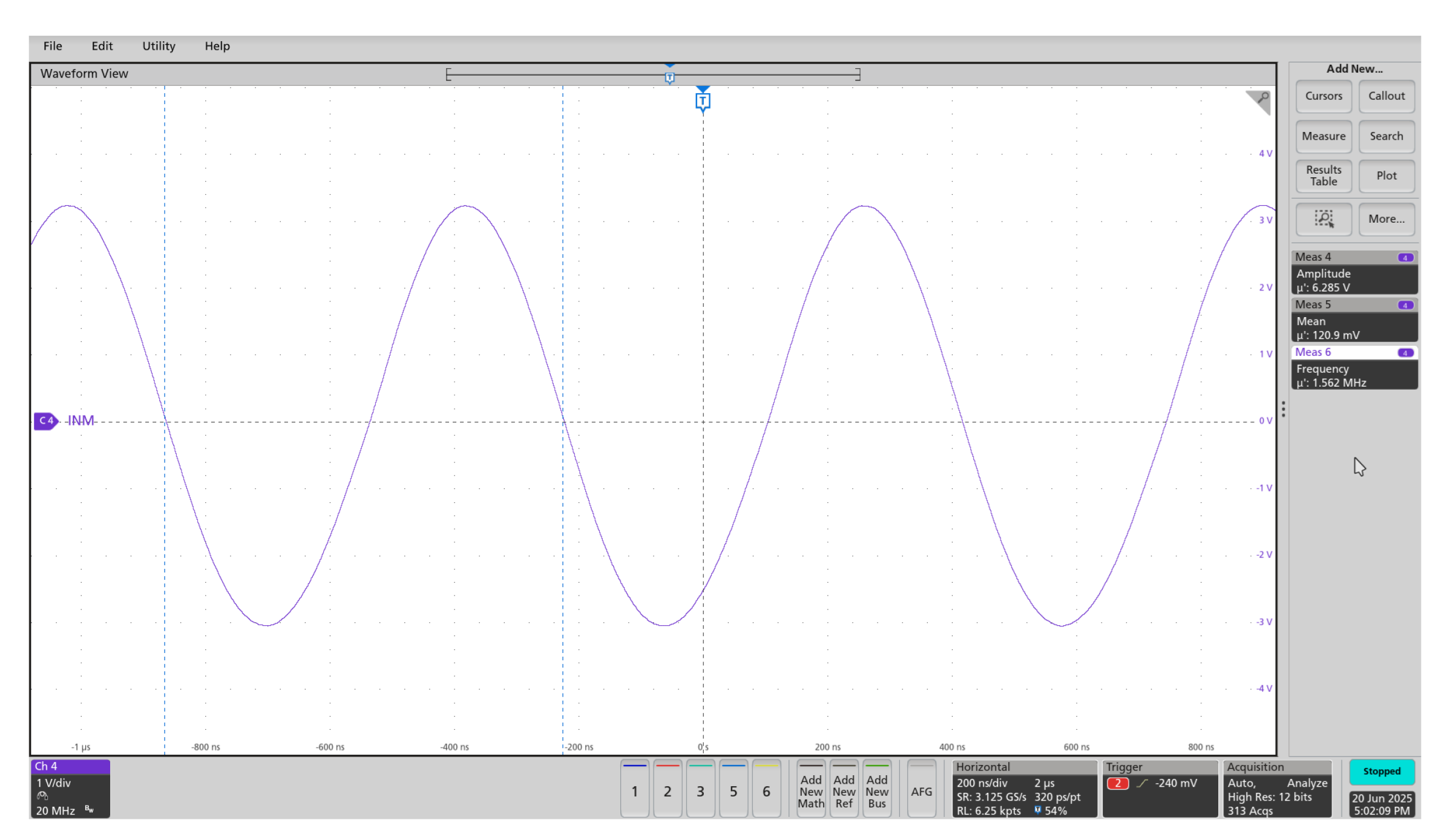

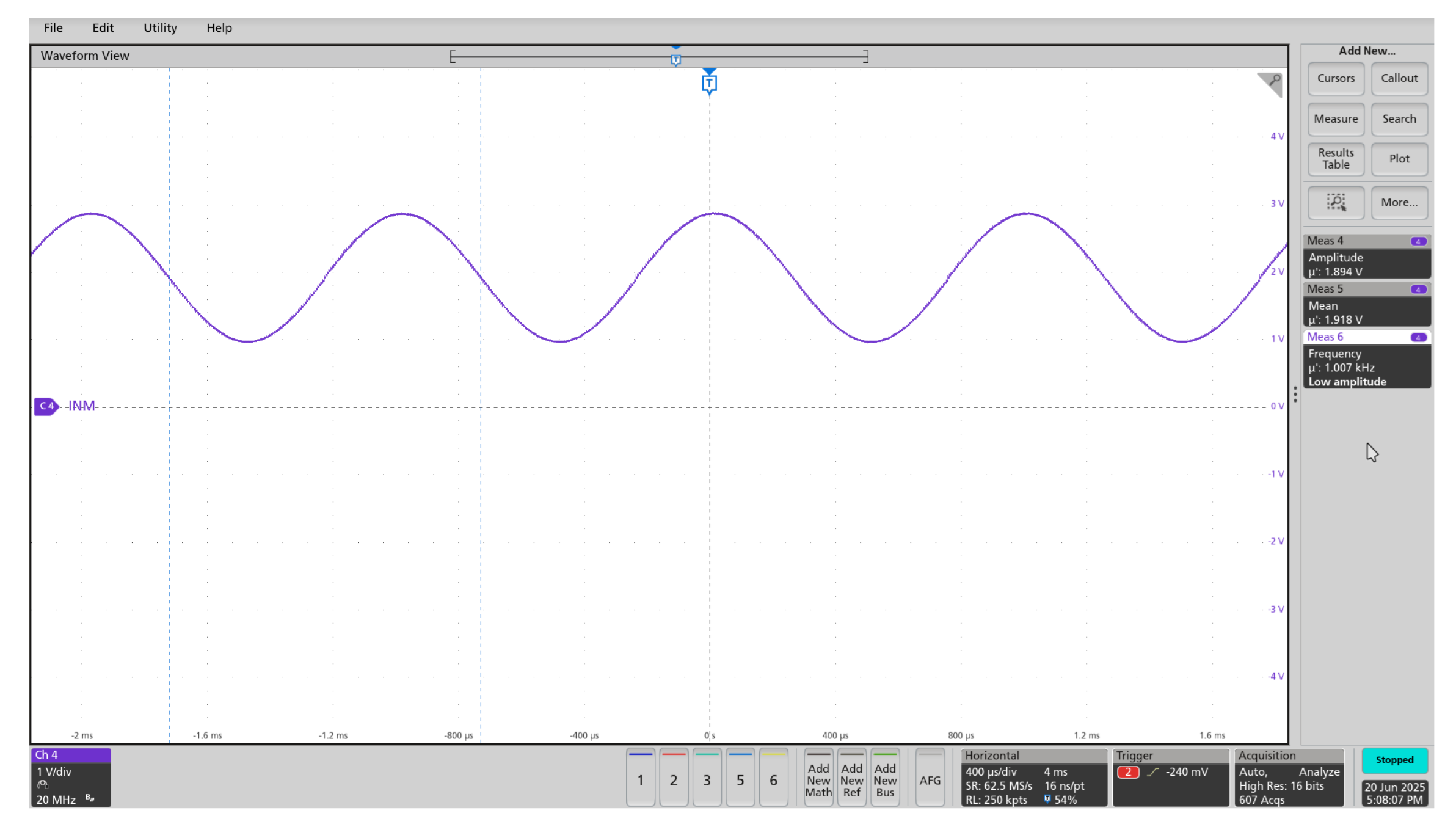

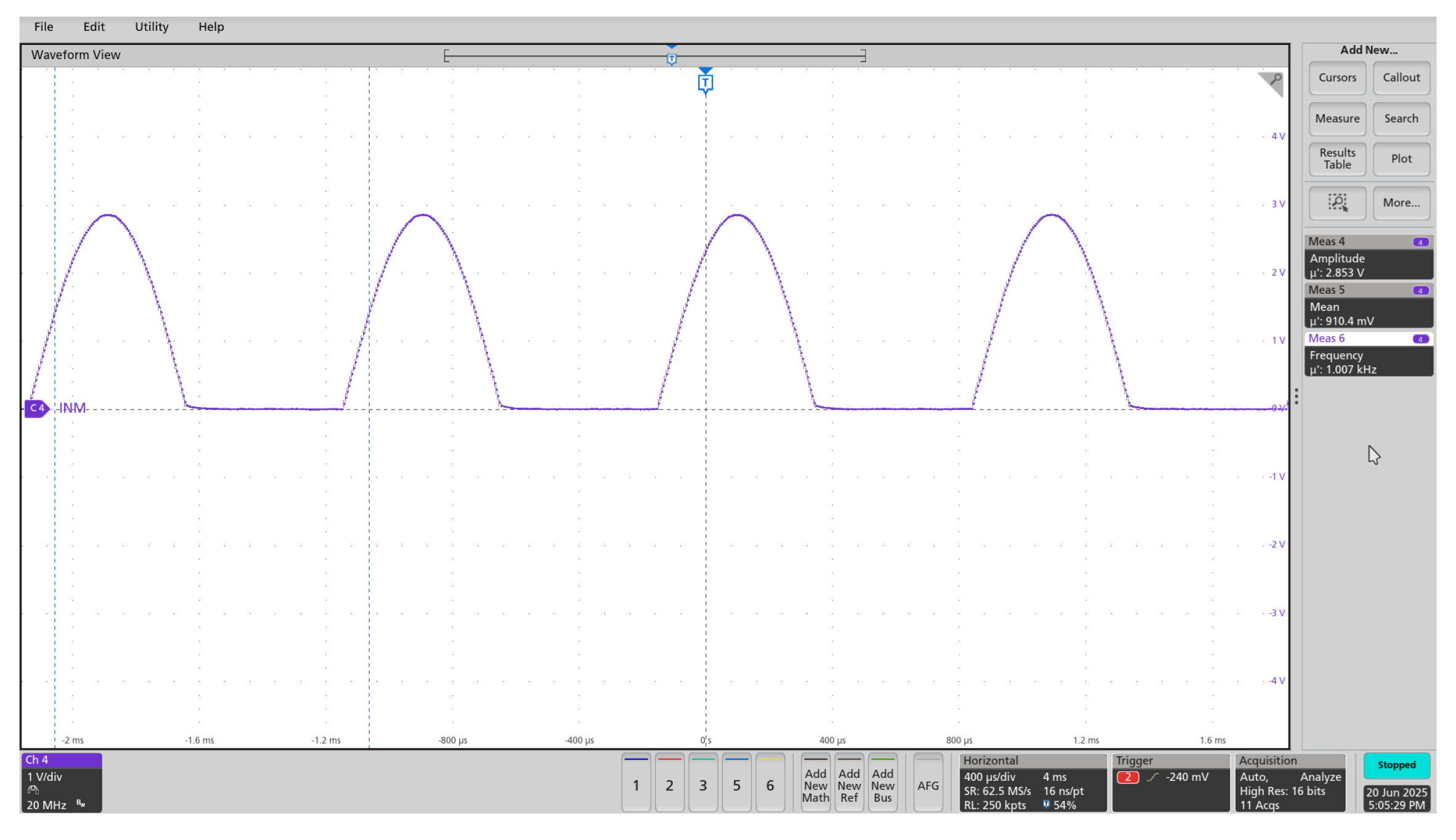

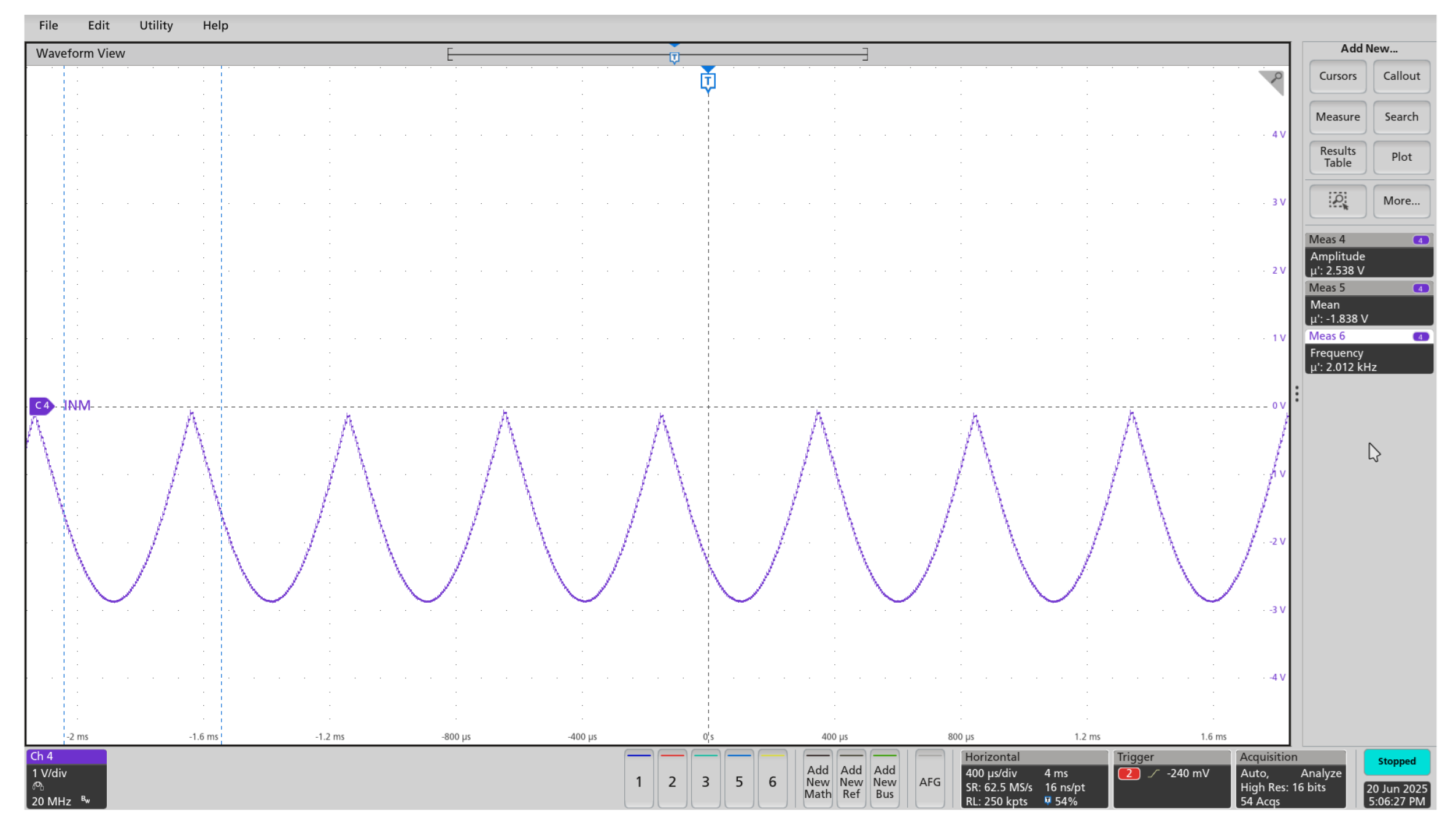

5.2. Experimental Validation

6. Conclusions

Funding

Abbreviations

| ASIC | Application-Specific Integrated Circuit |

| DAC | Digital-to-Analog Converter |

| DDS | Direct Digital Synthesis |

| DMA | Direct Memory Access |

| EMI | Electromagnetic Interference |

| FoM | Figure of Merit |

| FPGA | Field Programmable Gate Array |

| FSM | Finite State Machine |

| IP | Intellectual Property |

| LUT | Lookup Table |

| MAC | Multiply Accumulate |

| PCB | Printed Circuit Board |

| PWM | Pulse-Width Modulation |

| ROM | Read-Only Memory |

| SoC | System on Chip |

| UART | Universal Asynchronous Receiver/Transmitter |

| USB | Universal Serial Bus |

References

- Kim, J.; Mohamed, M. G. A.; Kim, H. Design of a Frequency Division Concurrent sine wave generator for an efficient touch screen controller SoC. 2015 International Symposium on Consumer Electronics (ISCE), Madrid, Spain, 2015; pp. 1–2. [Google Scholar]

- Bendicks, A.; Peters, A.; Frei, S. FPGA-Based Active Cancellation of the EMI of a Boost Power Factor Correction (PFC) by Injecting Modulated Sine Waves. IEEE Letters on Electromagnetic Compatibility Practice and Applications vol. 3(no. 1), 11–14. [CrossRef]

- Baozhong, Xie; Tiequn, Chen. Sine wave algorithm based on 2nd offset and its implementation in FPGA. IEEE 2011 10th International Conference on Electronic Measurement & Instruments, Chengdu, China, 2011; pp. 173–176. [Google Scholar]

- Adiono, T.; Timothy, V.; Ahmadi, N.; Candra, A.; Mufadli, K. CORDIC and Taylor based FPGA music synthesizer. TENCON 2015 - 2015 IEEE Region 10 Conference, Macao, China, 2015; pp. 1–6. [Google Scholar]

- Lutter, K.; Backer, A.; Drese, K.S. Guided Acoustic Waves in Polymer Rods with Varying Immersion Depth in Liquid. Sensors 2023, 23, 9892. [Google Scholar] [CrossRef] [PubMed]

- NXP Semiconductor, Sinusoidal Control of BLDCM with Hall Sensors - Application Note.

- Miller, Alec. AN3312: Arbitrary Waveform Generator Using DAC and DMA; Microchip Technology Inc.

- Revanna, N.; Viswanathan, T. R. Low frequency CMOS sinusoidal oscillator for impedance spectroscopy. 2014 IEEE Dallas Circuits and Systems Conference (DCAS), Richardson, TX, USA, 2014; pp. 1–4. [Google Scholar]

- Strelnikov, I. V.; Ryabov, I. V.; Klyuzhev, E. S. Direct Digital Synthesizer of Phase-Manipulated Signals, Based on the Direct Digital Synthesis Method. In 2020 Systems of Signal Synchronization, Generating and Processing in Telecommunications (SYNCHROINFO); Svetlogorsk, Russia, 2020; pp. 1–3. [Google Scholar]

- Roy, S. Discretized Sinusoidal Waveform Generators for Signal Processing Applications. 2018 2nd International Conference on Trends in Electronics and Informatics (ICOEI); pp. 1350–1353.

- Stoica, F. -G.; Calinescu, A.; Enachescu, M. A High-Speed, Area-Optimized, ROM-Less (Co)Sine Wave Synthesis Accelerator. 2024 International Symposium on Electronics and Telecommunications (ISETC), Timisoara, Romania; 2024, pp. 1–4. [CrossRef]

- BRUNELLI, C; BERG, H; GUEVORKIAN, D. Approximating sine functions using variable-precision taylor polynomials [J]; SiPS; pp. 57–62.

- Nekounamm, M.; Eshghi, M. An efficient ROM-less direct digital synthesizer based on Bhaskara I’s sine approximation formula. 2012 IEEE International Frequency Control Symposium Proceedings, Baltimore, MD, USA, 2012; pp. 1–6. [Google Scholar]

- LI, X J. A Direct digital frequency synthesizer based on two segment fourth-order parabolic approximation [J]. IEEE Transactions on Consumer Electronics vol. 55(no. 2), 322–326. [CrossRef]

- Chinnathambi, M.; Bharanidharan, N.; Rajaram, S. FPGA implementation of fast and area efficient CORDIC algorithm. 2014 International Conference on Communication and Network Technologies, Sivakasi, India, 2014; pp. 228–232. [Google Scholar]

- Schlör, Lasse. Fast MiniMax Polynomial Approximations of Sine and Cosine.

| Coefficient | Value |

|---|---|

| 0.999970210689953068626323587055728078 | |

| -0.499782706704688809140466617726333455 | |

| 0.0413661149638482252569383872576459943 | |

| -0.0012412397582398600702129604944720102 |

| Functions |

|---|

| dec_to_bin(value, sign, no_of_bits_for_int, no_of_bits_for_frac) |

| bin_to_dec(value, sign, no_of_bits_for_int, no_of_bits_for_frac) |

| sine_config(sin_type, amp, off, freq, phase) |

| control_signal(enable, inverted, load_trig) |

| write_reg(reg_name, write_value) |

| read_reg(reg_name) |

| read_sine_output(x_times) |

| LUTs required for different data bus widths | |||

| Implementation | 16 bits | 24 bits | 32 bits |

| Bhaskara | 1443 | 3363 | 6065 |

| CORDIC | 800 | 912 | 1024 |

| Parabolic synthesis | 179 | 406 | 779 |

| Taylor series | 583 | 2359 | 4043 |

| This Work (1 core) | 36 | 56 | 142 |

| This Work (4 cores) | 342 | 424 | 776 |

| Highest delays for different data bus widths[ns] | |||

| Implementation | 16 bits | 24 bits | 32 bits |

| Bhaskara | 75.992 | 119.387 | 159.401 |

| Parabolic synthesis | 18.848 | 29.082 | 34.462 |

| Taylor series | 44.858 | 56.88 | 62.469 |

| This Work (1 core) | 8.402 | 10.352 | 12.656 |

| This Work (4 cores) | 8.247 | 9.952 | 11.936 |

| Relative error for different data bus widths[%] | |||

| Implementation | 16 bits | 24 bits | 32 bits |

| Bhaskara | 0.153 | 0.167 | 0.16 |

| CORDIC | 0.025 | 0.021 | 0.021 |

| Parabolic synthesis | 0.017 | 0.003 | 0.003 |

| Taylor series | 0.001 | 0.0003 | 0.0003 |

| This Work (1 core) | 0.0048 | 0.00032 | 0.00019 |

| This Work (4 cores) | 0.0048 | 0.00032 | 0.00019 |

| This Work(1 core) | This Work (4 cores) | Taylor Series | Parabolic Synthesis | CORDIC | Bhaskara | |

|---|---|---|---|---|---|---|

| 16 bits | 5.807 | 13.538 | 26.152 | 57.354 | 164.940 | 16777.438 |

| 24 bits | 0.742 | 1.350 | 40.254 | 35.422 | 190.601 | 67050.246 |

| 32 bits | 1.366 | 1.760 | 75.769 | 80.538 | 256.672 | 154682.730 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2026 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license.