Submitted:

19 January 2026

Posted:

19 January 2026

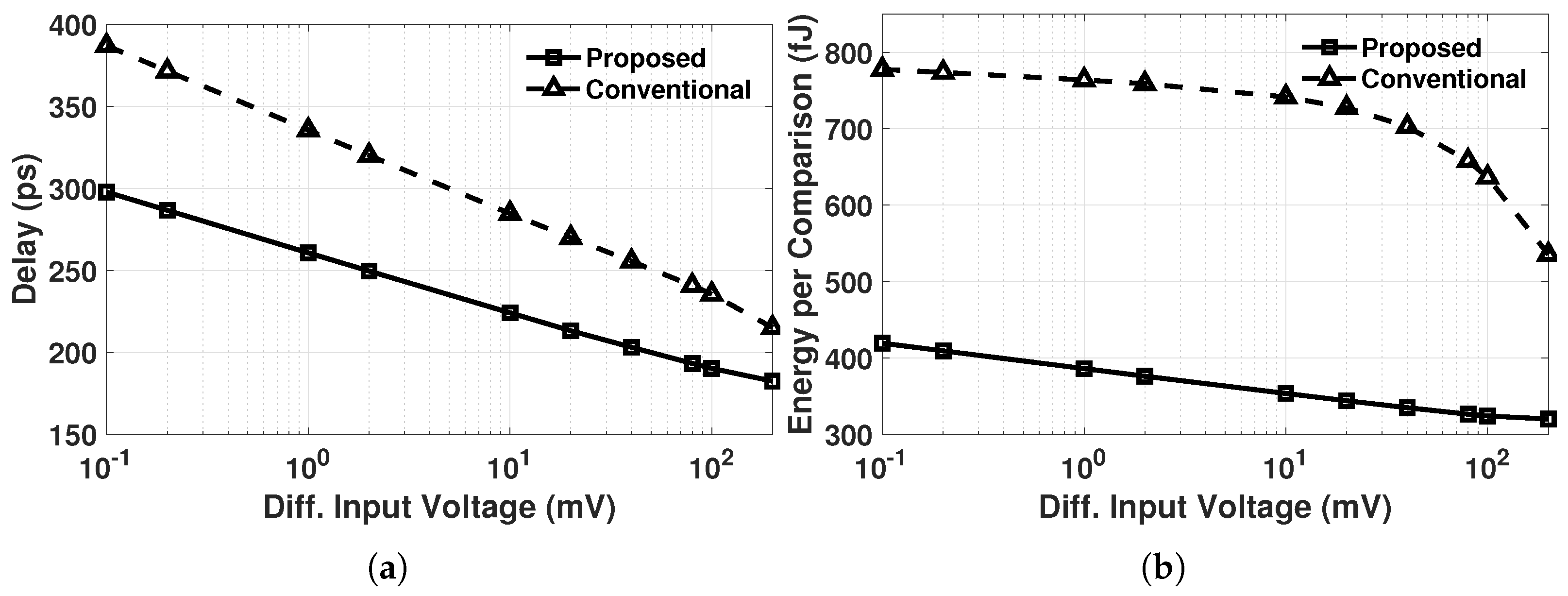

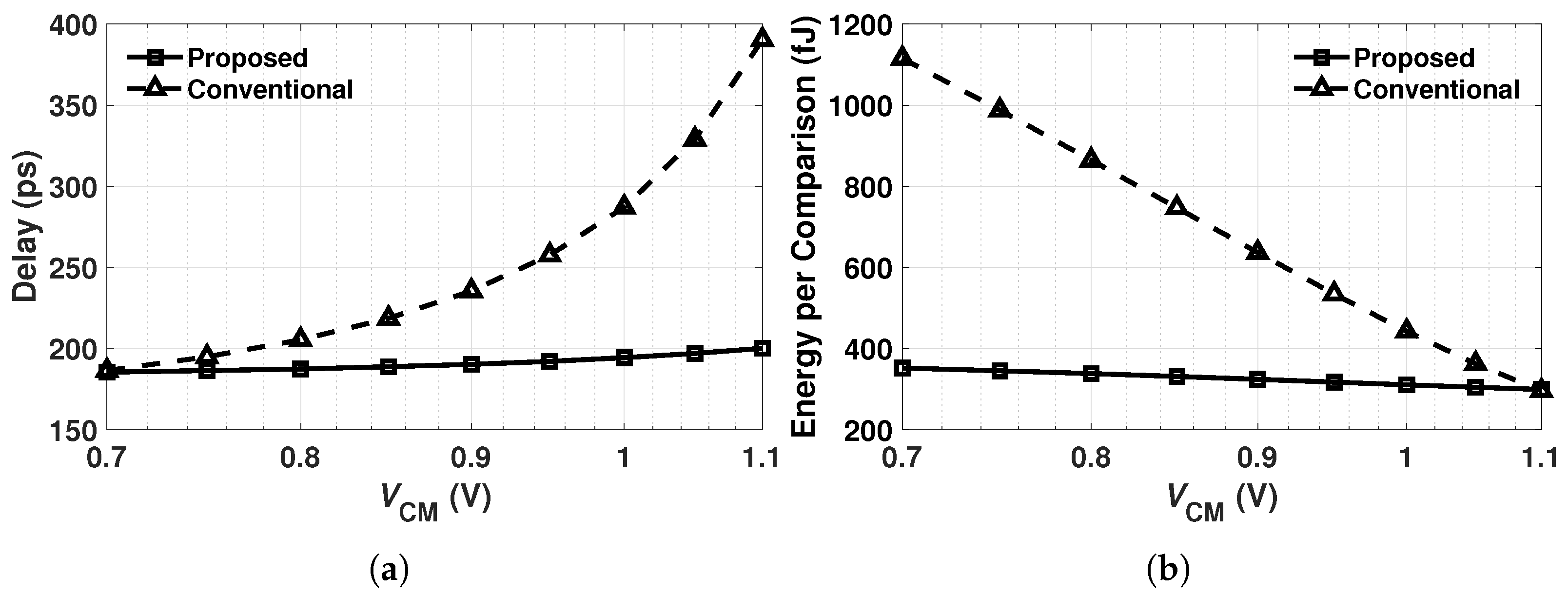

You are already at the latest version

Abstract

Keywords:

1. Introduction

2. Analysis and Design of Comparator

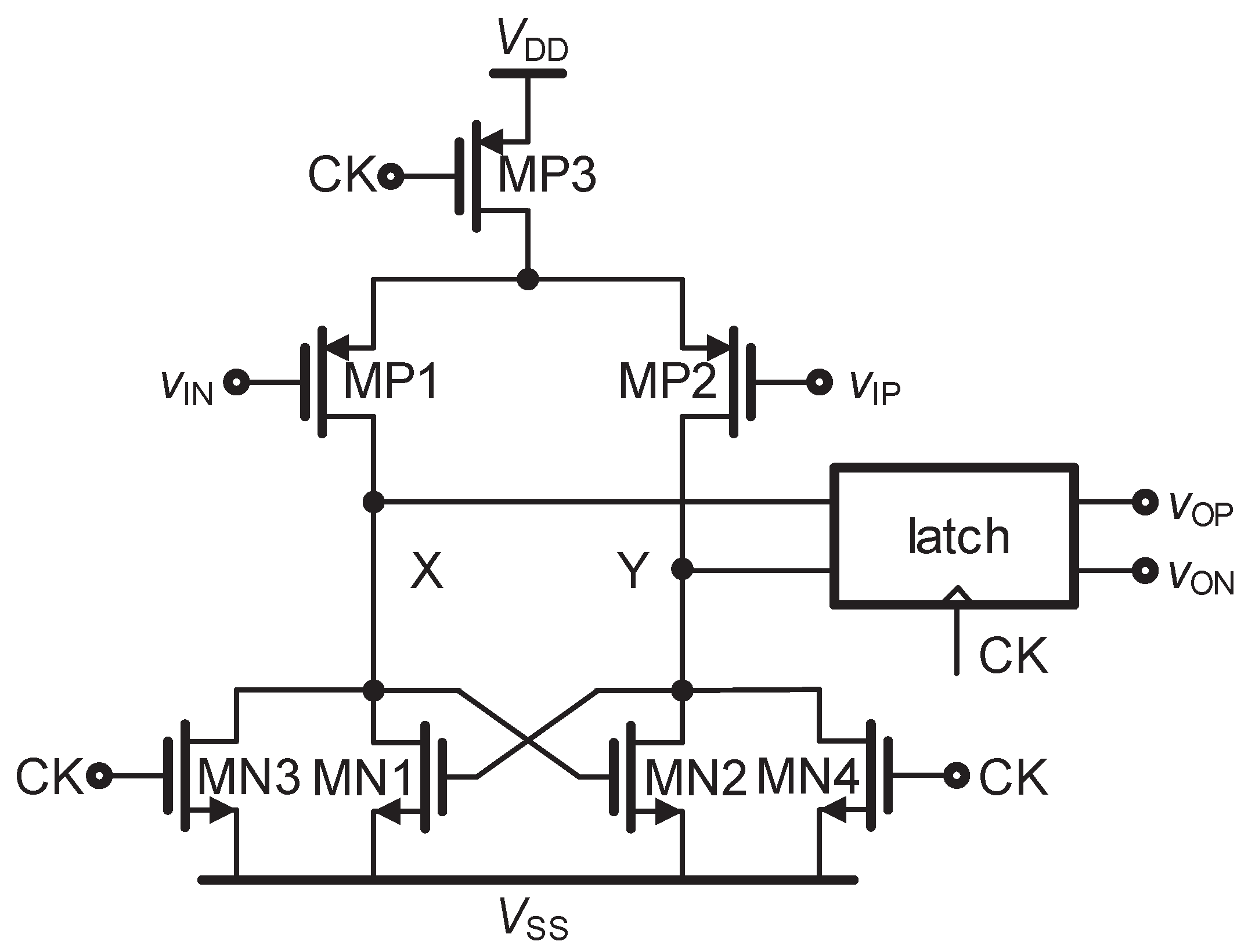

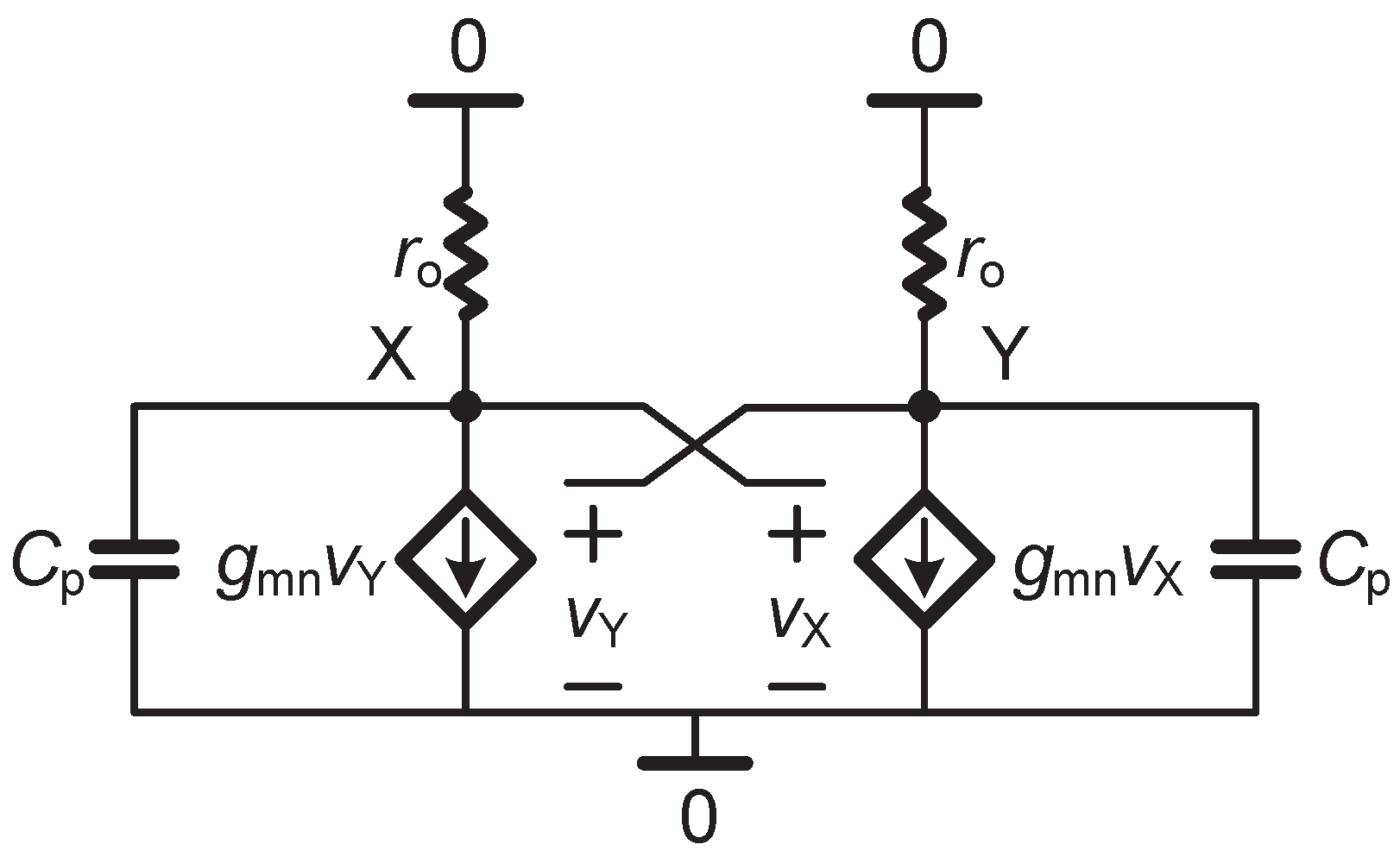

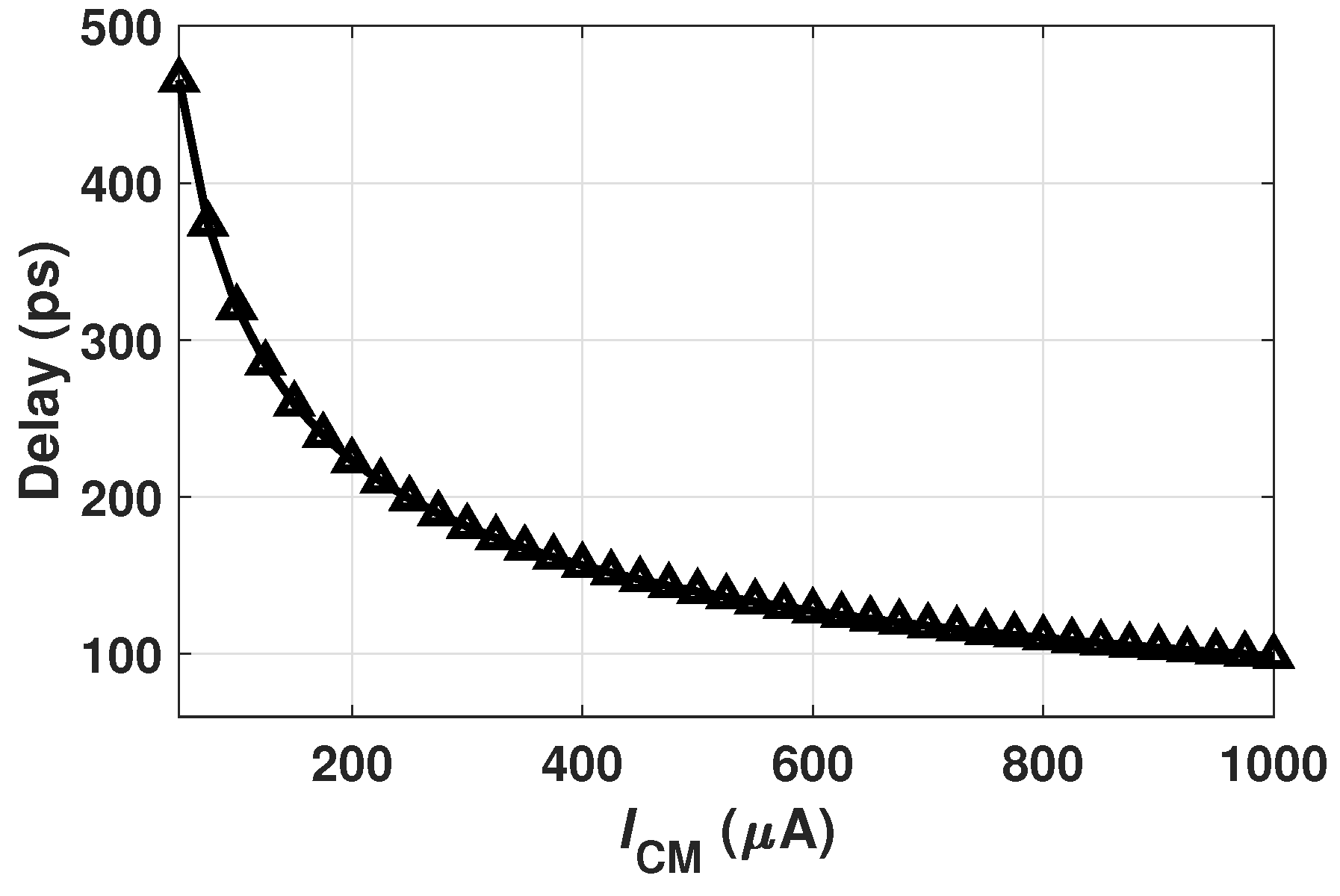

2.1. Analysis of Conventional Comparator

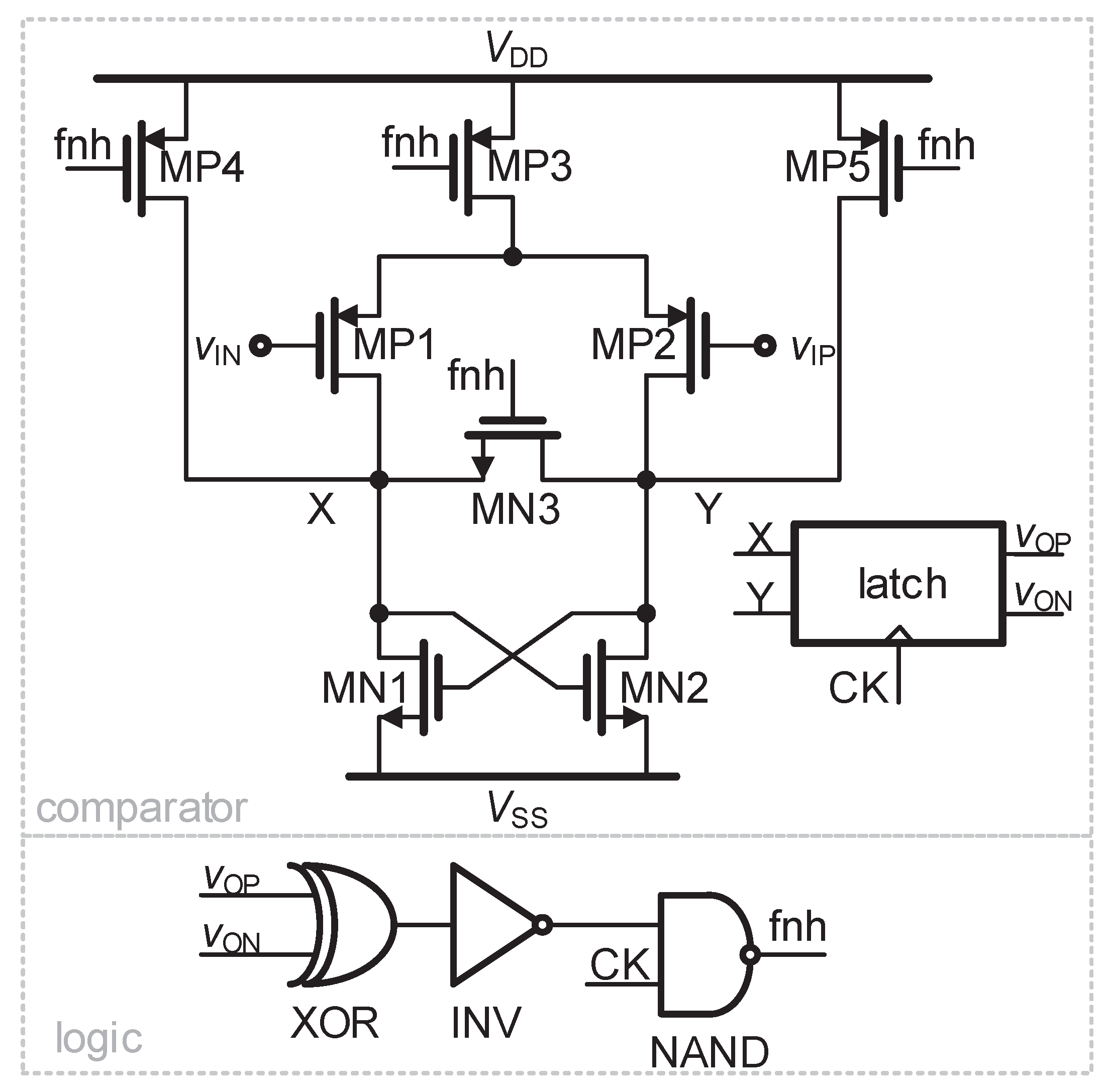

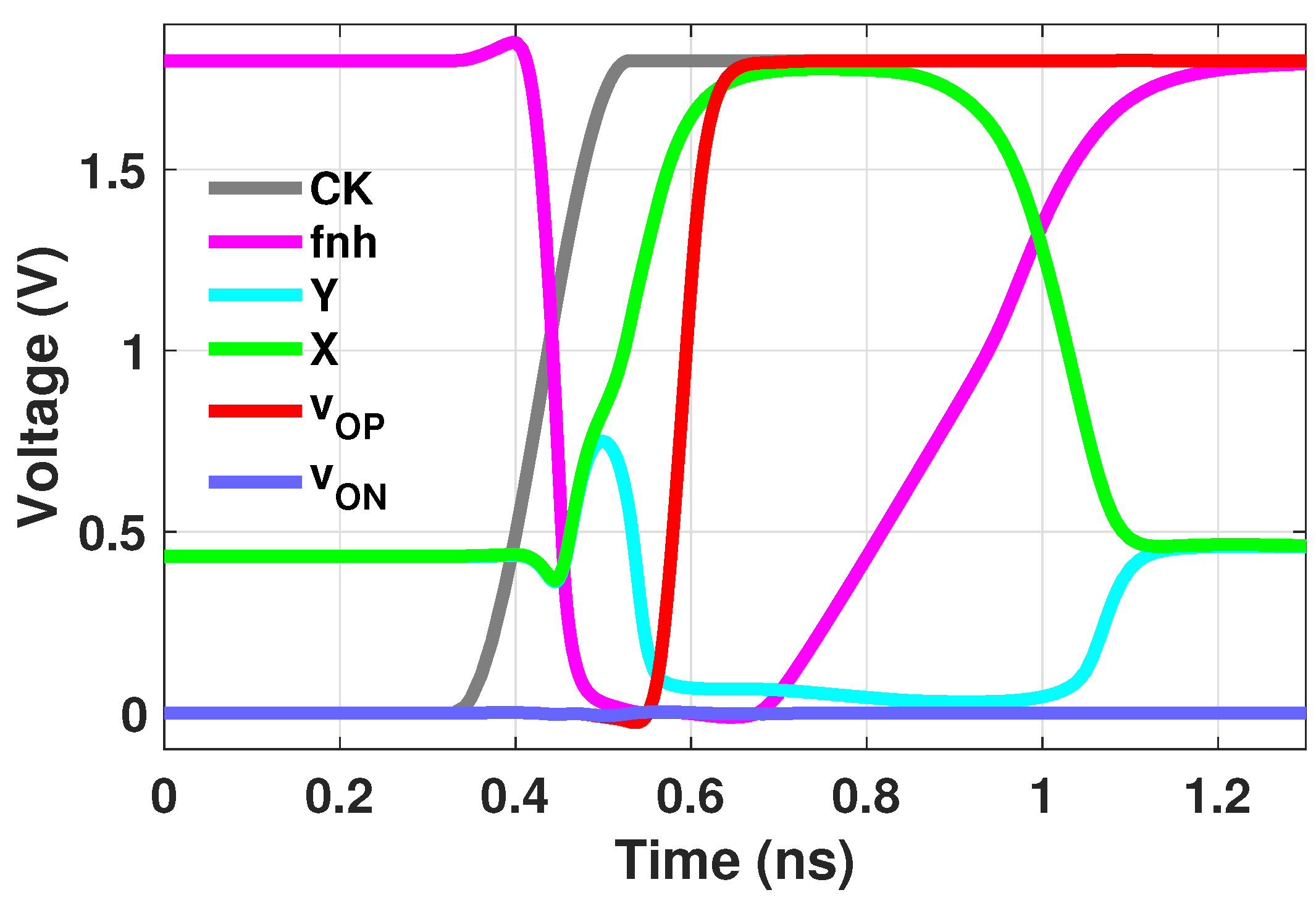

2.2. Proposed Enhanced Dynamic Bias Comparator

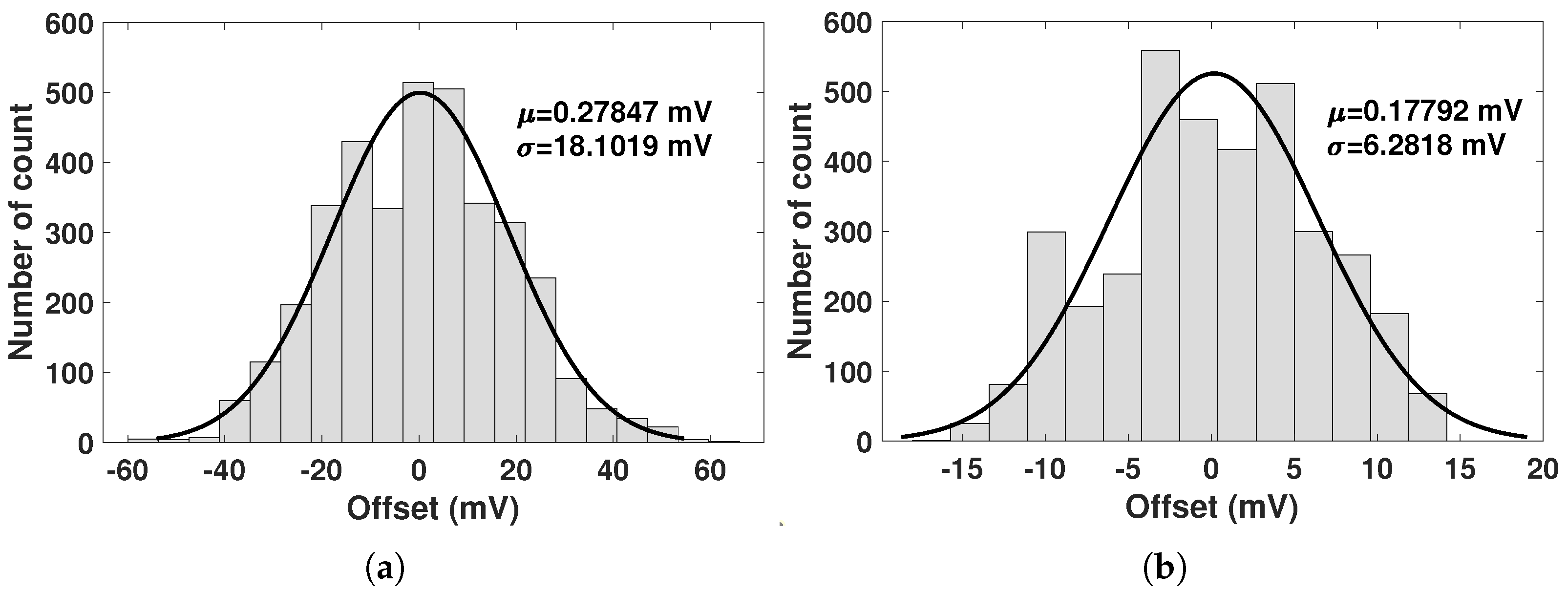

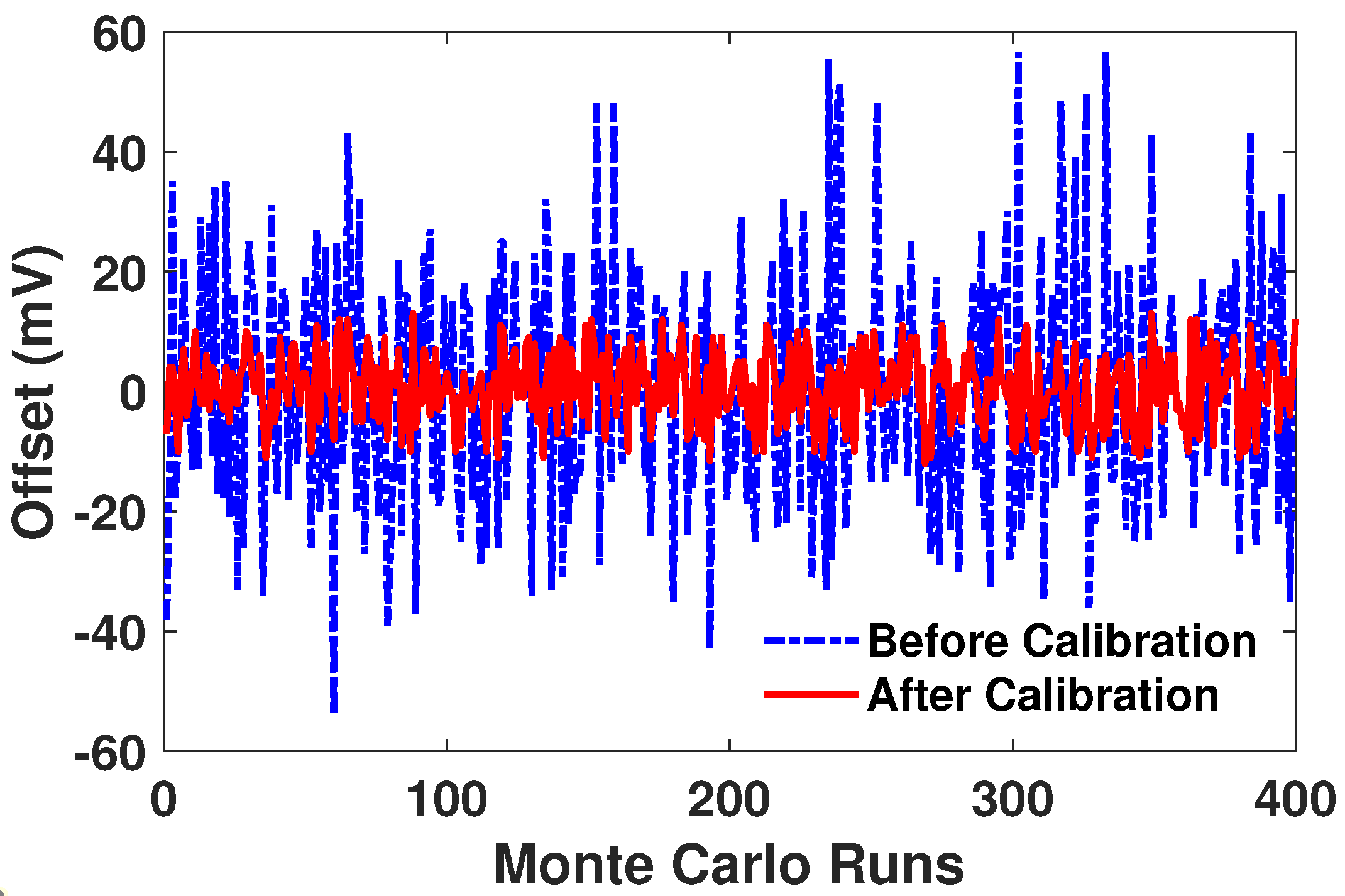

3. Design of the Offset Calibration Technique

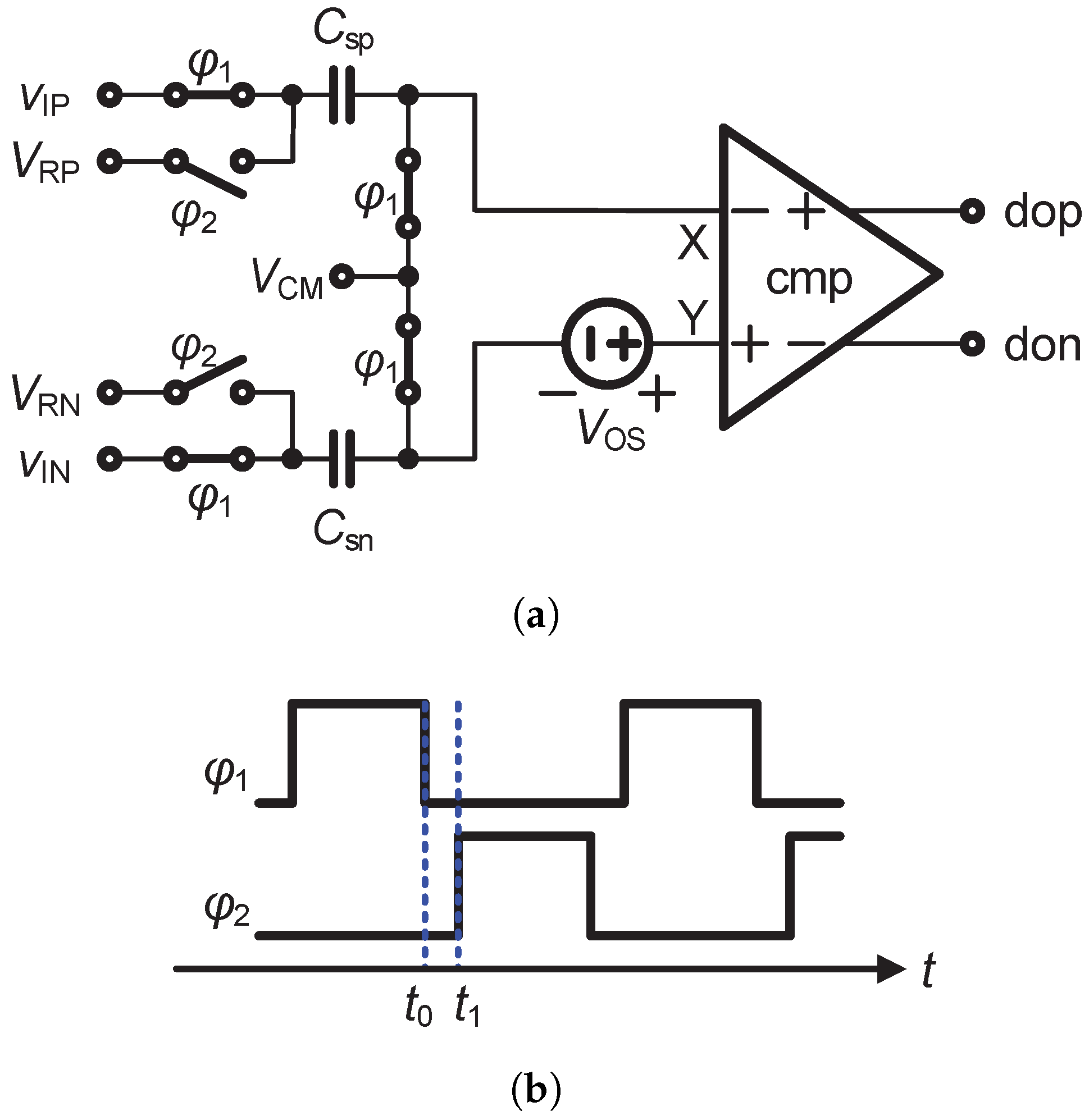

3.1. Working Principle of the Comparator

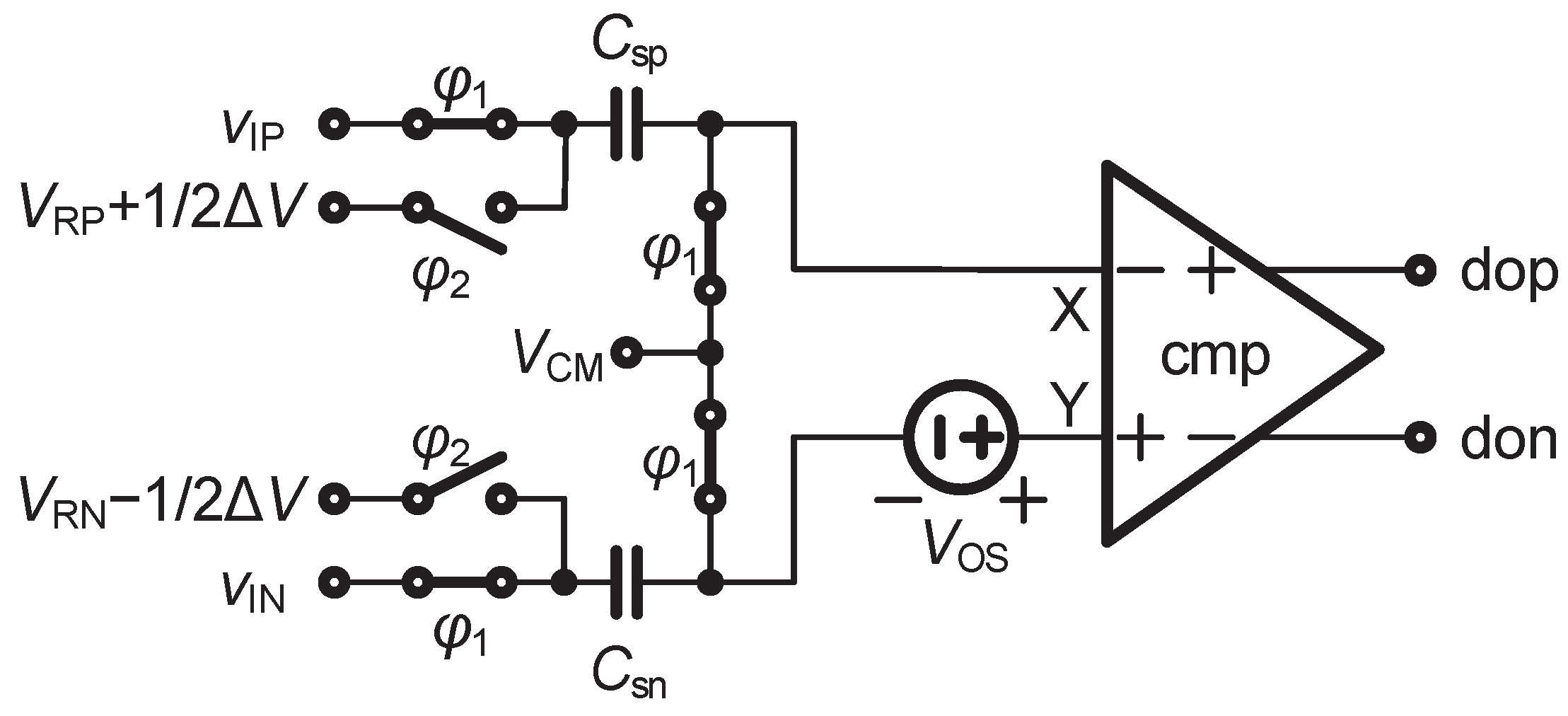

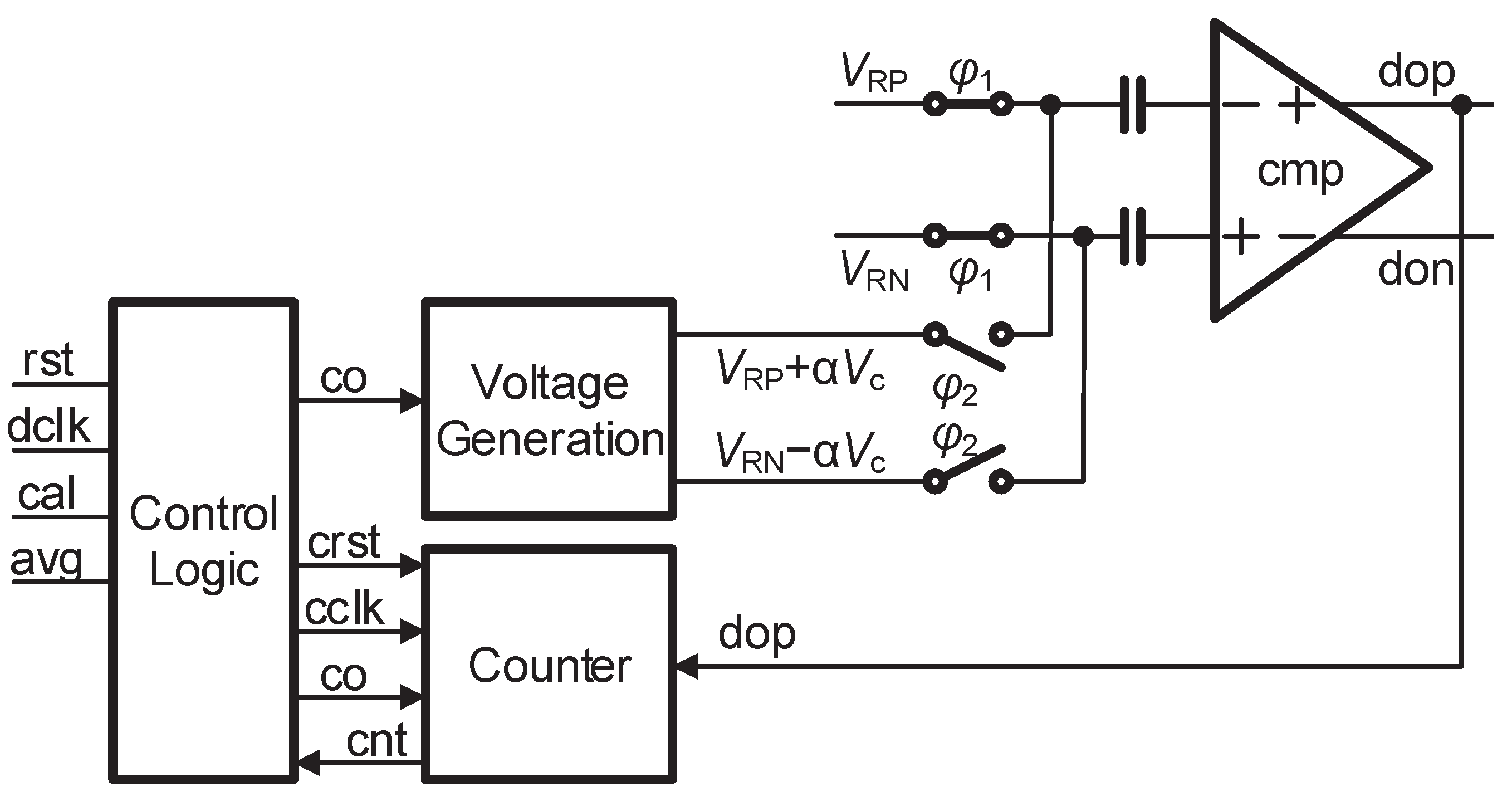

3.2. Proposed Reference-Compensated Offset Calibration Technique

4. Results

5. Conclusions

Author Contributions

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Gonen, B.; Sebastiano, F.; Quan, R.; et al. A Dynamic Zoom ADC With 109-dB DR for Audio Applications. IEEE Journal of Solid-State Circuits 2017, 52, 1542–1550. [Google Scholar] [CrossRef]

- Hurrell, C. P.; Lyden, C.; Laing, D.; et al. An 18 b 12.5 MS/s ADC With 93 dB SNR. IEEE Journal of Solid-State Circuits 2010, 45, 2647–2654. [Google Scholar] [CrossRef]

- Maddox, M.; Chen, B.; Coln, M.; et al. A 16 bit linear passive-charge-sharing SAR ADC in 55nm CMOS. In Proceedings of the 2016 IEEE Asian Solid-State Circuits Conference (A-SSCC), Toyama, Japan, 2016; pp. 153–156. [Google Scholar]

- Bindra, H. S.; Lokin, C. E.; Schinkel, D.; et al. A 1.2-V Dynamic Bias Latch-Type Comparator in 65-nm CMOS With 0.4-mV Input Noise. IEEE Journal of Solid-State Circuits 2018, 53, 1902–1912. [Google Scholar] [CrossRef]

- Tang, X.; Liu, J.; Shen, Y.; et al. Low-Power SAR ADC Design: Overview and Survey of State-of-the-Art Techniques. IEEE Transactions on Circuits and Systems I: Regular Papers 2018, 69, 2249–2262. [Google Scholar] [CrossRef]

- Wang, T. -Y.; Li, H. -Y.; Ma, Z. -Y.; et al. A Bypass-Switching SAR ADC With a Dynamic Proximity Comparator for Biomedical Applications. IEEE Journal of Solid-State Circuits 2018, 53, 1743–1754. [Google Scholar] [CrossRef]

- Razavi, B. Charge steering: A low-power design paradigm. In Proceedings of the IEEE 2013 Custom Integrated Circuits Conference, San Jose, CA, USA, 2013; pp. 1–8. [Google Scholar]

- Nikolic, B.; Oklobdzija, V. G.; Stojanovic, V.; et al. Improved sense-amplifier-based flip-flop: design and measurements. IEEE Journal of Solid-State Circuits 2000, 35, 876–884. [Google Scholar] [CrossRef]

- Wong, K.. -L. J.; Yang, C.. -K. K. Offset compensation in comparators with minimum input-referred supply noise. IEEE Journal of Solid-State Circuits 2004, 39, 837–840. [Google Scholar] [CrossRef]

- Wicht, B.; Nirschl, T.; Schmitt-Landsiedel, D. Yield and speed optimization of a latch-type voltage sense amplifier. IEEE Journal of Solid-State Circuits 2004, 39, 1148–1158. [Google Scholar] [CrossRef]

- Kong, L.; Lu, Y.; Alon, E. A multi-GHz area-efficient comparator with dynamic offset cancellation. In Proceedings of the 2011 IEEE Custom Integrated Circuits Conference (CICC), San Jose, CA, USA, 2011; pp. 1–4. [Google Scholar]

- van Elzakker, M.; van Tuijl, E.; Geraedts, P.; et al. A 10-bit Charge-Redistribution ADC Consuming 1.9 μW at 1 MS/s. IEEE Journal of Solid-State Circuits 2010, 45, 1007–1015. [Google Scholar] [CrossRef]

- Schinkel, D.; Mensink, E.; Klumperink, E.; et al. A Double-Tail Latch-Type Voltage Sense Amplifier with 18ps Setup+Hold Time. In Proceedings of the 2007 IEEE International Solid-State Circuits Conference. Digest of Technical Papers, San Francisco, CA, USA, 2007; pp. 314–605. [Google Scholar]

- Tang, J.; Wang, Y.; Gu, H.; Zou, W. Design of Self-Calibration Comparator for 12-Bit SAR ADCs. Electronics 2023, 12, 2277. [Google Scholar] [CrossRef]

- Xu, H.; Abidi, A. A. Analysis and Design of Regenerative Comparators for Low Offset and Noise. IEEE Transactions on Circuits and Systems I: Regular Papers 2019, 66, 2817–2830. [Google Scholar] [CrossRef]

- Razavi, B. Analysis and Design of Data Converters. In Cambridge University Press; 2025; pp. 91–92. [Google Scholar]

- Kinget, P.; Steyaert, M. Impact of transistor mismatch on the speed-accuracy-power trade-off of analog CMOS circuits. Proceedings of Custom Integrated Circuits Conference, San Diego, CA, USA, 1996; pp. 333–336. [Google Scholar]

- Pelgrom, M. J. M.; Duinmaijer, A. C. J.; Welbers, A. P. G. Matching properties of MOS transistors. IEEE Journal of Solid-State Circuits 1989, 24, 1433–1439. [Google Scholar] [CrossRef]

- Pelgrom, M. J. M.; Tuinhout, H. P.; Vertregt, M. Transistor matching in analog CMOS applications. Proceedings of International Electron Devices Meeting 1998. Technical Digest (Cat. No.98CH36217), San Francisco, CA, USA, 1998; pp. 915–918. [Google Scholar]

- Van der Plas, G.; Decoutere, S.; Donnay, S. A 0.16pJ/Conversion-Step 2.5mW 1.25GS/s 4b ADC in a 90nm Digital CMOS Process. In Proceedings of the 2006 IEEE International Solid State Circuits Conference - Digest of Technical Papers, San Francisco, CA, USA, 2006; p. pp. 2310. [Google Scholar]

- Jung, H.; Youn, E.; Jang, Y.-C. An 11-Bit 10 MS/s SAR ADC with C–R DAC Calibration and Comparator Offset Calibration. Electronics 2022, 11, 3654. [Google Scholar] [CrossRef]

- Lu, J.; Holleman, J. A Low-Power High-Precision Comparator With Time-Domain Bulk-Tuned Offset Cancellation. IEEE Transactions on Circuits and Systems I: Regular Papers 2013, 24, 1158–1167. [Google Scholar] [CrossRef]

- Xu, D.; Xu, S.; Chen, G. High-Speed and Low-Power Supply Voltage Dynamic Comparator. Electronics Letters 2015, 51, 1914–1916. [Google Scholar] [CrossRef]

- Babayan-Mashhadi, S.; Lotfi, R. Analysis and Design of a Low-Voltage Low-Power Double-Tail Comparator. IEEE Transactions on Very Large Scale Integration Systems 2014, 22, 343–352. [Google Scholar] [CrossRef]

- Wang, Y.; Yao, M.; Guo, B.; et al. A Low-Power High-Speed Dynamic Comparator with a Transconductance-Enhanced Latching Stage. IEEE Access 2019, 7, 93396–93403. [Google Scholar] [CrossRef]

- Yaqubi, E.; Zahiri, S. H. Optimum Design of a Double-Tail Latch Comparator on Power, Speed, Offset and Size. Analog Circ Sig Process 2017, 90, 309–319. [Google Scholar] [CrossRef]

| This Work | [23] | [24] | [25] | [26] | ||

|---|---|---|---|---|---|---|

| Technology (nm) | 180 | 180 | 180 | 180 | 180 | |

| Supply voltage (V) | 1.8 | 1.2 | 1.2 | 1.8 | 1.8 | |

| Operating frequency (MHz) | 150 | 2150 | 2000 | 500 | 1600 | |

| Delay time (ps) | 190.3 | 550 | 268.6 | 300 | 761 | |

| Energy/comparison (fJ) | 324.2 | 560 | 112.5 | 300 | 418 | |

| Offset voltage (mV) | 6.3 | 7.8 | 7.3 | 2.4 | 3.67 | |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2026 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).