Submitted:

03 January 2026

Posted:

05 January 2026

You are already at the latest version

Abstract

Keywords:

1. Introduction

2. Related Works

2.1. Motivation for Taylor-Series-Based Floating-Point Arithmetic

2.2. Mantissa Region Division Technique

2.3. Balancing LUT Size and Arithmetic Complexity

2.4. Comparative Analysis and Hardware Trade-Offs

- LUT size vs. arithmetic operations: Larger LUTs reduce polynomial order but increase memory usage.

- Number of segments vs. approximation error: Finer segmentation improves accuracy but requires more comparators and control logic.

- Multiplier complexity vs. latency: Higher-order polynomials need more multipliers but may reduce iteration counts.

3. Preparation

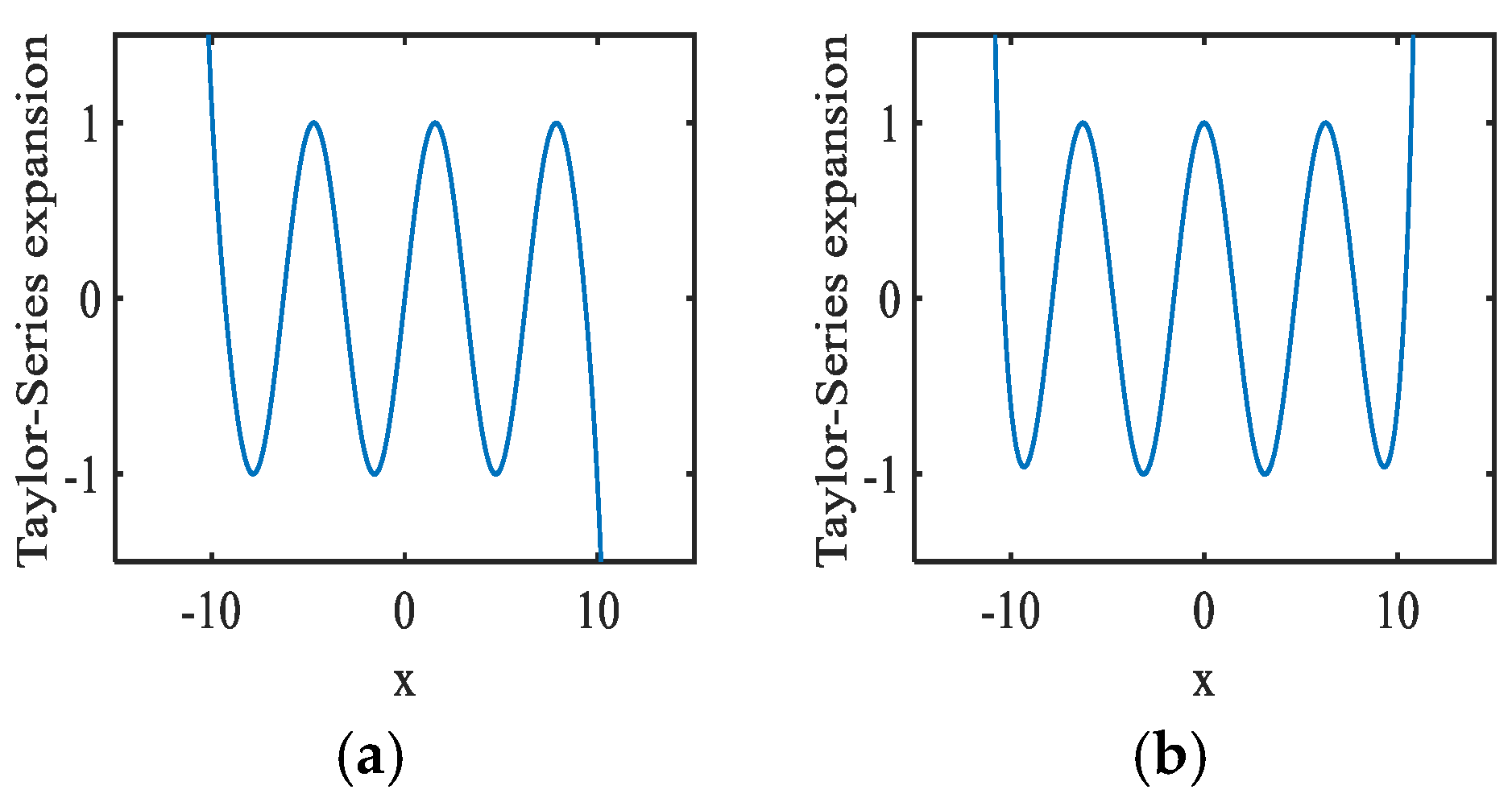

3.1. Taylor Series Expansion

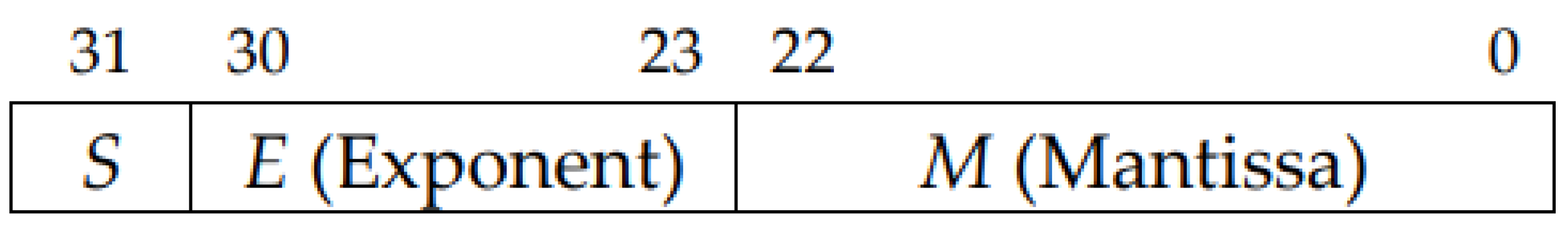

3.2. Representation of Floating-point Numbers

3.3. Mantissa Division Method for Taylor Series Expansion

3.3.1. One Mantissa Region for Taylor-Series Expansion

3.3.2. Division by 2 of Mantissa Region 1≤x<2

3.3.3. Division by 4 of Mantissa Region 1 ≤ x < 2

3.3.4. Division by 8 of Mantissa Region 1≤x<2

4. Division Algorithm Using Taylor Series Expansion

4.1. Introduction

4.2. Problem Formulation

4.3. Reciprocal Calculation by Taylor-Series Expansion

4.4. Numerical Simulation Results

4.4.1. One Mantissa Region of

4.4.2. Division by 2 of Mantissa Region

4.4.3. Division by 4 of Mantissa Region

4.5. Hardware Implementation Consideration

4.5.1. SRequired Numbers of Multiplications/Additions/ Subtractions for Taylor-Series Expansion

4.5.3. LUT Contents and Size

4.6. Summary of Division Algorithm Part

5. Inverse Square Root Algorithm Using Taylor Series Expansion

5.1. Introduction

5.2. Representation and Computation of Floating-Point Inverse Square Roots

5.3. Taylor-Series Expansion of Inverse Square Root

5.4. Number Simulation Results

5.4.1. One Mantissa Region of (Table 1)

5.4.2. Division by 2 of Mantissa Region

5.4.3. Division by 4 of Mantissa Region

5.5. Hardware Implementation Consideration

5.6. Summary of Inverter Square Root Algorithm Part

6. Square Root Algorithm Using Taylor Series Expansion

6.1. Introduction

6.2. Problem Formulation

6.3. Taylor-Series Expansion of Square Root

6.4. Numerical Simulation Results

6.4.1. One Mantissa Region of (Table 1)

6.4.2. Division by 2 of Mantissa Region

6.4.3. Division by 4 of Mantissa Region

6.5. Hardware Implementation Consideration

6.6. Summary of Square Root Algorithm Part

7. Exponentiation Algorithm Using Taylor Series Expansion

7.1. Introduction

7.2. Problem Formulation

7.3. Taylor Series Expansion of Exponential Function

7.4. Numerical Simulation Results

7.4.1. One Mantissa Region of

7.4.2. Division by 2 of Mantissa

7.4.3. Division by 4 of Mantissa

7.5. Hardware Implementation Consideration

7.6. Summary of Exponentiation Algorithm Part

8. Logarithm Algorithm Using Taylor Series Expansion

8.1. Introduction

8.2. Problem Formulation

8.3. Taylor Series Expansion of Mantissa Part for Base-2 Logarithm

8.4. Numerical Simulation Results

8.4.1. One Mantissa Region of 1 ≤ x < 2 (Table 1)

8.4.2. Division by 2 of Mantissa Region 1 ≤ x <2

8.5. Hardware Implementation Consideration

8.6. Summary of Logarithm Algorithm Part

9. Discussion

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- IEEE Computer Society. IEEE Standard for Floating-Point Arithmetic (IEEE Std 754-2019). IEEE: Piscataway, NJ, USA, 2019.

- Muller, J.M.; Brunie, N.; De Dinechin, F.D.; Jeannerod, C.-P.; Joldes, M.; Lefèvre, V.; Melquiond, G.; Revol, N.; Torres Serge, S. Handbook of Floating-Point Arithmetic[M]; Birkhäuser: Basel, Switzerland, 2018. [Google Scholar]

- Koren, I. Computer Arithmetic Algorithms, 2nd ed.; A K Peters/CRC Press: Natick, MA, USA, 2001. [Google Scholar]

- Chen, C.; Li, Z.; Zhang, Y.; Zhang, S.; Hou, J.; Zhang, H. Low-Power FPGA Implementation of Convolution Neural Network Accelerator for Pulse Waveform Classification. Algorithms 2020, 13, 213. [Google Scholar] [CrossRef]

- Lin, J.; Li, Y. Efficient Floating-Point Implementation of Model Predictive Control on an Embedded FPGA. IEEE Transactions on Control Systems Technology 2021, 29, 1473–1486. [Google Scholar]

- Chen, C.; Li, Z.; Zhang, Y.; Zhang, S.; Hou, J.; Zhang, H. A 3D Wrist Pulse Signal Acquisition System for Width Information of Pulse Wave. Sensors 2020, 20, 11. [Google Scholar] [CrossRef] [PubMed]

- Zhou, J.; Liu, Z.; Song, X. Constructing High-Radix Quotient Digit Selection Tables for SRT Division and Square Root. IEEE Transactions on Computers 2023, 72, 987–1001. [Google Scholar]

- Wang, X.; Yu, Z.; Gao, B.; Wu, H. An In-Memory Computing Architecture Based on a Duplex Two-Dimensional Material Structure for In-Situ Machine Learning. Nature Nanotechnology 2023, 18, 456–465. [Google Scholar]

- Kwon, T.J.; Draper, J. Floating-Point Division and Square Root Using a Taylor-series Expansion Algorithm. Microelectronics Journal 2009, 40, 1601–1605. [Google Scholar] [CrossRef]

- Muñoz, D.M.; Sánchez, D.F.; Llanos, C.H.; Ayala-Rincon, M. Tradeoff of FPGA design of a floating-point library for arithmetic operators. Journal of Integrated Circuits and Systems 2010, 5, 42–52. [Google Scholar] [CrossRef]

- Karani, R.K.; Rana, A.K.; Reshamwala, D.H.; Saldanha, K. A Floating Point Division Unit Based on Taylor-Series Expansion Algorithm and Iterative Logarithmic Multiplier. arXiv 2017, arXiv:1705.00218. [Google Scholar] [CrossRef]

- Wei, J.; Kuwana, A.; Kobayashi, H.; Kubo, K. IEEE754 Binary32 Floating-Point Logarithmic Algorithms Based on Taylor-Series Expansion with Mantissa Region Conversion and Division. In Fundamentals; IEICE , Translator; 2022; Volume E105-A, 7, pp. 1020–1027. [Google Scholar]

- Donisi, A.; Di Benedetto, L.; Liguori, R.; Licciardo, G.D.; Rubino, A. A FPGA Hardware Architecture for AZSPWM Based on a Taylor Series Decomposition. In Applications in Electronics Pervading Industry, Environment and Society. ApplePies;Lecture Notes in Electrical Engineering; Berta, R., De Gloria, A., Eds.; Springer: Cham, 2022; vol 1036. [Google Scholar]

- Vazquez-Leal, H.; Benhammouda, B.; Filobello-Nino, U.A.; Sarmiento-Reyes, A.; Jimenez-Fernandez, V.M.; Marin-Hernandez, A.; Agustin Leobardo Herrera-May, A.L.; Diaz-Sanchez, A.; Huerta-Chua, J. Modified Taylor Series Method for Solving Nonlinear Differential Equations With Mixed Boundary Conditions Defined on Finite Intervals. SpringerPlus 2014, 3, 1–7. [Google Scholar] [CrossRef] [PubMed]

- Chopde, A.; Bodas, S.; Deshmukh, V.; Bramhekar, S. Fast Inverse Square Root Using FPGA. Advancements in Communication and Systems 2024, 231–239. [Google Scholar]

- Moroz, L. V.; Samotyy, V. V.; Horyachyy, O. Y. Modified Fast Inverse Square Root and Square Root Approximation Algorithms: The Method of Switching Magic Constants. Computers 2021, 9, 21. [Google Scholar] [CrossRef]

- Li, P.; Jin, H.; Xi, W.; Xu, C.; Yao, H.; Huang, K. Reconfigurable Hardware Architecture for Miscellaneous Floating-Point Transcendental Functions. Electronics 2023, 12, 233. [Google Scholar] [CrossRef]

- Bandil, L.; Nagar, B.C. Hardware Implementation of Unsigned Approximate Hybrid Square Rooters for Error-Resilient Applications. IEEE Trans. Computers 2024, 73, 2734–2746. [Google Scholar]

- Kim, S.; Norris, C.J.; Oelund, J.I.; Rutenbar, R.A. Area-Efficient Iterative Logarithmic Approximate Multipliers for IEEE 754 and Posit Numbers. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 2024, 32, 455–467. [Google Scholar] [CrossRef]

- Haselman, M.; Beauchamp, M.; Wood, A.; Hauck, S.; Underwood, K.; Hemmert, K.S. A Comparison of Floating point and Logarithmic Number Systems for FPGAs. 13th Annual IEEE Symposium on Field-Programmable Custom Computing Machines (FCCM’05), 2005; pp. 181–190. [Google Scholar]

- Park, S.; Yoo, Y. A New Fast Logarithm Algorithm Using Advanced Exponent Bit Extraction for Software-based Ultrasound Imaging Systems. Electronics 2022, 12, 170. [Google Scholar] [CrossRef]

- Palomäki, K.I.; Nurmi, J. Taylor Series Interpolation-Based Direct Digital Frequency Synthesizer with High Memory Compression Ratio. Sensors 2025, 25, 2403. [Google Scholar] [CrossRef] [PubMed]

- Gustafsson, O.; Hellman, N. Approximate Floating-Point Operations With Integer Units by Processing in the Logarithmic Domain. IEEE 28th Symposium on Computer Arithmetic (ARITH), 2021 ; pp. 45–52. [Google Scholar]

- Kim, S.Y.; Kim, C.H.; Lee, W.J.; Park, I.; Kim, S.W. Low-Overhead Inverted LUT Design for Bounded DNN Activation Functions on Floating-point Vector ALUs. Microprocessors and Microsystems 2022, 93, 104592. [Google Scholar] [CrossRef]

- Węgrzyn, M.; Voytusik, S.; Gavkalova, N. FPGA-based Low Latency Square Root CORDIC Algorithm. Journal of Telecommunications and Information Technology 2025, 1, 1950. [Google Scholar] [CrossRef]

- Donald, E. The Art of Computer Programming. In -3rd[J]; : Seminumerical Algorithms, 1997; Volume 2, pp. 485–515. [Google Scholar]

- Wei, J.; Kuwana, A.; Kobayashi, H.; Kubo, K. “Revisit to Floating-Point Division Algorithm Based on Taylor-Series Expansion”. The 16th IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Ha Long Bay, Vietnam, 2020. [Google Scholar]

- Wei, J.; Kuwana, A.; Kobayashi, H.; Kubo, K.; Tanaka, Y. “Floating-Point Inverse Square Root Algorithm Based on Taylor-Series Expansion”. IEEE Transactions on Circuits and Systems II: Express Briefs 2021, Vol. 68(Issue 7), 2640–2644. [Google Scholar] [CrossRef]

- Wei, J.; Kuwana, A.; Kobayashi, H.; Kubo, K.; Tanaka, Y. “Floating-Point Square Root Calculation Algorithm Based on Taylor-Series Expansion and Region Division”. IEEE 64th International Midwest Symposium on Circuits and Systems (MWSCAS2021), Fully Virtual and On-line, 2021. [Google Scholar]

- Wei, J.; Kuwana, A.; Kobayashi, H.; Kubo, K. Divide and Conquer: Floating-Point Exponential Calculation Based on Taylor-Series Expansion. IEEE 14th International Conference on ASIC (ASICON 2021), On-Line Virtual, 2021. [Google Scholar]

| Number | Mantissa Region | Center value a |

|---|---|---|

| R1-1 | M = 1.xxxxxx (1.0 ≤ M < 2.0) | 1.5 |

| Number | Mantissa Region | Center value a |

|---|---|---|

| R2-1 | M = 1.0xxxxx… (1.0 ≤ M < 1.5) | 1.25 |

| R2-2 | M = 1.1xxxxx… (1.5 ≤ M < 2.0) | 1.75 |

| Number | Mantissa Region | Center value a |

|---|---|---|

| R4-1 | M = 1.00xxxxx… (1.00 ≤ M < 1.25) | 1.125 |

| R4-2 | M = 1.01xxxxx… (1.25 ≤ M < 1.50) | 1.375 |

| R4-3 | M = 1.10xxxxx… (1.50 ≤ M < 1.75) | 1.625 |

| R4-4 | M = 1.11xxxxx… (1.75 ≤ M < 2.00) | 1.875 |

| Number | Mantissa Region | Center value a |

|---|---|---|

| R8-1 | M = 1.000xxxx… (1.000 ≤ M < 1.125) | 1.0625 |

| R8-2 | M = 1.001xxxx… (1.125 ≤ M < 1.250) | 1.1875 |

| R8-3 | M = 1.010xxxx… (1.250 ≤ M < 1.375) | 1.3125 |

| R8-4 | M = 1.011xxxx… (1.375 ≤ M < 1.500) | 1.4375 |

| R8-5 | M = 1.100xxxx… (1.500 ≤ M < 1.625) | 1.5625 |

| R8-6 | M = 1.101xxxx… (1.625 ≤ M < 1.750) | 1.6875 |

| R8-7 | M = 1.110xxxx… (1.750 ≤ M < 1.875) | 1.8125 |

| R8-8 | M = 1.111xxxx… (1.875 ≤ M < 2.000) | 1.9375 |

| Accuracy |

||||||

|---|---|---|---|---|---|---|

| Taylor-series Expansion Region |

||||||

| R1-1 | 6 | 11 | 13 | 16 | 21 | |

| Accuracy |

||||||

| Taylor-series Expansion Region |

||||||

| R2-1 | 4 | 7 | 9 | 11 | 14 | |

| R2-2 | 3 | 6 | 8 | 9 | 12 | |

| Accuracy |

||||||

|---|---|---|---|---|---|---|

| Taylor-series Expansion Region |

||||||

| R4-1 | 3 | 6 | 7 | 8 | 11 | |

| R4-2 | 3 | 5 | 6 | 7 | 10 | |

| R4-3 | 3 | 5 | 6 | 7 | 9 | |

| R4-4 | 3 | 5 | 6 | 7 | 9 | |

| Accuracy |

||||||

|---|---|---|---|---|---|---|

| Taylor-series Expansion Region |

||||||

| R8-1 | 2 | 4 | 5 | 6 | 8 | |

| R8-2 | 2 | 4 | 5 | 6 | 8 | |

| R8-3 | 2 | 4 | 5 | 6 | 8 | |

| R8-4 | 2 | 4 | 5 | 6 | 8 | |

| R8-5 | 2 | 4 | 5 | 6 | 7 | |

| R8-6 | 2 | 4 | 5 | 6 | 7 | |

| R8-7 | 2 | 4 | 5 | 5 | 7 | |

| R8-8 | 2 | 4 | 5 | 5 | 7 | |

| # of Taylor-series expansion terms | # of multiplications | # of additions and subtractions |

|---|---|---|

| 3 | 3 | 3 |

| 4 | 4 | 4 |

| 5 | 4 | 4 |

| 6 | 5 | 5 |

| 7 | 5 | 5 |

| 8 | 6 | 6 |

| Address () | LUT data |

| 00 | Reciprocal of a = 1.125 |

| 01 | Reciprocal of a = 1.357 |

| 10 | Reciprocal of a = 1.625 |

| 11 | Reciprocal of a = 1.875 |

| Accuracy |

||||||

|---|---|---|---|---|---|---|

| Taylor-series Expansion Region |

||||||

| R1-1 | 5 | 9 | 12 | 14 | 19 | |

| Accuracy |

||||||

|---|---|---|---|---|---|---|

| Taylor-series Expansion Region |

||||||

| R2-1 | 3 | 7 | 8 | 10 | 13 | |

| R2-2 | 3 | 6 | 7 | 8 | 9 | |

| Accuracy |

||||||

|---|---|---|---|---|---|---|

| Taylor-series Expansion Region |

||||||

| R4-1 | 3 | 5 | 6 | 7 | 10 | |

| R4-2 | 2 | 5 | 6 | 7 | 9 | |

| R4-3 | 2 | 4 | 5 | 6 | 8 | |

| R4-4 | 2 | 4 | 5 | 6 | 8 | |

| Accuracy |

||||||

|---|---|---|---|---|---|---|

| Taylor-series Expansion Region |

||||||

| R8-1 | 2 | 4 | 5 | 6 | 8 | |

| R8-2 | 2 | 4 | 5 | 6 | 7 | |

| R8-3 | 2 | 4 | 5 | 6 | 7 | |

| R8-4 | 2 | 4 | 5 | 5 | 7 | |

| R8-5 | 2 | 4 | 4 | 5 | 7 | |

| R8-6 | 2 | 4 | 4 | 5 | 7 | |

| R8-7 | 2 | 3 | 4 | 5 | 7 | |

| R8-8 | 2 | 3 | 4 | 5 | 7 | |

| # of Taylor-series expansion terms | # of multiplications | # of additions and subtractions | # of LUT words for N regions |

|---|---|---|---|

| 3 | 3 | 3 | 8N |

| 4 | 4 | 4 | 10N |

| 5 | 4 | 4 | 12N |

| 6 | 5 | 5 | 14N |

| 7 | 5 | 5 | 16N |

| 8 | 6 | 6 | 18N |

| ) | LUT data |

|---|---|

| 00 |

for a = 1.125 |

| 01 |

for a = 1.357 |

| 10 |

for a = 1.625 |

| 11 |

for a = 1.875 |

| Accuracy |

||||||

|---|---|---|---|---|---|---|

| Taylor-series Expansion Region |

||||||

| R1-1 | 3 | 7 | 9 | 12 | 15 | |

| Accuracy |

||||||

|---|---|---|---|---|---|---|

| Taylor-series Expansion Region |

||||||

| R2-1 | 3 | 5 | 7 | 8 | 11 | |

| R2-2 | 2 | 5 | 6 | 7 | 10 | |

| Accuracy |

||||||

|---|---|---|---|---|---|---|

| Taylor-series Expansion Region |

||||||

| R4-1 | 2 | 4 | 5 | 6 | 9 | |

| R4-2 | 2 | 4 | 5 | 6 | 8 | |

| R4-3 | 2 | 4 | 5 | 6 | 8 | |

| R4-4 | 2 | 4 | 5 | 5 | 7 | |

| Accuracy |

||||||

|---|---|---|---|---|---|---|

| Taylor-series Expansion Region |

||||||

| R8-1 | 2 | 3 | 4 | 5 | 7 | |

| R8-2 | 2 | 3 | 4 | 5 | 7 | |

| R8-3 | 2 | 3 | 4 | 5 | 7 | |

| R8-4 | 2 | 3 | 4 | 5 | 6 | |

| R8-5 | 2 | 3 | 4 | 5 | 6 | |

| R8-6 | 2 | 3 | 4 | 5 | 6 | |

| R8-7 | 2 | 3 | 4 | 4 | 6 | |

| R8-8 | 2 | 3 | 4 | 4 | 6 | |

| # of Taylor-series expansion terms | # of multiplications | # of additions and subtractions |

|---|---|---|

| 3 | 3 | 3 |

| 4 | 4 | 4 |

| 5 | 5 | 5 |

| 6 | 6 | 6 |

| 7 | 7 | 7 |

| 8 | 8 | 8 |

| ) | LUT data |

|---|---|

| 00 |

for a = 1.125 |

| 01 |

for a = 1.357 |

| 10 |

for a = 1.625 |

| 11 |

for a = 1.875 |

| Accuracy |

||||||

|---|---|---|---|---|---|---|

| Taylor-series Expansion Region |

||||||

| R1-1 | 4 | 7 | 8 | 9 | 11 | |

| Accuracy |

||||||

|---|---|---|---|---|---|---|

| Taylor-series Expansion Region |

||||||

| R2-1 | 3 | 5 | 6 | 7 | 9 | |

| R2-2 | 3 | 5 | 6 | 7 | 9 | |

| Accuracy |

||||||

|---|---|---|---|---|---|---|

| Taylor-series Expansion Region |

||||||

| R4-1 | 3 | 4 | 5 | 5 | 7 | |

| R4-2 | 3 | 4 | 5 | 5 | 7 | |

| R4-3 | 3 | 4 | 5 | 5 | 7 | |

| R4-4 | 3 | 4 | 5 | 5 | 7 | |

| # of Taylor-series expansion terms | # of multiplications | # of additions and subtractions |

|---|---|---|

| 3 | 3 | 3 |

| 4 | 4 | 4 |

| 5 | 5 | 5 |

| 6 | 6 | 6 |

| 7 | 7 | 7 |

| 8 | 8 | 8 |

| (αβ) | LUT data |

|---|---|

| 00 | Exp(a) for a = 1.125 |

| 01 | Exp(a) for a = 1.357 |

| 10 | Exp(a) for a = 1.625 |

| 11 | Exp(a) for a = 1.875 |

| Accuracy |

||||||

|---|---|---|---|---|---|---|

| Taylor-series Expansion Region |

||||||

| R1-1 | 13 | 15 | 18 | 22 | 23 | |

| Accuracy |

||||||

|---|---|---|---|---|---|---|

| Taylor-series Expansion Region |

||||||

| R2-1 | 10 | 11 | 13 | 16 | 16 | |

| R2-2 | 4 | 5 | 7 | 9 | 10 | |

| Accuracy |

||||||

|---|---|---|---|---|---|---|

| Taylor-series Expansion Region |

||||||

| R4-1 | 8 | 8 | 10 | 12 | 12 | |

| R4-2 | 4 | 5 | 6 | 8 | 8 | |

| R4-3 | 4 | 4 | 6 | 7 | 8 | |

| R4-4 | 4 | 4 | 5 | 7 | 7 | |

| # of Taylor-series expansion terms | # of multiplications | # of additions and subtractions |

|---|---|---|

| 3 | 3 | 3 |

| 4 | 4 | 4 |

| 5 | 5 | 5 |

| 6 | 6 | 6 |

| 7 | 7 | 7 |

| 8 | 8 | 8 |

| (αβ) | LUT data |

|---|---|

| 00 |

for a = 1.125 |

| 01 |

for a = 1.357 |

| 10 |

for a = 1.625 |

| 11 |

for a = 1.875 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2026 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).