Submitted:

12 December 2025

Posted:

16 December 2025

You are already at the latest version

Abstract

Keywords:

1. Introduction

2. Materials and Methods

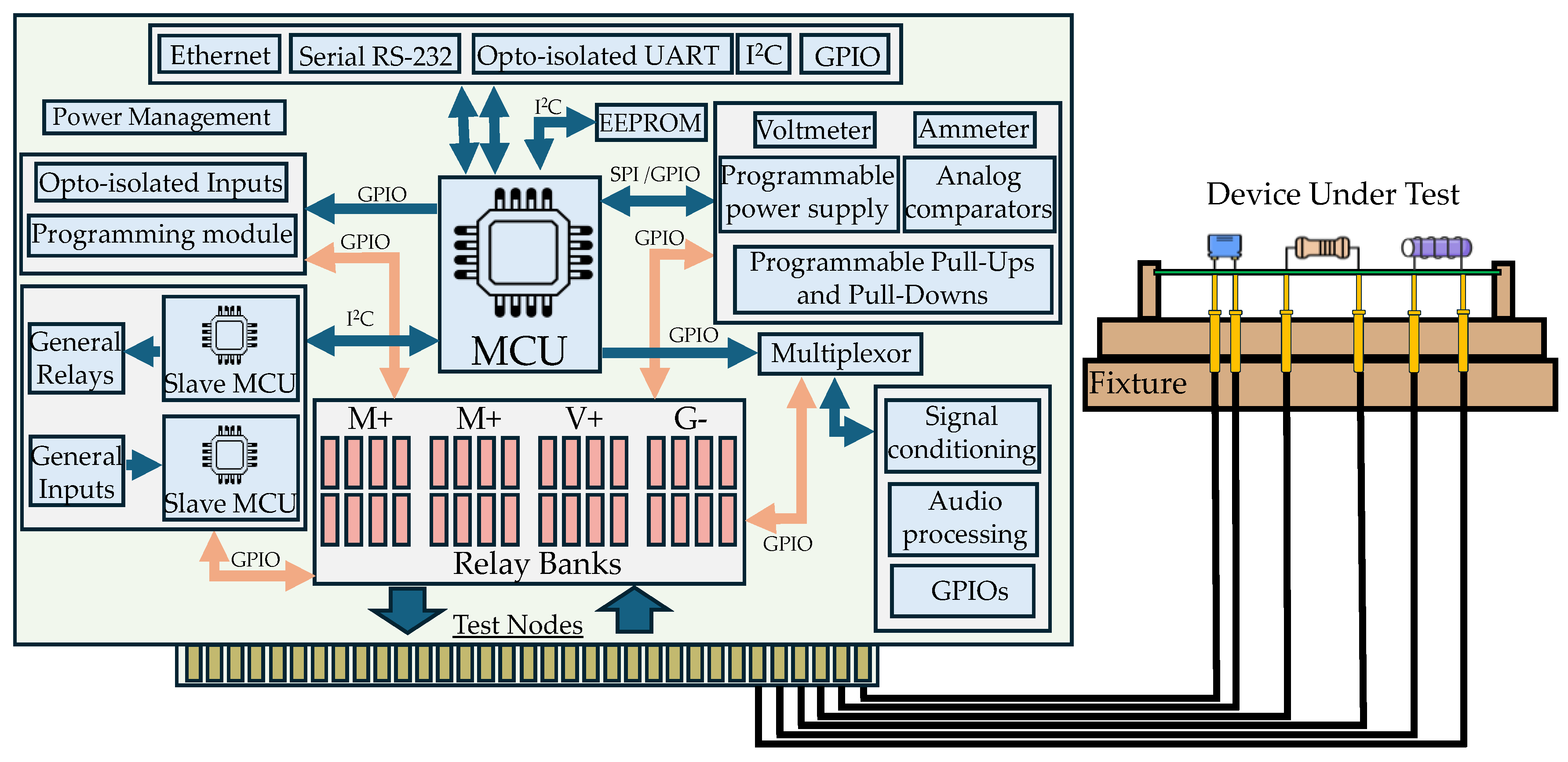

2.1. Design Overview

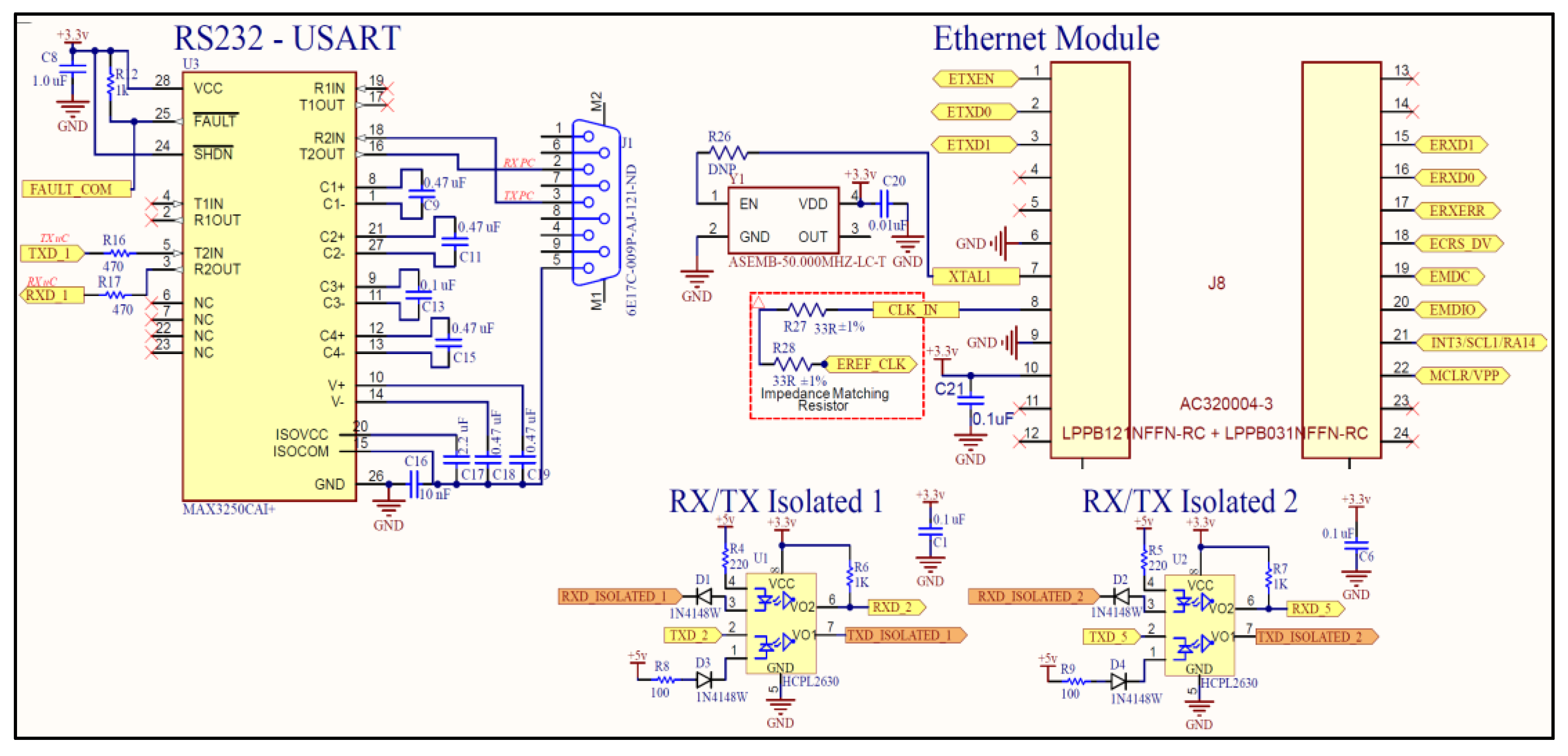

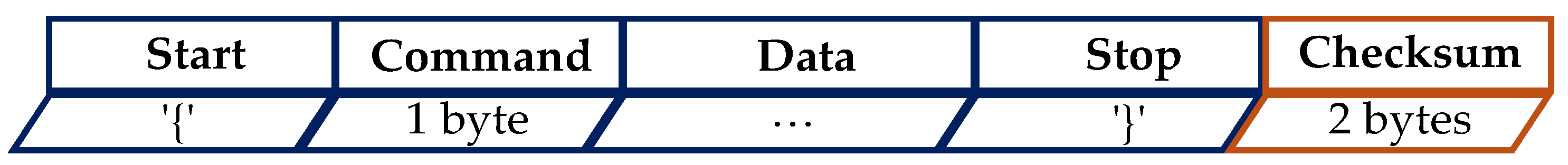

2.1.1. Communication Approach

- 0 × 01: Start an automated testing task.

- 0 × 02: Send data limits.

- 0 × 03: Request data results.

- 0 × 21: Write general relays

- 0 × 22: Read general inputs

- 0 × 50 to 0xAF: Start individual testing tasks.

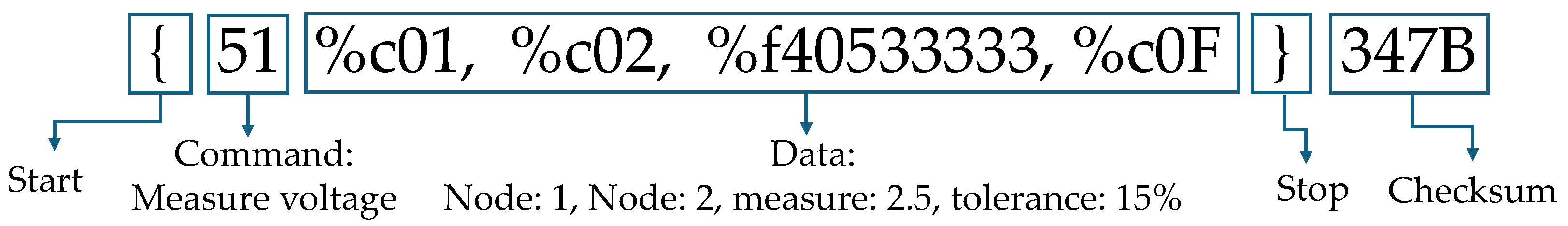

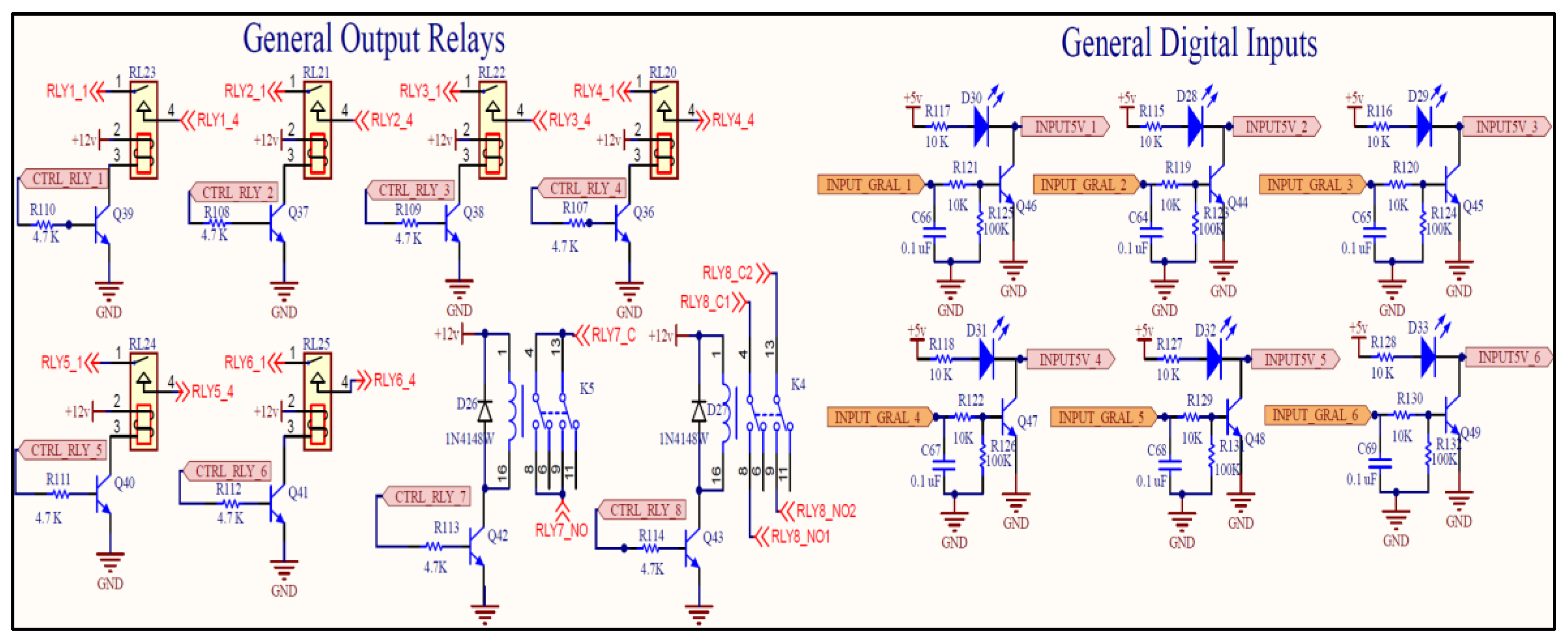

2.1.2. Relay Banks

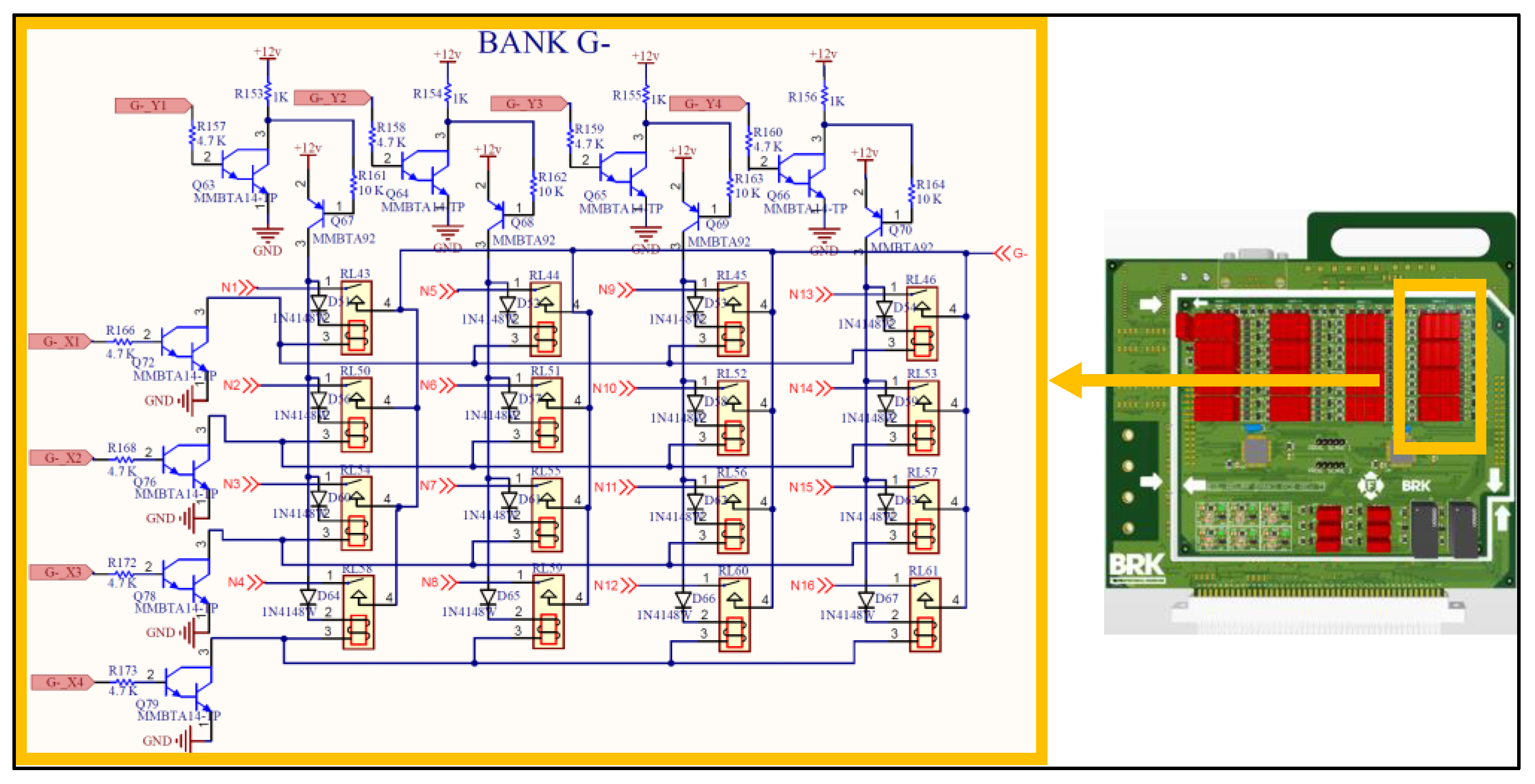

2.1.3. Programmable Power Supplies

- DAQ_1: A high-accuracy, stability, and precision analog voltage capable of setting a high-current power supply (VDUT) from 0 V to 10 V through a pre-regulator circuitry and overcurrent protection circuitry, current is controlled and monitored by the main MCU. This power supply can be connected to the V+ bus and serves as the primary voltage stimulus source for the DUT.

- DMM_Supply: A high-current power supply from 0 V to 10 V via a pre-regulator circuitry able to be connected to the M+ bus for general voltage stimuli for testing tasks.

- CROSS_REF_VOLT: An analog voltage that can be set as a reference voltage for analog comparators, pull-ups, and speed-up circuitry in M+ and M- buses.

- CURRENT_PROG: An analog voltage used to set an analog current limit in the overcurrent protection circuitry in the DAQ_1.

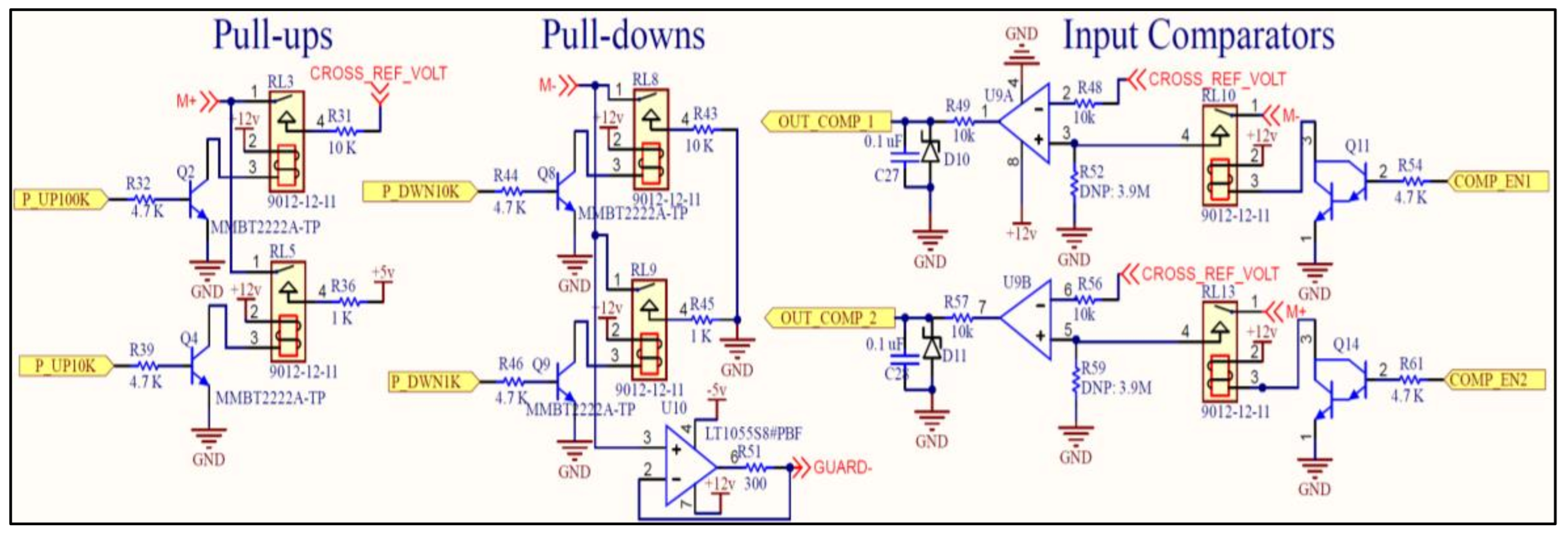

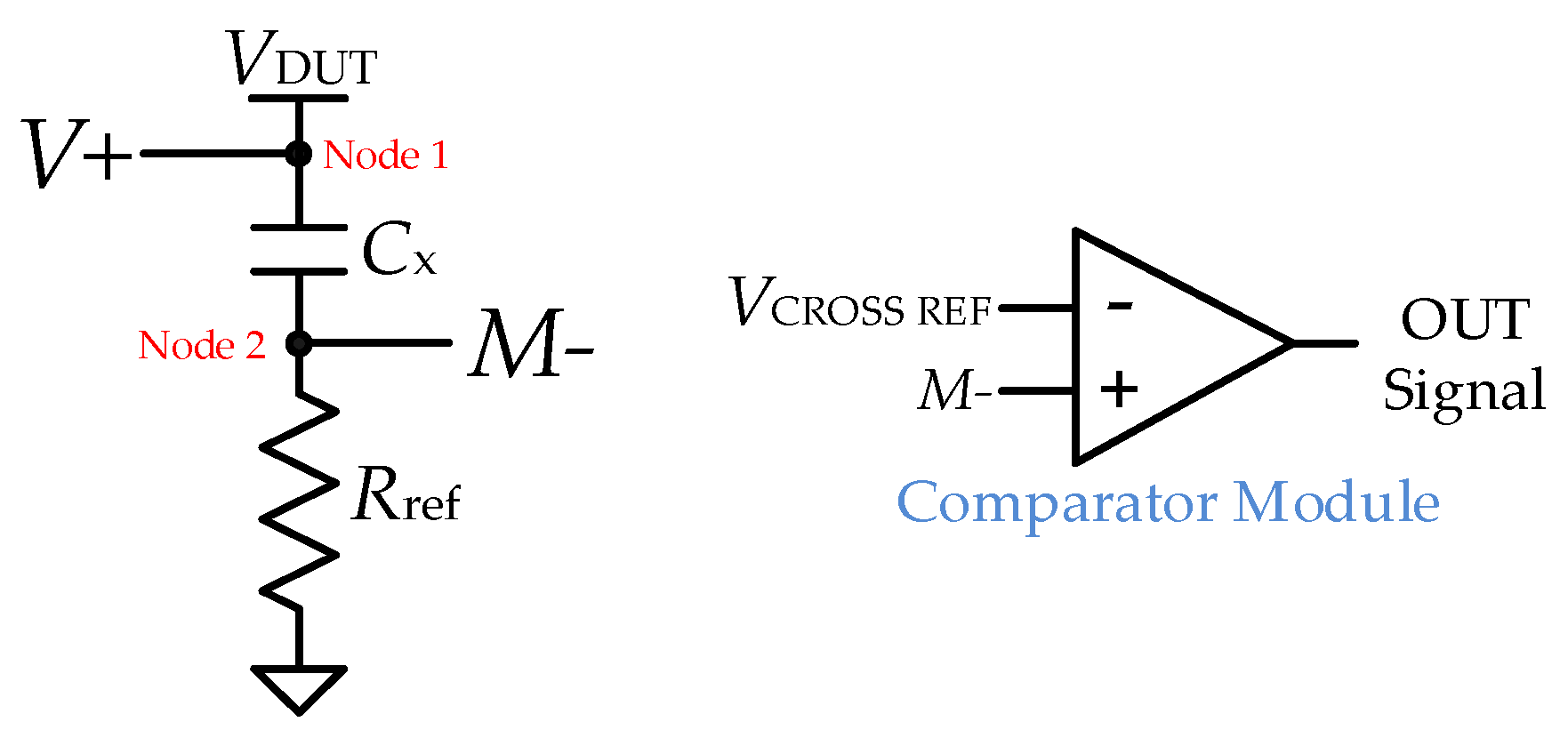

2.1.4. Programmable Pull-Ups, Pull-Downs, and Analog Comparators

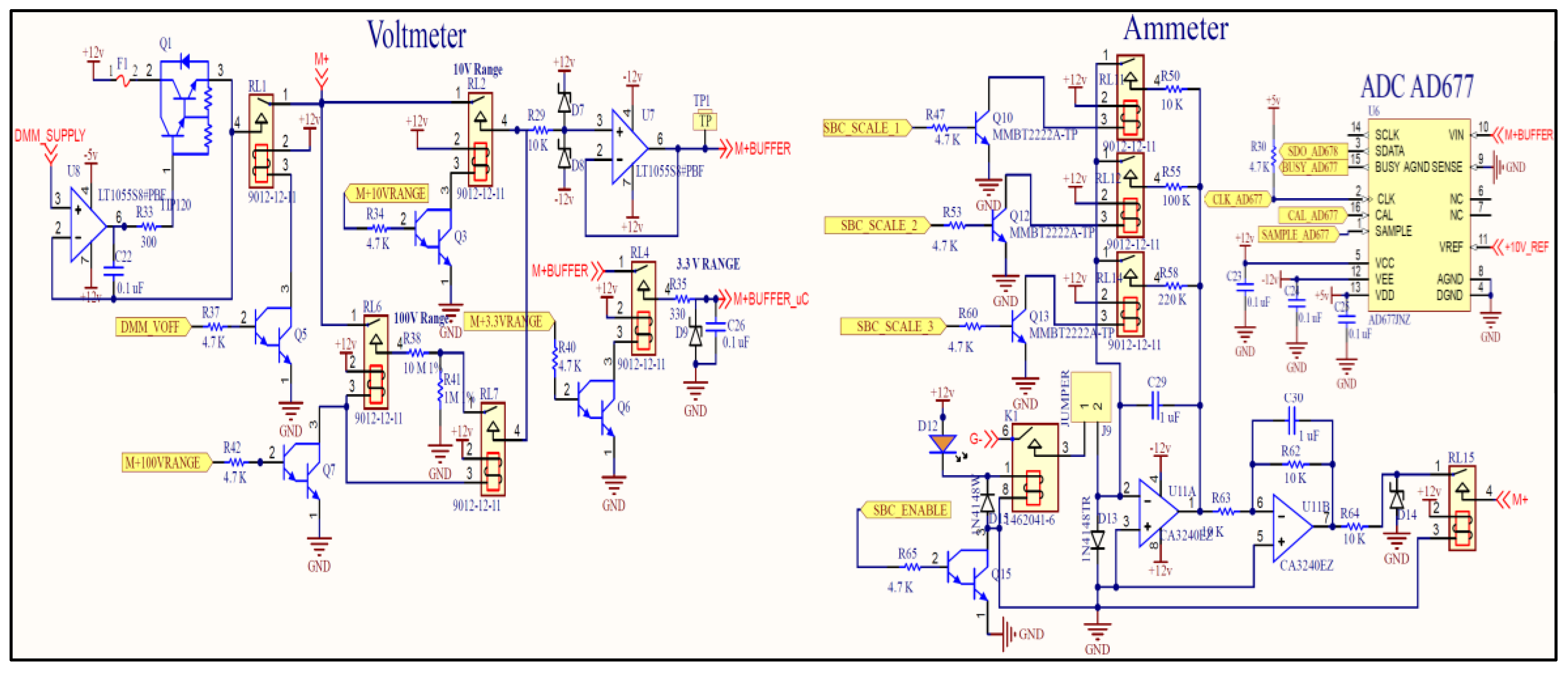

2.1.5. DMM

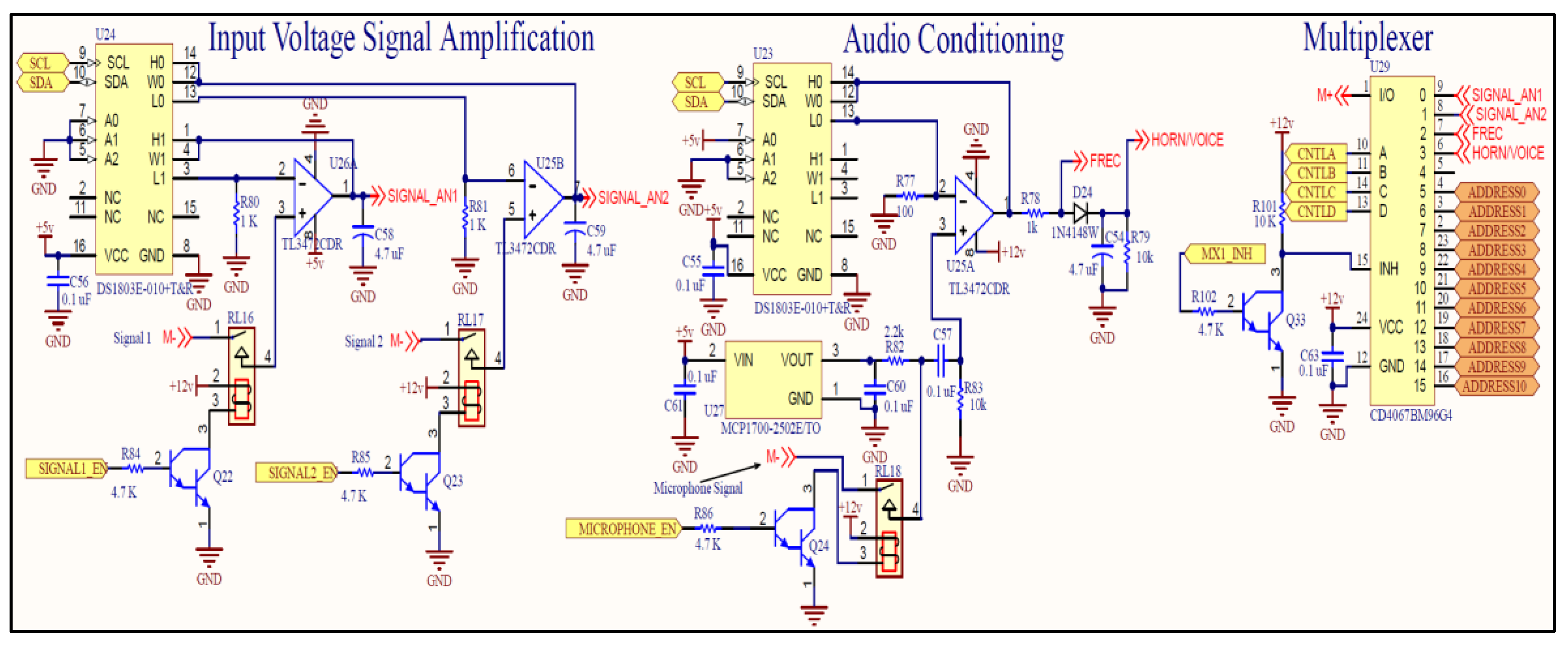

2.1.6. Signal Amplification, Audio Conditioning, and Multiplexing

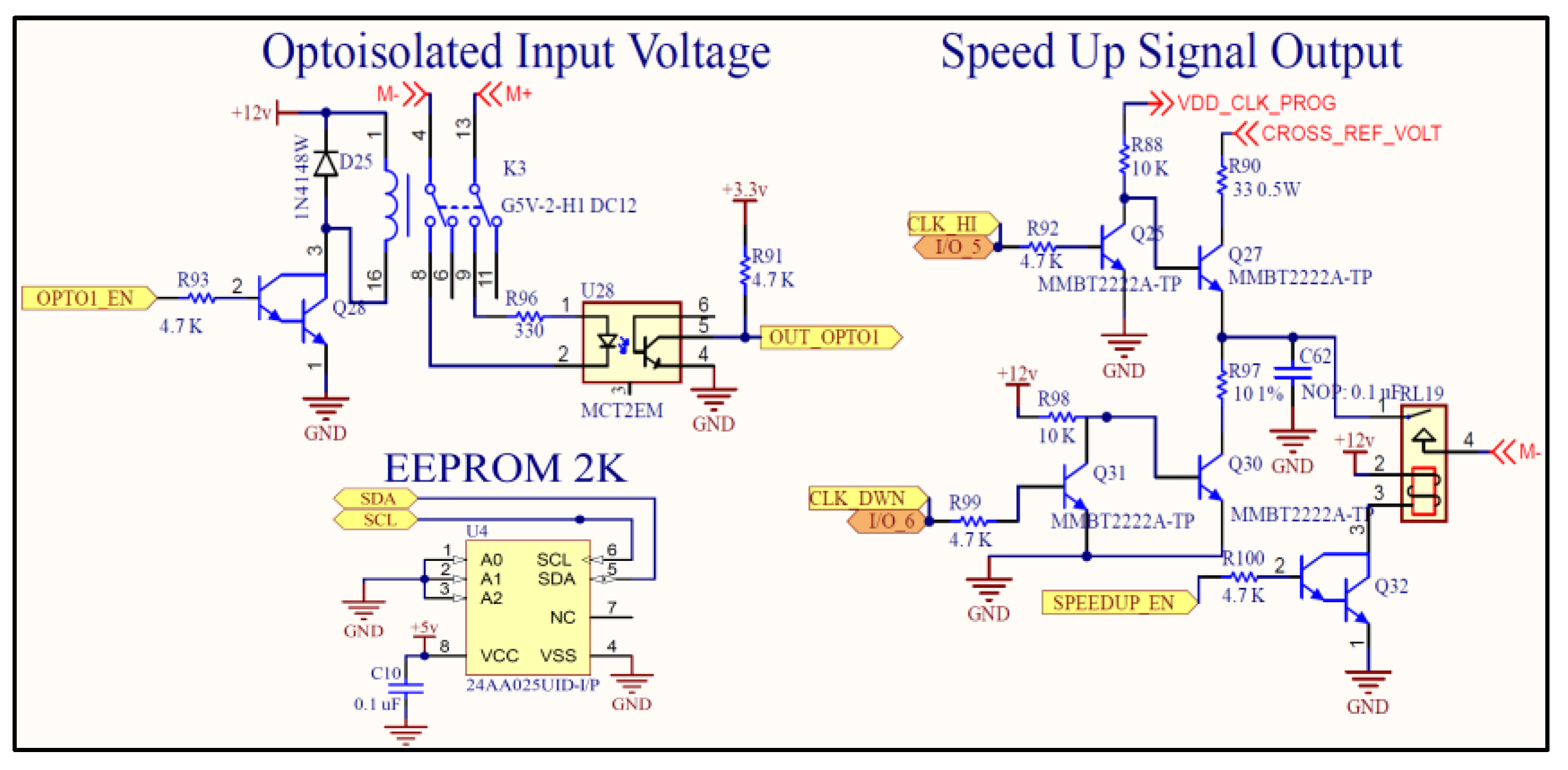

2.1.7. General Opto-Isolated Inputs, Speed-Up Signal, and EEPROM

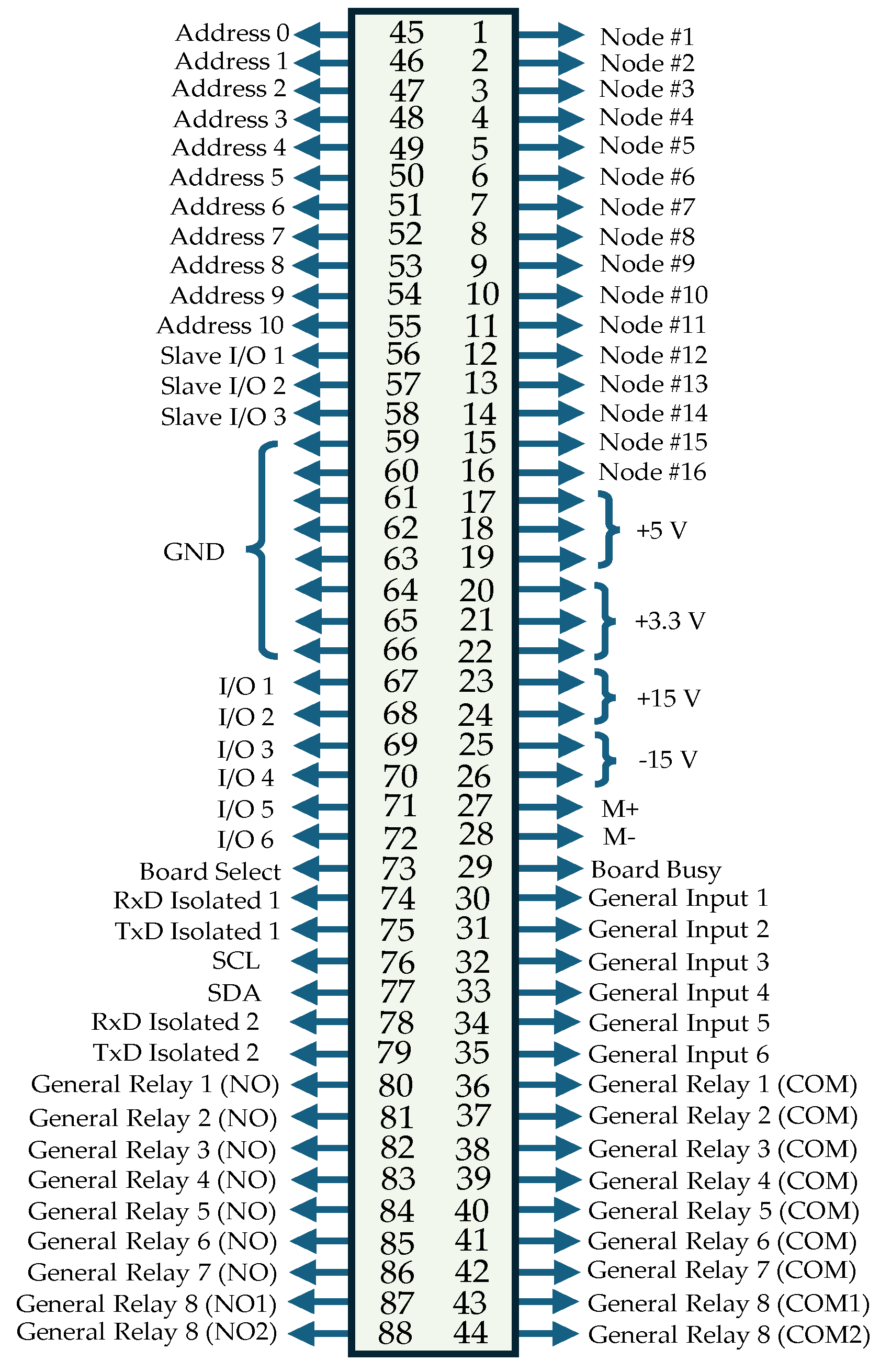

2.1.8. General-Purpose Inputs/Outputs

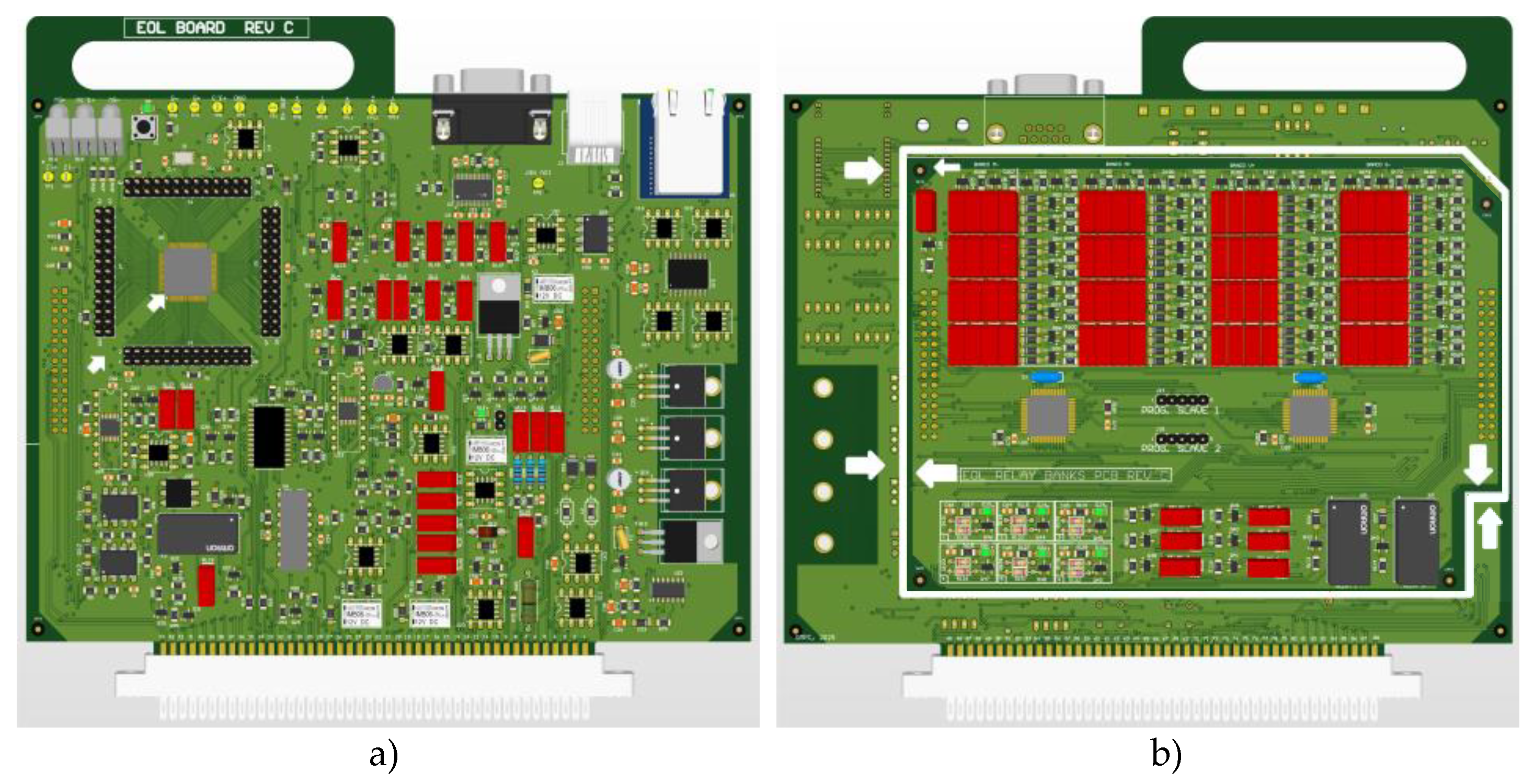

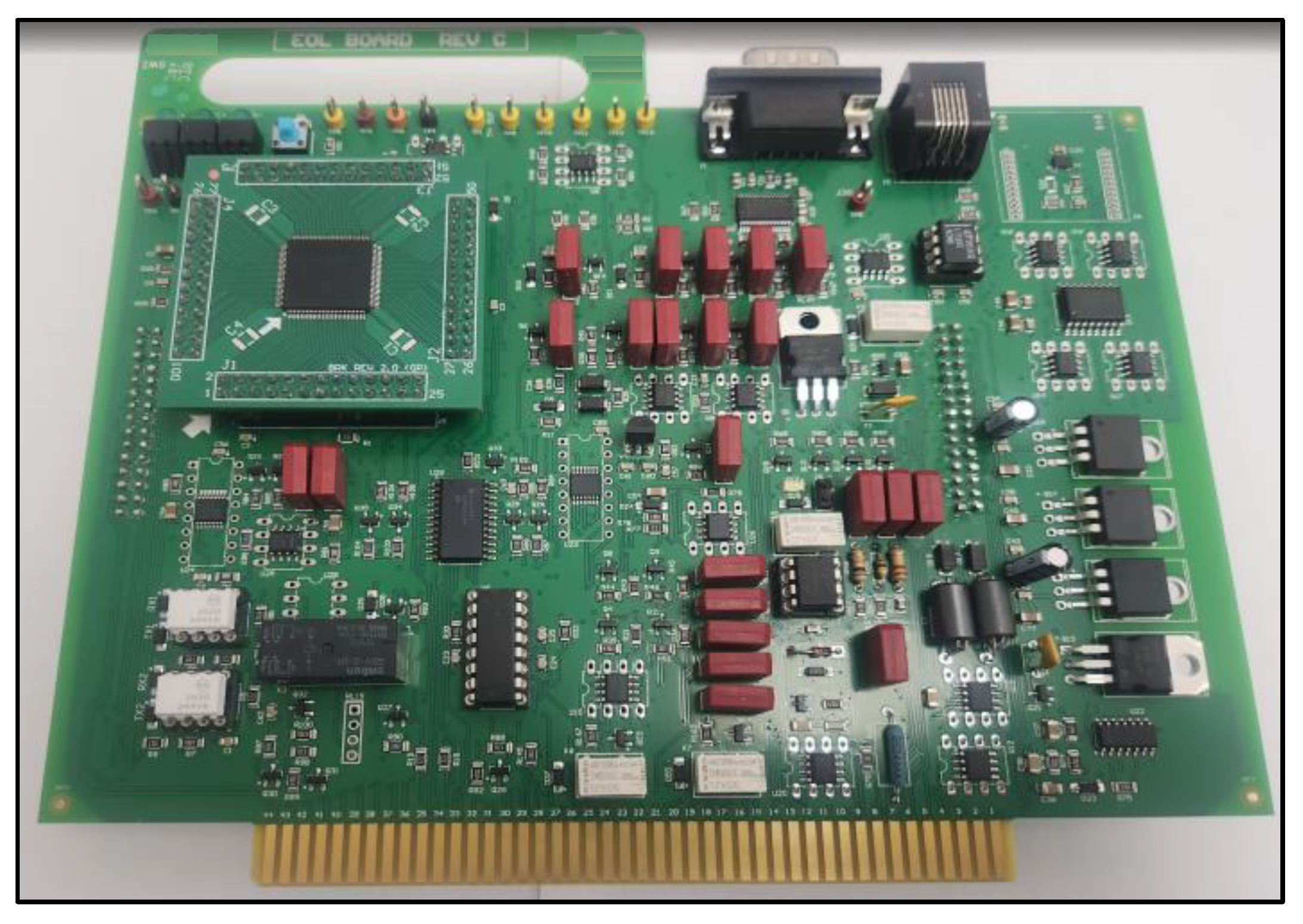

2.2. Implementation Overview

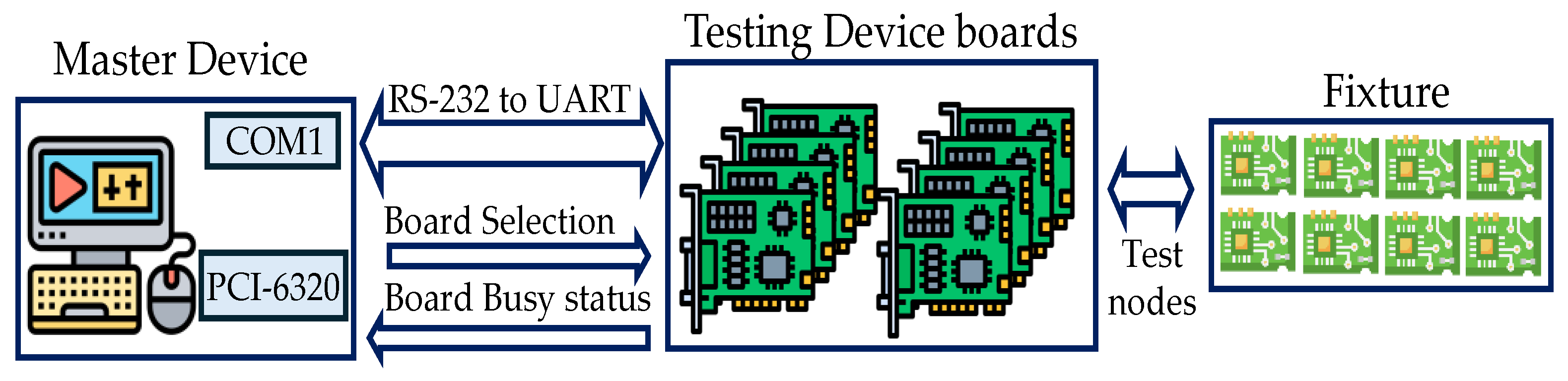

2.2.1. Control

- Board-selection. A digital input indicates a direct selection of a specific device board to accept any RS-232 instruction given.

- Board-busy. A digital output indicates its busy status to the master device.

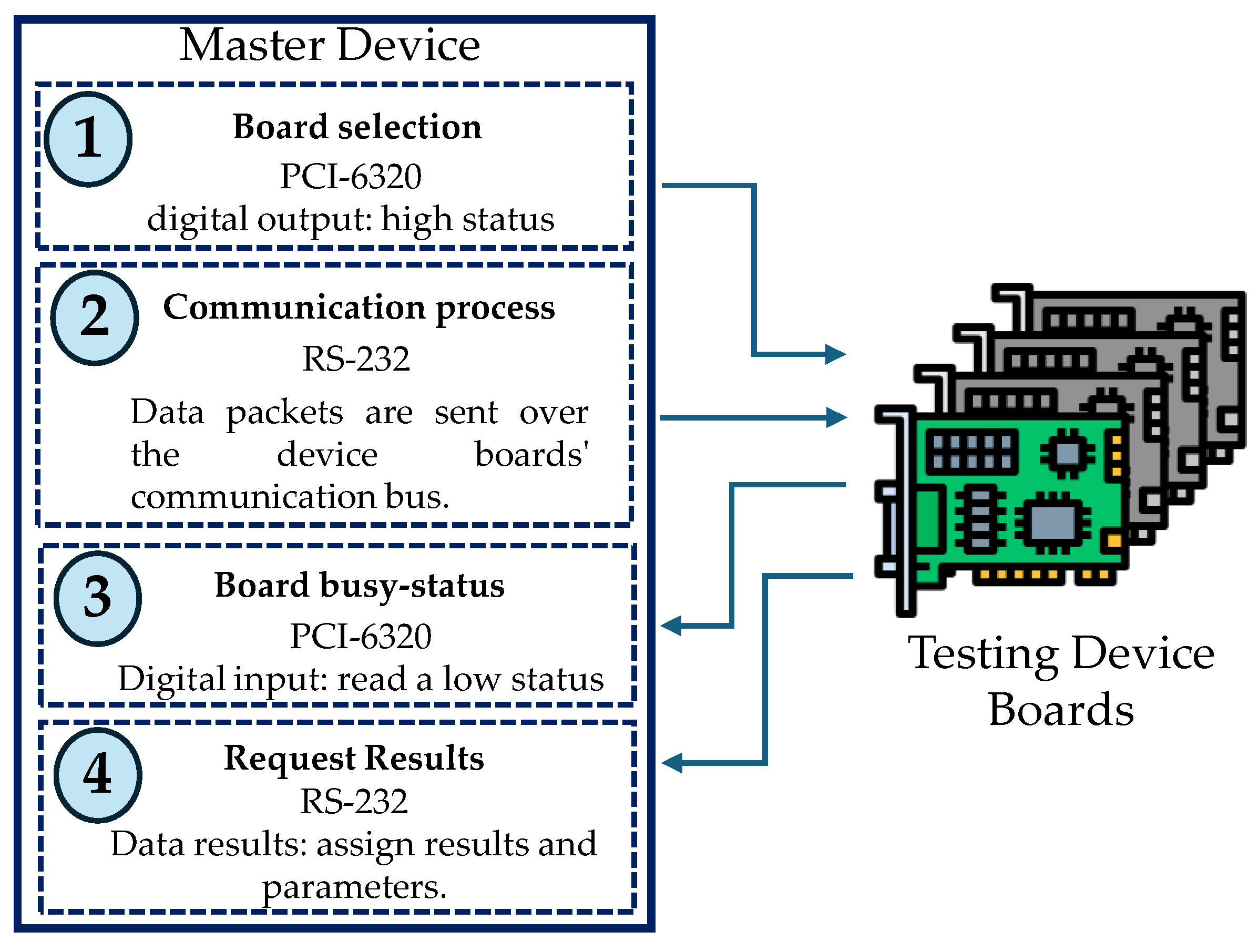

- Device board selection. The master device indicates a low-to-high digital output transition via the PCI-6320 to select a specific testing device board.

- Communication process. (i) The master device sends parameters such as the model name to test, test limits and tolerances, test node setup, and specific electrical tests to perform, and (ii) the master device sends a test command to start an automated testing routine based on the previously received testing data.

- Device board Busy-Status. After the test command is issued, the device board initiates a low-to-high transition on its digital output to indicate a busy status to the master device. The master device runs in a while loop, waiting until the testing device board completes a testing routine and transitions the busy state from high to low; this change indicates that the testing task has finished.

- Request Results. At this point, the master device can request the testing results by sending a request-result data packet.

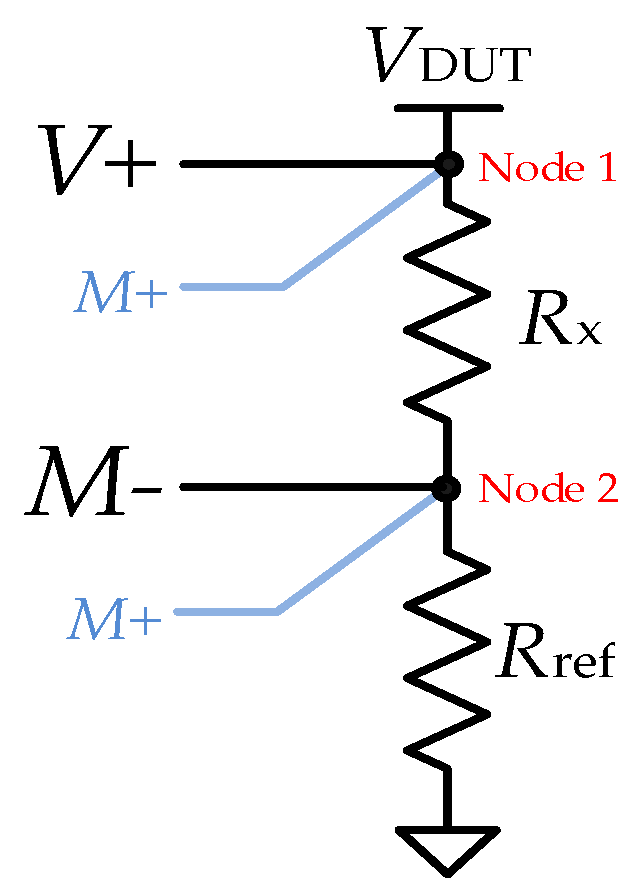

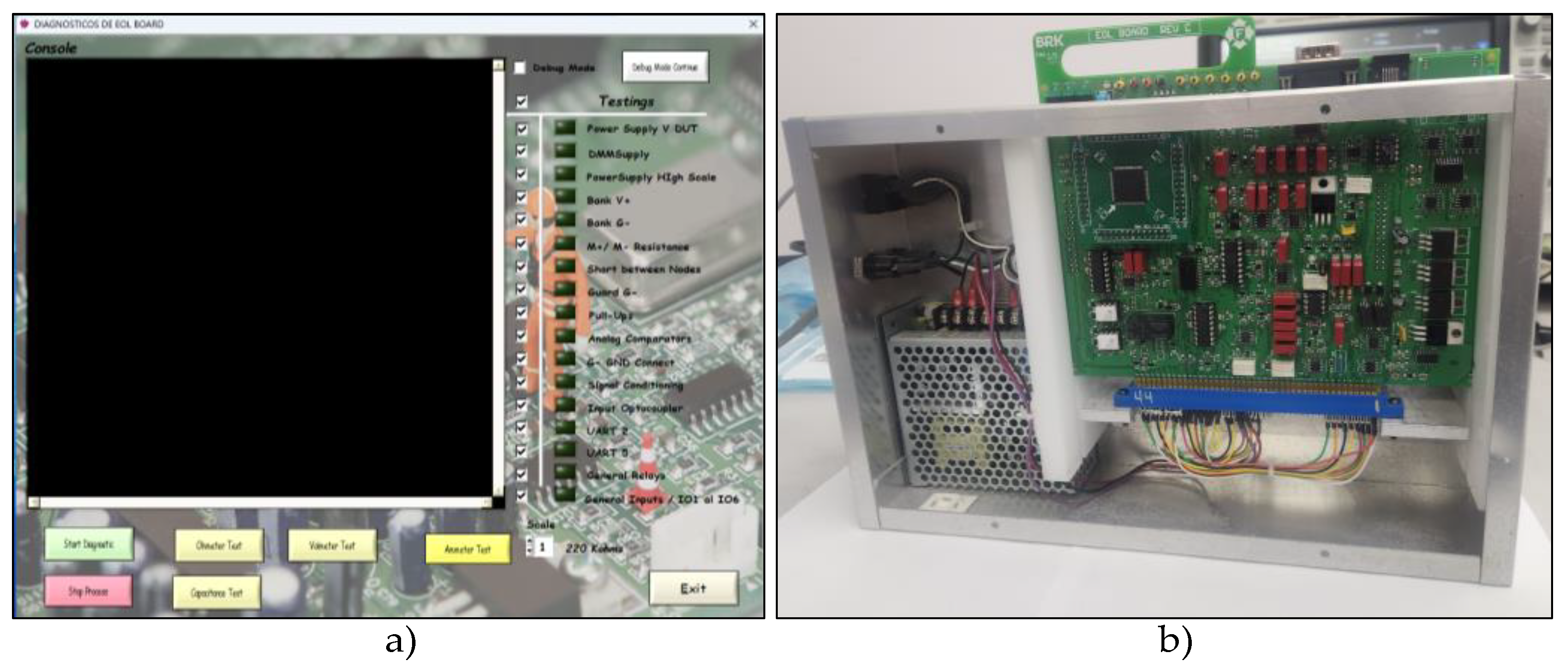

2.2.2. Testing Tasks

- Short-circuit and open-circuit testing. Correct wiring assemblies.

- Voltage stimuli to the DUT and monitor responses from signal processing.

- Voltmeter measurements, and ammeter to standby-current measurements.

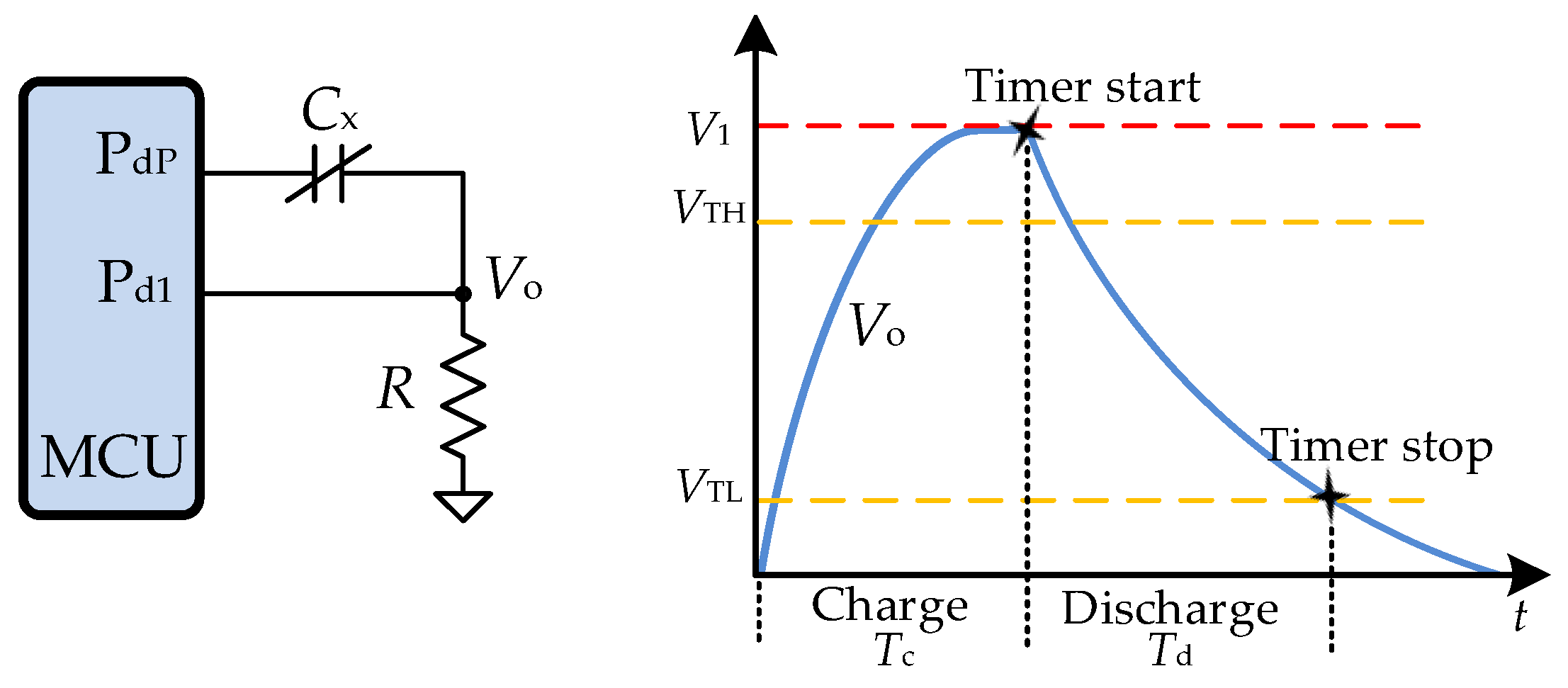

- Resistance and capacitance measurements.

- Read analog and digital signals.

- Audio detection.

- Read and write DUT data via UART. Factory-stored parameters in the product.

- Mix signals input and outputs depending on functional testing in the DUT.

3. Results

3.1. Experimental Evaluation

3.1.1. Communication Approach

3.1.2. Programmable Power Supplies

3.1.3. Programmable Pull-Ups, Pull-Downs, and Analog Comparators

3.1.4. DMM

3.1.5. Signal Amplification, Audio Conditioning, and Multiplexing

3.1.6. General Opto-Isolated Inputs, Speed-Up Signal, and EEPROM

3.1.7. General-Purpose Inputs/Outputs

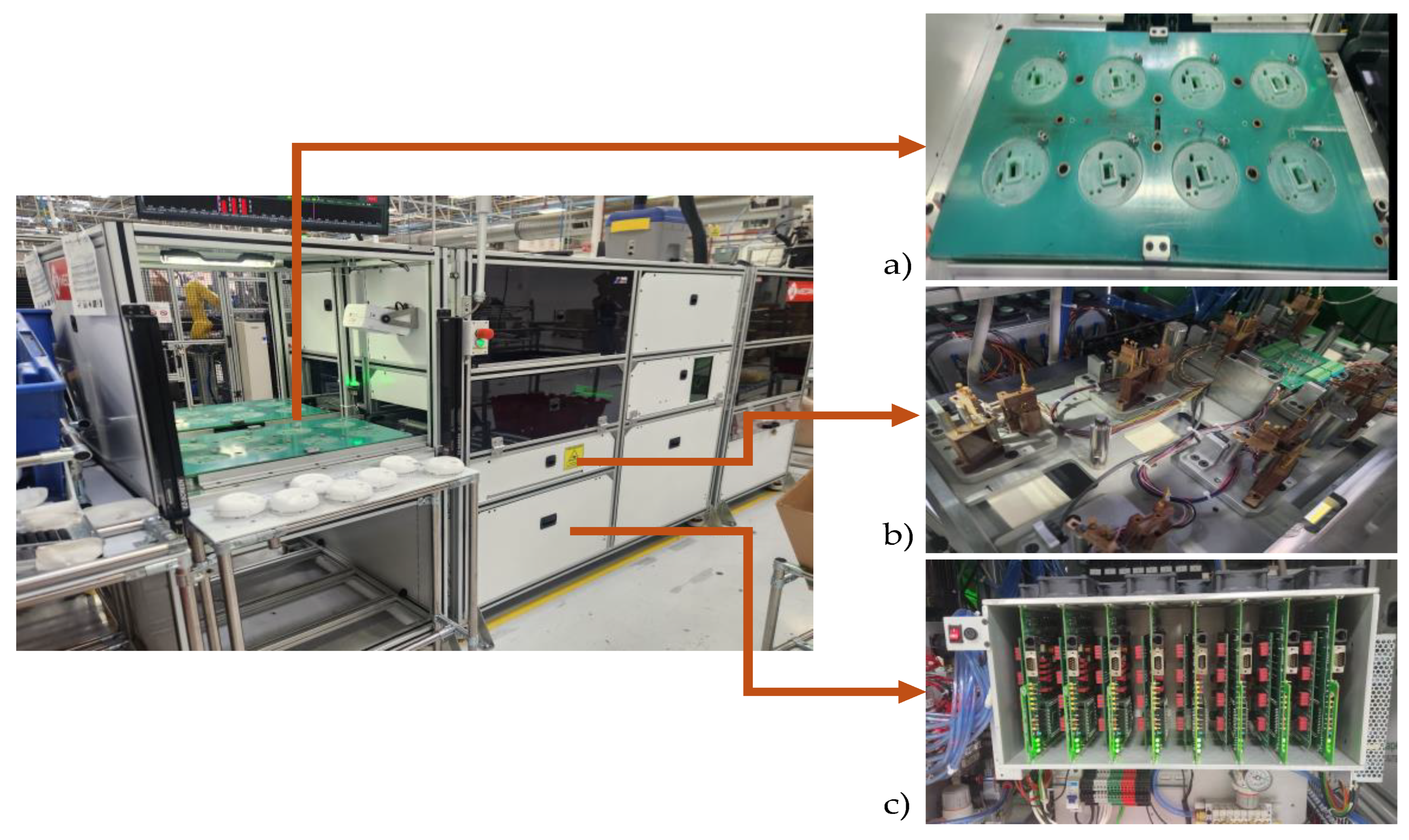

3.2. Automated Device Board Implementation

- Power up the DUT and read data via UART communication.

- Correct wiring of mechanical connectors via voltage stimuli and open circuit testing.

- Battery voltage measurement with and without load.

- Standby-current measurements.

- Press mechanical buttons and measure voltage responses in specific test nodes.

- Battery bars presence, short circuit detection in assembly bars.

- Audio detection and sound patterns.

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Appendix A. Electrical Design Schematics

References

- Buckroyd, A. In-Circuit Testing; Butterworth-Heinemann: Oxford, UK, 2015. [Google Scholar]

- Gupta, R. Failure Mode and Effects Analysis of PCB for Quality Control Process. MAPAN 2023, 38, 547–556. [Google Scholar] [CrossRef]

- Hatzopoulos, A.A. Analog Circuit Testing. In Proceedings of the 2017 International Mixed Signals Testing Workshop (IM-STW), Thessaloniki, Greece, 3–5 July 2017; pp. 1–6. [Google Scholar] [CrossRef]

- Petkov, N.; Ivanova, M. Printed Circuit Board and Printed Circuit Board Assembly Methods for Testing and Visual Inspection: A Review. Bull. Electr. Eng. Inform. 2024, 13, 2566–2585. [Google Scholar] [CrossRef]

- Lai, J.-P.; Lin, Y.-L.; Lin, H.-C.; Shih, C.-Y.; Wang, Y.-P.; Pai, P.-F. RLC Circuit Forecast in Analog IC Packaging and Testing by Machine Learning Techniques. Micromachines 2022, 13, 1305. [Google Scholar] [CrossRef] [PubMed]

- Monagas Martín, J.E.; Nevado, A.S.; Martínez, A.V. Low Cost Programmable Modular System to Perform In-Circuit Test (ICT) Full Development of the Hardware, Software and Mechanics of an ICT Machine. In Proceedings of the 2016 Technologies Applied to Electronics Teaching (TAEE), Seville, Spain, 22–24 June 2016; pp. 1–7. [Google Scholar] [CrossRef]

- Oliveira, R.; Freitas, L.; Costa, D.; Vicente, J.; Gonçalves, A.M.; Malheiro, T.; Machado, J. A Systematic Analysis of Printed Circuit Boards Bending during In-Circuit Tests. Machines 2022, 10, 135. [Google Scholar] [CrossRef]

- Hough, D.G. The IEEE Standard 754: One for the History Books. Computer 2019, 52, 109–112. [Google Scholar] [CrossRef]

- Reverter, F. The art of directly interfacing sensors to microcontrollers. J. Low Power Electron. Appl. 2012, 2, 265–281. [Google Scholar] [CrossRef]

- Puentes-Conde, G.M.; Sifuentes, E.; Molina, J.; Enríquez-Aguilera, F.; Bravo, G.; Enríquez, G.N. Direct Interface Circuits for Resistive, Capacitive, and Inductive Sensors: A Review. Electronics 2025, 14, 2393. [Google Scholar] [CrossRef]

- Sherman, D. Measure Resistance and Capacitance Without an A/D: AN449; Philips Semiconductors Microcontroller Products; Philips Semiconductors: Eindhoven, The Netherlands, 1993. [Google Scholar]

- Webjör, Å. Simple A/D for MCUs Without Built-in A/D Converters: AN477; Motorola Semiconductors; MOTOROLA Ltd.: Chicago, IL, USA, 1993. [Google Scholar]

- Cox, D. Implementing Ohmmeter/Temperature Sensor: AN512; Microchip Technology: Chandler, AZ, USA, 1994. [Google Scholar]

- Richey, R. Resistance and Capacitance Meter Using a PIC16C622: AN611; Microchip Technology: Chandler, AZ, USA, 1997. [Google Scholar]

- Bierl, L. Precise Measurements with the MSP430; Texas Instruments: Dallas, TX, USA, 1996. [Google Scholar]

- Merritt, B. MSP430 Based Digital Thermometer; Application Report 1999; Texas Instruments: Dallas, TX, USA, 1999. [Google Scholar]

| Data type | Identifier | Value | Representation | ASCII Conversion |

|---|---|---|---|---|

| Char | %c | 91 | hex-format: 0 × 5B | ‘5’, ‘B’ |

| Integer | %i | 13,675 | hex-format: 0 × 356B | ‘3’, ‘5’, ‘6’, ‘B’ |

| Float | %f | 8.95 | float to IEEE754 32-bits: 0 × 410F3333 | ‘4’, ‘1’, ‘0’, ‘F’,’3, ‘3’, ‘3’, ‘3’ |

| String | %s | ‘b’ | no changes | ‘b’ |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).