Submitted:

08 July 2025

Posted:

09 July 2025

You are already at the latest version

Abstract

Keywords:

1. Introduction

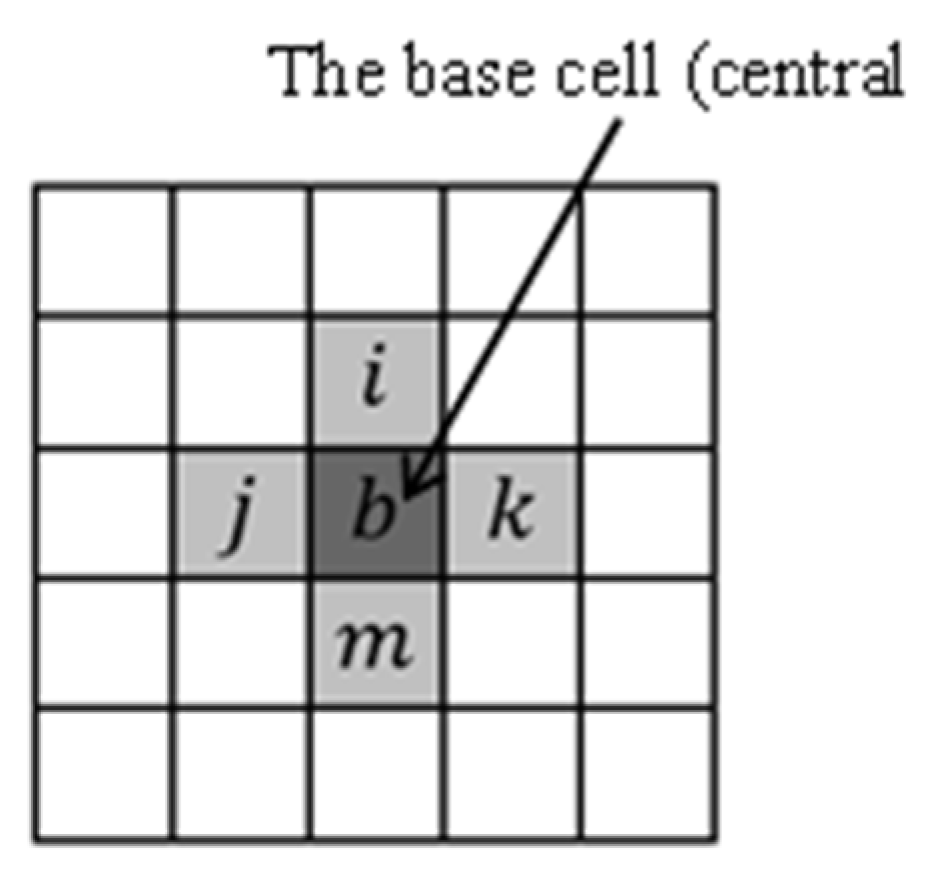

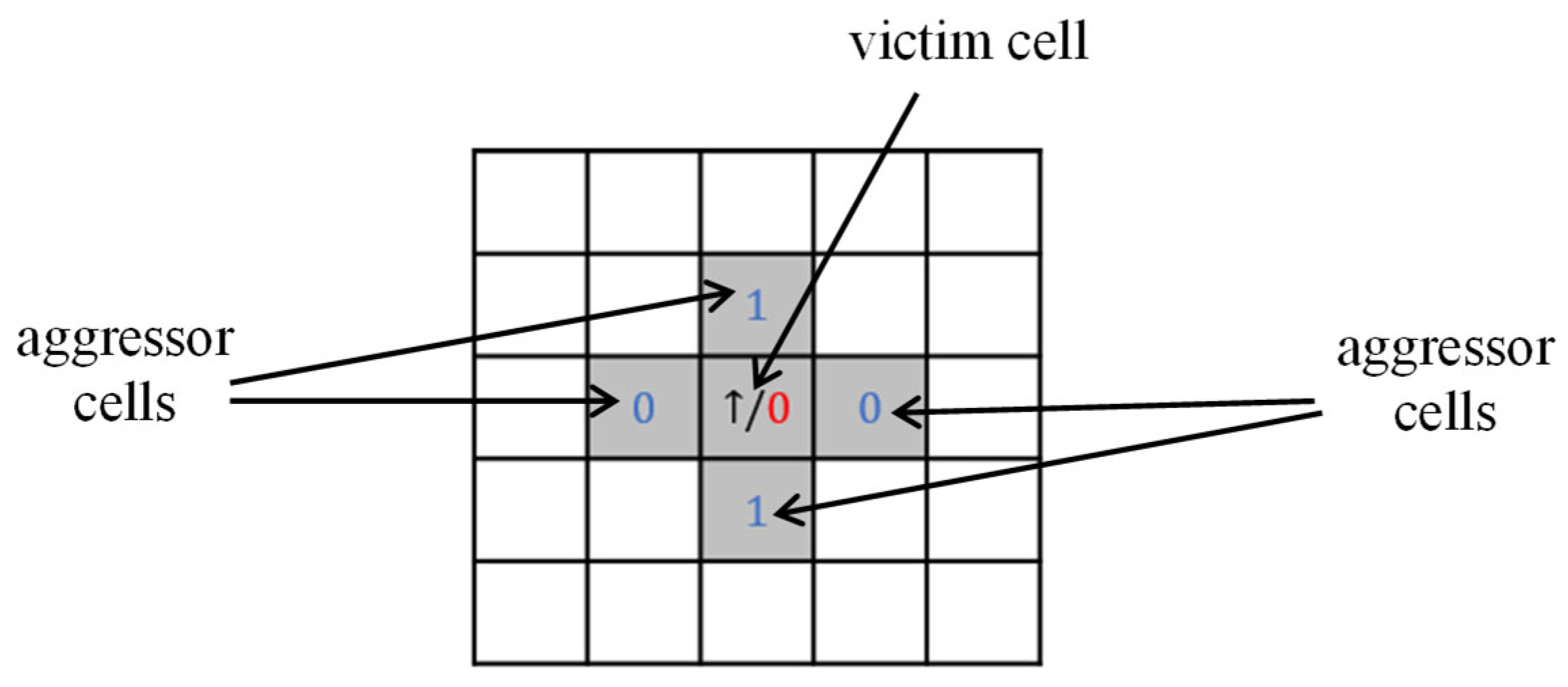

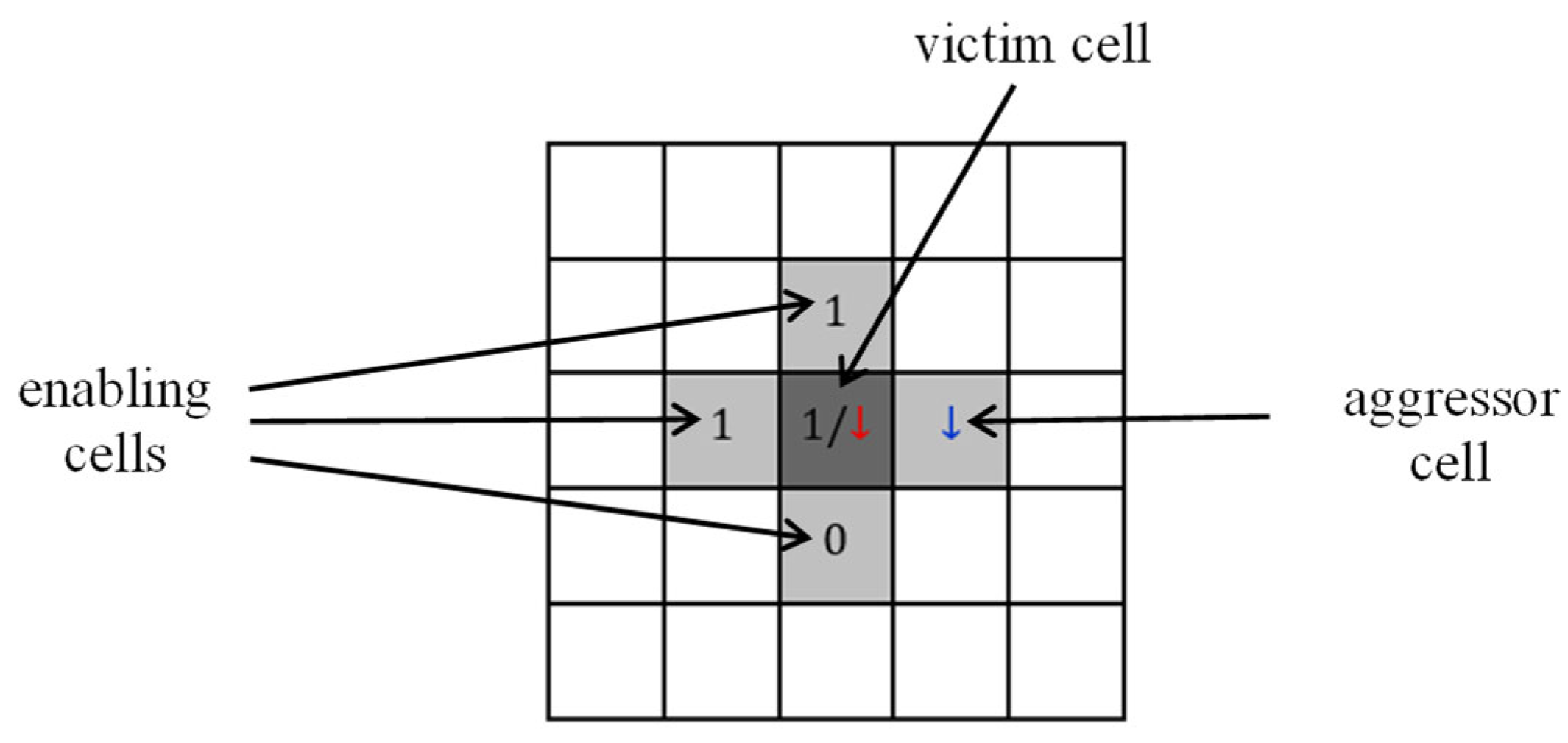

2. Assumptions, Notations and Preliminaries

2.1. Assumptions

2.2. Notations

| Operation of reading a memory cell and checking the value read by comparing it with the expected one. | |

| Operation of writing the logical value 0 (1) to the addressed cell. | |

| Write operation to change the state of the addressed cell (transition write operation). | |

| Write operation without changing the state of the addressed cell (non-transition write operation). | |

| , | Memory operations with cell . |

| () | A change of logical state in a memory cell from to 1 (to 0) by sensitizing a memory fault (i.e., a memory error). |

| Row (column) address in a memory operation. | |

| The logical value of memory cell . |

2.3. Preliminaries

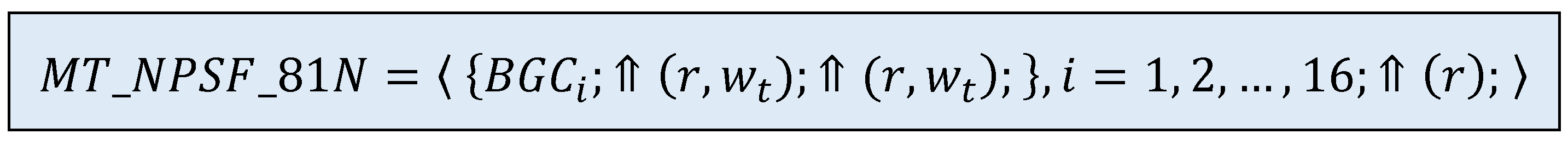

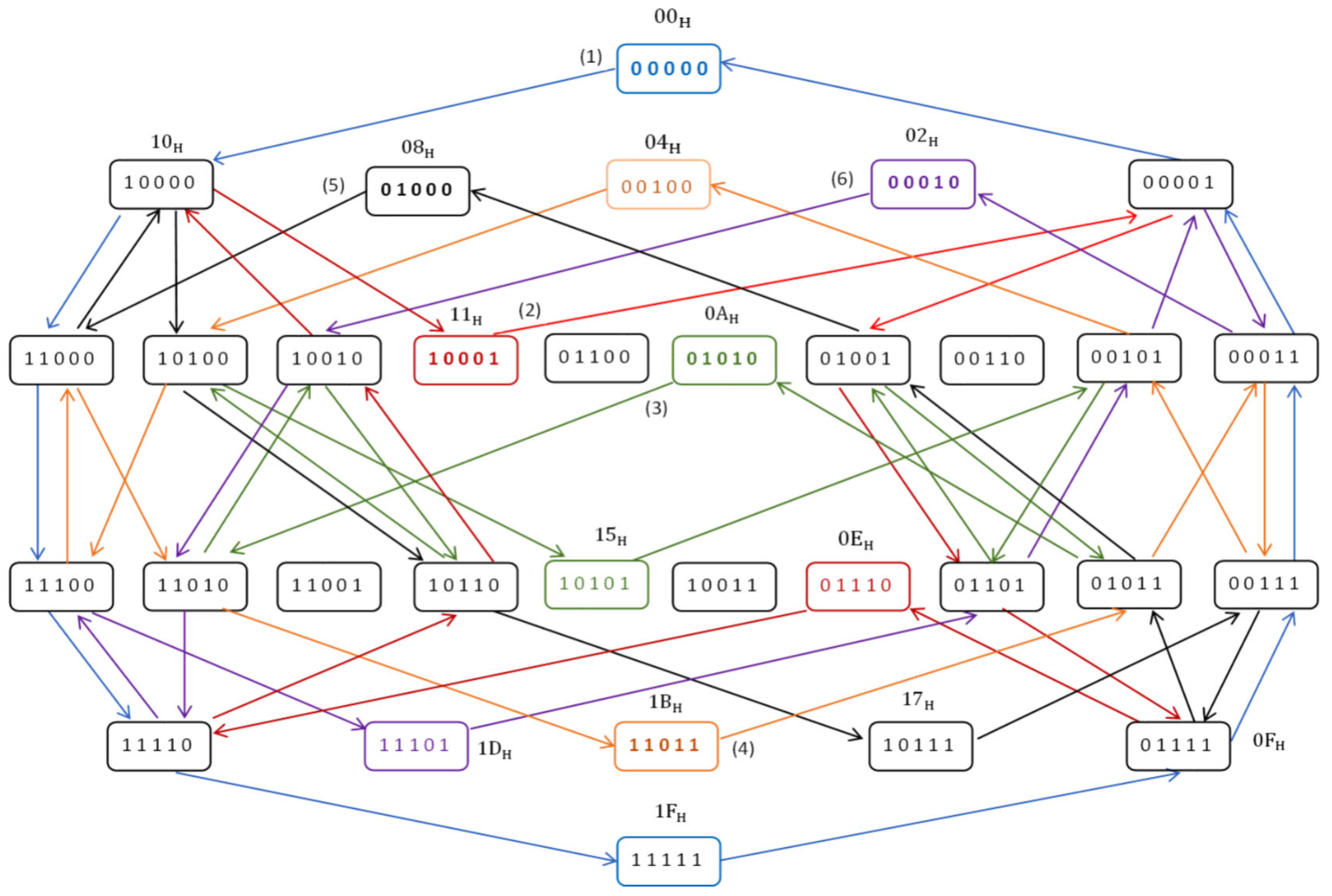

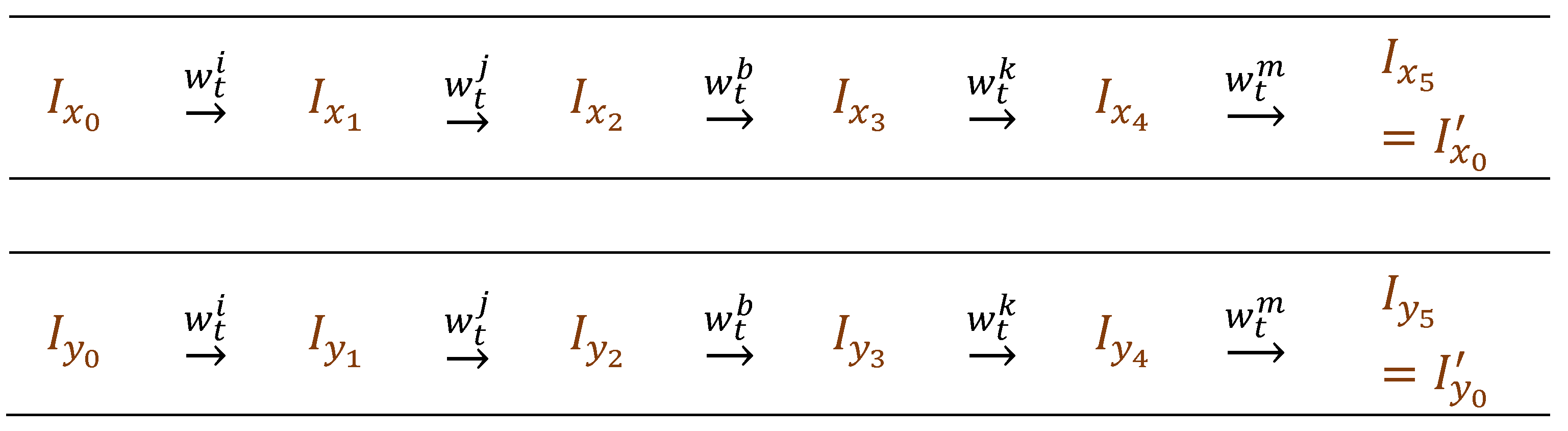

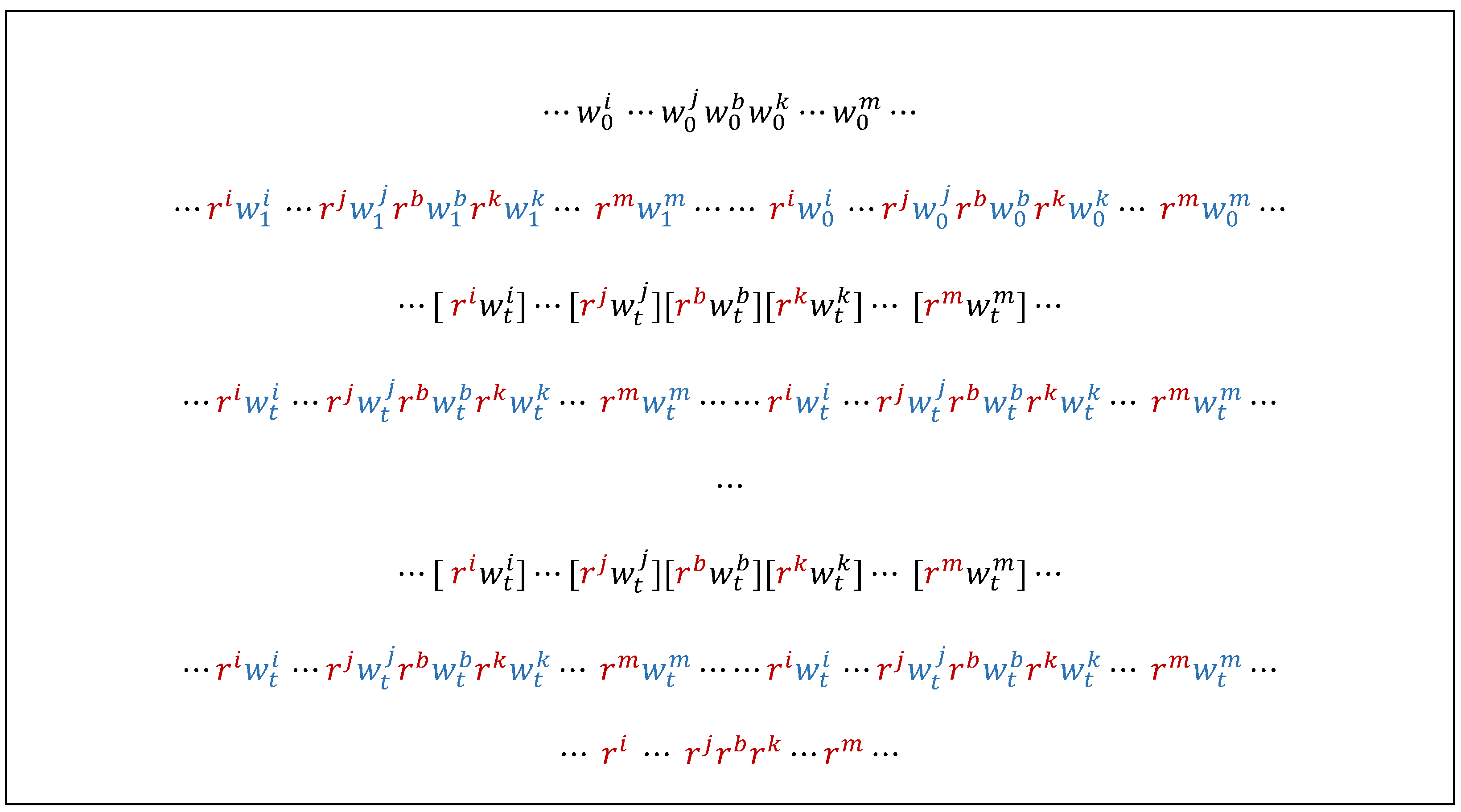

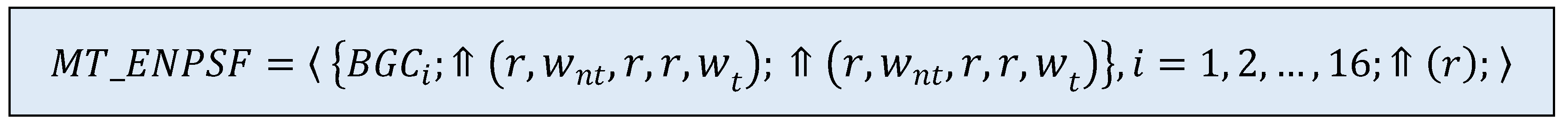

3. Near-Optimal March Tests for the NPSF Model

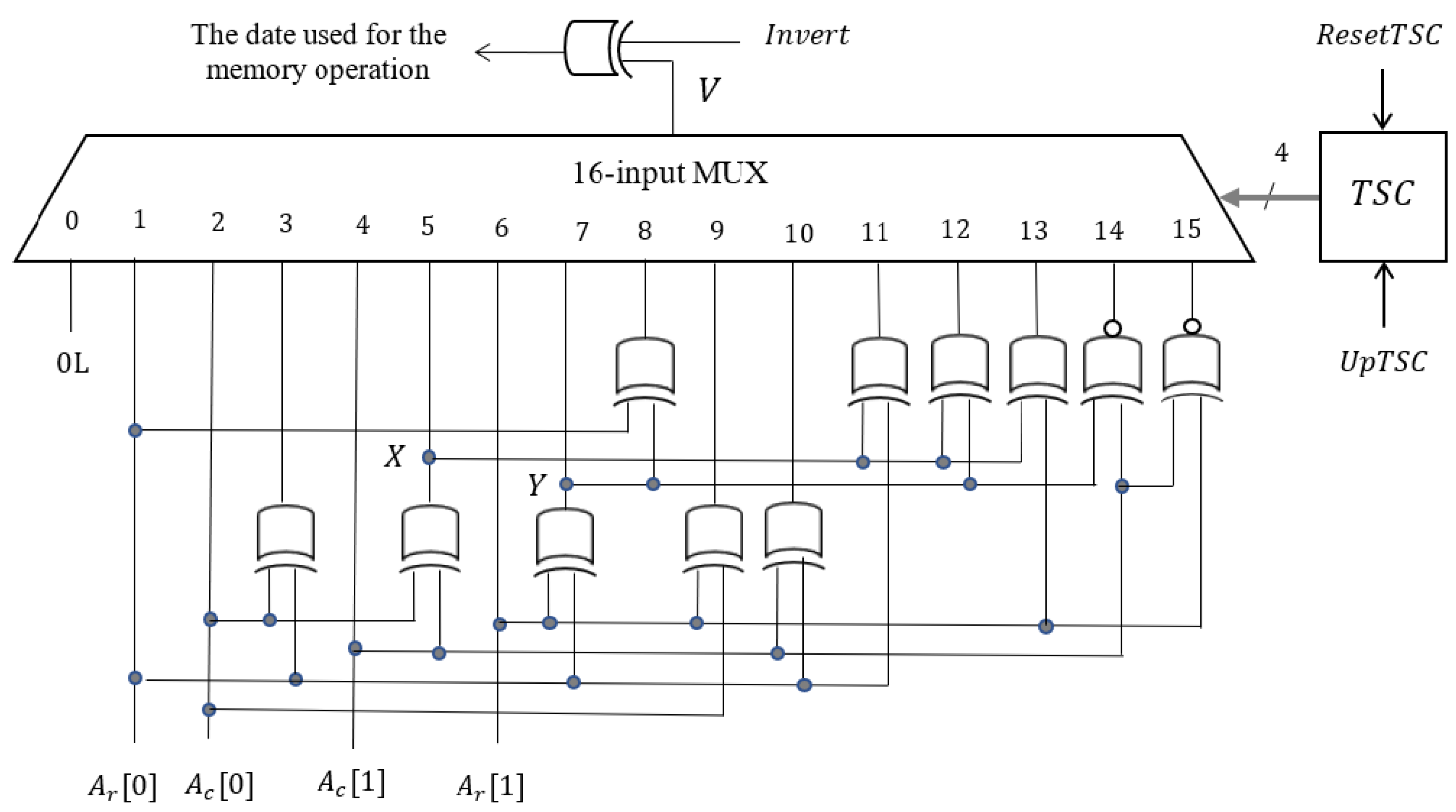

4. Considerations for BIST Implementation of the Proposed Memory Tests

5. Conclusion

Supplementary Materials

Funding

Acknowledgements

Conflicts of Interest

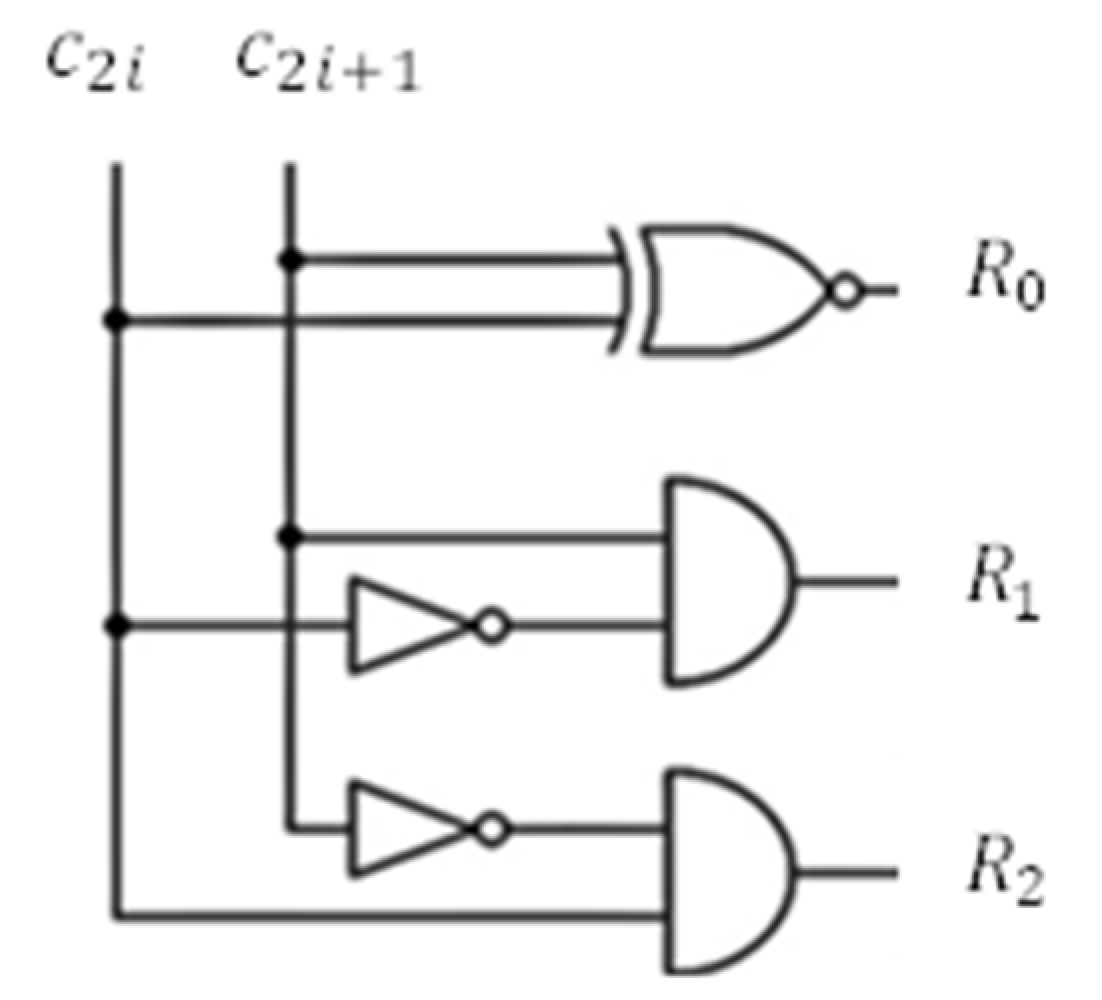

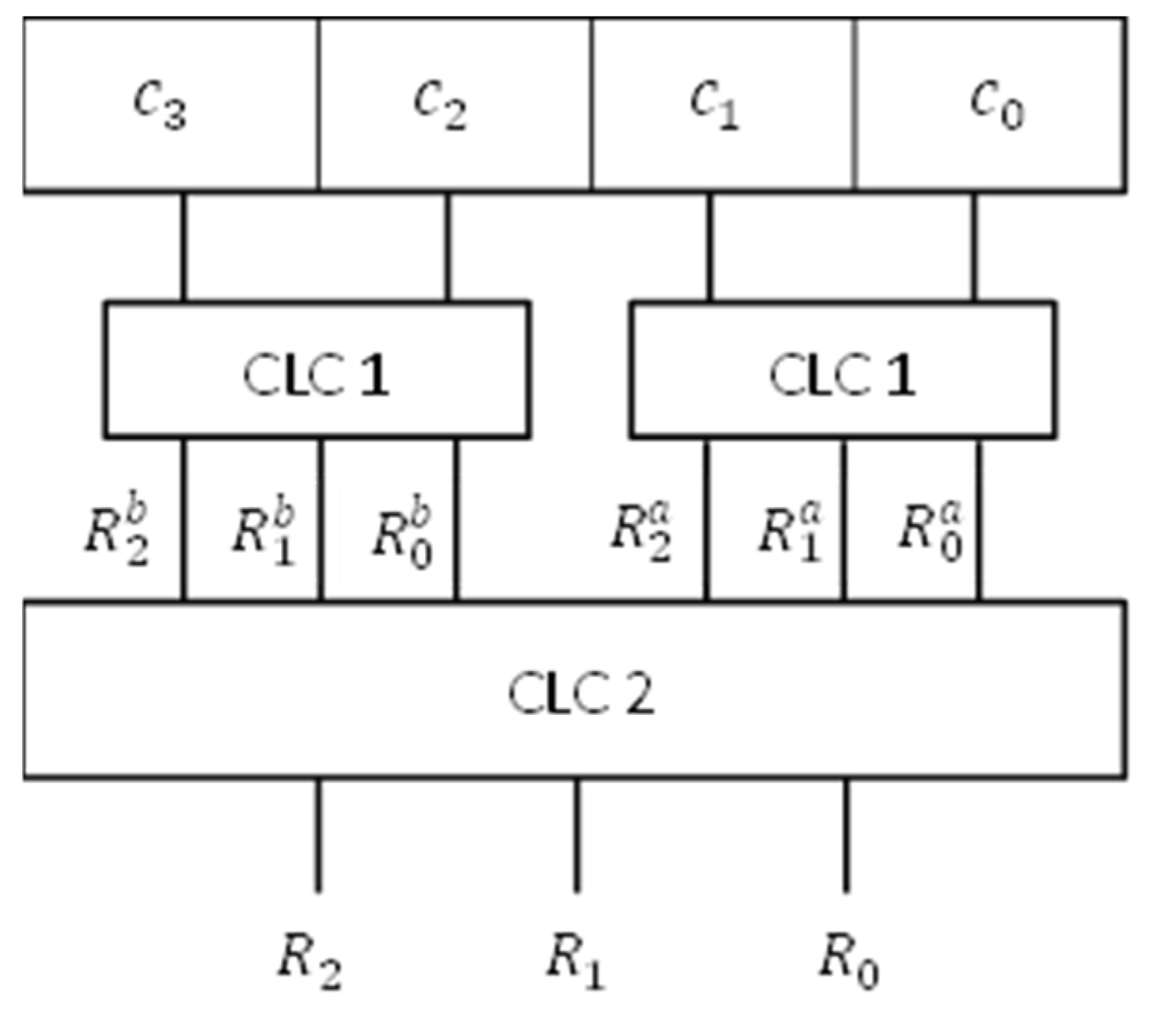

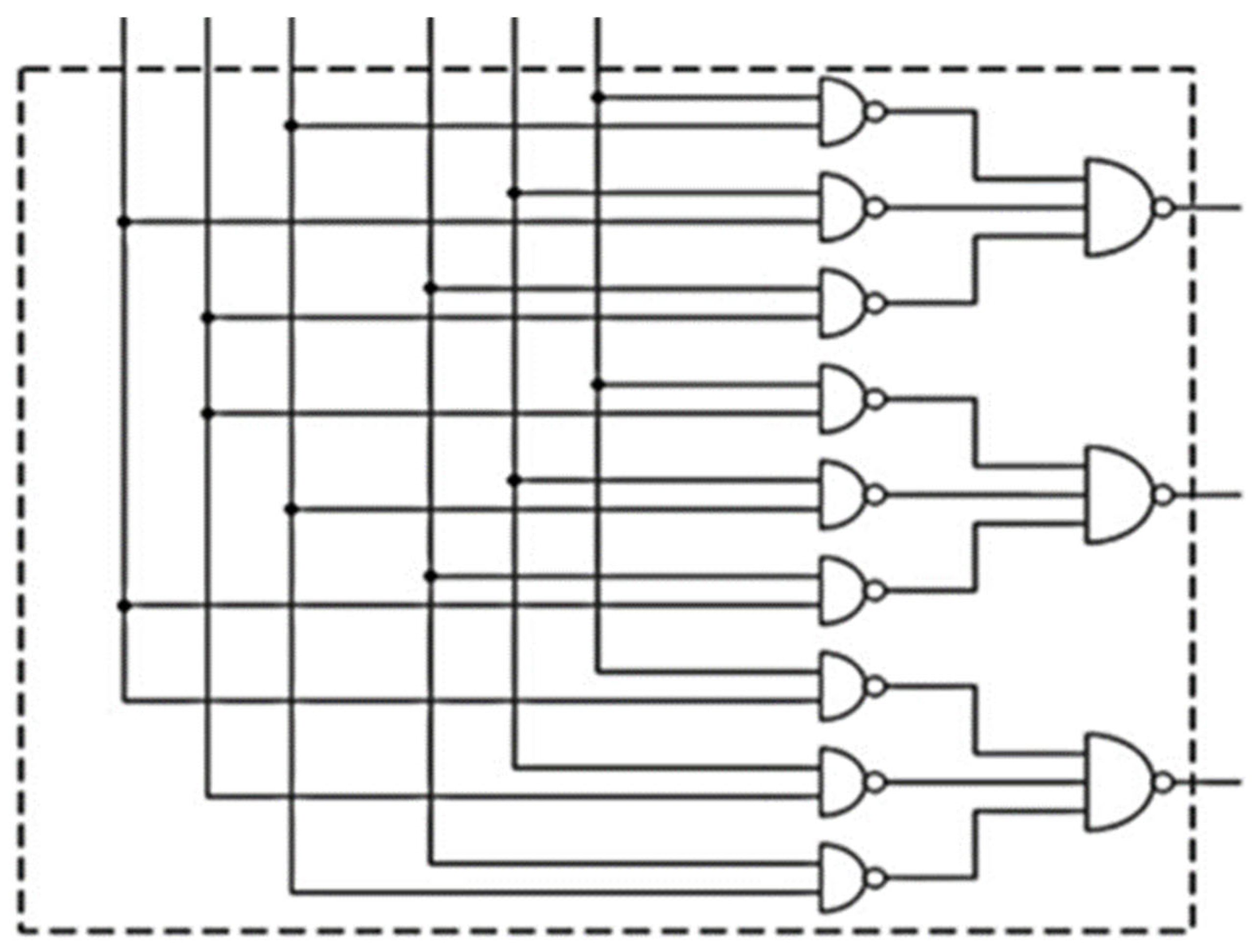

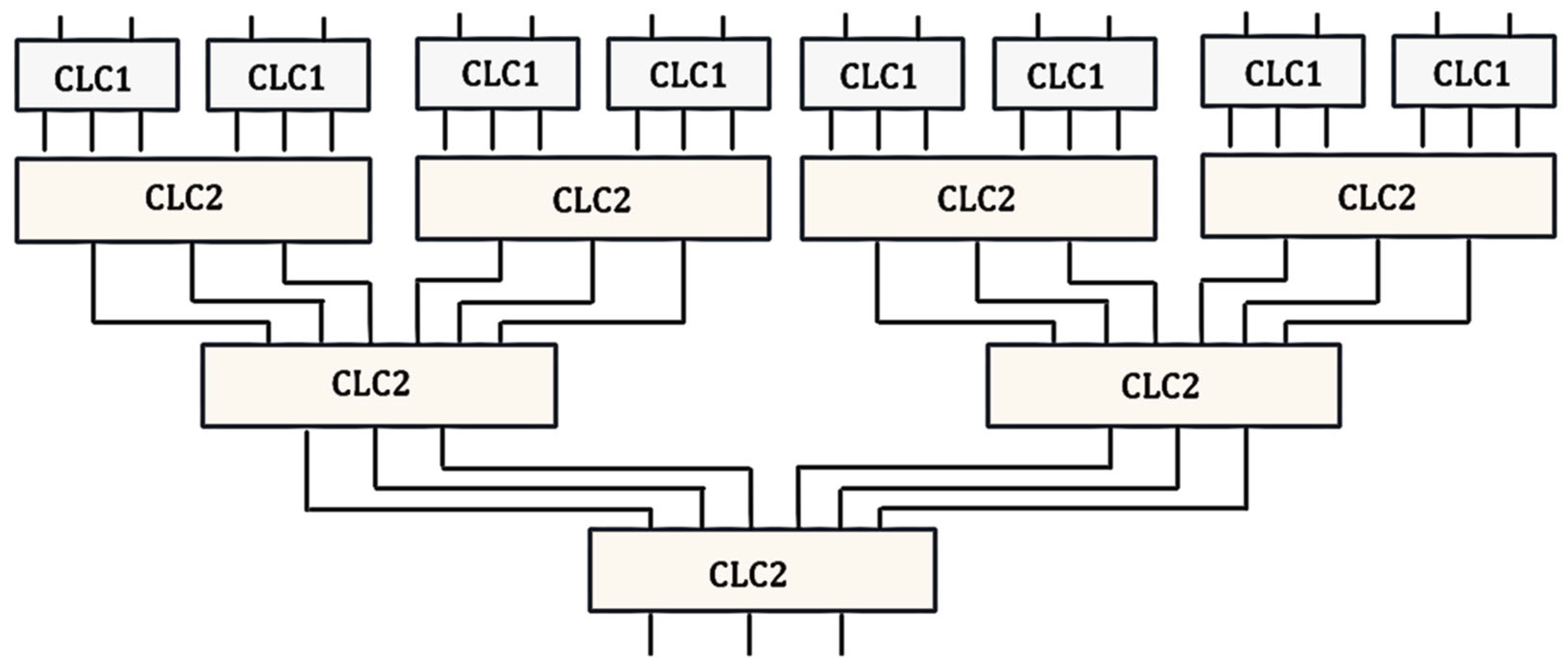

Appendix A. Hardware Generation of Modulo 3 Residues

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | ||

| 1 | 2 | 4 | 8 | 16 | 32 | 64 | ||

| 1 | 2 | 1 | 2 | 1 | 2 | 1 |

References

- Chakravarthi, V. S., A practical Approach to VLSI System on Chip (SoC) Design: A Comprehensive Guide, Second Edition, Springer, 2022.

- Dean Adams, R., High Performance Memory Testing: Design Principles, Fault Modeling and Self-Test, Springer, New York, NY, USA, 2003.

- Mazumder, P., Chakraborty, K., Testing and Testable Design of High-Density Random-Access Memories (Frontiers in Electronic Testing), Kluwer Academic, Boston, Mass, USA, 1996.

- Mrozek, I., Multi-run Memory Tests for Pattern-Sensitive Faults, Springer, 2019.

- Ramana Kumari, K. L. V., Asha Rani, M., Balaji, N., 3-Cell Neighborhood Pattern-Sensitive Fault Testing in Memories Using Hamiltonian and Gray Sequences, Journal of Computational and Theoretical Nanoscience, Vol. 18 (3), pp. 879-884, March 2021.

- Hamdioui S., Testing Static Random-Access Memories: Defects, Fault Models and Test Patterns, Kluwer Academic Publishers, The Netherlands, 2004.

- van de Goor, A.J., Al-Ars, Z., Functional Faults Models: A Formal Notation and a Taxonomy, Proc. 18th IEEE VLSI Test Symp., Montreal, Canada, April-May 2000, pp. 281-289.

- Samanta, A., Saha, M., Mahato, A.K., BIST Design for Static Neighbourhood Pattern-Sensitive Fault Test, IJCA Proc. on International Conference on Communication, Circuits and Systems 2012 iC3S (5): 23-28, June 2013.

- Harutunyan, G., Vardanian, V.A., Zorian, Y., Minimal March Tests for Unlinked Static Faults in Random Access Memories, Proc. of 23rd IEEE VLSI Symposium, Palm Springs, CA, USA, May 2005, pp. 53–59.

- Cascaval, P., Bennett, S., Efficient March Test for 3-Coupling Faults in Random Access Memories, Microprocessors and Microsystems, Elsevier, Vol. 24 (10), 2001, 501-509.

- Cascaval, P., Bennett, S., Hutanu, C., Efficient March Tests for a Reduced 3-Coupling and 4-Coupling Faults in RAMs, Journal of Electronic Testing. Theory and Applications, Vol. 20 (2), 2004, pp. 227-243.

- Cascaval, P., Cascaval, D., March SR3C: A Test for a Reduced Model of All Static Simple Three-Cell Coupling Faults in Random-Access Memories, Microelectronics Journal, Vol. 41 (4), 2010, pp. 212-218.

- Cascaval, P., Cascaval, D., March Test Algorithm for Unlinked Static Reduced Three-Cell Coupling Faults in Random-Access Memories, Microelectronics Journal, Vol. 93, November, 2019.

- Cascaval, P., Cascaval, D., Near-optimal March Tests for Three-Cell and Four-Cell Coupling Fault Models in Random-Access Memories, Romanian Journal of Information Science and Technology, Vol. 27 (3-4), 2024, 323–335.

- Mrozek, I; Shevchenko, NA and Yarmolik, VN, Universal Address Sequence Generator for Memory Built-in Self-Test, Fundamenta Informaticae, Vol. 188 (1), 41-61, Dec. 2022. [CrossRef]

- Jidin, A.Z., Hussin, R., Fook, L.W., Mispan, M.S., A Review Paper on Memory Fault Models and Test Algorithms, Bulletin of Electrical Engineering and Informatics, Vol. 10 (6), 2021, 3083-3093.

- Hantos, G., Flynn, D., Desmulliez, M.P.Y., Built-In Self-Test (BIST) Methods for MEMS: A Review. Micromachines, Vol. 12 (1), 40, 2020.

- Zhang, L.; Wang, Z.; Li, Y.; Mao, L., A Precise Design for Testing High-Speed Embedded Memory Using a BIST Circuit, IETE Journal of Research, Vol. 63, pp. 473–481, 2017.

- Thakur, R.S., Awasthi, A., A Review Paper on Memory Testing Using BIST, Global Research and Development Journal for Engineering, Vol. 1 (4), 2016, pp. 94-98.

- Hou, C., Li, J., Fu, T., A BIST Scheme with the Ability of Diagnostic Data Compression for RAMs, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol. 33 (12), 2014, pp. 2020-2024.

- Nair, C., Thatte, S.M., Abraham, J.A., Efficient Algorithms for Testing Semiconductor Random-Access Memories, IEEE Transactions on Computers, C-27 (6), 1978, pp. 572–576.

- Papachristou, C.A., Saghal, N.B., An Improved Method for Detecting Functional Faults in Random-Access Memories, IEEE Transactions on Computers, C-34 (2), 1985, pp.110–116.

- Cockburn, B.F., Deterministic Tests for Detecting Single V-Coupling Faults in RAMs, Journal of Electronic Testing: Theory and Applications, Vol. 5, pp. 91–113, 1994.

- Wu, T.C., Fan, W.K., et al, A New Test Algorithm and Fault Simulator of Simplified Three-Cell Coupling Faults for Random Access Memories, IEEE ACCESS, Vol. 12, 2024, 109218-109229.

- Hayes, J.P., Detection of Pattern-Sensitive Faults in Random-Access Memories, IEEE Transactions on Computers, Vol. C-24 (2), 1975, pp. 150 – 157.

- Ramana Kumari, K.L.V., Asha Rani, M., Balaji, N., Testing of Neighborhood Pattern-Sensitive Faults for Memory. In: Reddy, V.S., Prasad, V.K., Wang, J., Reddy, K.T.V. (eds) Soft Computing and Signal Processing. Advances in Intelligent Systems and Computing, Vol. 1340, Springer, Singapore, 2022.

- Hayes, J. P., Testing Memories for Single-Cell Pattern-Sensitive Faults, IEEE Transactions on Computers, 29 (3), 1980, pp. 249–254.

- Suk, D., Reddy, S., Test Procedures for a Class of Pattern-Sensitive Faults in Semiconductor Random-Access Memories, IEEE Transactions on Computers, C-29 (6), 1980, pp. 419-429.

- Karpovsky, M.G., Yarmolik, V.N., Transparent Random-Acces Memory Testing for Pattern-Sensitive Faults, Journal of Electronic Testing. Theory and Applications, Vol. 9, Dec. 1996, pp. 860-969.

- Kang, D. C., Cho, S. B., An Efficient Build–in Self–Test Algorithm for Neighborhood Pattern-Sensitive Faults in High–Density Memories, Proc. 4th Korea–Russia Int. Symp. Science and Technology, 2000, Vol. 2, pp. 218–223.

- Buslowska, E., Yarmolik, V. N., Multi-Run March Tests for Pattern-Sensitive Faults in RAM, 2018 IEEE East-West Design & Test Symposium (EWDTS 2018), SEP 14-17, 2018, Kazan, Russia.

- Cheng, K.L., Tsai, M.F., Wu, C.W., Neighborhood Pattern-Sensitive Fault Testing and Diagnostics for Random-Access Memories, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol. 21 (11), 2002, 1328-1336.

- Huzum, C., Cascaval, P., A Multibackground March Test for Static Neighborhood Pattern-Sensitive Faults in Random-Access Memories, Electronics and Electrical Engineering (Elektronika ir Elektrotechnika) – Section System Engineering, Computer Technology, Vol. 119 (3), 81-86, April 2012.

- Wang, L.T., Wu, C.W., Wen, X., Memory Testing and Built-In Self-Test. In VLSI Test Principles and Architectures, 1st ed.; Design for Testability, Elsevier, Amsterdam, The Netherlands, 2006.

- Bernardi, P., Grosso, M., Sonza Reorda, M., Zhang, Y., A Programmable BIST for DRAM testing and diagnosis, IEEE International Test Conference, 2-4 Nov, 2010, Austin, TX, USA, pp: 1-10.

- Rusli, J. R.; Sidek, R. M.; Wan Zuha, W. H., Development of Automated Neighborhood Pattern Sensitive Fault Syndrome Generator for SRAM, 10th IEEE Int. Conf. on Semiconductor Electronics (ICSE), Kuala Lumpur, Malaysia, Sept 19-21, 2012.

- Cascaval, P., Silion, R., Cascaval, D., A Logic Design for MarchS3C Memory Test BIST Implementation, Romanian Journal of Information Science and Technology, Vol. 12 (4), 2009, pp. 440-454.

- Yarmolik, V. N., Levantsevich, V. A., Demenkovets, D. V., Mrozek, I., Construction and Application of March Tests for Pattern-Sensitive Memory Faults Detection, Informatics, Vol. 18 (1), 2021.

- Mrozek, I., Analysis of Multibackground Memory Testing Techniques, International Journal of Applied Mathematics and Computer Science, Vol. 20 (1), March, 2010, pp. 191–205.

- Parvathi, M., Himasree, T., Bhavyasree, T., Novel Test Methods for NPSF Faults in SRAM, 2018 Int. Conference on Computational and Characterization Techniques in Engineering & Sciences (CCTES), Lucknow, India, 14-15 September, 2018.

- Huzum, C., Cascaval, P., A Fault Primitive Based Model for all Static Neighborhood Pattern-Sensitive Faults in Random-Access Memories, Bul. Inst. Polit. Iasi, Tom LV (LIX), Fasc. 3, Automatică şi Calculatoare, 2009.

- Ribenboim, P., Classical Theory of Algebraic Numbers, Springer Science, New York, NY, USA, 2001.

| 0 | 1 | 2 | 3 | ||

| 0 | |||||

| 1 | |||||

| 2 | |||||

| 3 | |||||

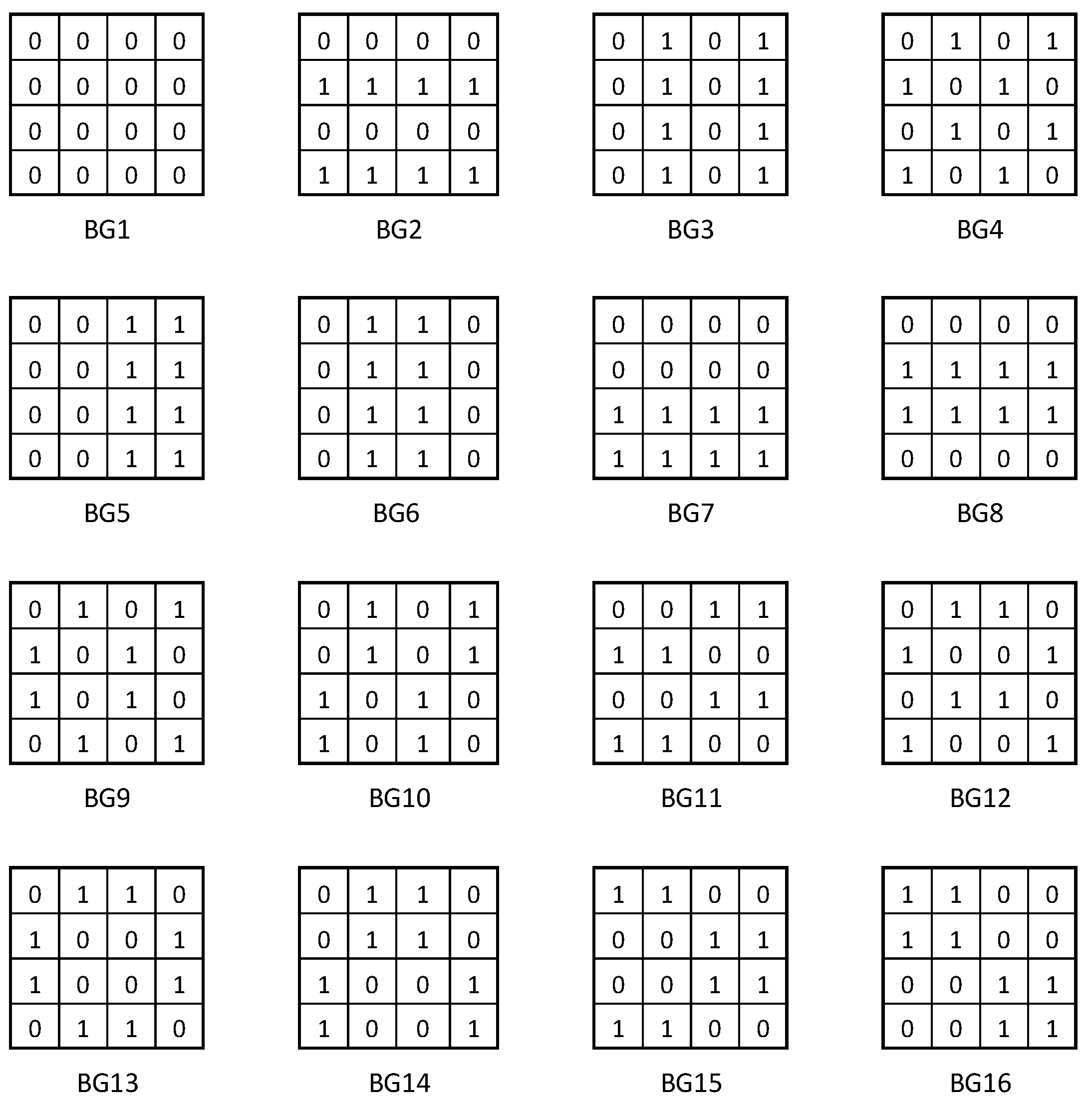

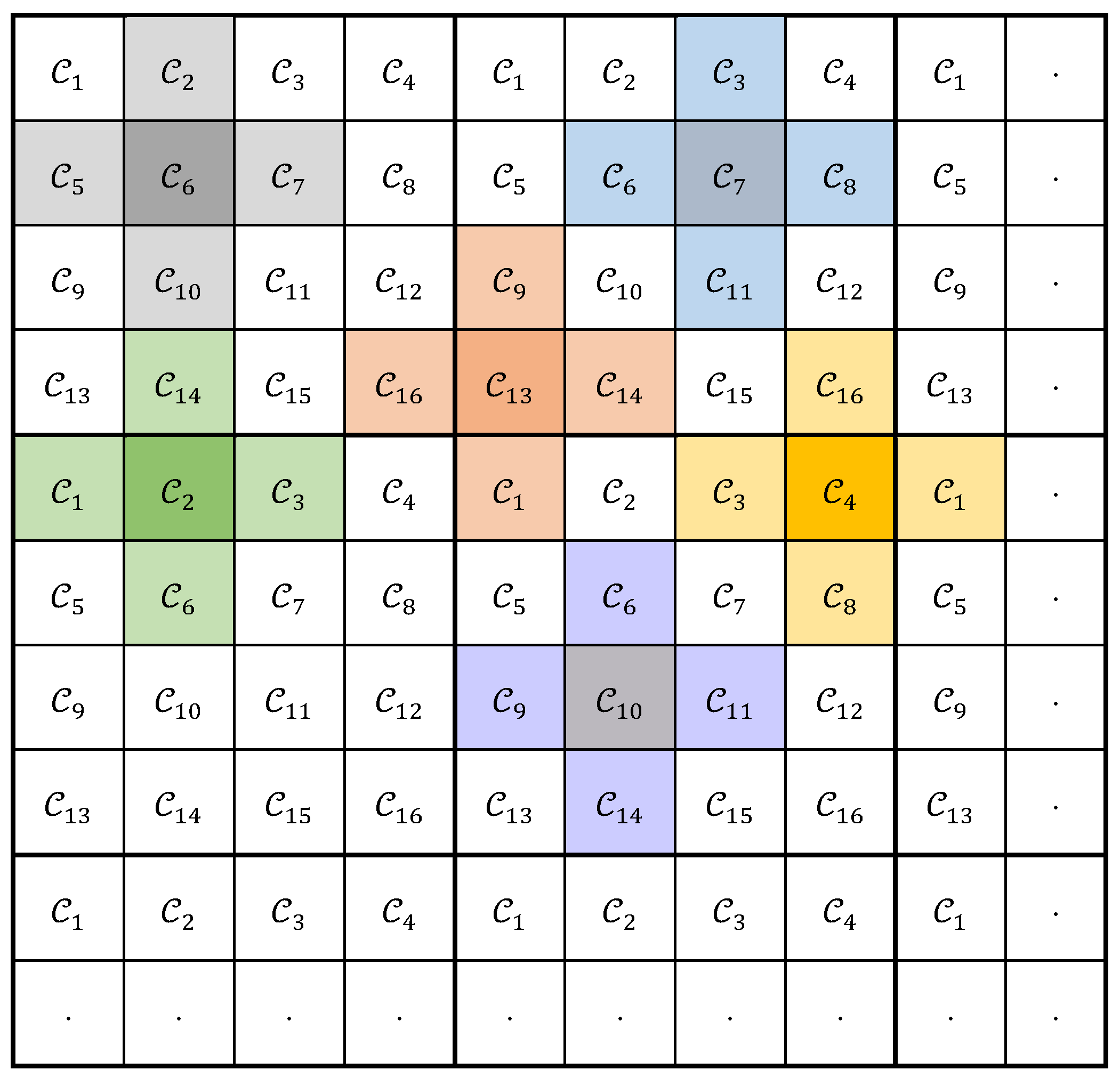

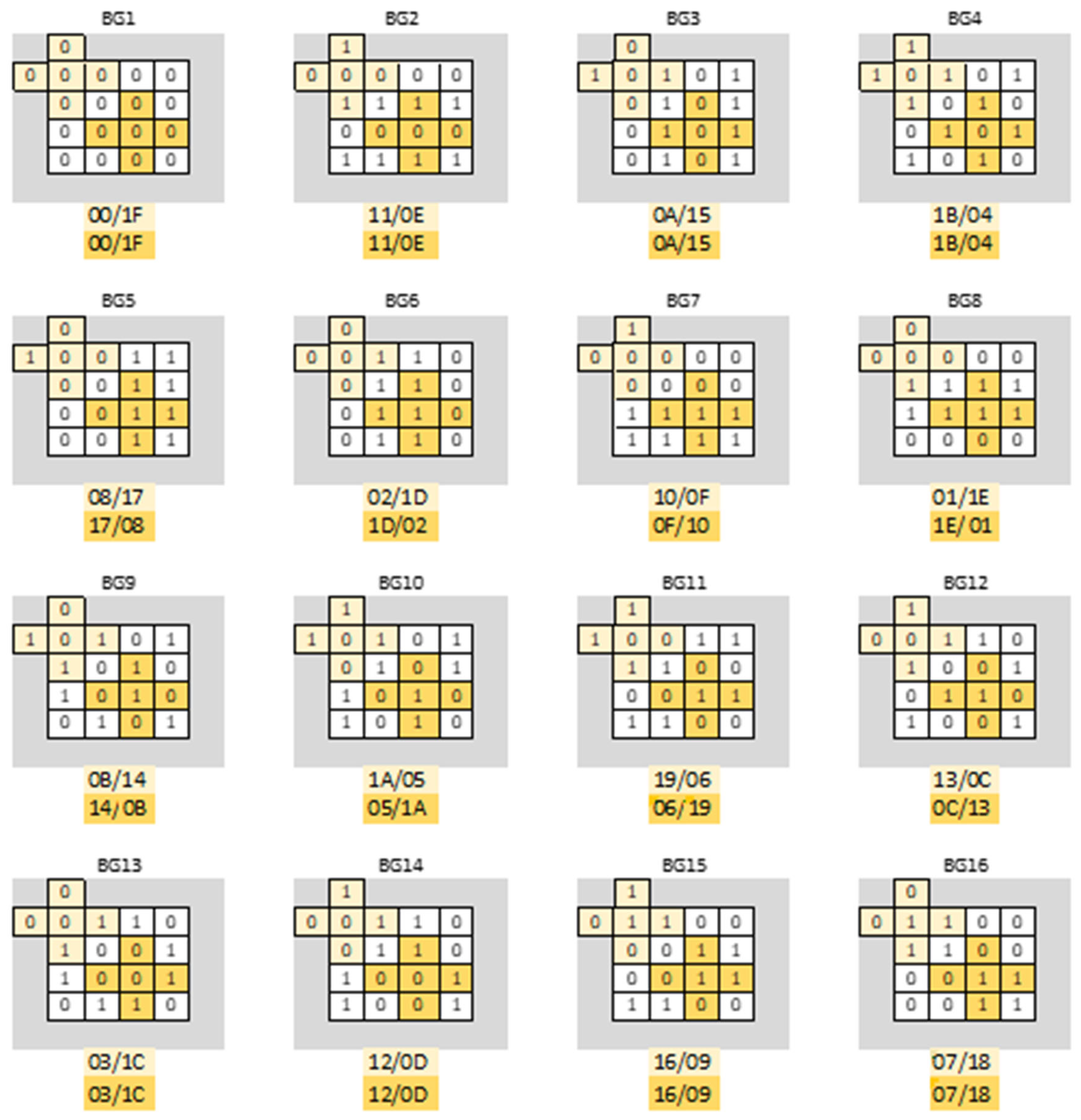

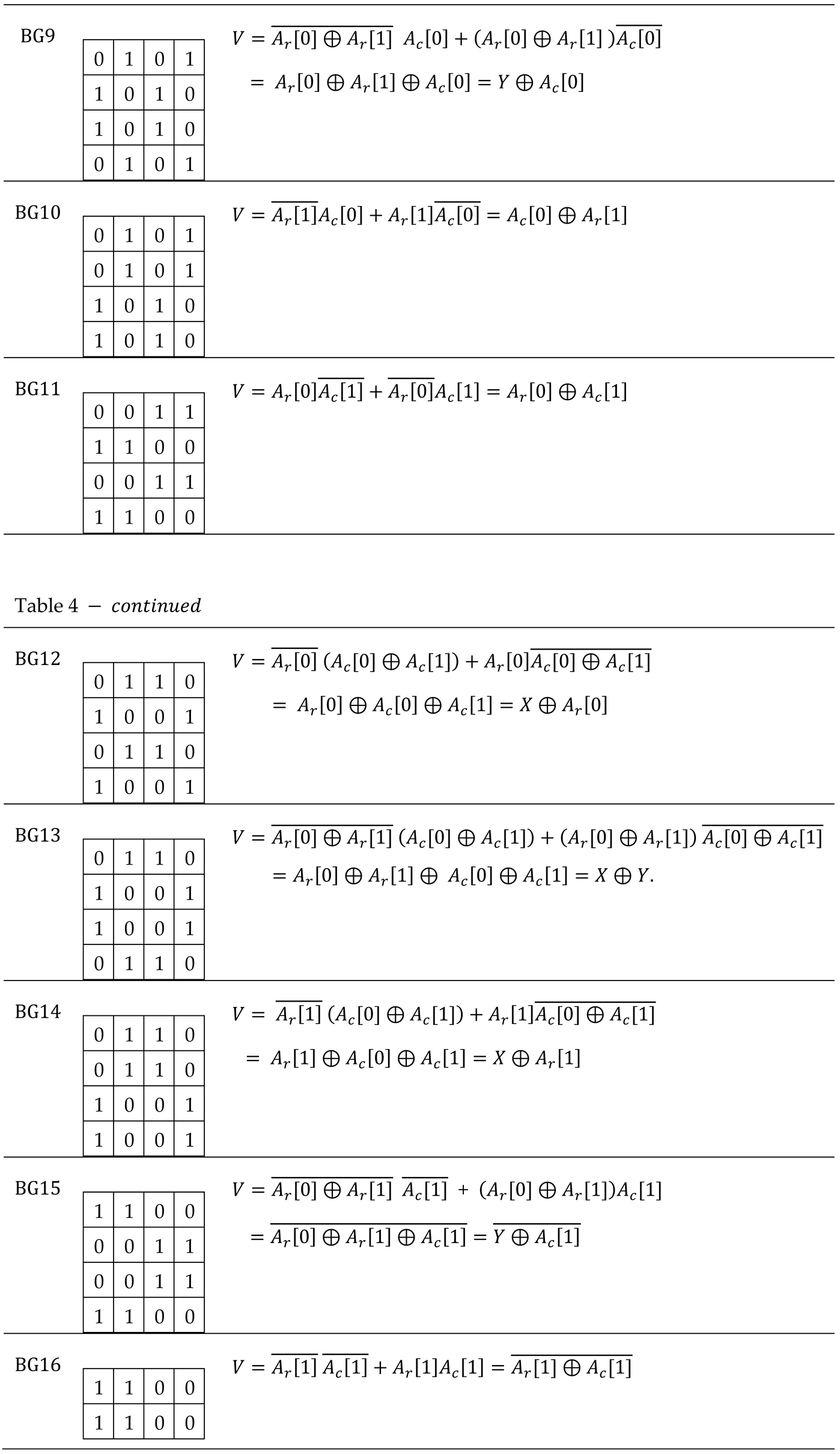

| BG1 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 |

| 1F | 1F | 1F | 1F | 1F | 1F | 1F | 1F | 1F | 1F | 1F | 1F | 1F | 1F | 1F | 1F | |

| BG2 | 11 | 11 | 11 | 11 | 0E | 0E | 0E | 0E | 11 | 11 | 11 | 0E | 0E | 11 | 0E | 0E |

| 0E | 0E | 0E | 0E | 11 | 11 | 11 | 11 | 0E | 0E | 0E | 11 | 11 | 0E | 11 | 11 | |

| BG3 | 0A | 15 | 0A | 15 | 0A | 15 | 0A | 15 | 0A | 0A | 0A | 15 | 0A | 15 | 0A | 15 |

| 15 | 0A | 15 | 0A | 15 | 0A | 15 | 0A | 15 | 15 | 15 | 0A | 15 | 0A | 15 | 0A | |

| BG4 | 1B | 04 | 1B | 04 | 04 | 1B | 04 | 1B | 1B | 04 | 1B | 04 | 04 | 1B | 04 | 1B |

| 04 | 1B | 04 | 1B | 1B | 04 | 1B | 04 | 04 | 1B | 04 | 1B | 1B | 04 | 1B | 04 | |

| BG5 | 08 | 02 | 07 | 1D | 08 | 02 | 17 | 1D | 08 | 02 | 17 | 1D | 08 | 02 | 17 | 1D |

| 17 | 1D | 08 | 02 | 17 | 1D | 08 | 02 | 17 | 1D | 08 | 02 | 17 | 1D | 08 | 02 | |

| BG6 | 02 | 17 | 1D | 08 | 02 | 17 | 1D | 08 | 02 | 17 | 1D | 08 | 02 | 17 | 1D | 08 |

| 1D | 08 | 02 | 17 | 1D | 08 | 02 | 17 | 1D | 08 | 02 | 17 | 1D | 08 | 02 | 17 | |

| BG7 | 10 | 10 | 10 | 10 | 01 | 01 | 01 | 01 | 0F | 0F | 0F | 0F | 1E | 1E | 1E | 1E |

| 0F | 0F | 0F | 0F | 1E | 1E | 1E | 1E | 10 | 10 | 10 | 10 | 01 | 01 | 01 | 01 | |

| BG8 | 01 | 01 | 01 | 01 | 0F | 0F | 0F | 0F | 1E | 1E | 01 | 1E | 10 | 10 | 10 | 10 |

| 1E | 1E | 1E | 1E | 10 | 10 | 10 | 10 | 01 | 01 | 1E | 01 | 0F | 0F | 0F | 0F | |

| BG9 | 0B | 14 | 0B | 14 | 05 | 1A | 05 | 1A | 14 | 0B | 14 | 0B | 1A | 05 | 1A | 05 |

| 14 | 0B | 14 | 0B | 1A | 05 | 1A | 05 | 0B | 14 | 0B | 14 | 05 | 1A | 05 | 1A | |

| BG10 | 1A | 05 | 1A | 05 | 0B | 14 | 0B | 14 | 05 | 1A | 05 | 1A | 14 | 0B | 14 | 0B |

| 05 | 1A | 05 | 1A | 14 | 0B | 14 | 0B | 1A | 05 | 1A | 05 | 0B | 14 | 0B | 14 | |

| BG11 | 19 | 13 | 06 | 0C | 06 | 0C | 19 | 13 | 19 | 13 | 06 | 0C | 06 | 0C | 19 | 13 |

| 06 | 0C | 19 | 13 | 19 | 13 | 06 | 0C | 06 | 0C | 19 | 13 | 19 | 13 | 06 | 0C | |

| BG12 | 13 | 06 | 0C | 19 | 0C | 19 | 13 | 06 | 13 | 06 | 0C | 19 | 0C | 19 | 13 | 06 |

| 0C | 19 | 13 | 06 | 13 | 06 | 0C | 19 | 0C | 19 | 13 | 06 | 13 | 06 | 0C | 19 | |

| BG13 | 03 | 16 | 1C | 09 | 0D | 18 | 12 | 07 | 1C | 09 | 03 | 16 | 12 | 07 | 0D | 18 |

| 1C | 09 | 03 | 16 | 12 | 07 | 0D | 18 | 03 | 16 | 1C | 09 | 0D | 18 | 12 | 07 | |

| BG14 | 12 | 07 | 0D | 18 | 03 | 16 | 1C | 09 | 0D | 18 | 12 | 07 | 1C | 09 | 03 | 16 |

| 0D | 18 | 12 | 07 | 1C | 09 | 03 | 16 | 12 | 07 | 0D | 18 | 03 | 16 | 1C | 09 | |

| BG15 | 16 | 1C | 09 | 03 | 18 | 12 | 07 | 0D | 09 | 03 | 16 | 1C | 07 | 0D | 18 | 12 |

| 09 | 03 | 16 | 1C | 07 | 0D | 18 | 12 | 16 | 1C | 09 | 03 | 18 | 12 | 07 | 0D | |

| BG16 | 07 | 0D | 18 | 12 | 16 | 1C | 09 | 03 | 18 | 12 | 07 | 0D | 09 | 03 | 16 | 1C |

| 18 | 12 | 07 | 0D | 09 | 03 | 16 | 1C | 07 | 0D | 18 | 12 | 16 | 1C | 09 | 03 | |

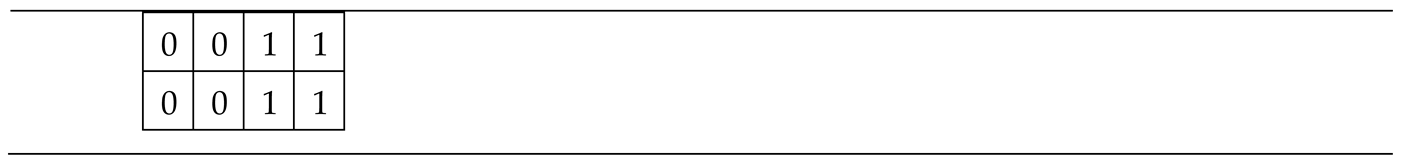

| Fulfillment of equation (5) |

|

| 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).