Introduction

One of the most significant technological breakthroughs in the electronics world at the end of the 20th century was the development of a new process technology – SiGe BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor), which combines the advantages of high-speed bipolar transistors and CMOS- structures. This process technology [

1,

2,

3,

4,

5,

6,

7,

8] serves as the foundation for creating electronic components for system-on-chip solutions, which have become the basis for a new generation of devices and telecommunications equipment (radar systems, cellular and satellite communications, navigation systems, etc.). Originally developed by IBM, this technology is now widely used worldwide and continues to evolve, with leading microelectronics companies such as Intel, Intersil, Motorola, Texas Instruments, and TSMC contributing to its advancement. The reason for its widespread adoption lies in its combination of high-performance characteristics, reliability comparable to conventional silicon-based devices, and cost-effectiveness. [

9]

The purpose and novelty of this article is to summarize the fundamental properties and provide a comparative analysis of 24 modified SiGe BiCMOS output stages of operational amplifiers (Op-Amps) with an operating temperature range up to 250°C.

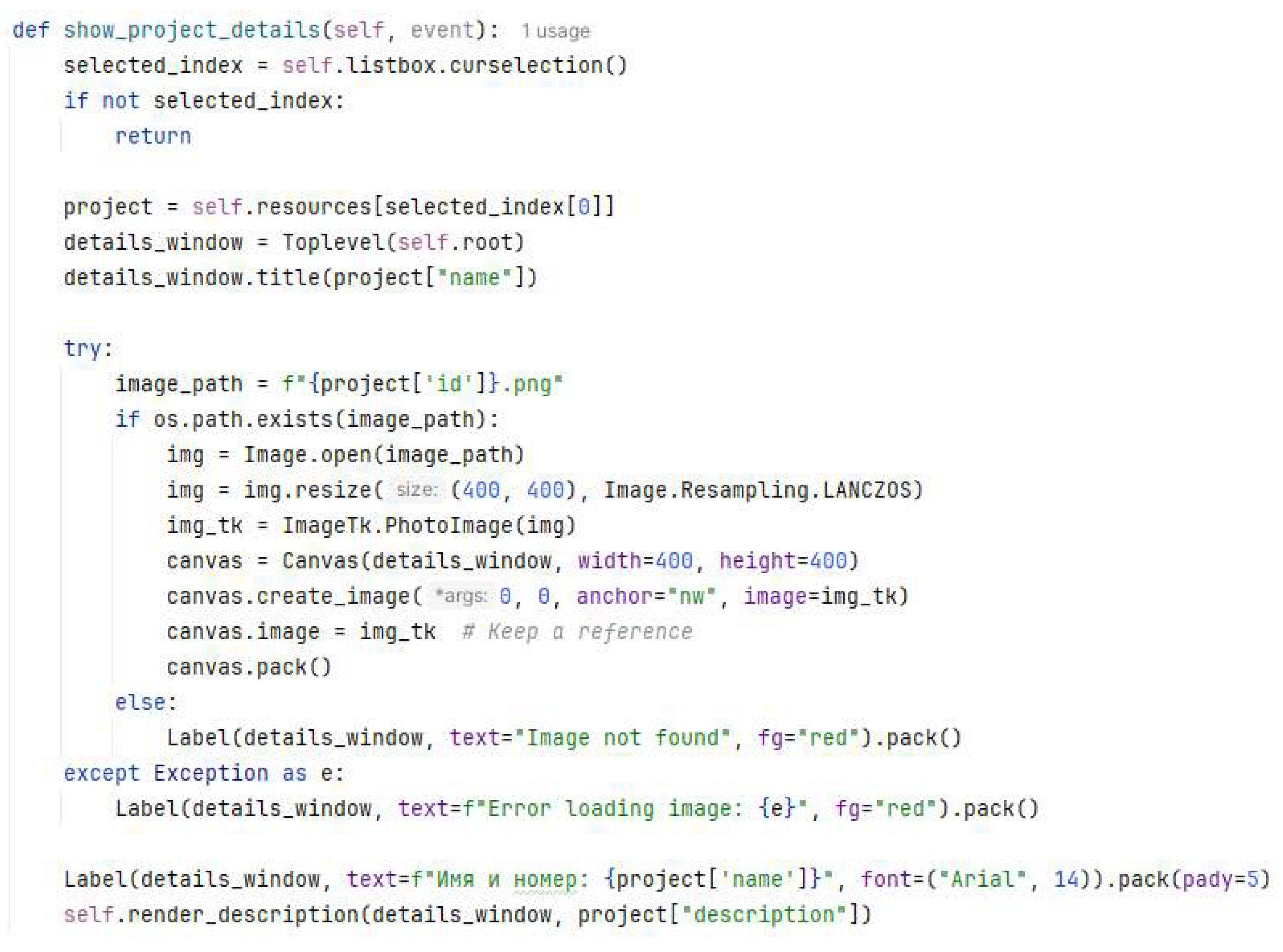

A cataloging and visualization program for OS of high-temperature Op-Amps based on heterojunction n-p-n bipolar and n- and p-channel metal-oxide-semiconductor field-effect transistors

To select the optimal circuit design solution for a specific Op-Amp implementation, a buffer amplifiers (BA) cataloging program was developed (

Figure 1). This program represents an interactive platform containing electrical schematics adapted for SiGe technology processes, utilizing exclusively heterojunction n-p-n bipolar and CMOS transistors.

Figure 1.

Fragment of the BA cataloging and visualization program description file.

Figure 1.

Fragment of the BA cataloging and visualization program description file.

This program solves the following problems:

- cataloging of circuits with a description of their operation;

- graphical visualization of the selected circuit solution with displaying the numbering of components and their connections (as in

Figure 2).

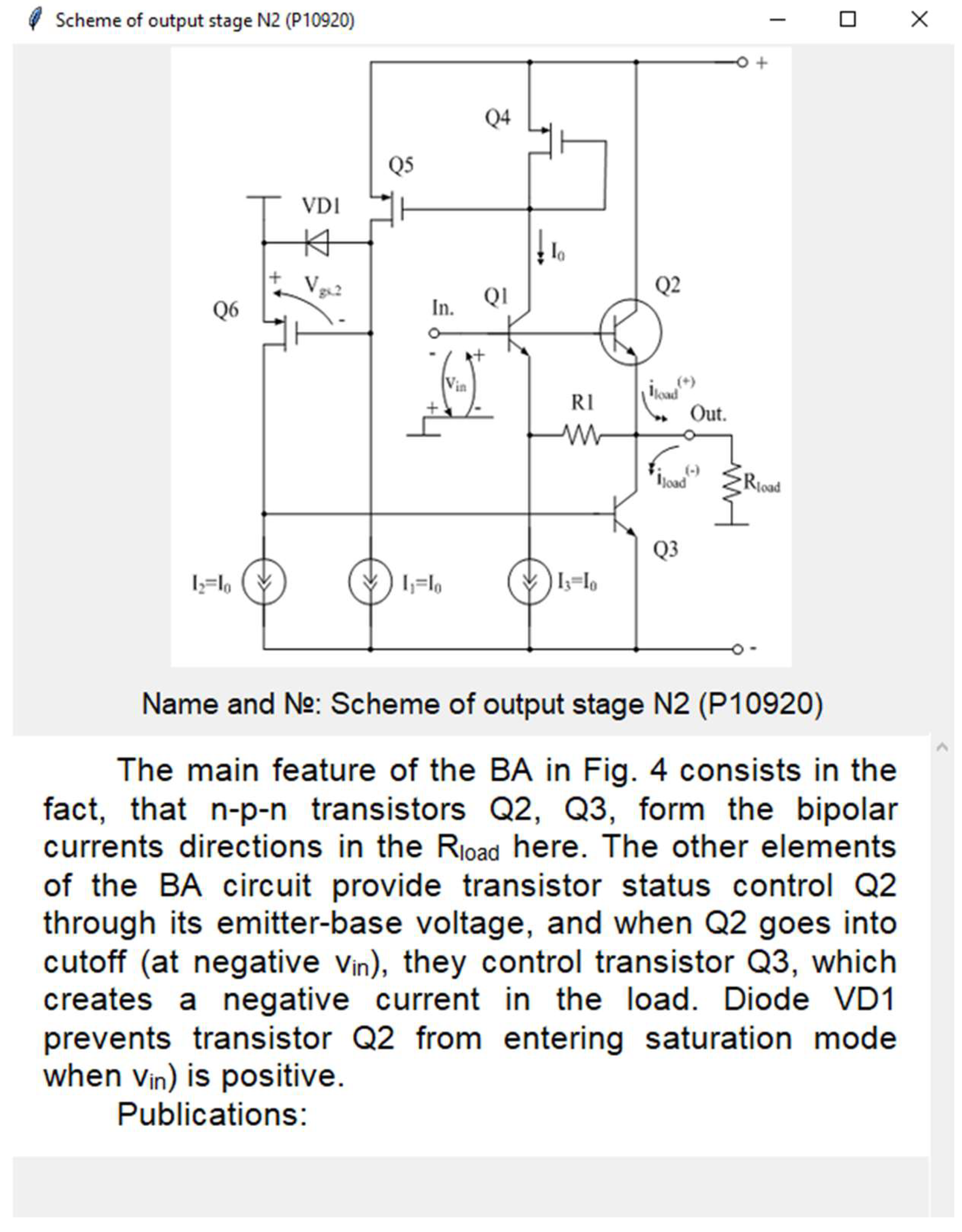

Figure 2.

Basic scheme information window.

Figure 2.

Basic scheme information window.

Thus, the program as an effective tool for designers of high-temperature SiGe Op-Amps, enabling optimization of the output stage (BA) selection process while accounting for its circuit design characteristics.

Buffer amplifier circuits for high-temperature Op-Amps using heterojunction n-p-n bipolar and CMOS transistors, as implemented in the program

When calculating the maximum output currents of the BA (

and

) for the considered circuits, it should be taken into account that in real Op-Amps circuits, the signal source connected to the BA input (In.) is not an ideal voltage source with zero output impedance. Consequently, the separate stage (SS) limits the maximum possible load currents values. Therefore, when evaluating

and

for specific circuits (measured at R

load=0), the maximum possible output currents

and

of the separate stage SS must be taken into account. In

Figure 3 shows a BA circuit with non-ideal SS signal source.

Figure 3.

On the operation of the BA with a non-ideal signal source SS.

Figure 3.

On the operation of the BA with a non-ideal signal source SS.

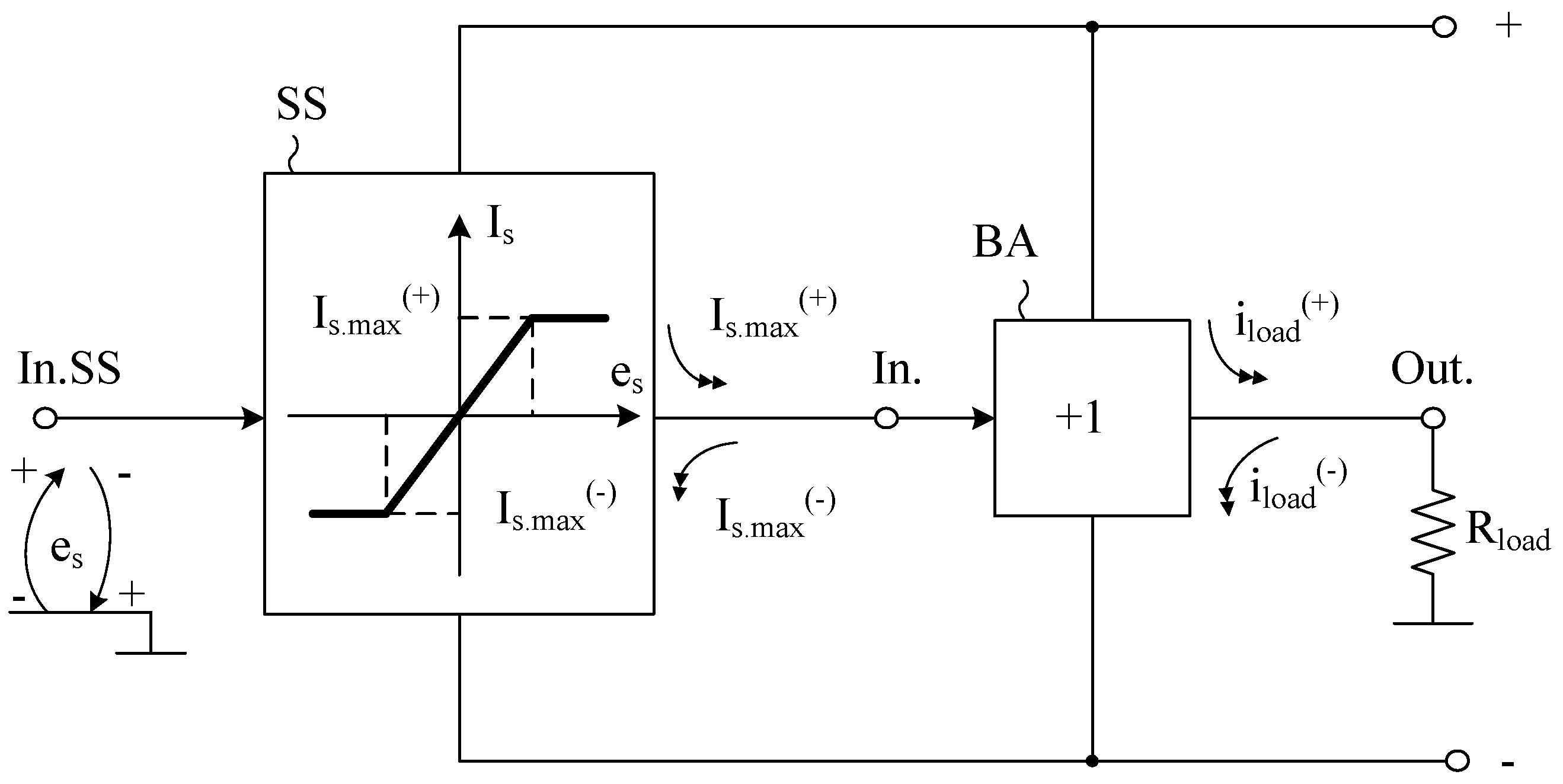

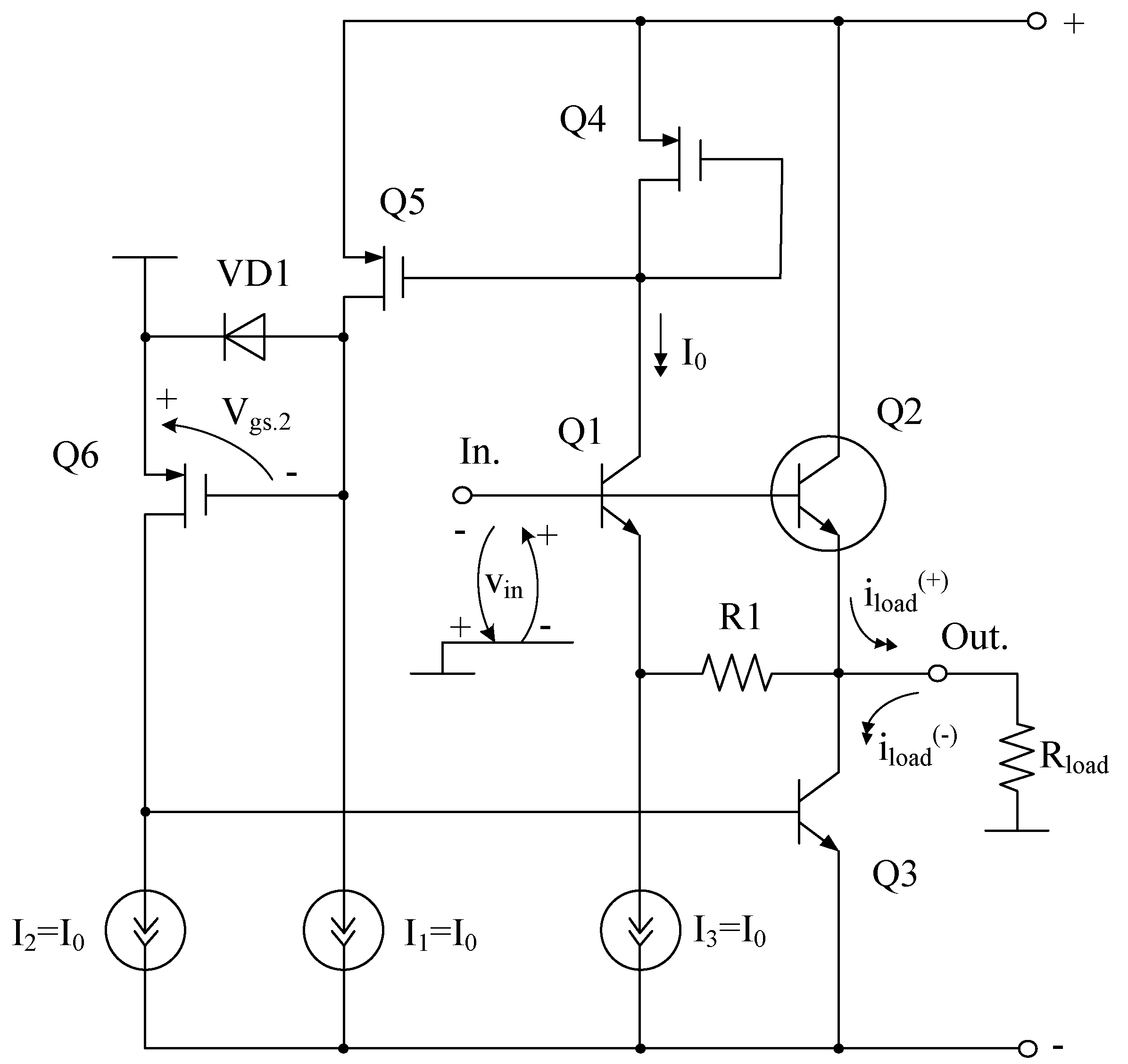

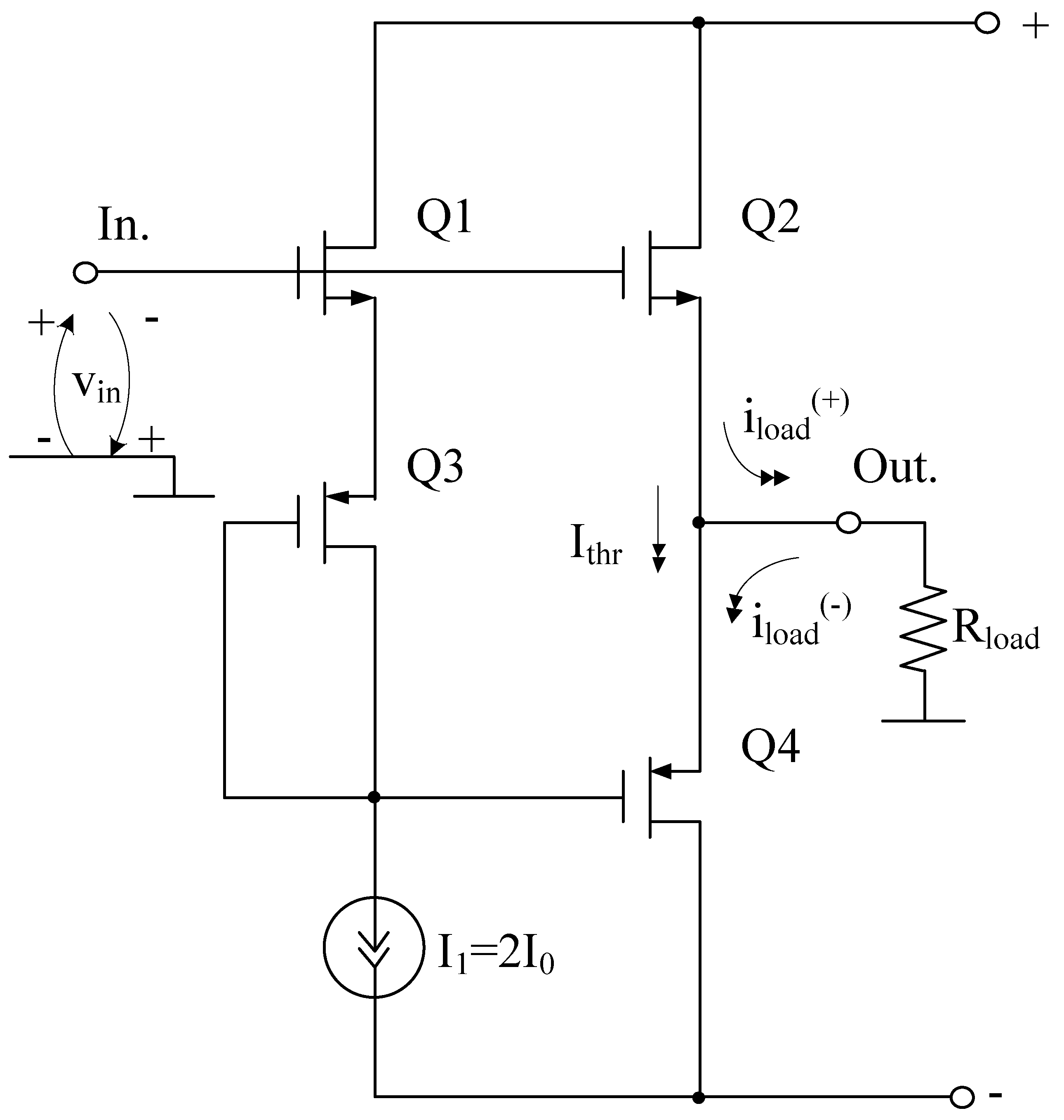

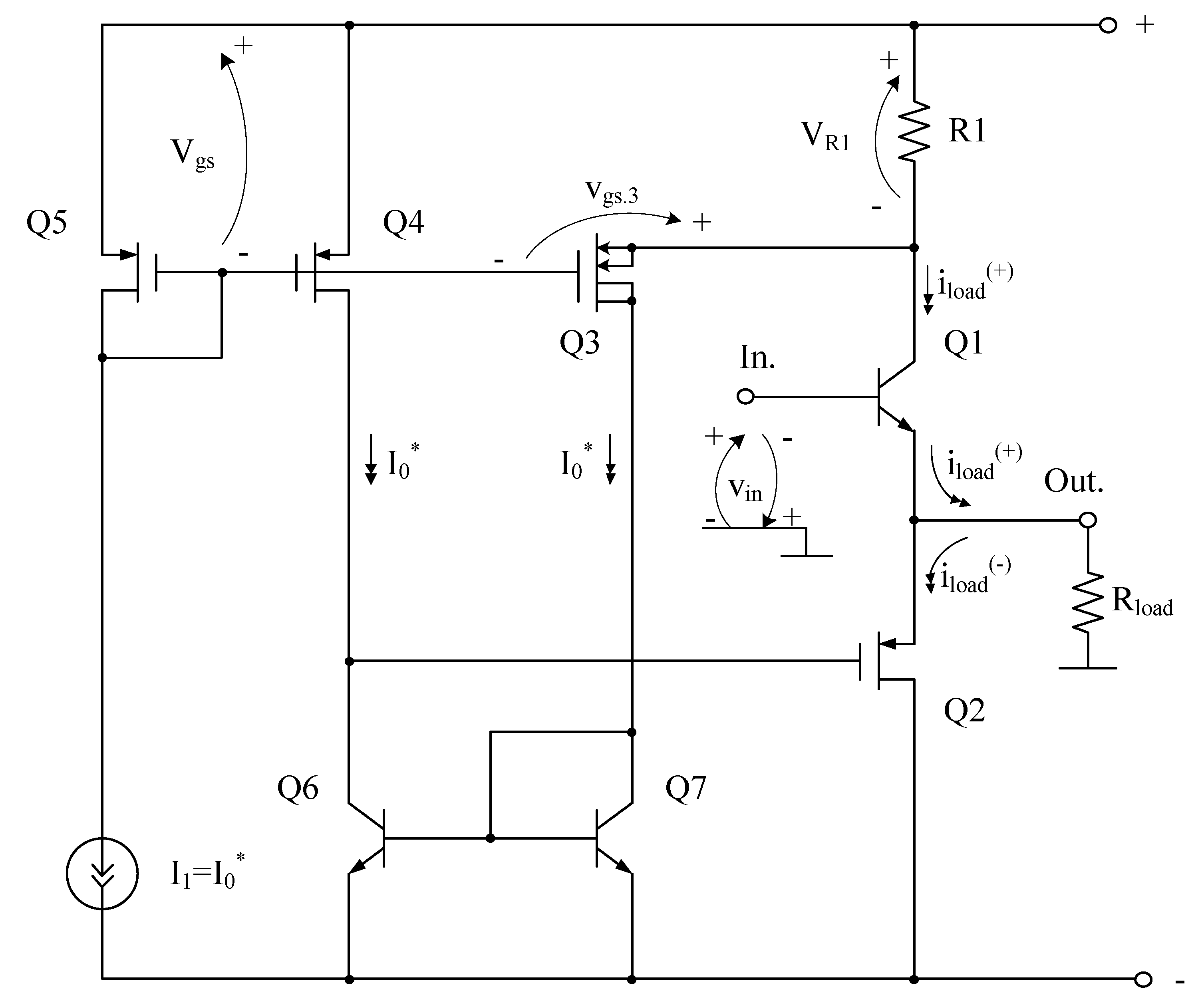

The main feature of the BA in

Figure 4 consists in the fact, that n-p-n transistors Q2, Q3, form the bipolar currents directions in the R

load load here. The other elements of the BA circuit provide transistor status control Q2 through its emitter-base voltage, and when Q2 goes into cutoff (at negative v

in), they control transistor Q3, which creates a negative current in the load. Diode VD1 prevents transistor Q2 from entering saturation mode when v

in is positive.

Figure 4.

SiGe buffer amplifier: modification №1.

Figure 4.

SiGe buffer amplifier: modification №1.

The setting of the BA circuit in

Figure 4 is provided by selection of resistor R2 and currents I

1=I

2=I

3. In this case, the maximum values of currents in the load

and

are determined by the formulas:

where

– transistor base current gain Q2,

– maximum possible value of SS (

Figure 3) output current with positive v

in,

– maximum collector current Q3.

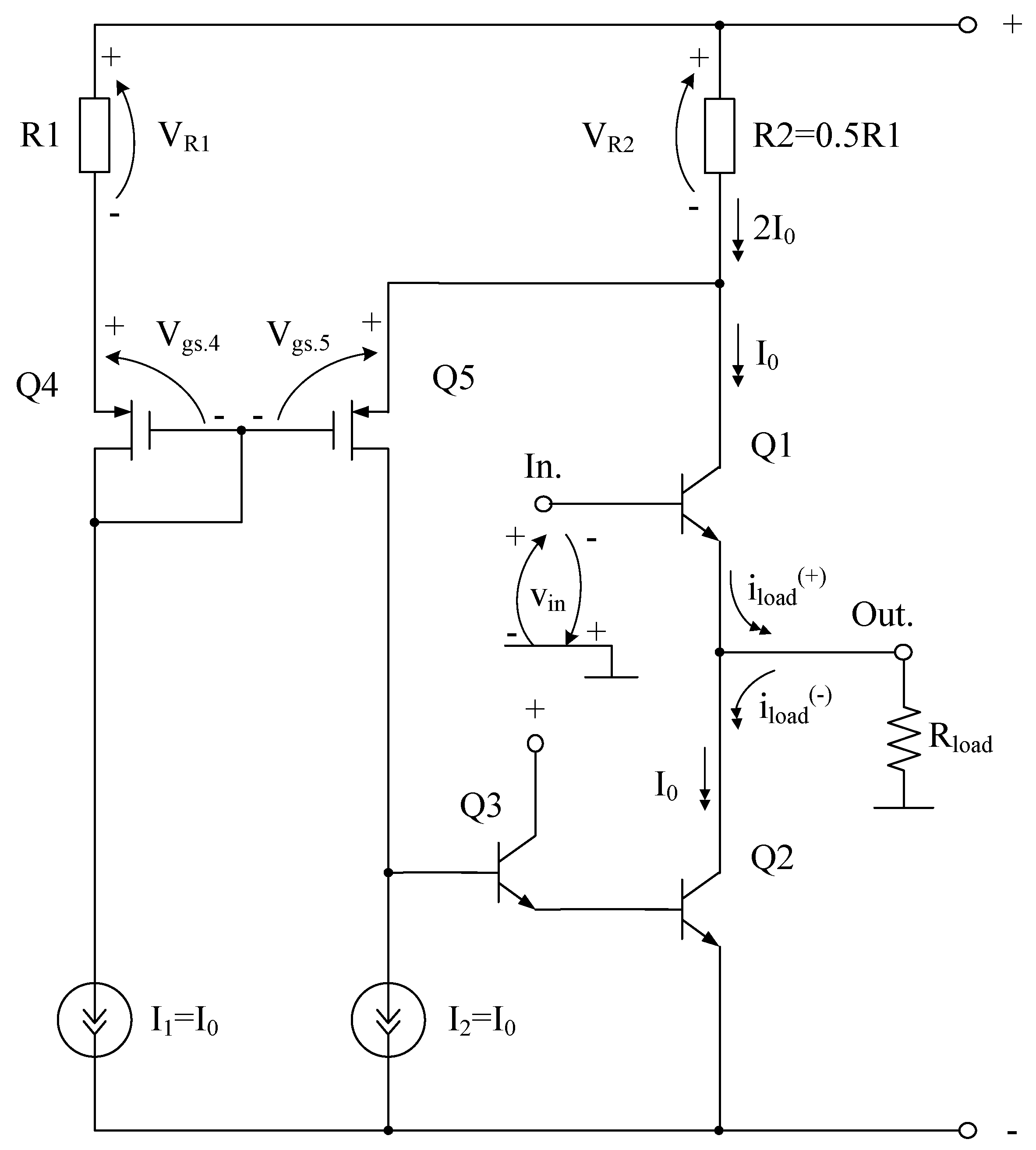

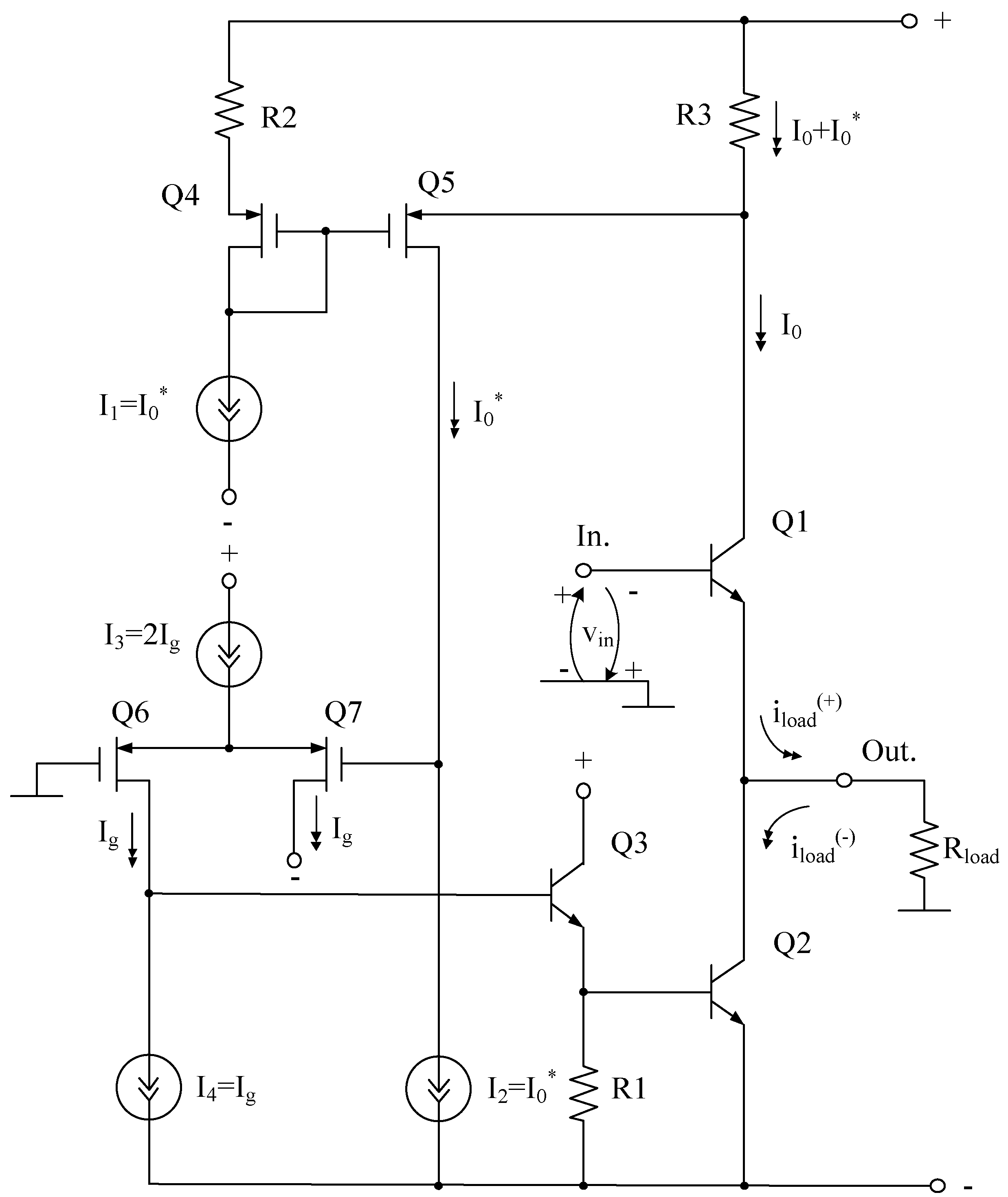

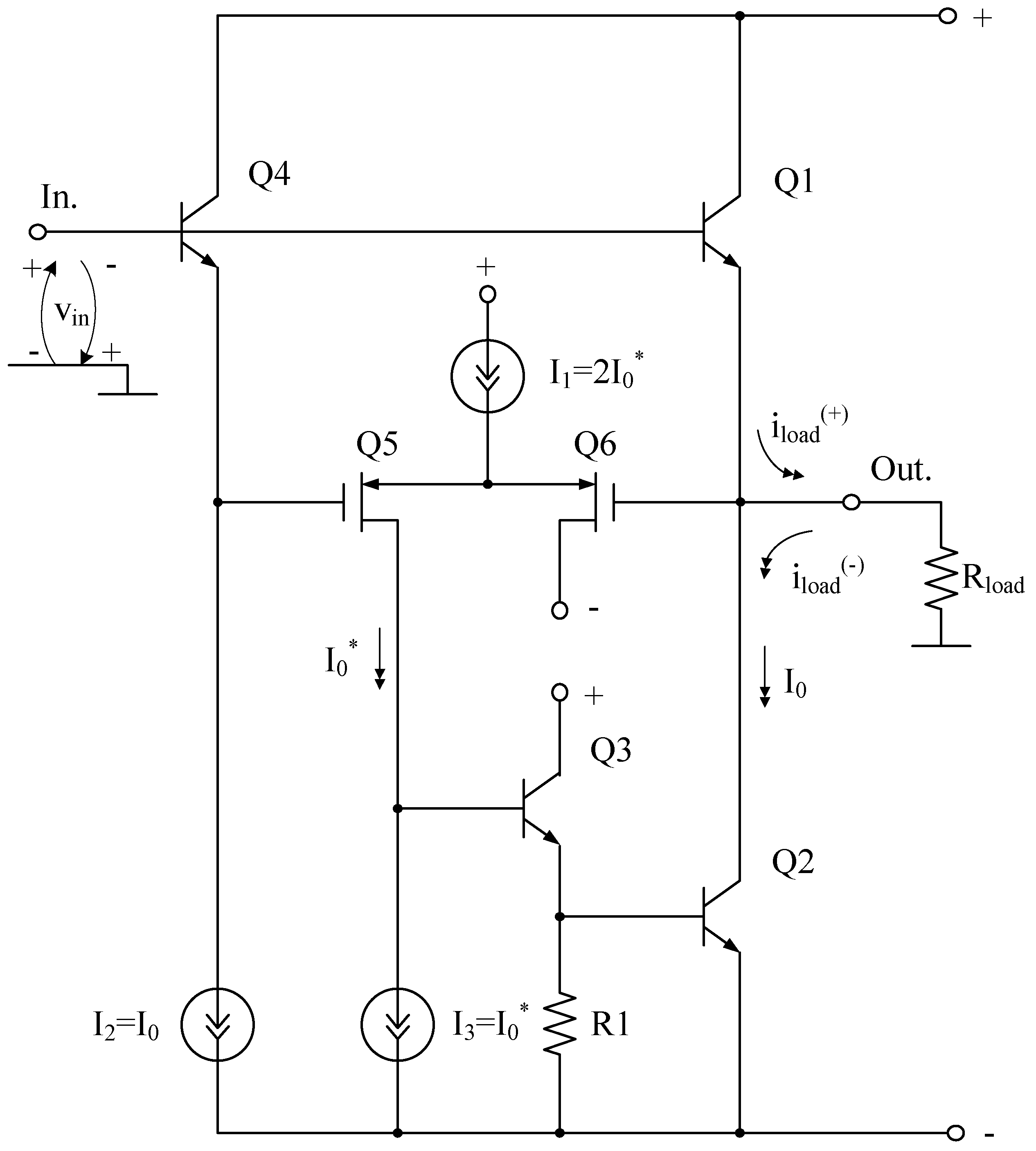

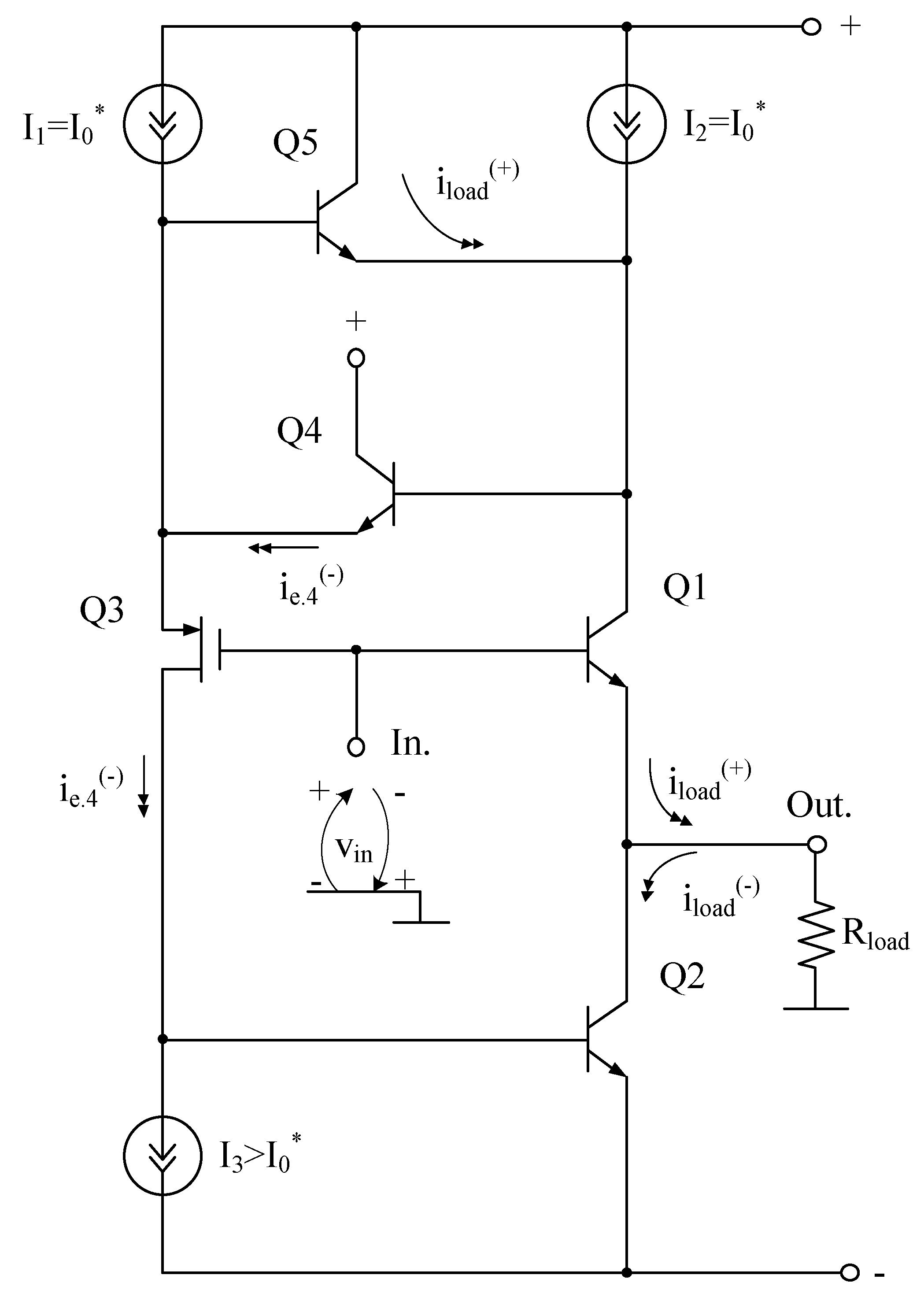

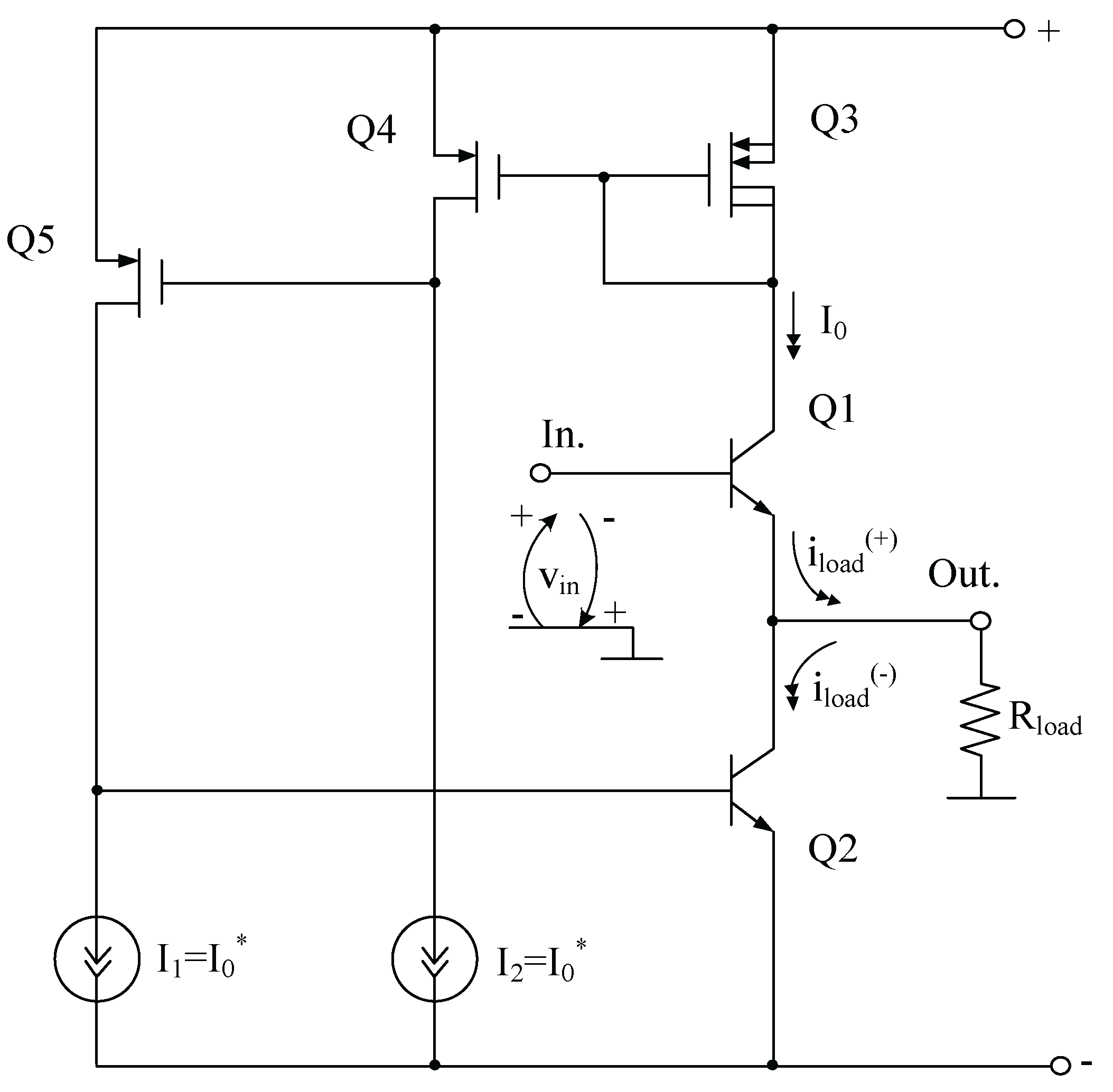

The feature of BA (

Figure 5) is that the bipolar directions of the currents in the R

load are here formed by n-p-n transistors Q1, Q2, Q3 and depend on the current I

0. Other elements of the BA circuit provide control of the state of transistors Q2 and Q3, and when Q1 goes into cutoff (at negative v

in), they control transistors Q2 and Q3, which create negative current in the load. Adjustment of the BA circuit is provided by selection of resistances of resistors R1÷R2 and currents I

1=I

2.

Figure 5.

SiGe buffer amplifier: modification №2.

Figure 5.

SiGe buffer amplifier: modification №2.

In this case

and

are determined by the formulas:

where

– base current gain coefficients of bipolar transistors Q1÷Q3,

– maximum possible value of SS (

Figure 3) output current with positive v

in,

– source current I

1.

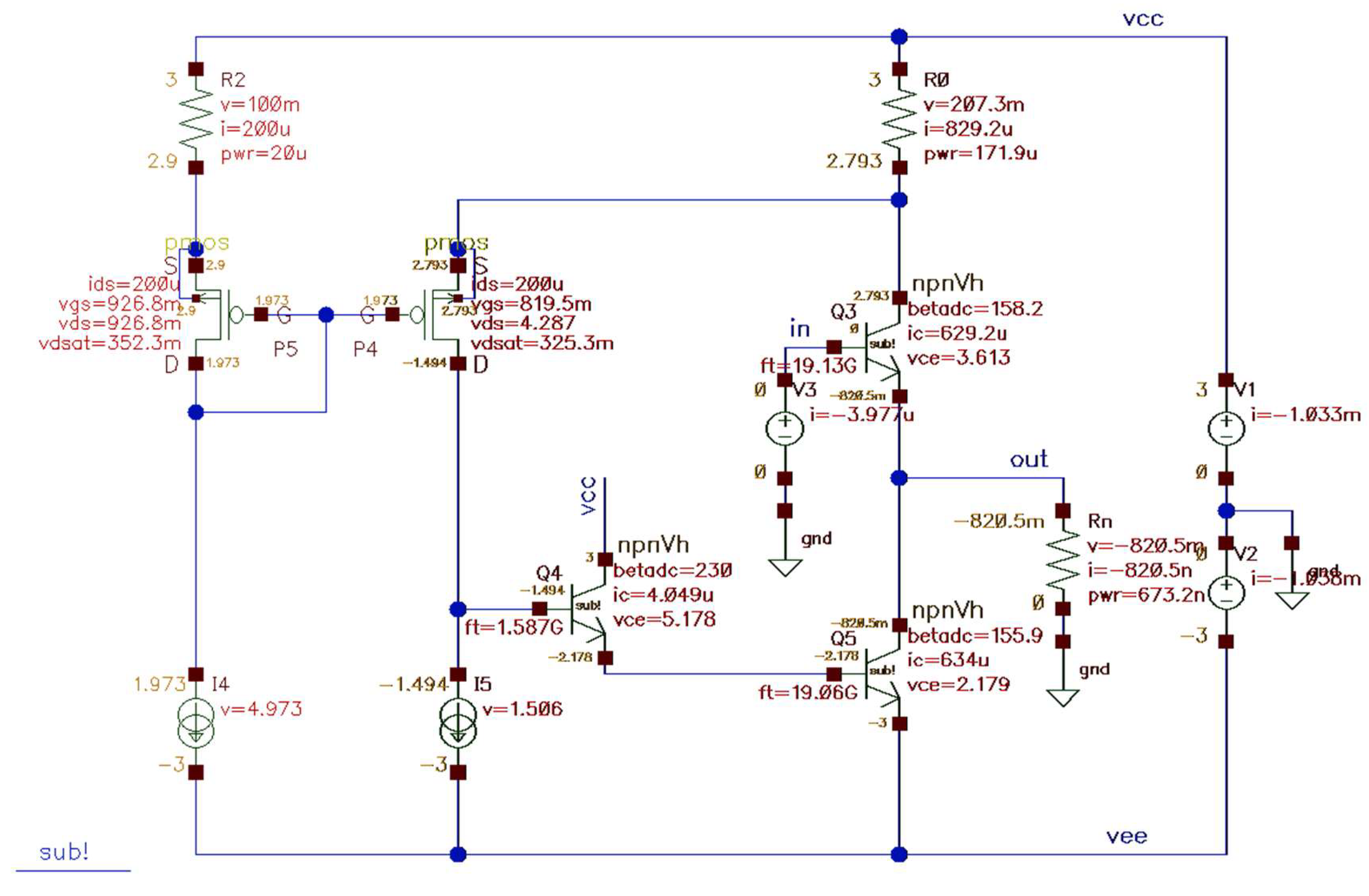

Figure 6 shows the static mode of BA

Figure 5 in Cadance simulation software at I

4=I

5=200 µA, resistors R2=500 Ω and R0=250 Ω, supply voltages ±3 V.

Figure 6.

Static mode of SiGe BA Fig.5 (modification №2) at t=27 oC.

Figure 6.

Static mode of SiGe BA Fig.5 (modification №2) at t=27 oC.

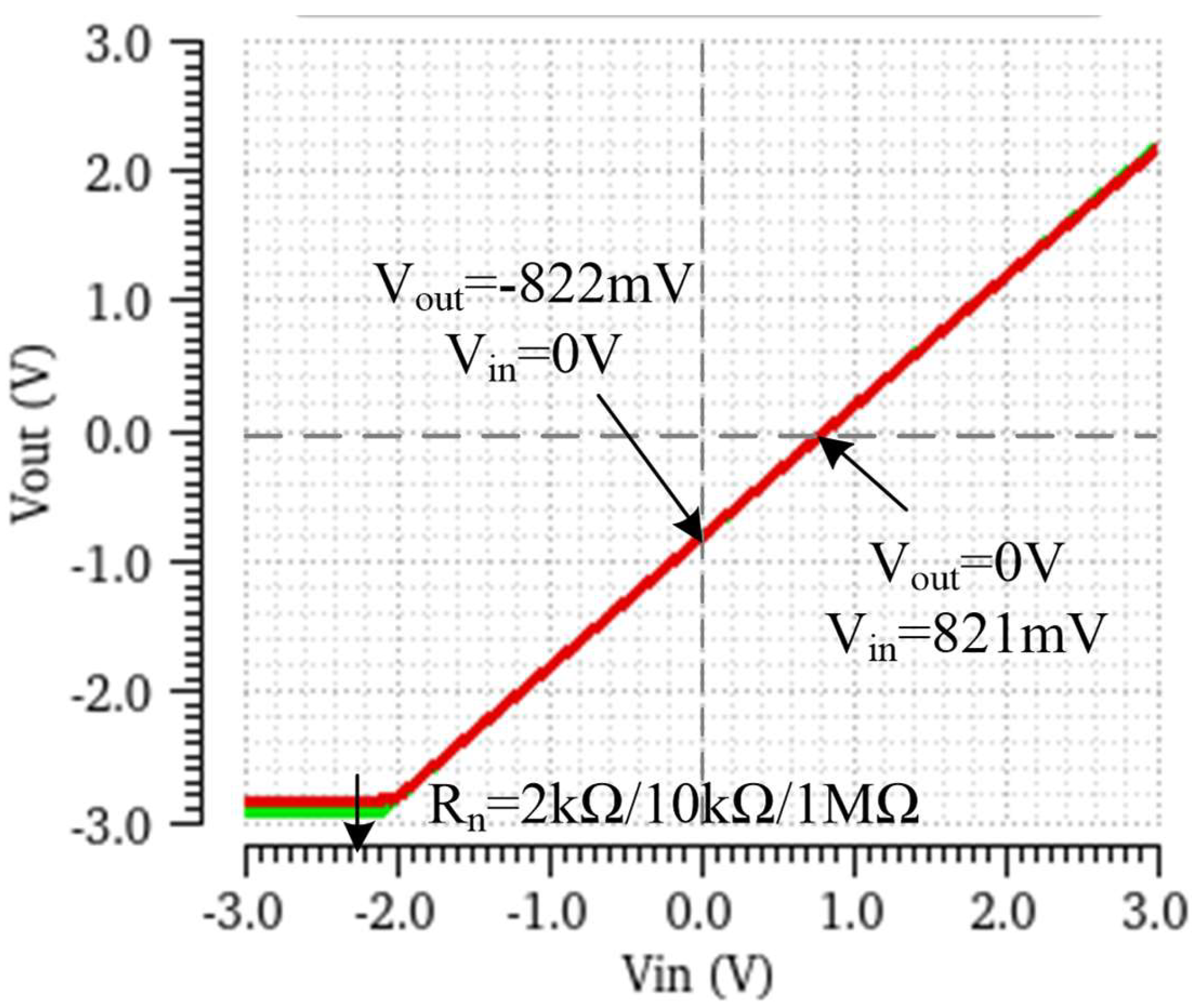

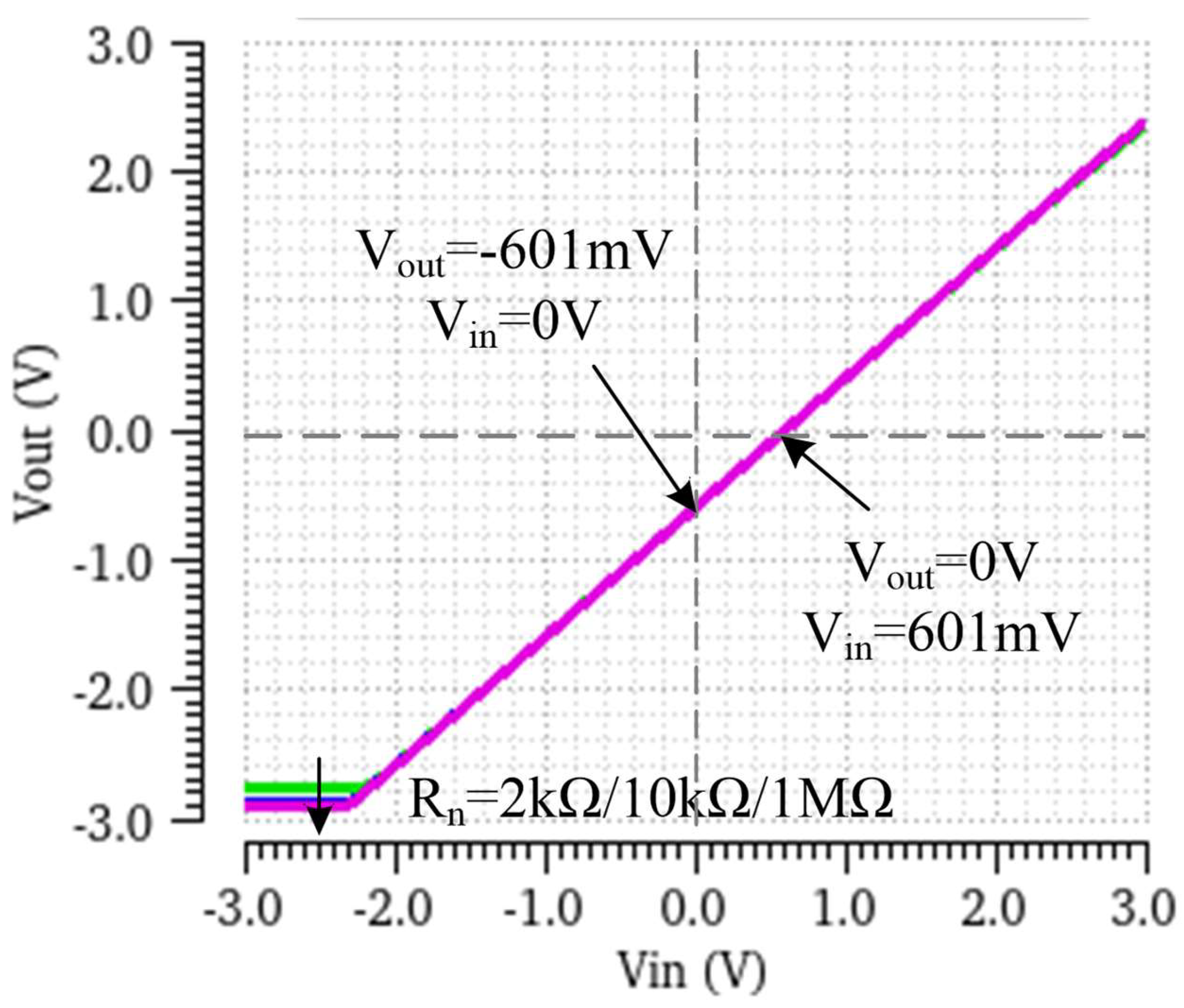

Figure 7 shows the amplitude characteristic of BA

Figure 6 at different load resistances R

load.

Figure 7.

Amplitude characteristic of SiGe BA in

Figure 6 at R

load=2 kΩ, 10 kΩ, t=27

oC.

Figure 7.

Amplitude characteristic of SiGe BA in

Figure 6 at R

load=2 kΩ, 10 kΩ, t=27

oC.

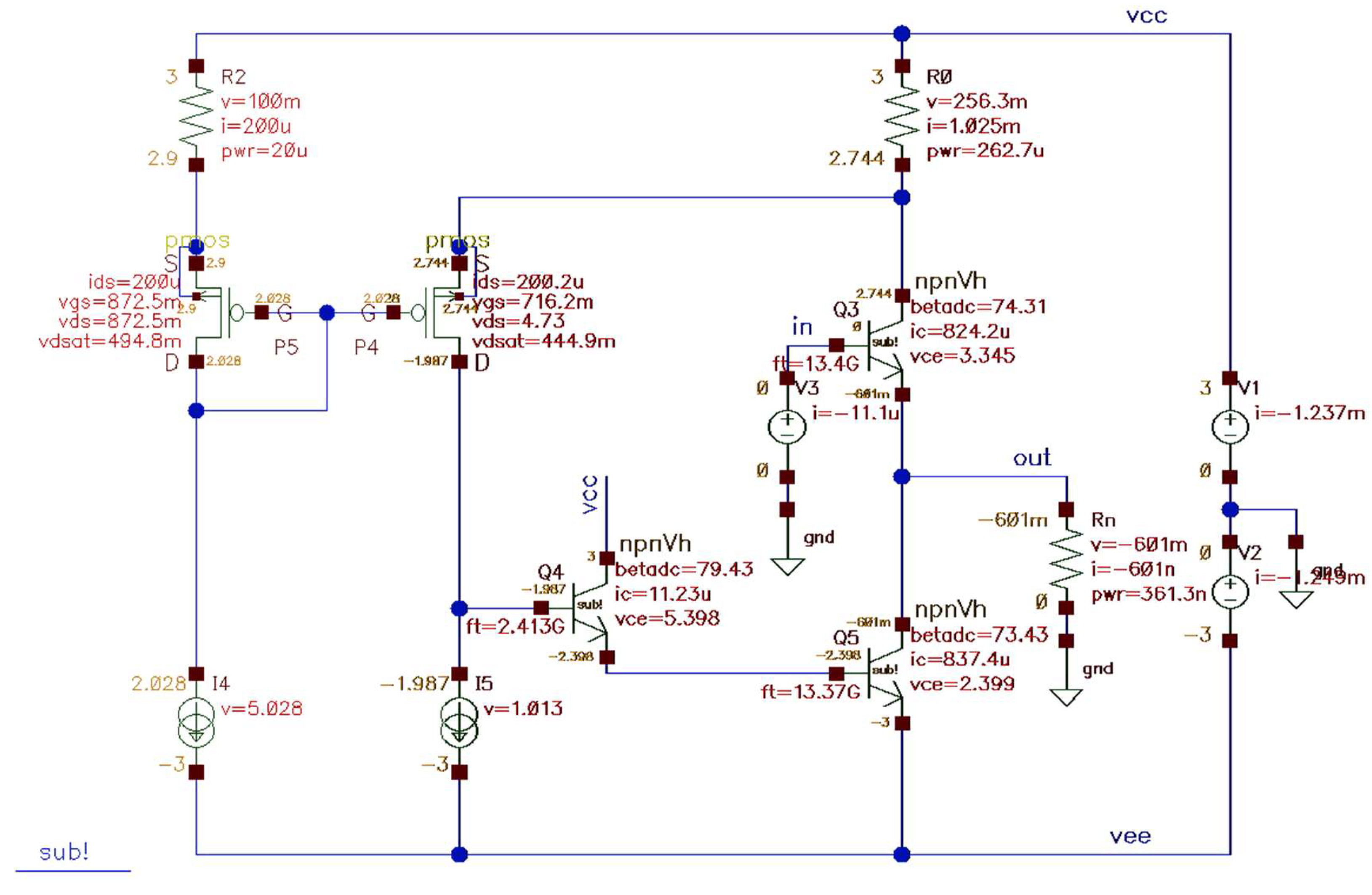

Figure 8 shows the static mode of BA

Figure 5 in Cadance simulation software at t=250

oC, I

4=I

5=200 µA, resistors R2=500 Ω and R0=250 Ω, supply voltages ±3 V.

Figure 8.

Static mode of SiGe BA Fig.5 (modification №2) at t=250 oC.

Figure 8.

Static mode of SiGe BA Fig.5 (modification №2) at t=250 oC.

Figure 9 shows the amplitude characteristic of BA

Figure 8 at different load resistances R

load.

Figure 9.

Amplitude characteristic of SiGe BA in

Figure 8 at R

load=2 kΩ, 10 kΩ, 1 MΩ, t=250

oC.

Figure 9.

Amplitude characteristic of SiGe BA in

Figure 8 at R

load=2 kΩ, 10 kΩ, 1 MΩ, t=250

oC.

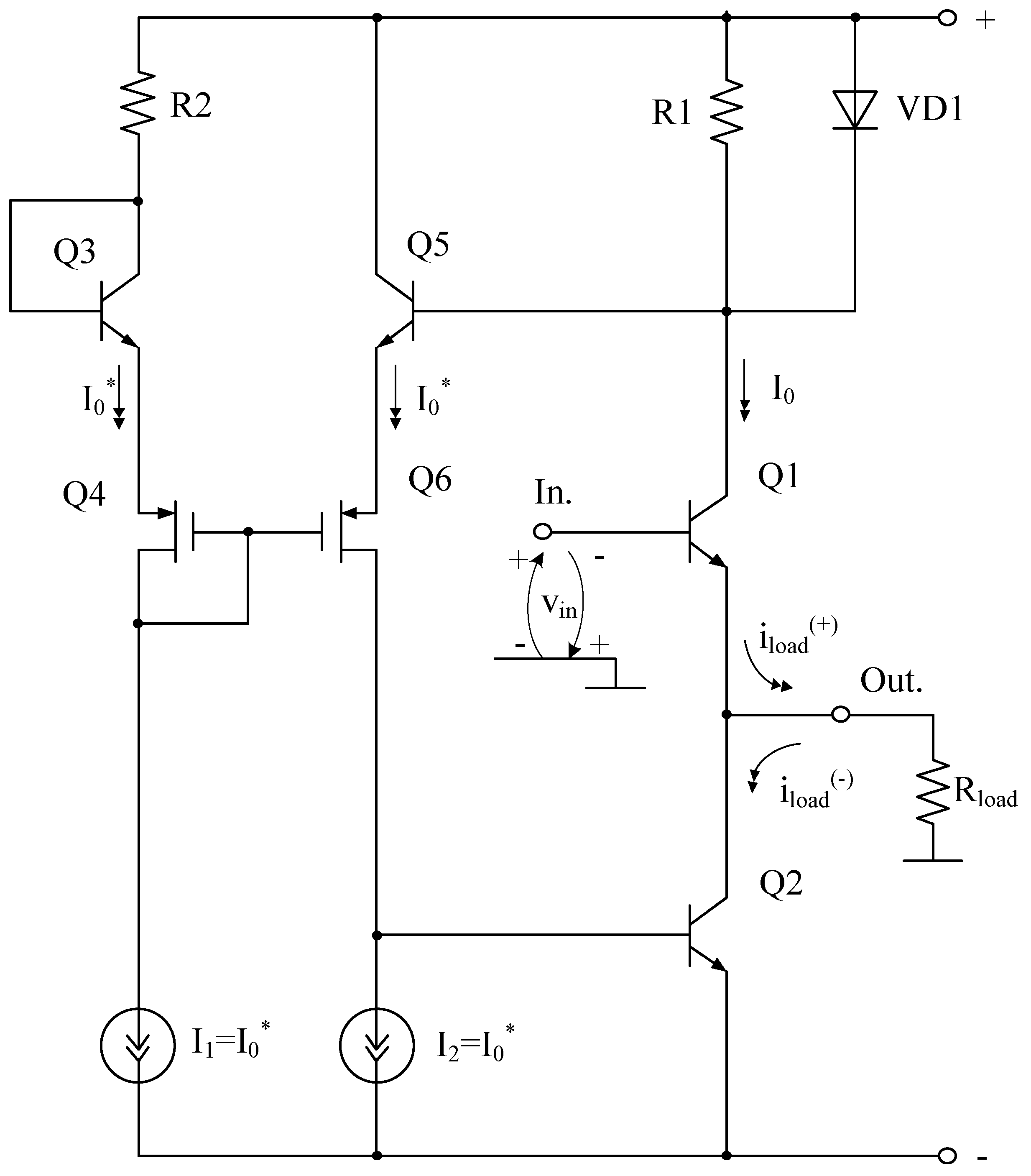

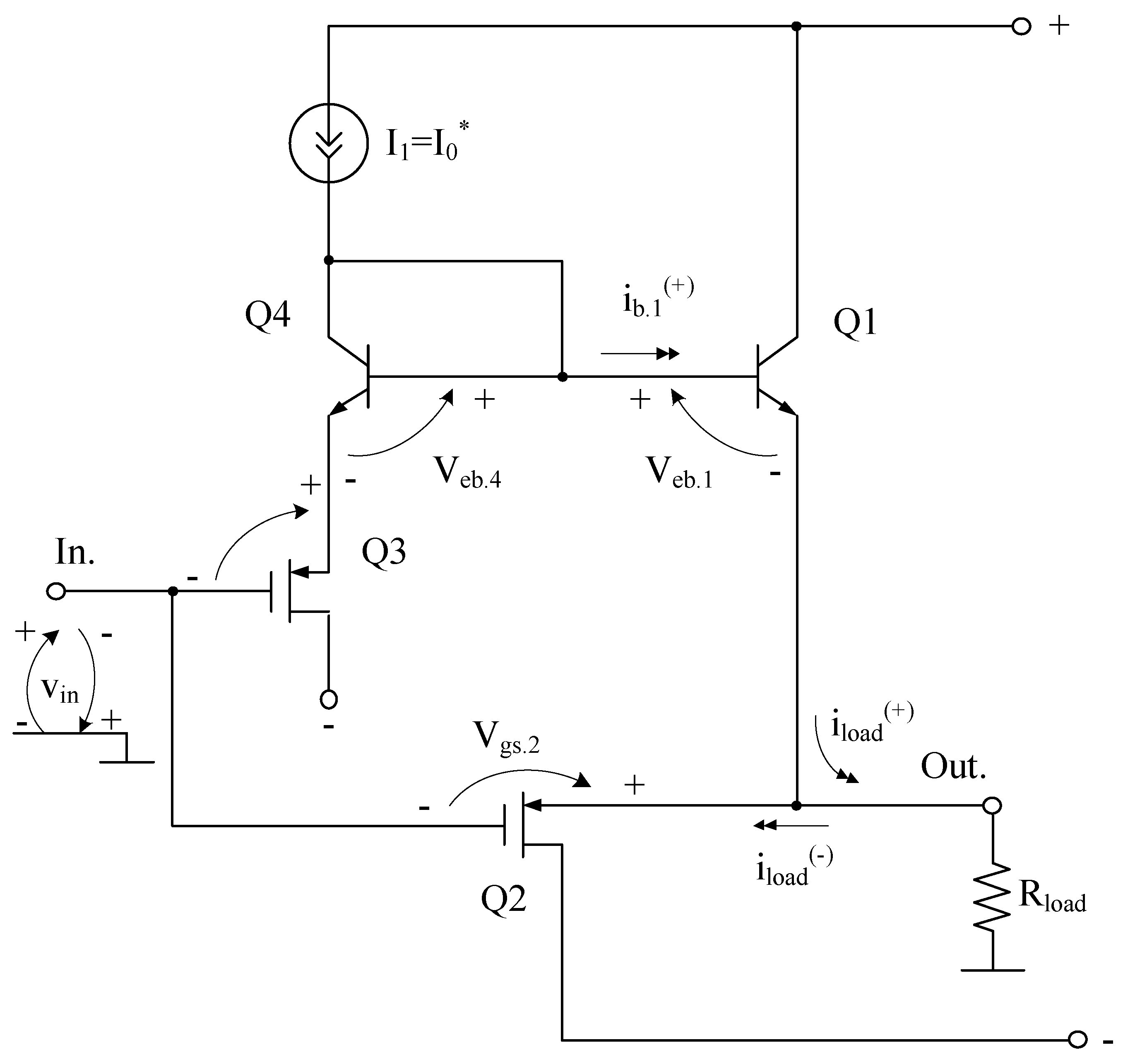

In circuit BA in

Figure 10, the bipolar current directions in the R

load are formed by n-p-n transistors Q1, Q2, Q3. Other elements of the BA circuit provide state monitoring of transistor Q1 and, when Q1 goes into cutoff (at negative v

in), control transistors Q2 and Q3, which create a negative current in the load. Setting of the BA circuit is provided by selection of resistors R1÷R3 and reference currents I

1÷I

4.

Figure 10.

SiGe buffer amplifier: modification №3.

Figure 10.

SiGe buffer amplifier: modification №3.

In this case

and

are determined by the formulas:

where

– base current gain coefficients of bipolar transistors Q1÷Q3,

– maximum possible value of SS (

Figure 3) output current with positive v

in,

– current, seted by the source I

3 (I

3=2I

g).

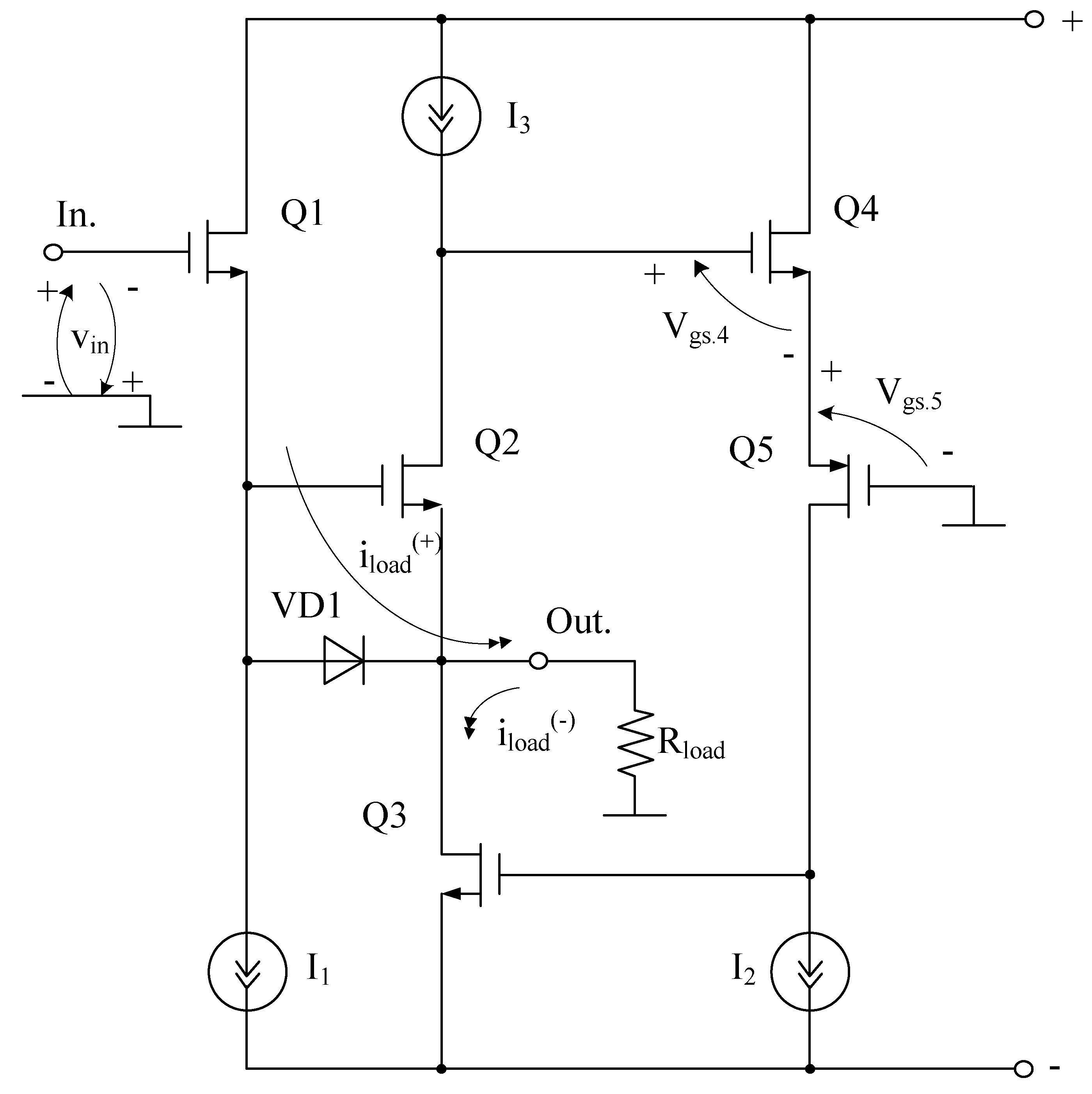

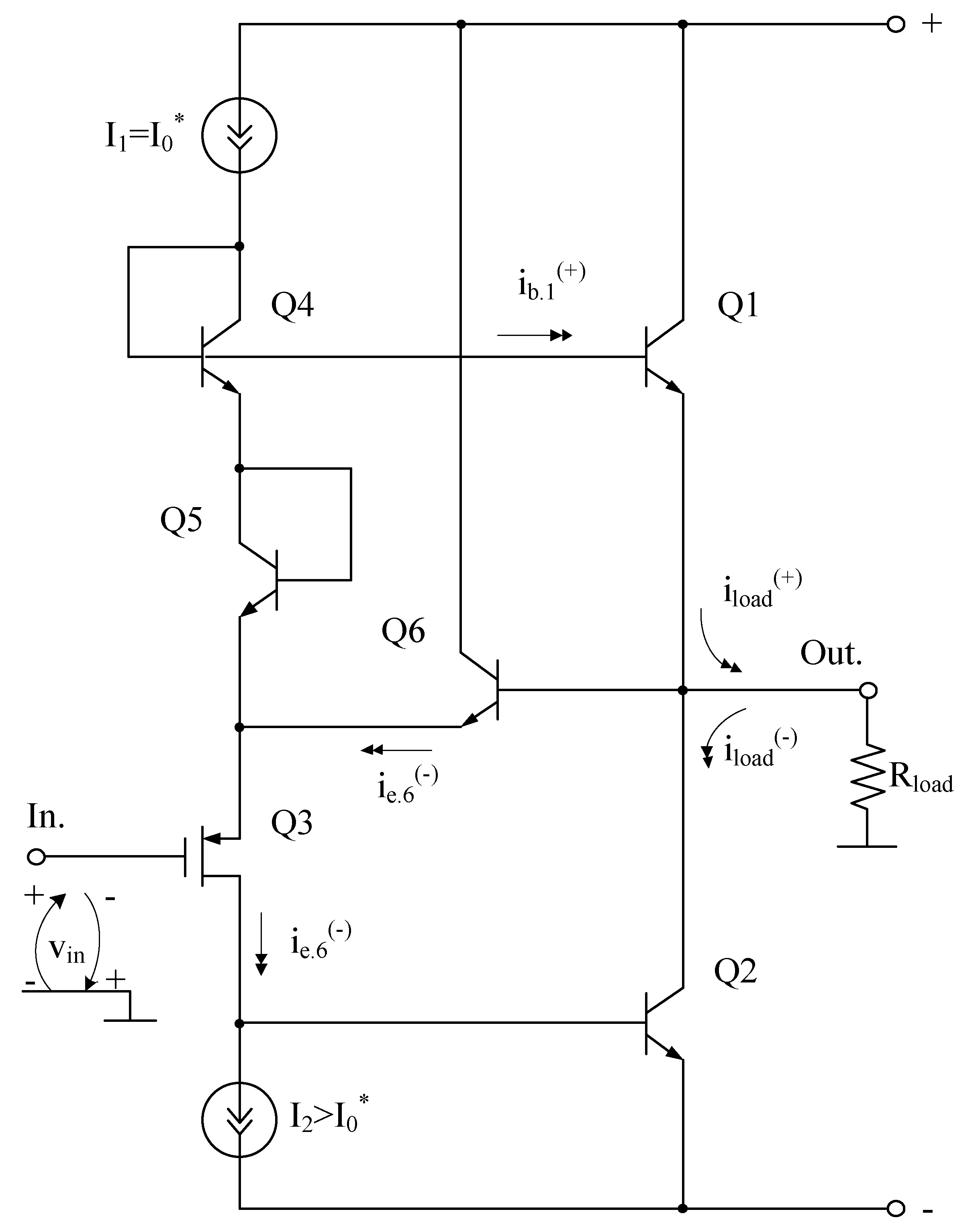

In the BA circuit of

Figure 11, the p-n junction of VD1 limits the voltage drop across resistor R1 when the BA input voltages are positive and the big currents in load. Transistors Q3, Q4, and reference current source I

1 set the static mode of Q5 and Q6. The BA circuit setting is provided by selection of resistors R1÷R2 and currents I

1=I

2.

Figure 11.

SiGe buffer amplifier: modification №4.

Figure 11.

SiGe buffer amplifier: modification №4.

In this case

and

are determined by the formulas:

where

,

– base current gain coefficients of bipolar transistors Q1÷Q2,

– maximum possible value of SS (

Figure 3) output current with positive v

in,

– voltage drop across the resistor R1,

– emitter junction resistance Q5, s

6 – drain-gate transconductance Q6.

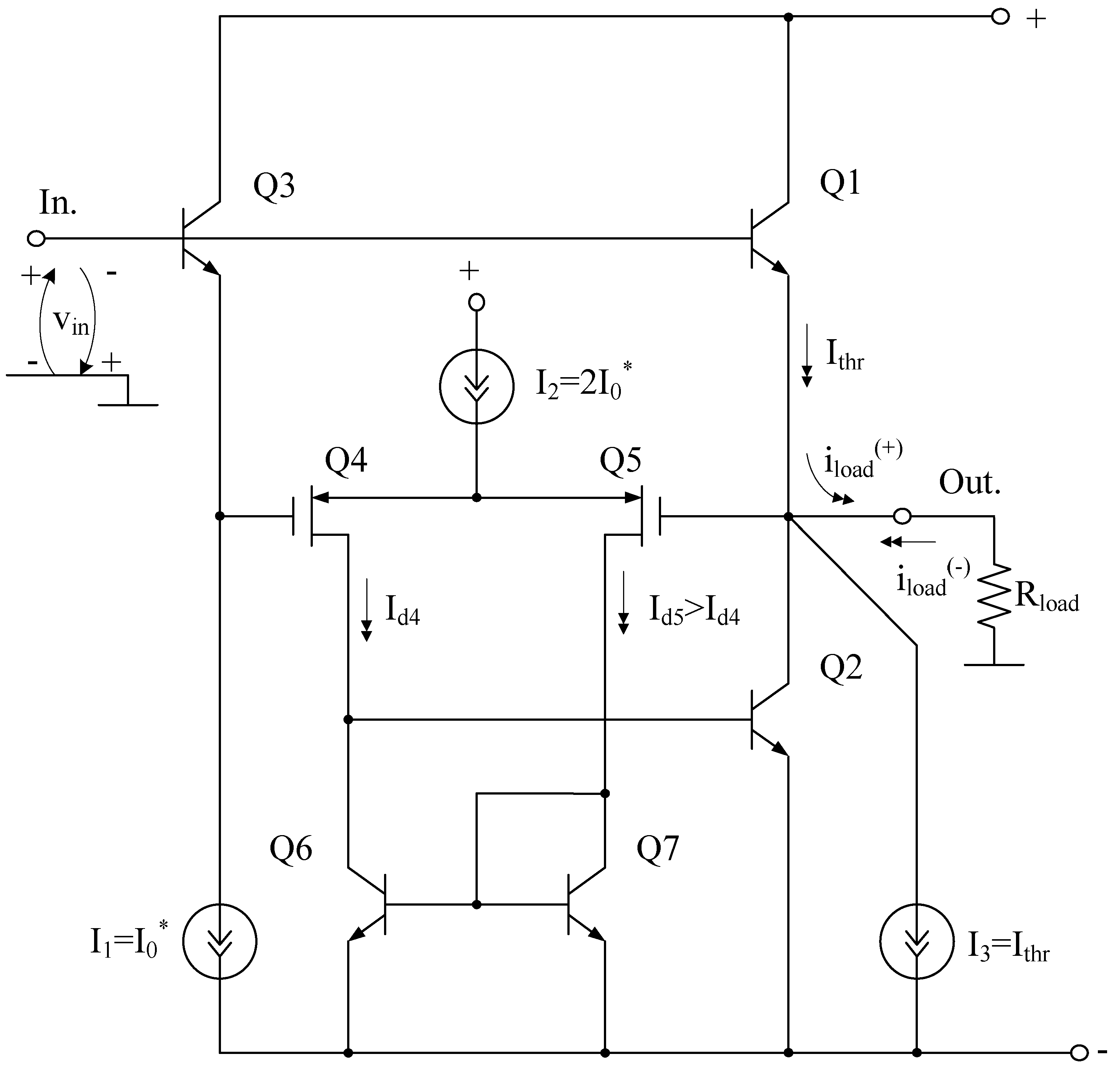

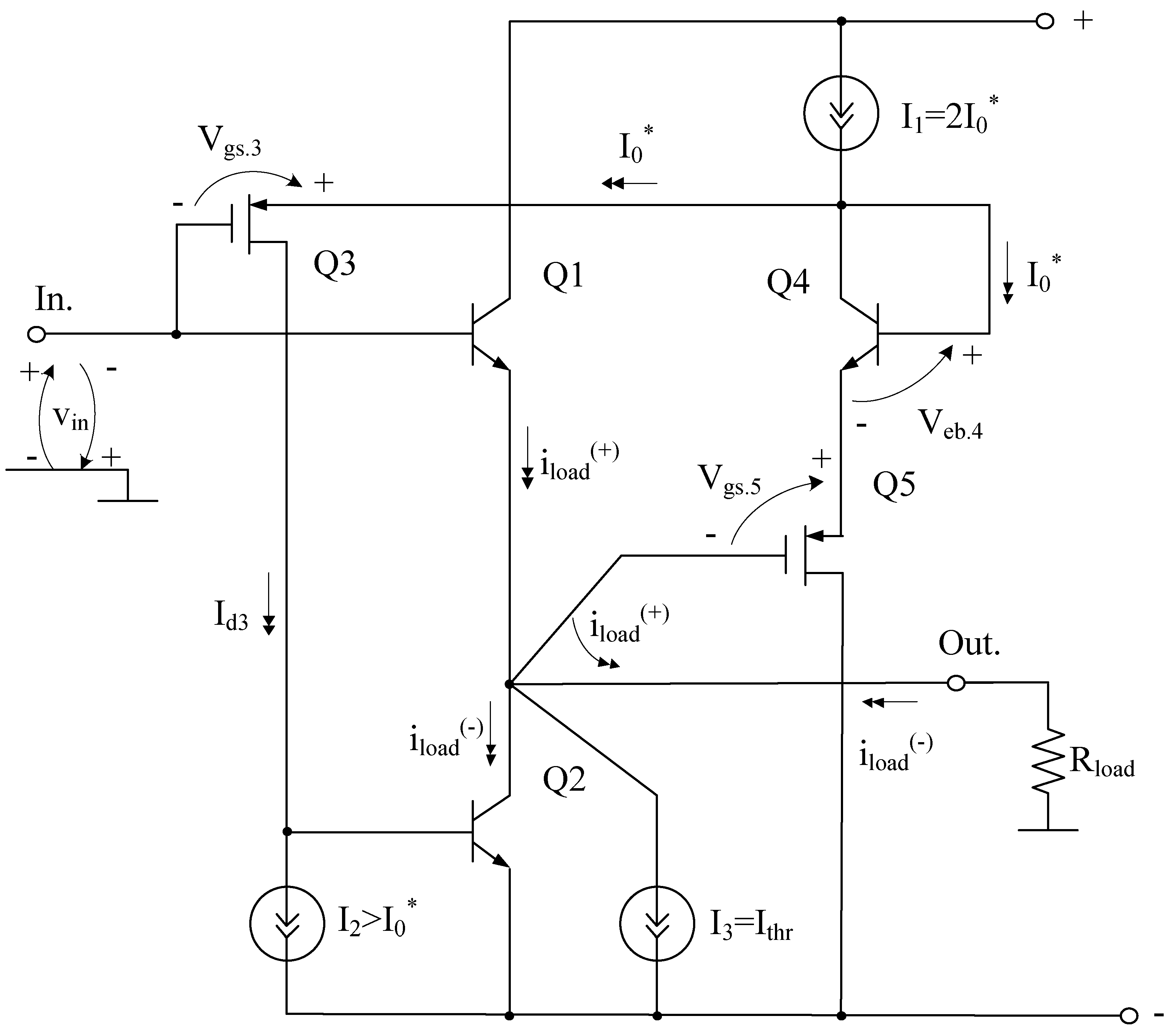

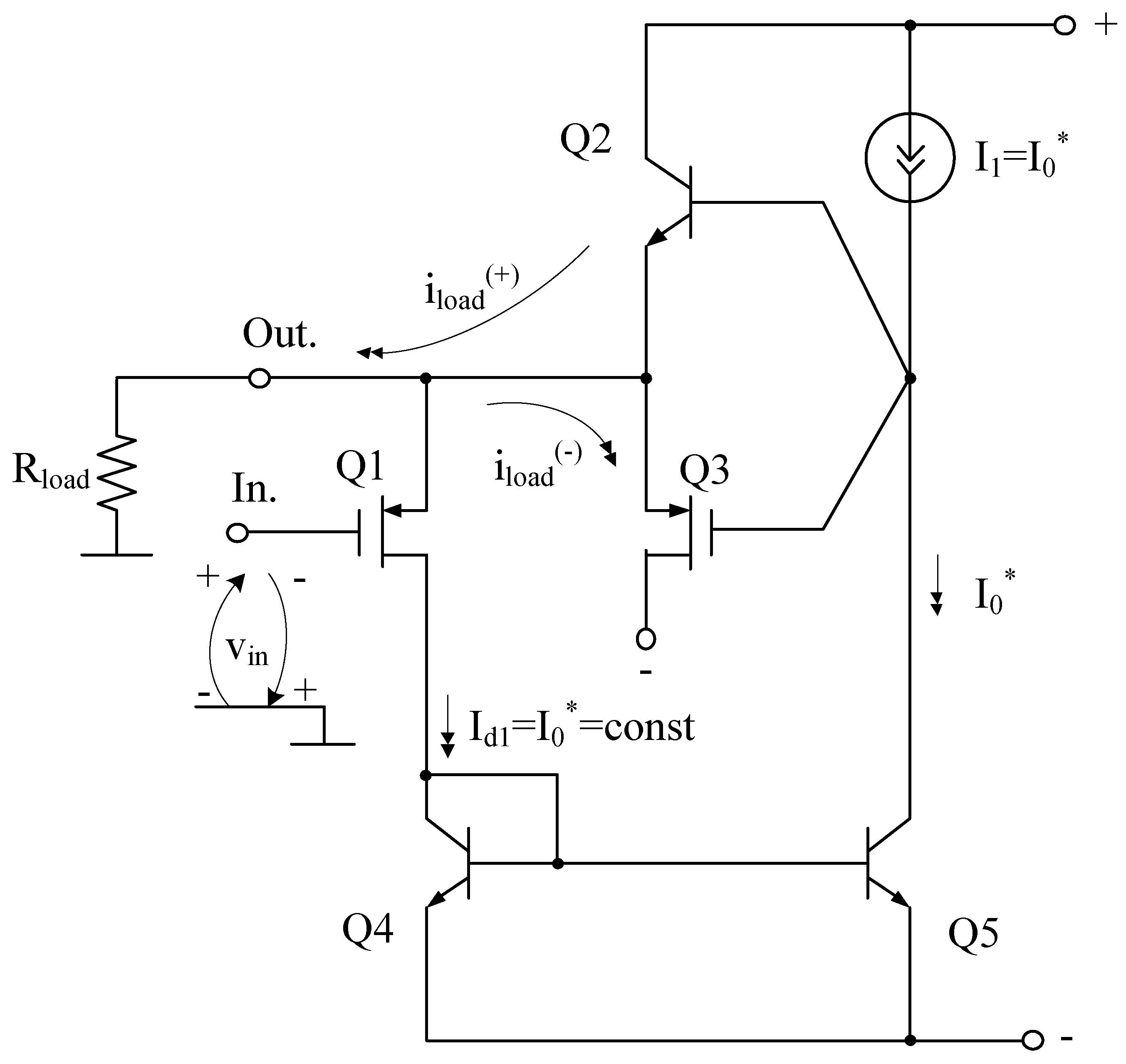

The peculiarity of BA (

Figure 12) is that the bipolar directions of the currents in the R

load load are here formed by the n-p-n transistors Q1, Q2. Other elements of the BA circuit provide state control of the transistor Q1, and when Q1 goes into cutoff (at negative v

in), control transistor Q2. The BA circuit is adjusted by selecting the currents 2I

1=I

2 and I

3.

Figure 12.

SiGe buffer amplifier: modification №5.

Figure 12.

SiGe buffer amplifier: modification №5.

In this case

and

are determined by the formulas:

where

– maximum possible value of SS (

Figure 3) output current with positive v

in;

,

– base current gain coefficients of bipolar transistors Q1÷Q2,

– two-terminal device current I

1 .

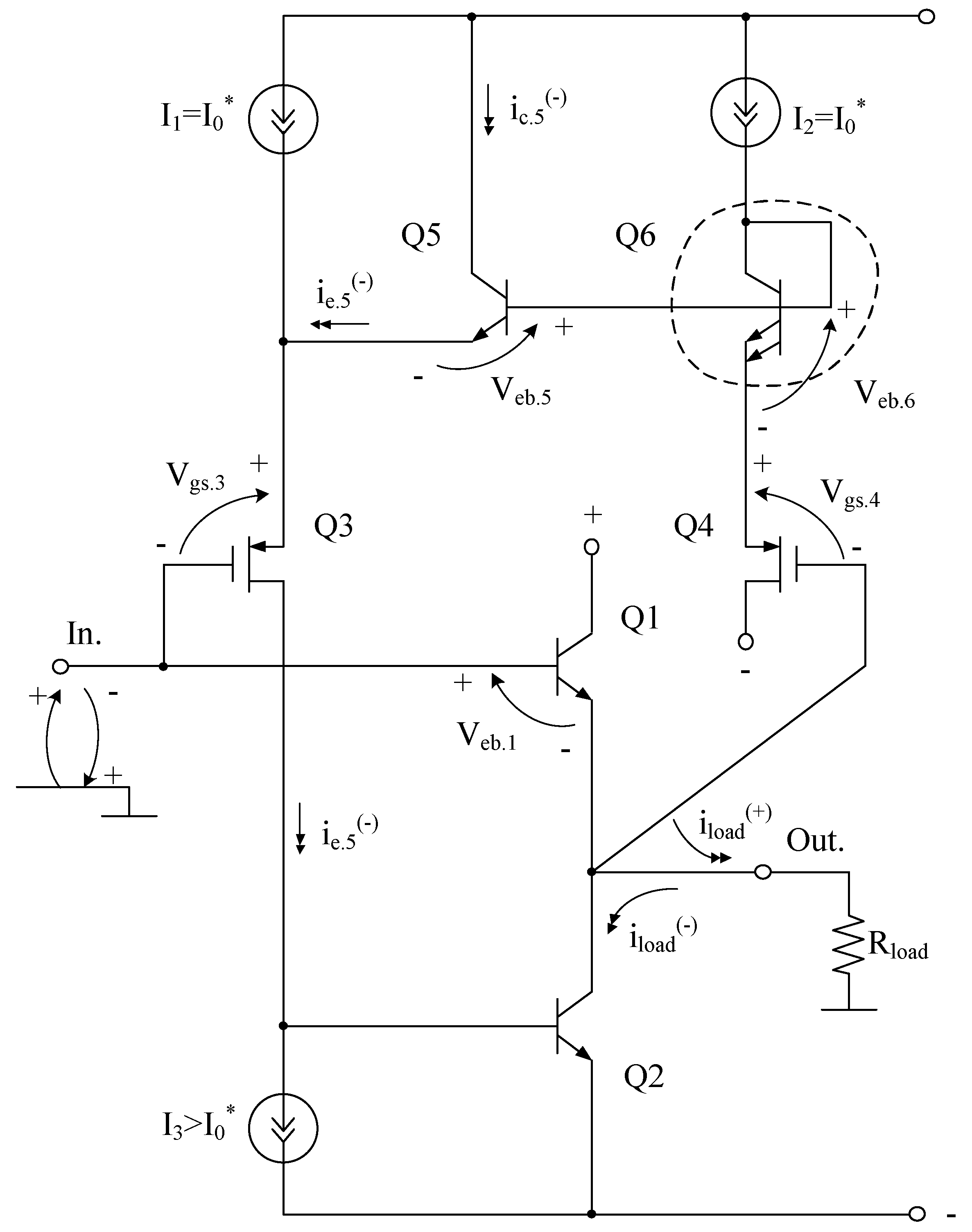

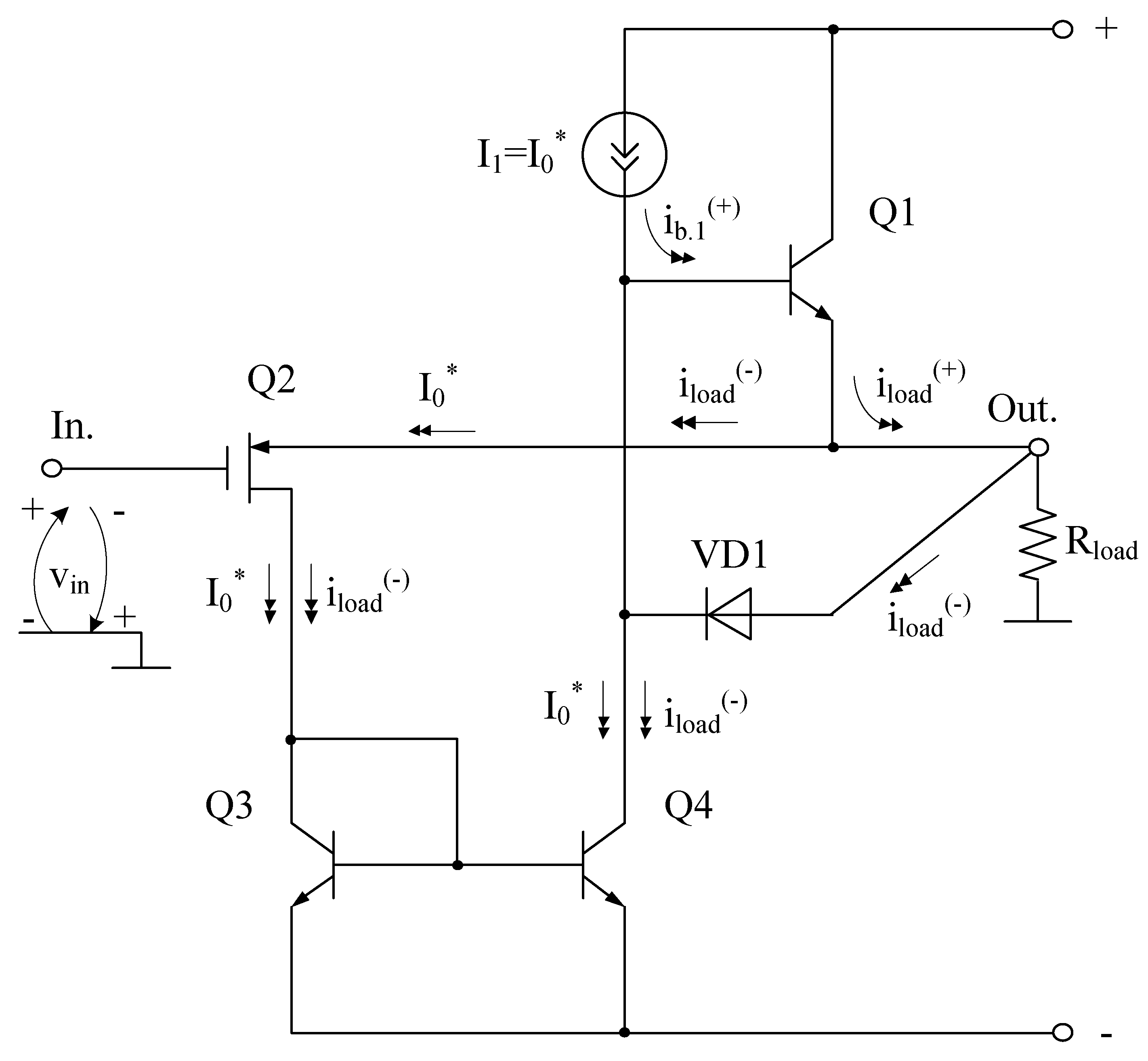

In circuit BA in

Figure 13, the static mode setting of the transistors is provided by selecting the reference current sources I

1, I

2, and I

3.

Figure 13.

SiGe buffer amplifier: modification №6.

Figure 13.

SiGe buffer amplifier: modification №6.

Here, the values of the maximum output currents

and

are determined by the formulas:

where

– maximum possible value of SS (

Figure 3) output current with positive v

in;

,

– base current gain coefficients of bipolar transistors Q1÷Q2,

. In this case

.

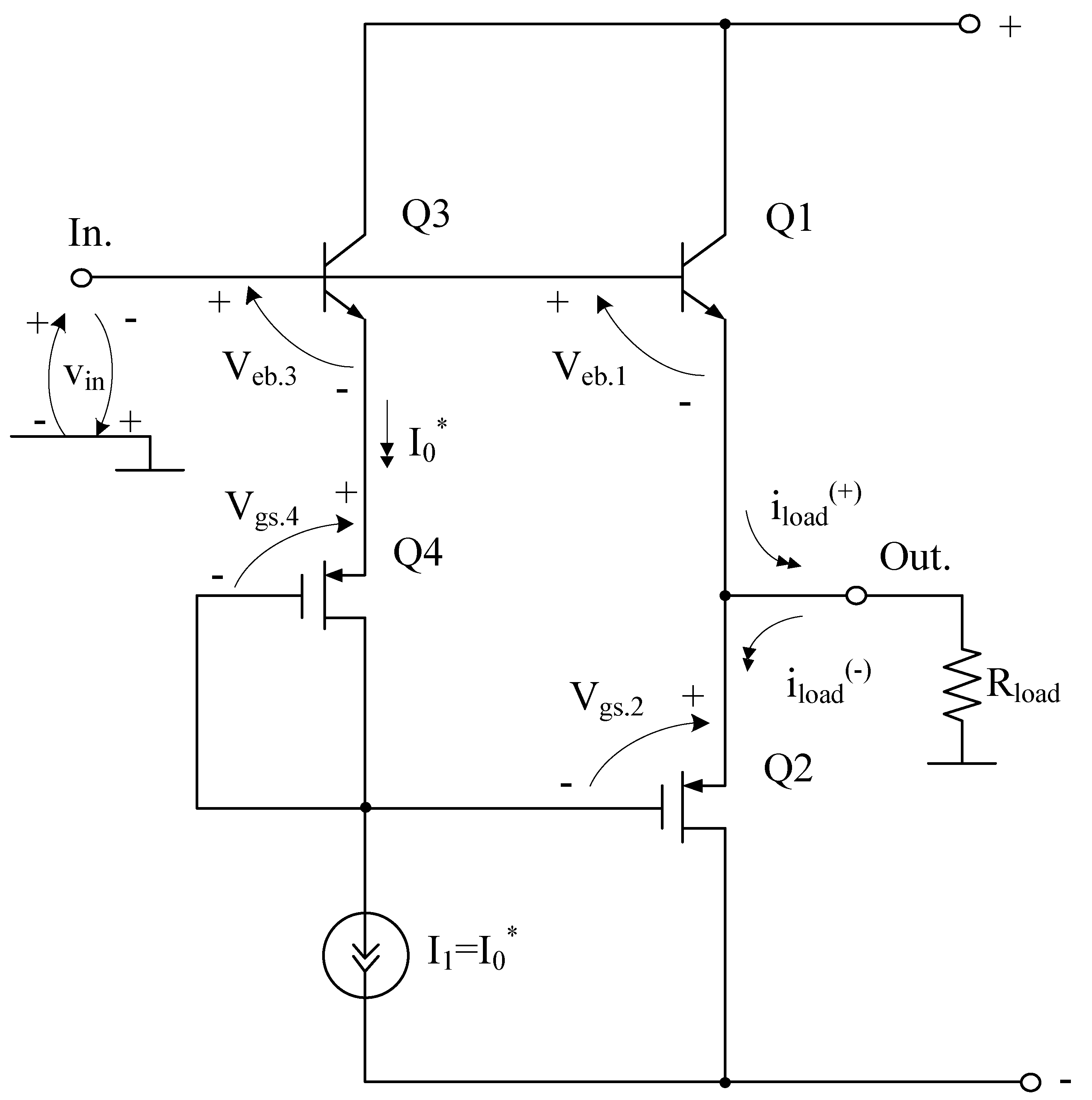

The positive current direction in the load R

load in BA (

Figure 14) is determined by the base current gain

of the transistor Q1 and the reference current source I

1. Adjustment of the BA circuit is provided by selection of currents I

1=I

2 and resistance of resistor R1.

Figure 14.

SiGe buffer amplifier: modification №7.

Figure 14.

SiGe buffer amplifier: modification №7.

Thus in the scheme of

Figure 14 the currents

and

are determined by the formulas:

where

,

– base current gain coefficients of bipolar transistors Q1÷Q2,

– two-terminal device current I

1,

– maximum amplitude of the input signal when negative v

in, R1 – resistor resistance R1, s

4 – the steepness of the drain-gate characteristic of the transistor Q4.

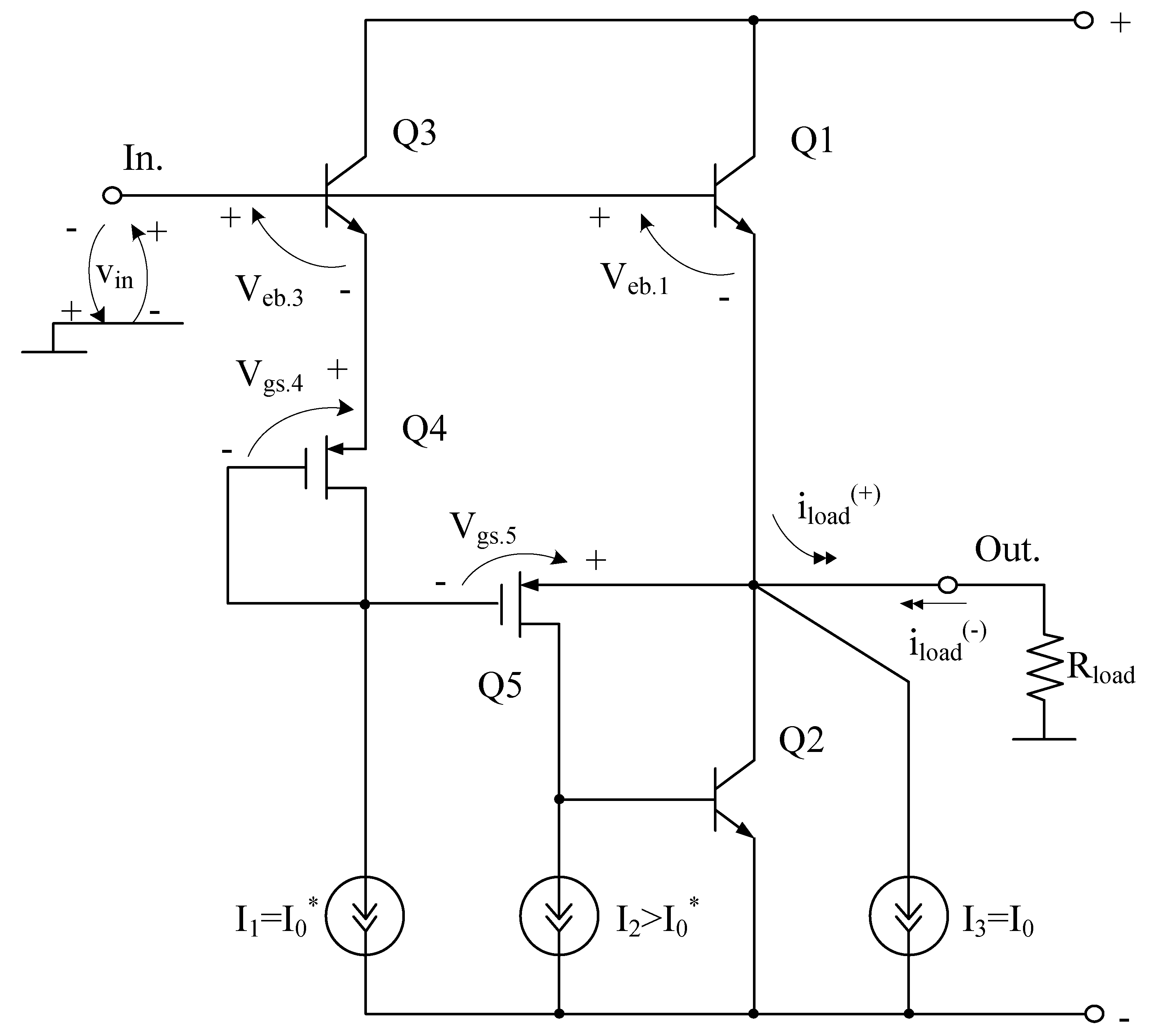

The peculiarity of BA in

Figure 15 is that the bipolar directions of the currents in the R

load load here are determined by transistors Q1, Q2, Q5, the maximum possible value of the output current of the intermediate stage (

Figure 3) at positive v

in, and the source current I

2. The BA circuit is configured by selecting the numerical values of I

1=I

2 and I

3.

Figure 15.

SiGe buffer amplifier: modification №8.

Figure 15.

SiGe buffer amplifier: modification №8.

In this case

and

are determined by the formulas:

where

,

,

– base current gain coefficients of bipolar transistors Q1, Q2, Q5;

– maximum possible value of SS (

Figure 3) output current with positive v

in;

– two-terminal device current I

1=I

2.

In circuit BA in

Figure 16, the positive currents in the load R

load are generated by the n-p-n transistor Q1 and the negative currents by the field-effect transistor Q2. The circuit is adjusted by selecting the current I

1.

Figure 16.

SiGe buffer amplifier: modification №9.

Figure 16.

SiGe buffer amplifier: modification №9.

In this case, the maximum currents

and

are determined by the formulas:

where

– base current gain coefficient of bipolar transistor Q1,

– maximum possible value of SS (

Figure 3) output current with positive v

in,

– maximum transistor current Q2.

The BA circuit (

Figure 17) differs from the BA circuit

Figure 16 by the use of bipolar transistor Q2, which together with field-effect transistor Q5 provides negative currents in the load R

load. Adjustment of the BA circuit is provided by selection of currents I

1, I

2 and I

3.

Figure 17.

SiGe buffer amplifier: modification №10.

Figure 17.

SiGe buffer amplifier: modification №10.

In the circuit of

Figure 17, the maximum currents are

and

are determined by the formulas:

where

– base current gain coefficient of bipolar transistor Q1,

– maximum possible value of SS (

Figure 3) output current with positive v

in,

– maximum collector current of the transistor Q2.

BA

Figure 18 is realized on complementary field-effect transistors Q1, Q2 and Q3, Q4. Moreover, Q1 and Q3 and the reference current source I

1 set the static mode of transistors Q2, Q4. The adjustment of the BA circuit is provided by selecting the current I

1, and also by changing the channel widths of the transistors.

Figure 18.

SiGe buffer amplifier: modification №11.

Figure 18.

SiGe buffer amplifier: modification №11.

In this case

and

are determined by the formulas:

where

– maximum transistor drain current Q2,

– maximum transistor drain current Q4.

In the circuit of

Figure 19, control of the state of transistor Q1 by the emitter-base voltage is provided by a differential stage on transistors Q5 and Q6, which compare the emitter-base voltages of transistors Q1 and Q4 and, when Q1 is latched, controls transistors Q3, Q2. This generates a negative current direction in the load. Adjustment of the BA circuit is provided by selection of currents I

1=2I

2, I

3 and resistance of resistor R1.

Figure 19.

SiGe buffer amplifier: modification №12.

Figure 19.

SiGe buffer amplifier: modification №12.

In circuit BA

Figure 19 the maximum currents in the load

and

are determined by the formulas:

where

,

,

– base current gain coefficients of bipolar transistors Q1÷Q3,

– maximum possible value of SS (

Figure 3) output current with positive v

in,

.

The BA circuit in

Figure 20 is realized on complementary field-effect transistors Q1÷Q4. Adjustment of the BA circuit is provided by selection of currents I

1, I

2, I

3.

Figure 20.

SiGe buffer amplifier: modification №13.

Figure 20.

SiGe buffer amplifier: modification №13.

In this case

and

are determined by the formulas:

where

– maximum transistor drain current Q1,

– maximum transistor drain current Q3.

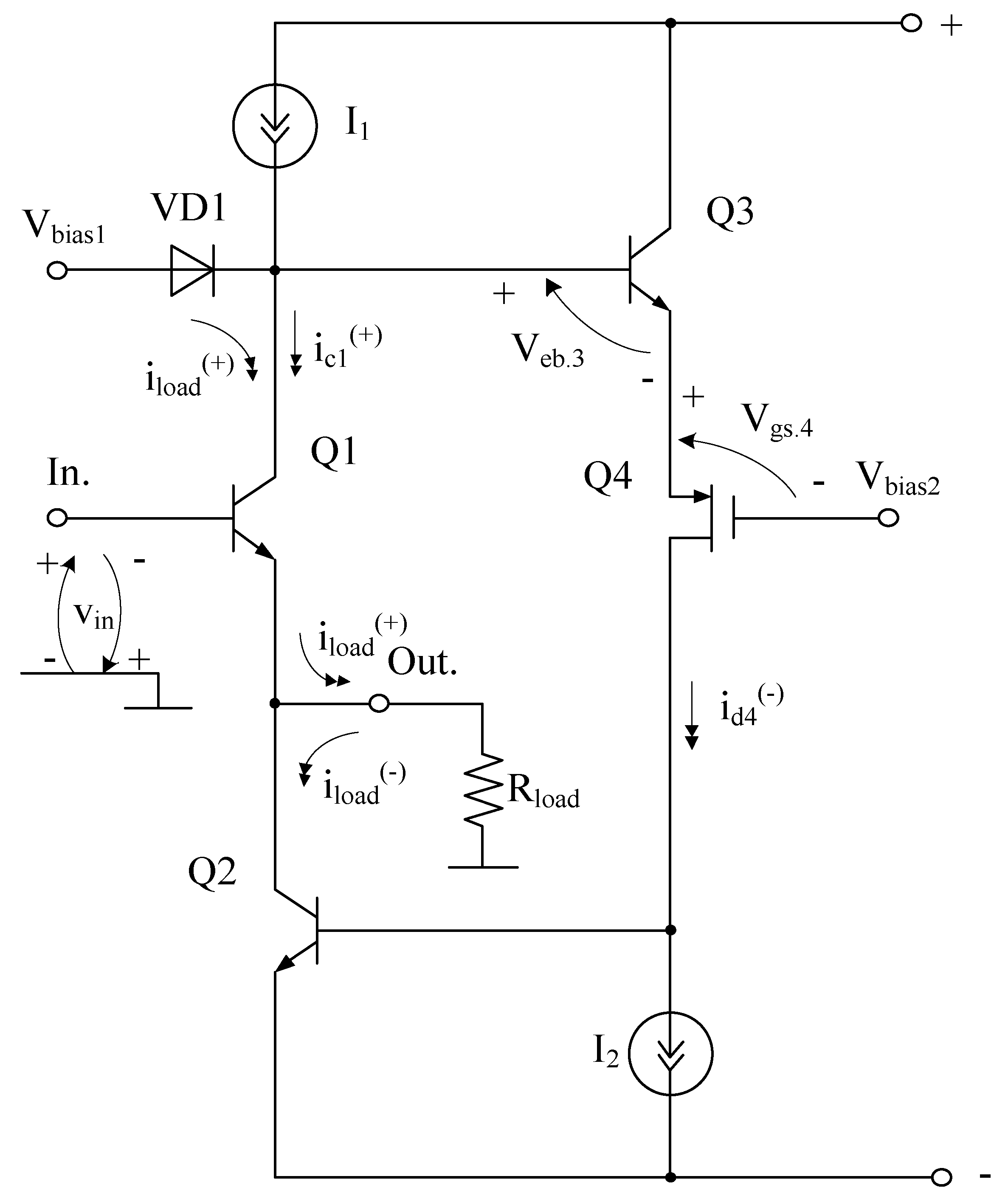

In circuit BA (

Figure 21), the status of transistor Q1 is monitored by numerical values of its collector current, which is compared with the source current I

1. At high positive currents in the load, the p-n junction of VD1 opens, through which i

load(+)is shorted to the low impedance bias circuit source V

bias1. The BA circuit is set up by selecting currents I

1, I

2, and sources V

bias1, V

bias2.

Figure 21.

SiGe buffer amplifier: modification №14.

Figure 21.

SiGe buffer amplifier: modification №14.

In this case, the currents

and

are determined by the formulas:

where

,

,

– base current gain coefficients of bipolar transistors Q1÷Q3,

– maximum possible value of SS (

Figure 3) output current with positive v

in.

The circuit BA in

Figure 22 has an increased input impedance due to the use of the field-effect transistor Q3. The BA setting is provided by selecting the currents I

1, I

2.

Figure 22.

SiGe buffer amplifier: modification №15.

Figure 22.

SiGe buffer amplifier: modification №15.

In this case, the maximum currents

and

are determined by the formulas:

where

– base current gain coefficient of bipolar transistor Q1,

,

– maximum collector current of the transistor Q2,

.

BA (

Figure 23) is realized on n-p-n bipolar transistor Q1 and field-effect transistors Q2, Q4. The BA circuit is tuned by selecting the current I

1.

Figure 23.

SiGe buffer amplifier: modification №16.

Figure 23.

SiGe buffer amplifier: modification №16.

In this case, the maximum currents in the load

and

are defined by the formulas:

where

– current gain of the base of the bipolar transistor Q1,

– maximum possible value of SS (

Figure 3) output current with positive v

in,

– maximum transistor drain current Q4.

In the BA circuit (

Figure 24), the current in the load in the positive direction is provided by the bipolar transistor Q2 and in the negative direction by the field-effect transistor Q3. The BA static mode is set by selecting the current I

1.

Figure 24.

SiGe buffer amplifier: modification №17.

Figure 24.

SiGe buffer amplifier: modification №17.

In this case, the maximum currents in the load

and

are determined by the formulas:

where

– current gain of the base of the bipolar transistor Q2,

,

– maximum drain current of the field-effect transistor Q3.

The peculiarity of BA in

Figure 25 is that the bipolar directions of the currents in the R

load are here determined by transistor Q1, bipolarized by I

1 (at positive v

in) and field-effect transistor Q2 (at negative v

in). The static mode of the BA circuit is set by selecting the current

.

Figure 25.

SiGe buffer amplifier: modification №18.

Figure 25.

SiGe buffer amplifier: modification №18.

In this circuit the currents

and

are determined by the formulas:

where

– current gain of the base of the bipolar transistor Q1,

,

– maximum drain current of the field-effect transistor Q2.

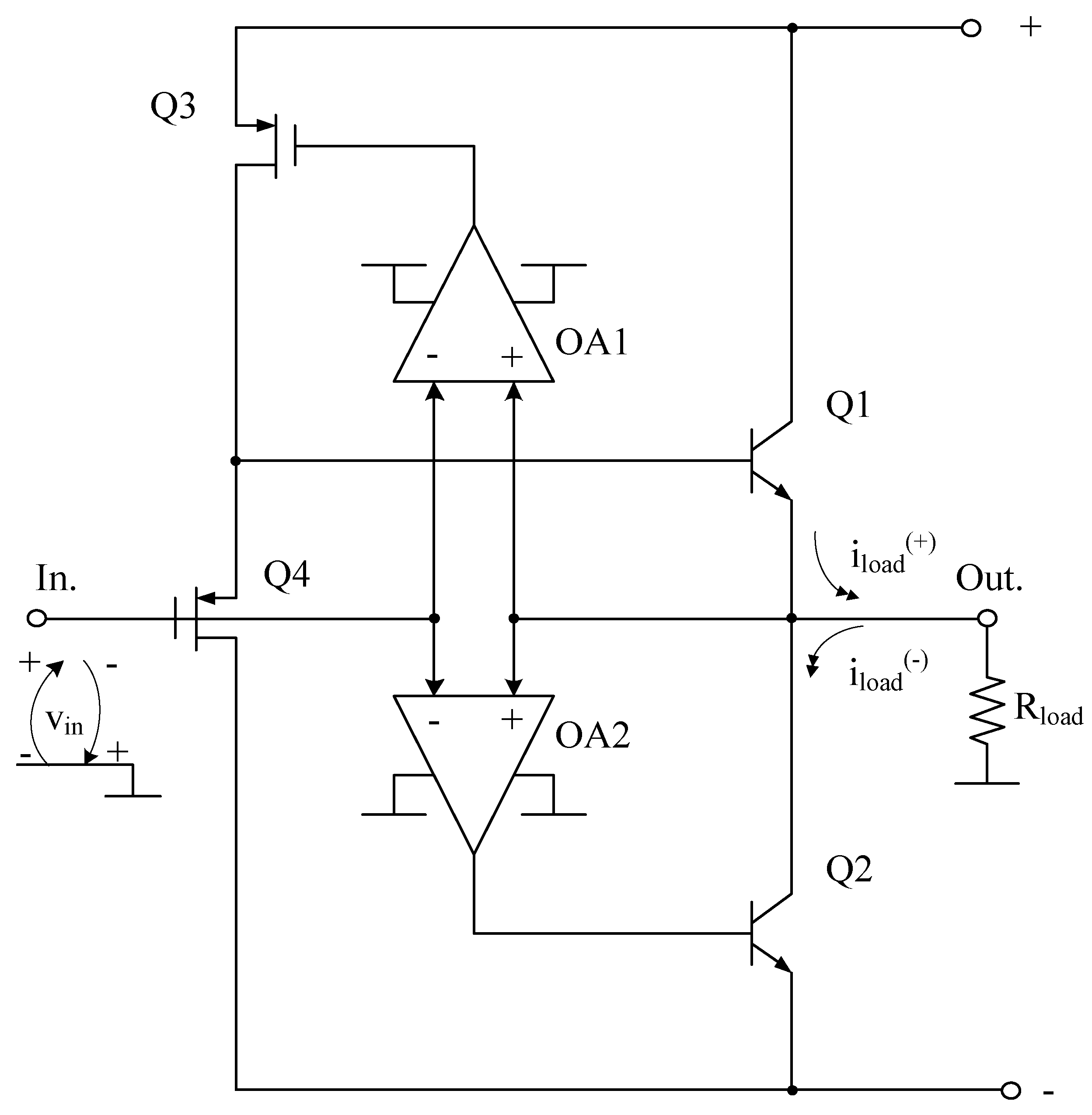

Figure 26 shows a generalized scheme BA, which can have several partial variants of construction, which is determined by the practical implementation of comparison schemes OA1, OA2. Setting BA to the limiting parameters is provided by the choice of OA1, OA2.

Figure 26.

SiGe buffer amplifier: modification №19.

Figure 26.

SiGe buffer amplifier: modification №19.

In this case, the currents

and

are determined by the formulas:

where

– maximum collector current of the transistor Q1,

– maximum collector current of the transistor Q2.

The peculiarity of the scheme BA in

Figure 27 is that by selecting the channel width of transistor Q3 and the resistance of resistor R1, the numerical values of the through current of transistors Q1 and Q2 are set. The setting of the BA is ensured by selecting the current I

1 and the resistance of resistor R1.

Figure 27.

SiGe buffer amplifier: modification №20.

Figure 27.

SiGe buffer amplifier: modification №20.

In this case, the currents

and

are determined by the formulas:

where

– current gain of the base of the bipolar transistor Q1,

– maximum possible value of SS (

Figure 3) output current with positive v

in,

– maximum drain current of the field-effect transistor Q2.

The BA static mode setting in

Figure 28 is provided by selecting the currents

,

,

.

Figure 28.

SiGe buffer amplifier: modification №21.

Figure 28.

SiGe buffer amplifier: modification №21.

In this scheme, the maximum values of currents

and

are determined by the formulas:

where

– base current gain coefficients of bipolar transistors Q1÷Q2, Q4;

– maximum possible value of SS (

Figure 3) output current with positive v

in,

– two-terminal device current I

1= I

2.

The feature of BA in

Figure 29 is that the bipolar directions of the currents in the R

load load are here formed by the bipolar transistor Q1 and the field-effect transistor Q2.

Figure 29.

SiGe buffer amplifier: modification №22.

Figure 29.

SiGe buffer amplifier: modification №22.

In these scheme maximum values of currents in the load

and

are determined by the formulas:

where

– current gain of the base of the bipolar transistor Q1,

– current of the reference current source I

1,

– maximum drain current of the field-effect transistor Q2.

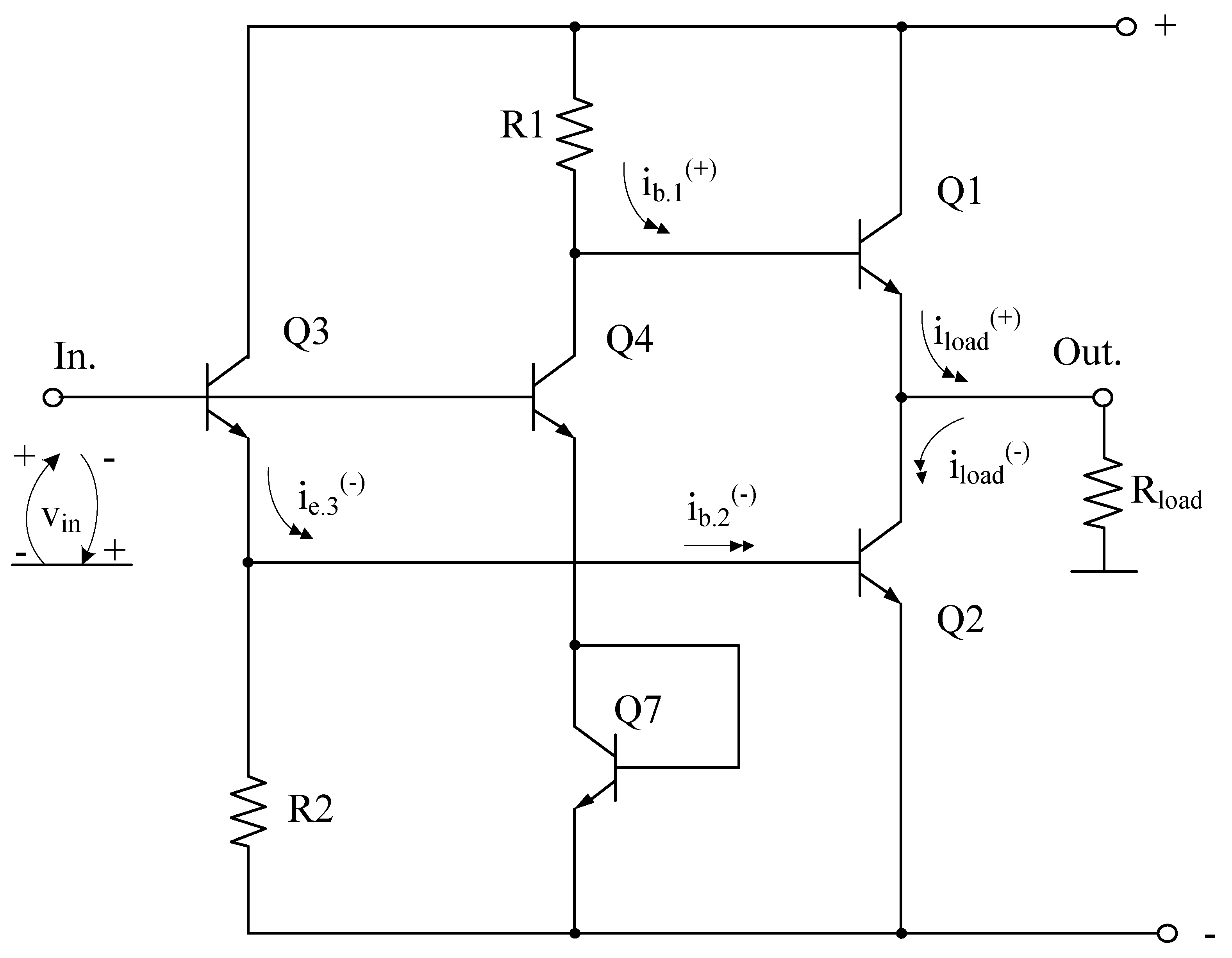

The BA circuit in

Figure 30 provides inverting amplification of the input signal. Its peculiarity is that it is realized only on SiGe bipolar transistors and has low supply voltages. The BA is tuned by selecting resistors R1 and R2.

Figure 30.

SiGe inverting buffer amplifier: modification №23

Figure 30.

SiGe inverting buffer amplifier: modification №23

In this case, the currents

and

are determined by the formulas:

where

– base current gain coefficients of bipolar transistors Q1÷Q3,

– maximum possible value of SS (

Figure 3) output current with negative v

in,

– value of current passing through the resistor R1.

In the BA circuit (

Figure 31), the field-effect transistors Q1, Q3, Q4 and Q5 provide control of the bipolar transistor Q2 at negative input signals. The BA circuit is configured by selecting the currents I

1, I

2.

Figure 31.

SiGe buffer amplifier: modification №24.

Figure 31.

SiGe buffer amplifier: modification №24.

In this circuit, the maximum values of the currents in the load

and

are determined by the formulas:

where

– current gain of the base of the bipolar transistor Q1,

– maximum possible value of SS (

Figure 3) output current with positive v

in,

– maximum collector current of the transistor Q2.