Submitted:

28 March 2025

Posted:

31 March 2025

You are already at the latest version

Abstract

Keywords:

1. Introduction

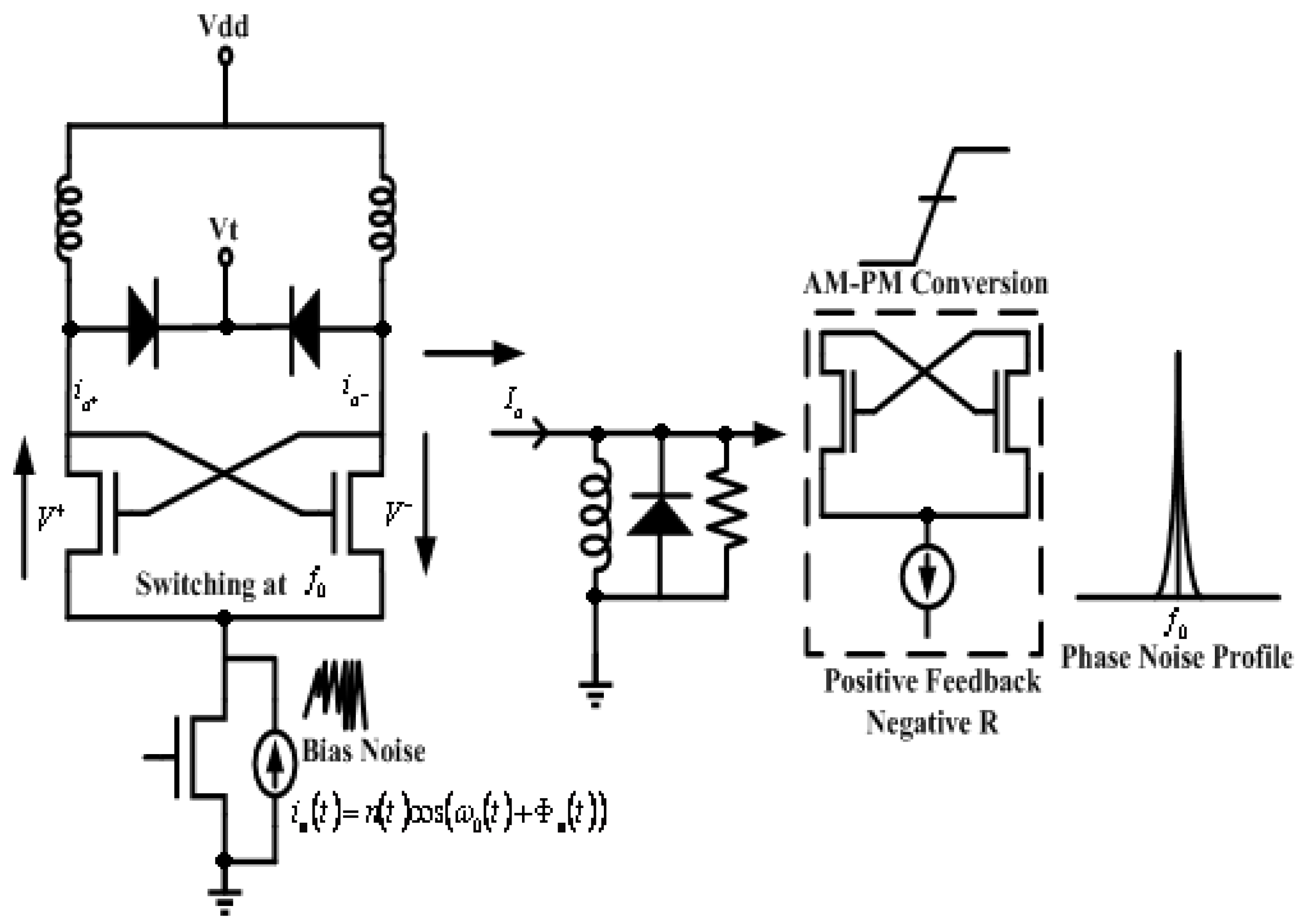

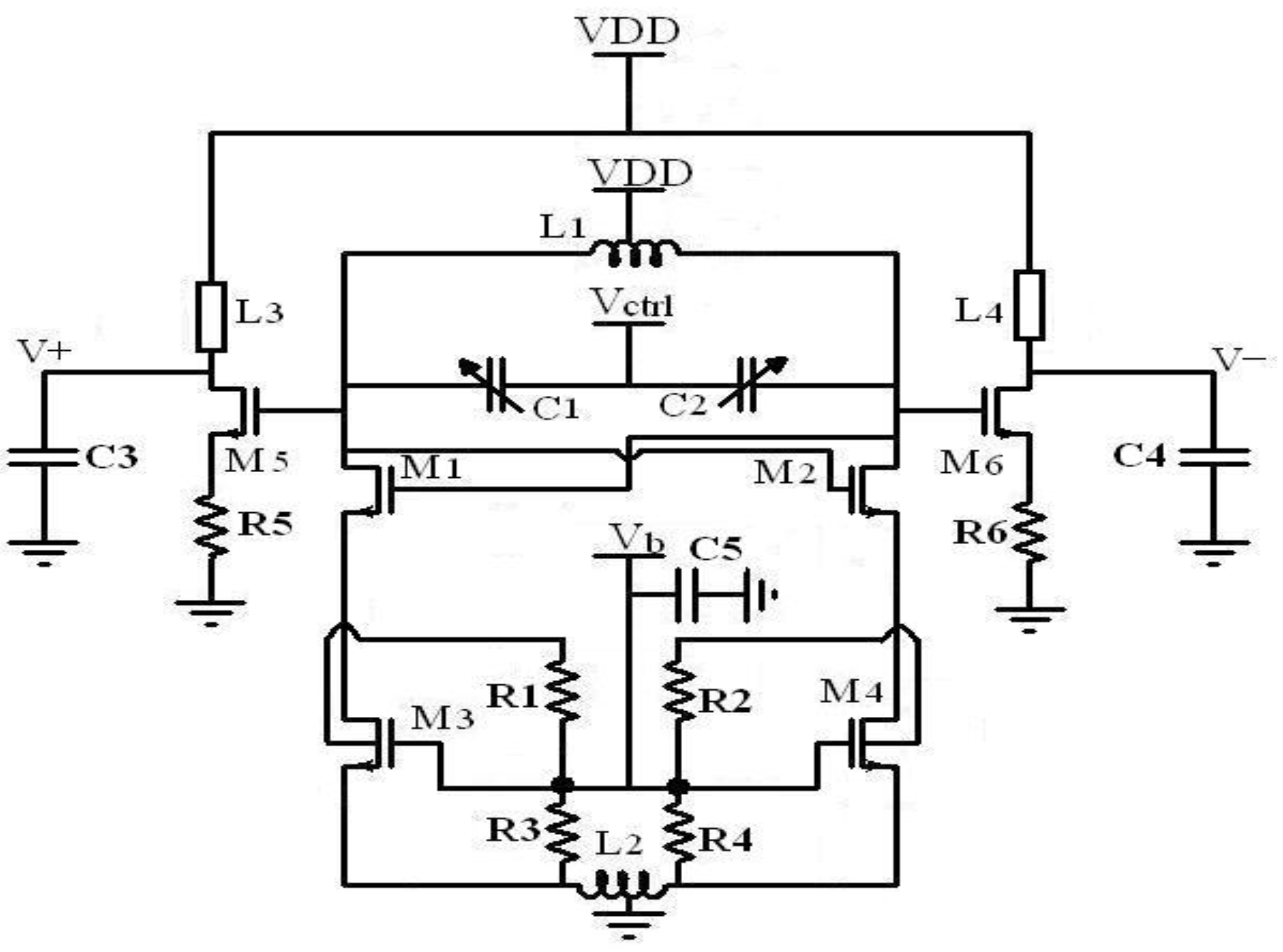

2. VCO Design

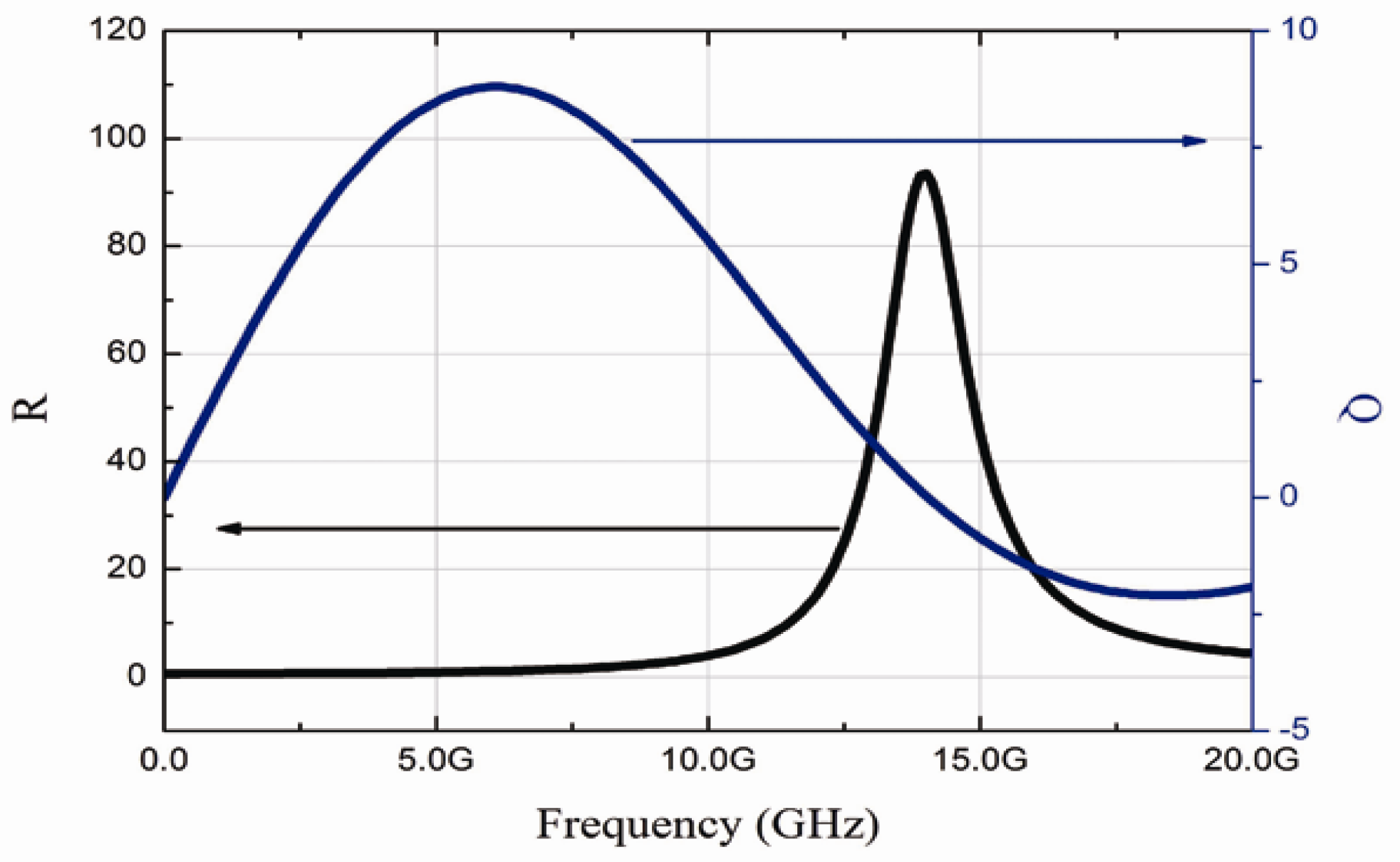

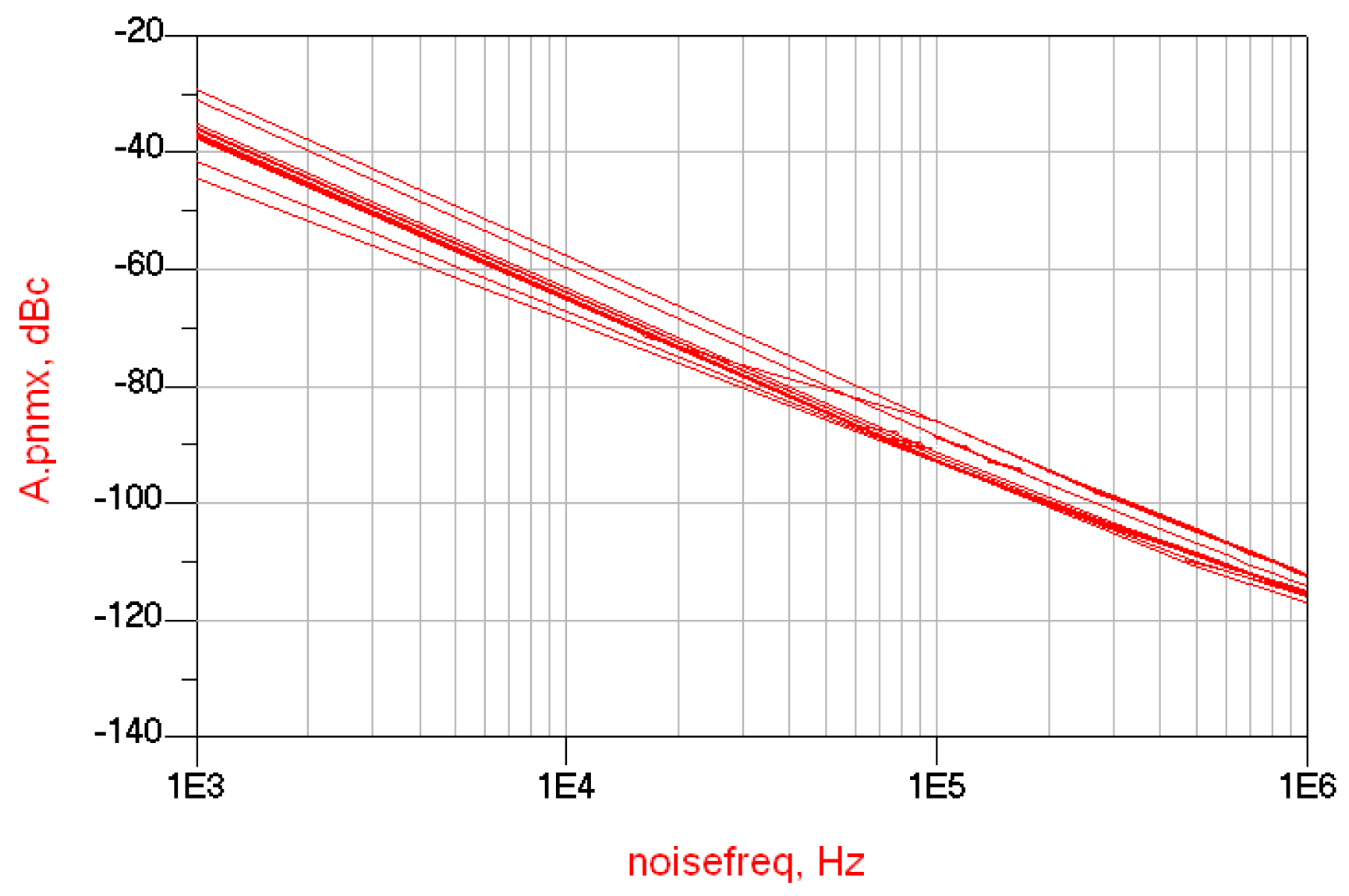

2.1. Phase Noise

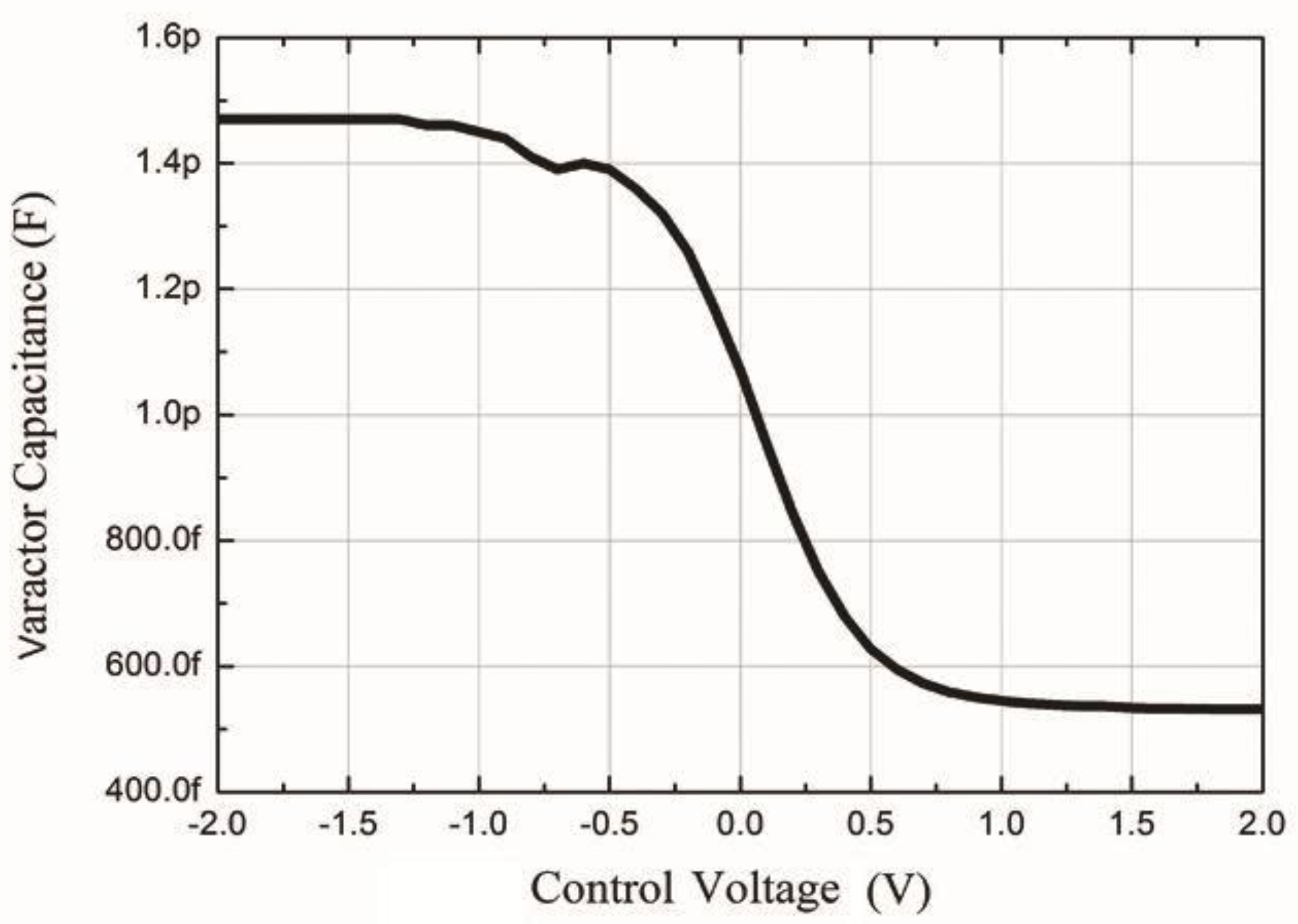

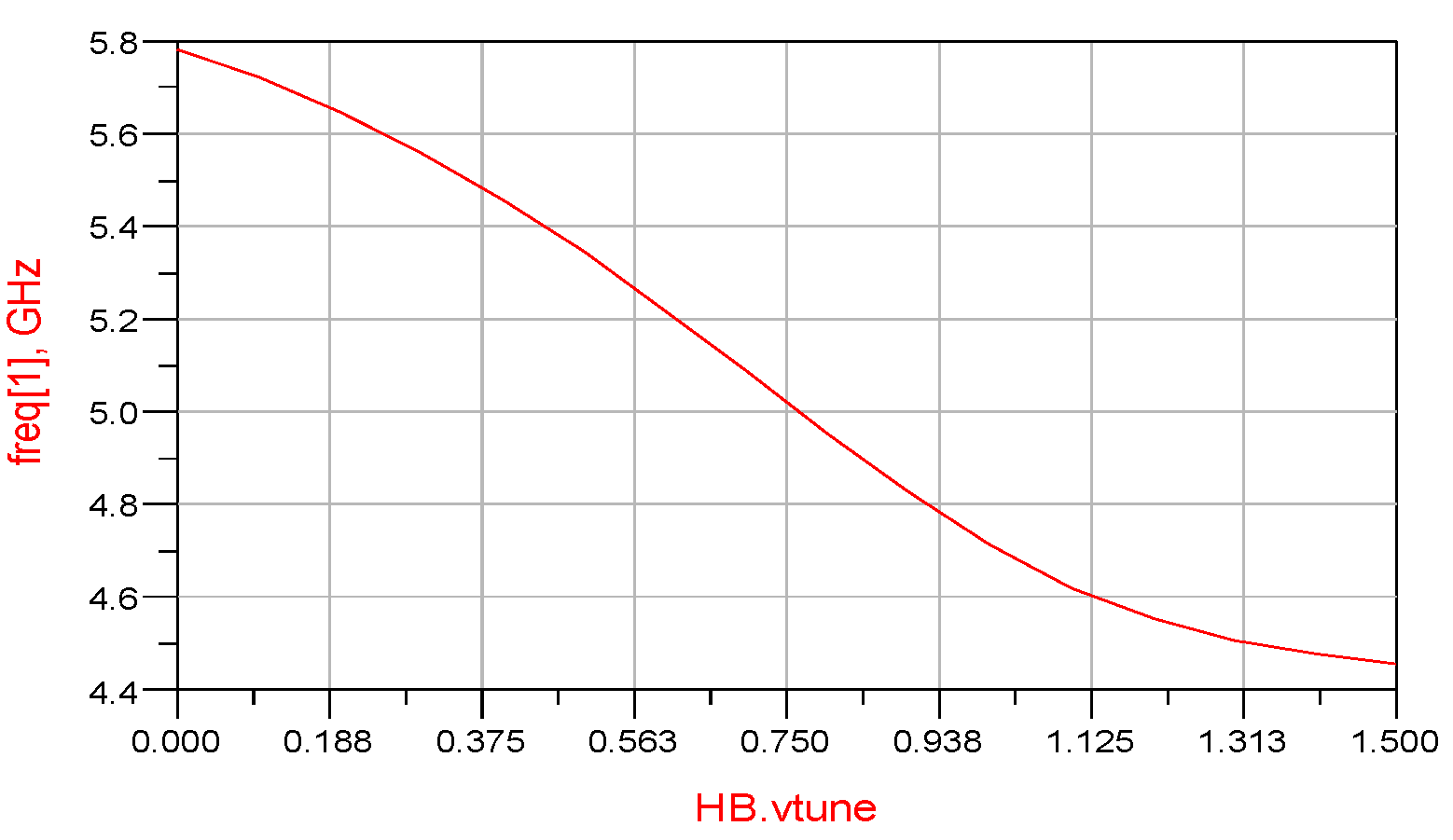

2.2. VCO Design

3. Simulation and Measurement Results

3.1. Simulation Results

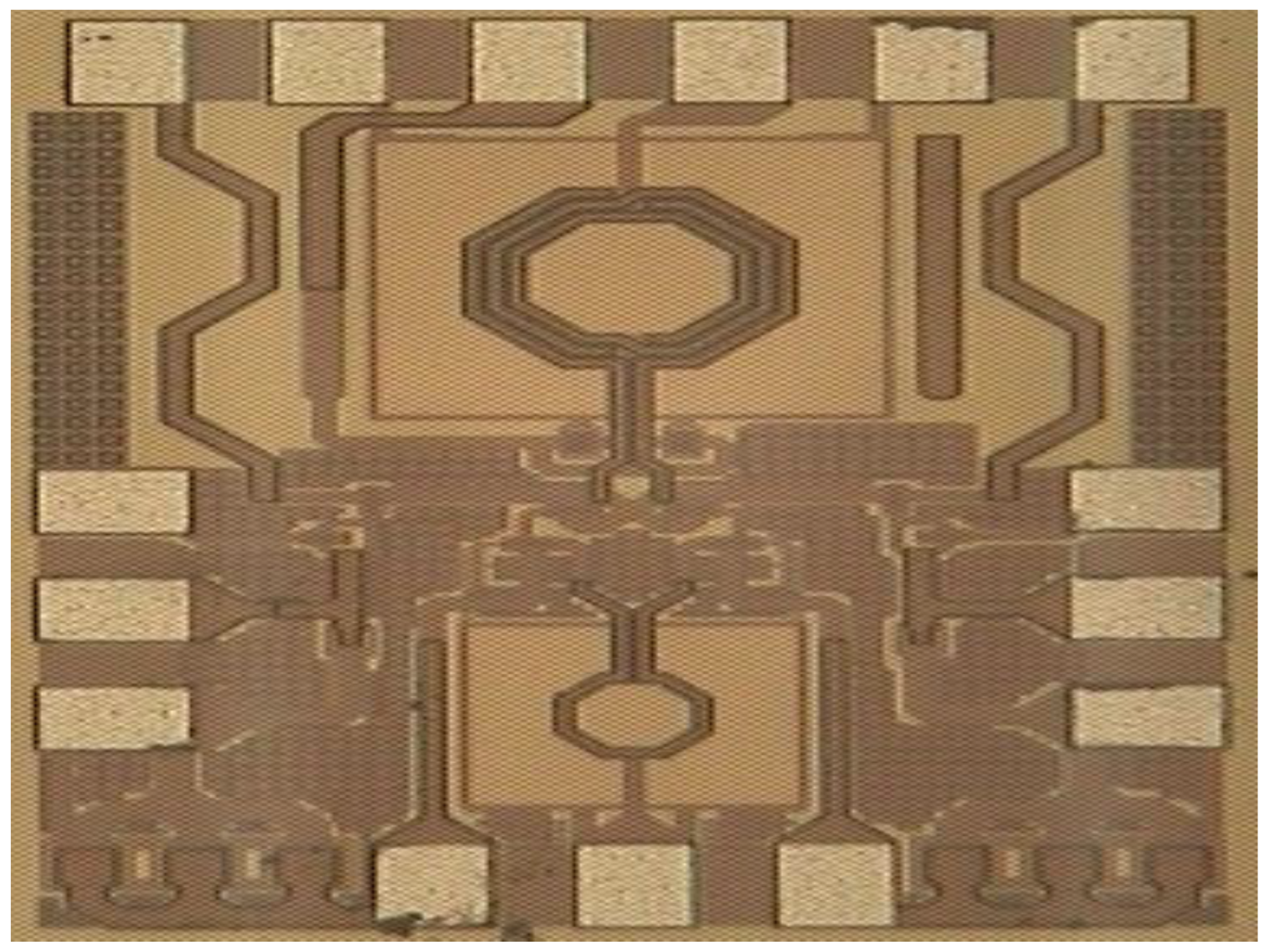

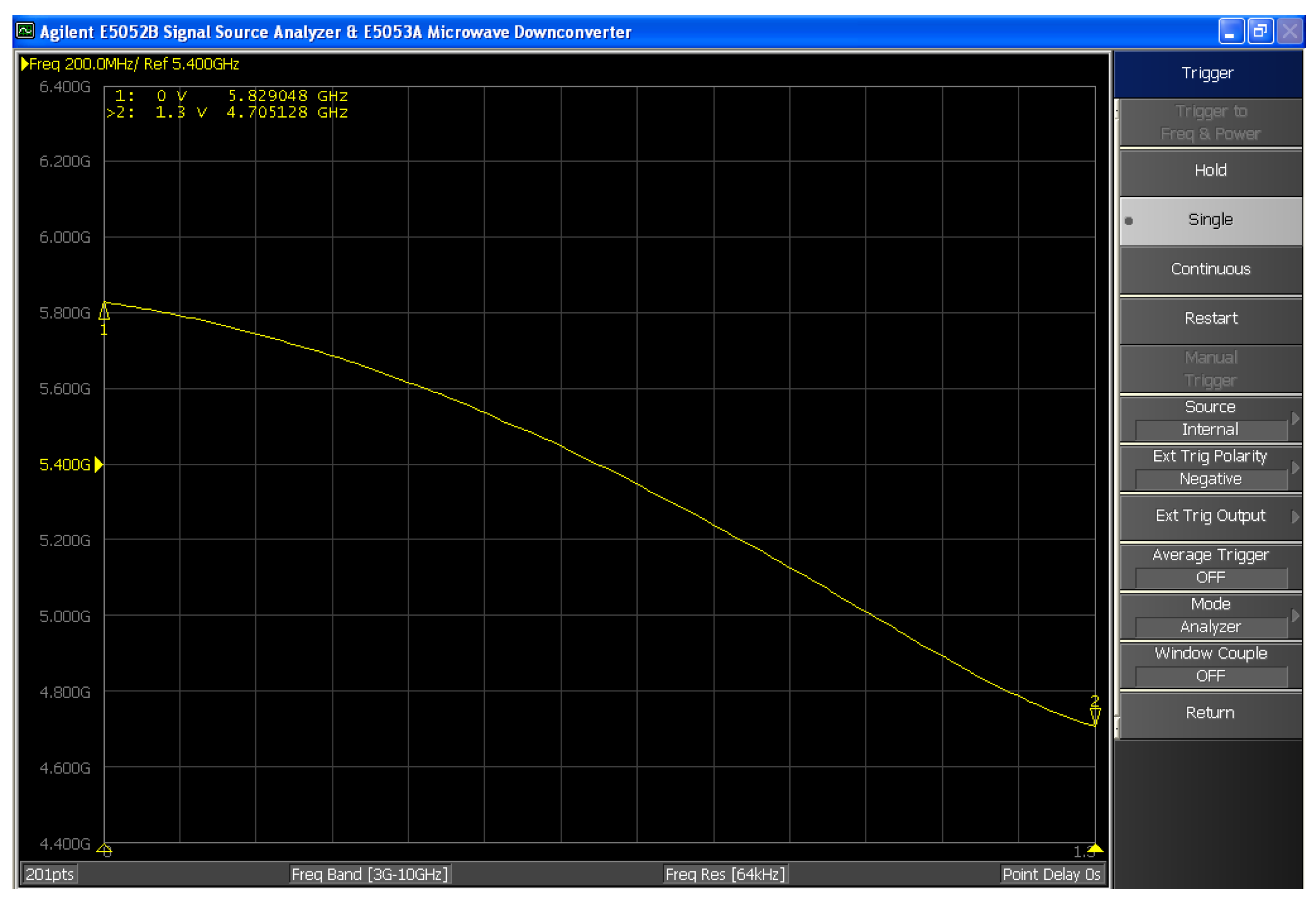

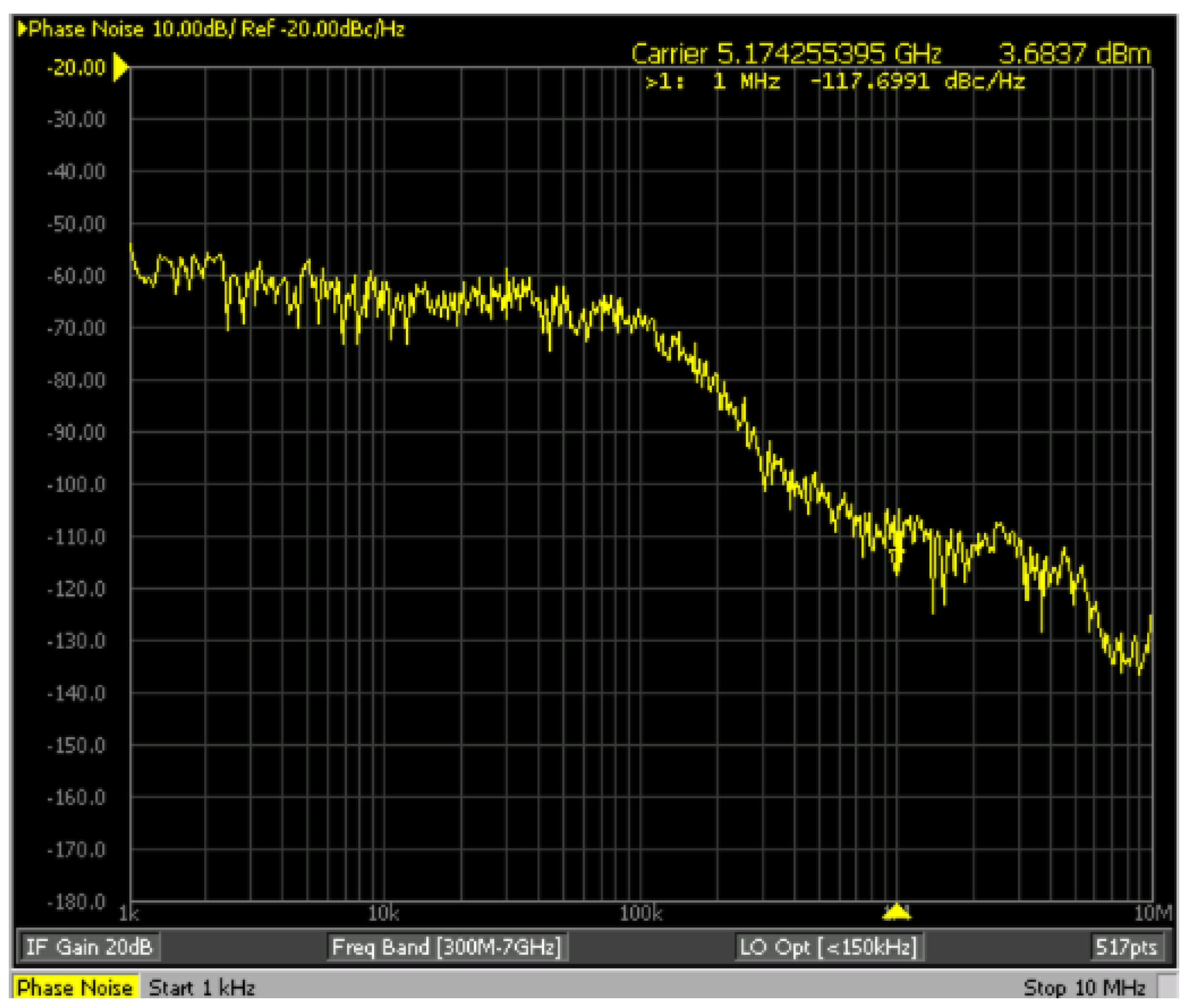

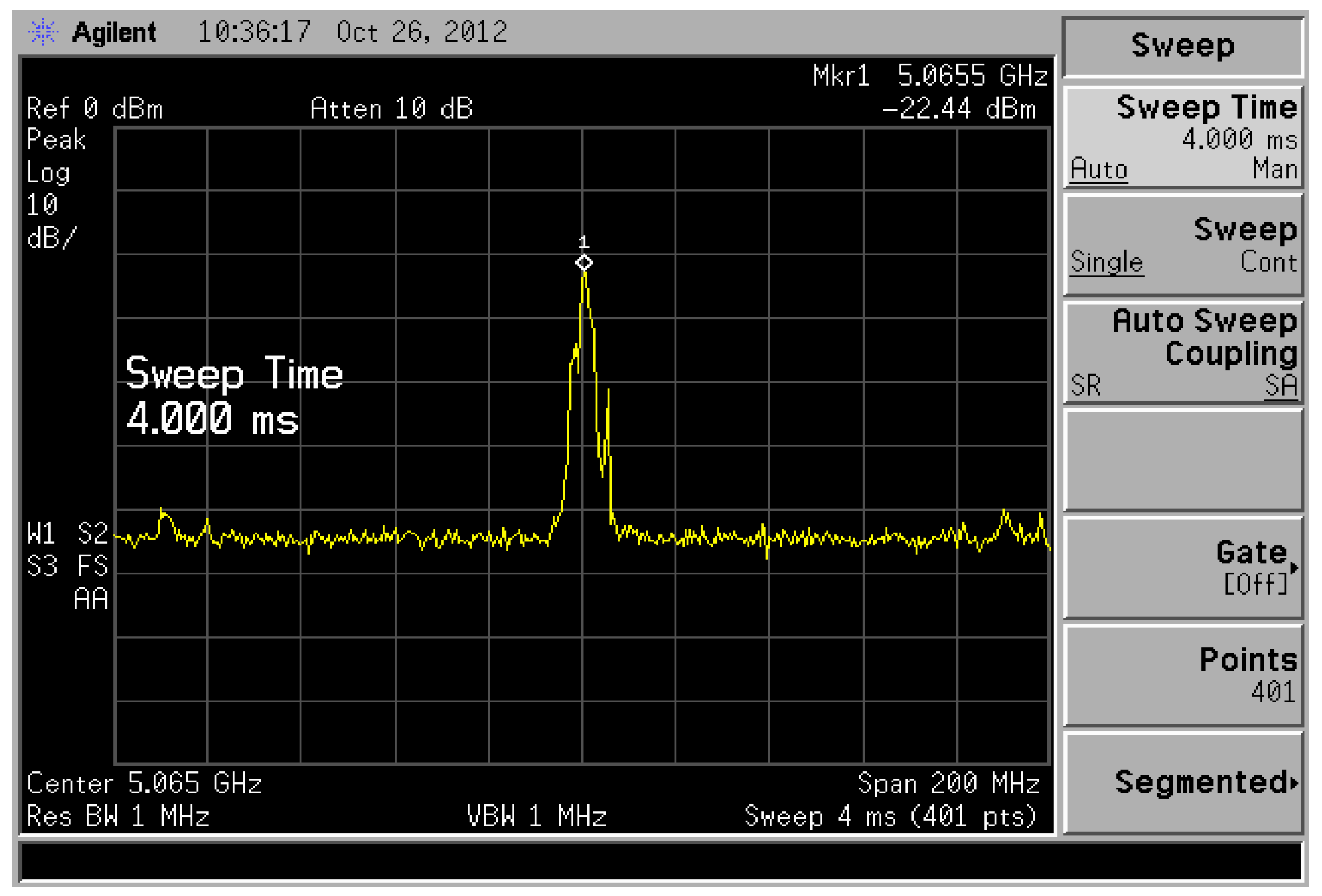

3.2. Measurement Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Singh, S.; Arya, R.K.; Sahana, B.C. RF Circuits for 5G Applications: Designing with mmWave Circuitry, 1st ed.; Wiley-Scrivener: USA, 2023. [Google Scholar]

- Sobot, R. Wireless Communication Electronics: Introduction to RF Circuits and Design Technique, 2nd ed.; Springer: Switzerland, 2021. [Google Scholar]

- Free, C.E.; Aitchison, C.S. RF and Microwave Circuit Design: Theory and Applications, 1st ed.; Wiley: USA, 2021. [Google Scholar]

- De Cock, W.; Steyaert, M.A. CMOS 10GHz voltage controlled, LC-oscillator with integrated high-Q inductor. In Proceedings of the 27th European Solid-State Circuits Conference, Villach, Austria; 2001; pp. 498–501. [Google Scholar]

- Hung, C.M.; Shi, L.; Lagnado, I.; O, K.K. A 25.9-GHz Voltage-controlled oscillator fabricated in a CMOS process. 2000 Symposium on VLSI Circuits. Digest of Technical Papers (Cat. No.00CH37103), Honolulu, HI, USA, 2000; pp. 100–101. [Google Scholar]

- Razavi, B. Design of Analog CMOS Integrated Circuits, 2nd ed.; McGraw-Hill Education: New York, USA, 2017. [Google Scholar]

- Lesson, D.B. A simple model of feedback oscillator noise spectrum. Proceedings of the IEEE, 1966, 54, 329–330. [Google Scholar] [CrossRef]

- Hajimiri, A.; Lee, T.H. A general theory of phase noise in electrical oscillators. IEEE J. Solid-State Circuits, 1998, 33, 179–194. [Google Scholar] [CrossRef]

- Hajimiri, A.; Lee T., H. Design Issuse in CMOS Differential LC Oscillators. IEEE J. Solid-State Circuits 1999, 34, 717–724. [Google Scholar] [CrossRef]

- Hajimiri, A.; Lee, T.H. Oscillator Phase Noise: A Tutorial. IEEE J. Solid-State Circuits 2000, 35, 326–335. [Google Scholar]

- Jerng, A. .; Sodini, C.G. The impact of device type and sizing on phase noise mechanisms. IEEE J. Solid-State Circuits, 2005, 40, 360–369. [Google Scholar] [CrossRef]

- Perraud, L.; Bonnot, L.; Sornin, N.; Pinatel, C. Fully Integrated 10 GHz CMOS VCO for Multi-Band WLAN Applications. Proceedings of 29th Eurpean Solid-State Circuits Conference (ESSCIRC), 2003; pp. 353–356. [Google Scholar]

- Ham, D.; Hajimiri, A. Concepts and methods in optimization of integrated LC VCOS. IEEE J. Solid-State Circuits, 2001, 36, 896–909. [Google Scholar] [CrossRef]

- Liu, J.; Liao, H.; Huang, R. A 5-GHz low-phase noise CMOS VCO with swing boosting technique. Microwave and Optical Technology Letter, 2009, 51, 2061–2064. [Google Scholar] [CrossRef]

- Moon, Y.J.; Roh, Y.-S.; Jeong, C.-Y.; Yoo, C. A 4.39-5.26 GHz LC-Tank CMOS voltage controlled oscillator with small VCO-gain variation. IEEE Microw. Wirel. Compon. Lett., 2009, 19, 524–526. [Google Scholar] [CrossRef]

- Lo, Y.-C.; Silva-Martinez, J. A 5-GHz CMOS LC quadrature VCO with dynamic current-clipping coupling to improve phase noise and phase accuracy. IEEE Trans. Microw. Theory Tech., 2013, 61, 2632–2640. [Google Scholar] [CrossRef]

| Post-simulation | Measurement | |

|---|---|---|

| Frequency (GHz) | 5 | 5.06 |

| Tuning range (MHz) | 1324 | 1124 |

| Phase Noise (dBc/Hz) | -116.5 | -117.69 |

| FOM (dBc/Hz @MHz) | -181.4 | -196.6 |

| Output Power (dBm) | -4.6 | -22.44 |

| Power Consumption (mW) | 8.1 | 3.4 |

| Chip size (mm2) | 0.499 | |

| Ref. | CMOS Tech. (μm) |

Frequency (GHz) |

Phase Noise, dBc/Hz @1MHz | Tuning Range (%) | FOM (dBc/Hz) | PDC (mW) |

PFTN (dB) |

|---|---|---|---|---|---|---|---|

| [11] | 0.18 | 5.3 | -124 | 8 | -190 | 13.5 | -9.09 |

| [14] | 0.18 | 5 | -122.7 | 6.4 | -189.3 | 5.28 | -8.25 |

| [15] | 0.18 | 5.2 | -113.7 | 9.56 | -180 | 9.7 | N/A |

| [16] | 0.13 | 5 | -121 | 20 | -189 | 4.2 | N/A |

| This work | 0.18 | 5.06 | -117.7 | 22.2 | -188.6 | 3.4 | -4.3 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).