Submitted:

03 January 2025

Posted:

06 January 2025

You are already at the latest version

Abstract

Keywords:

1. Introduction

2. Literature Review

2.1. Universal Verification Methodology on System-on-Chip

2.2. Coverage of the Verification

2.3. Verification with Artificial Intelligence

2.4. SPI under Wearable and IoT Devices

3. Materials and Methods

3.1. Materials: What Should Be Tested in SPI and Take Care of

3.2. Methods: Test Plan

3.3. Methods: Designing the Test Plan

| Test Case ID | Description | Expected Outcome |

|---|---|---|

| No_01 | Validate SPI data transmission using default settings | Reliable communication between Master and Slave with default parameters |

| No_02 | Verify SPI clock divider operation across various divider configurations | SPI clock frequency aligns with the expected value for all divider settings |

| No_03 | Check data transfer in MSB-first format | Data is sent and received in MSB-first order |

| No_04 | Check data transfer in LSB-first format | Data is sent and received in LSB-first order |

| No_05 | Confirm full-duplex communication between MOSI and MISO | Both lines successfully transmit and receive data simultaneously |

| No_06 | Evaluate transmission with variable word lengths (8-bit, 16-bit, 32-bit, 64-bit) | Accurate data exchange across all specified word lengths |

| No_07 | Validate control register operations (e.g., GO_BSY, LSB, IE bits) | Control registers respond correctly when set or cleared |

| No_08 | Assess transmission functionality on rising clock edges for both MOSI and MISO | Data is correctly transmitted and received during rising clock edges |

| No_09 | Assess transmission functionality on falling clock edges for both MOSI and MISO | Data is correctly transmitted and received during falling clock edges |

| No_10 | Test compatibility with extended character lengths up to 128 bits | Accurate data transfer across character lengths up to 128 bits |

- Test Item Definition: Test items are defined to cover all possible scenarios, from basic data transmission to advanced functionalities. The provided test items, such as verifying MSB/LSB-first transmission, edge-based communication, and variable word lengths, ensure that all critical aspects of the protocol are tested. These test cases align with the SPI Master Core Specification, which allows flexible configurations like up to 128-bit data transfers, MSB or LSB-first settings, and edge-specific transmission.

- Test Case Prioritization: High-priority cases, such as basic transmission, serve as a foundation for testing more complex scenarios like variable word lengths and multi-character transmissions. This incremental approach minimizes the risk of overlooking fundamental issues.

- Simulation and Emulation: The testing methodology transitions from simulation to emulation for validating SPI under real-world conditions. Simulations are conducted at the register-transfer level (RTL) using models like UVM to verify logical functionality, while emulation replicates the behavior on physical hardware. This dual-layer approach ensures comprehensive coverage and identifies design flaws early in the process.

- Top-Level Verification: Finally, the entire SPI system is tested as part of a fully integrated design to validate interactions between subsystems. This phase confirms the protocol’s reliability under operational constraints typical of wearable and IoT environments.

3.4. Example Test Cases and Their Significance

3.4.1. Fundamental Operation: Ensuring That the Core Settings Perform as Expected

3.4.2. Checks the Clock Divider’s Accuracy: SPI and External Peripherals’ Synchronization

3.4.3. Behavior of Control Registers, Advanced Features

- The interrupt functionality behaves as expected (triggering appropriate actions when specific conditions, like data ready or transmission complete, occur).

- The slave selection works properly, ensuring that the correct device (in a multi-slave configuration) is addressed when the SPI bus is used. This step is important for confirming that the more complex, advanced

- features of the SPI controller are operational and that the device interacts correctly with various external components or peripherals.

3.5. Importance of Sanity Testing in Verification

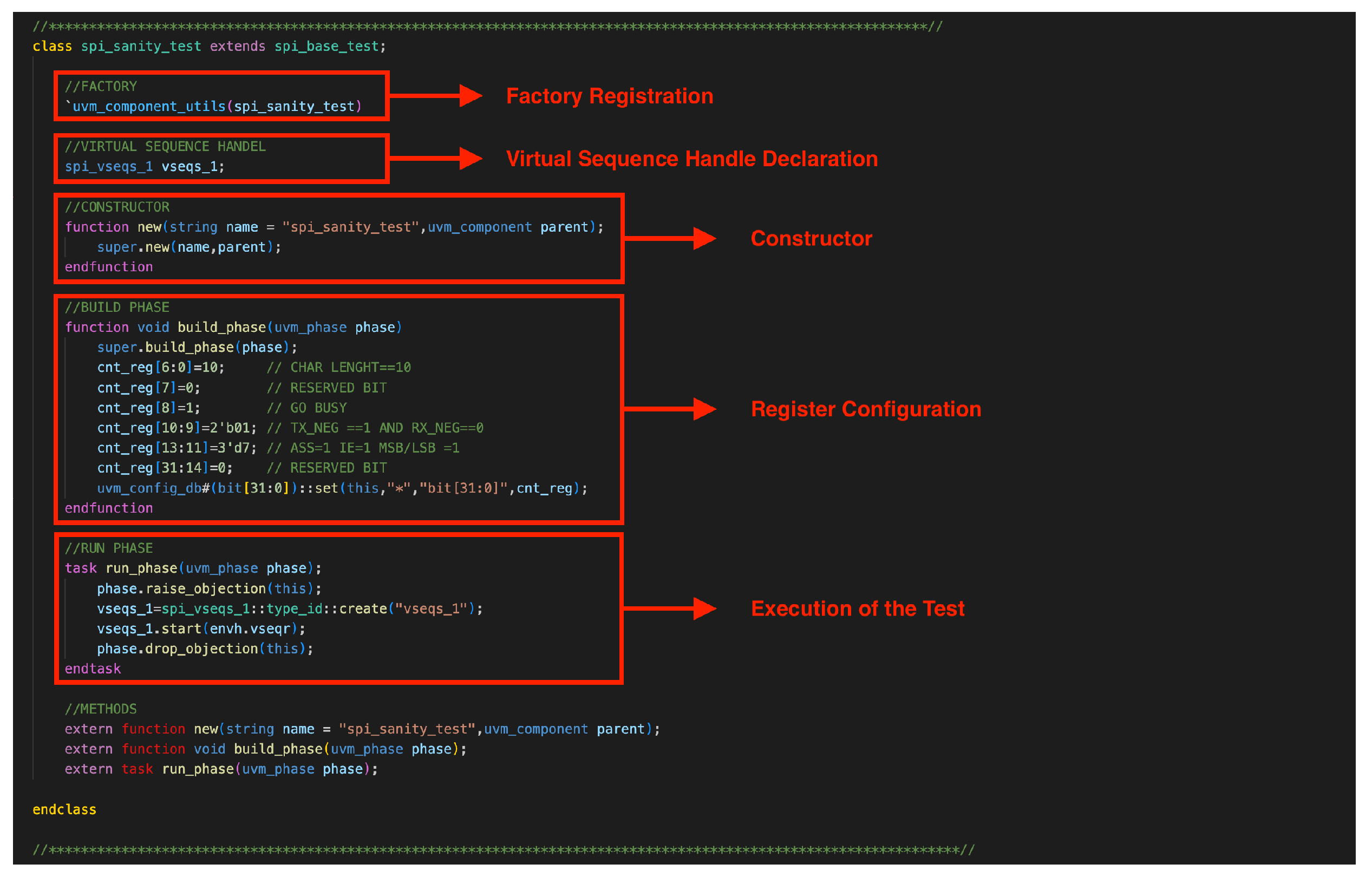

3.6. Breakdown of the Code: spi_sanity_test Class

3.6.1. Factory Registration

3.6.2. Virtual Sequence Handle Declaration

3.6.3. Constructor

3.7. Build Phase: Register Configuration

- CHAR LENGTH (cnt_reg[6:0] = 10): This specifies the number of bits per transaction. A value of 10 indicates that each SPI transfer consists of 10 bits, a standard configuration for validating medium-length transfers during a sanity test.

- RESERVED BIT (cnt_reg[7] = 0): Reserved bits are set to 0 for consistency and to ensure no undefined behaviors in register configurations.

- GO BUSY (cnt_reg[8] = 1): The GO or BUSY flag signals the SPI interface to initiate a transfer. Setting this bit ensures that the SPI controller begins a transaction during the test.

- TX_NEG and RX_NEG (cnt_reg[10:9] = 2’b01): These bits control the data capture and transmission phase. Setting TX_NEG = 1 and RX_NEG = 0 configures the transmitter to change data on the falling edge and the receiver to sample data on the rising edge, a common configuration for SPI protocols.

-

ASS, IE, MSB/LSB (cnt_reg[13:11] = 3’d7):

- -

- ASS (Automatic Slave Select): A value of 1 ensures the chip select (CS) signal is managed automatically.

- -

- IE (Interrupt Enable): Enabling interrupts (IE = 1) ensures that any irregularities during communication are flagged immediately.

- -

- MSB/LSB: Setting this to 1 configures the SPI to transmit the most significant bit (MSB) first, which is standard for many SPI devices.

- RESERVED BITS (cnt_reg[31:14] = 0): Setting all unused bits to 0 prevents unintentional interference.

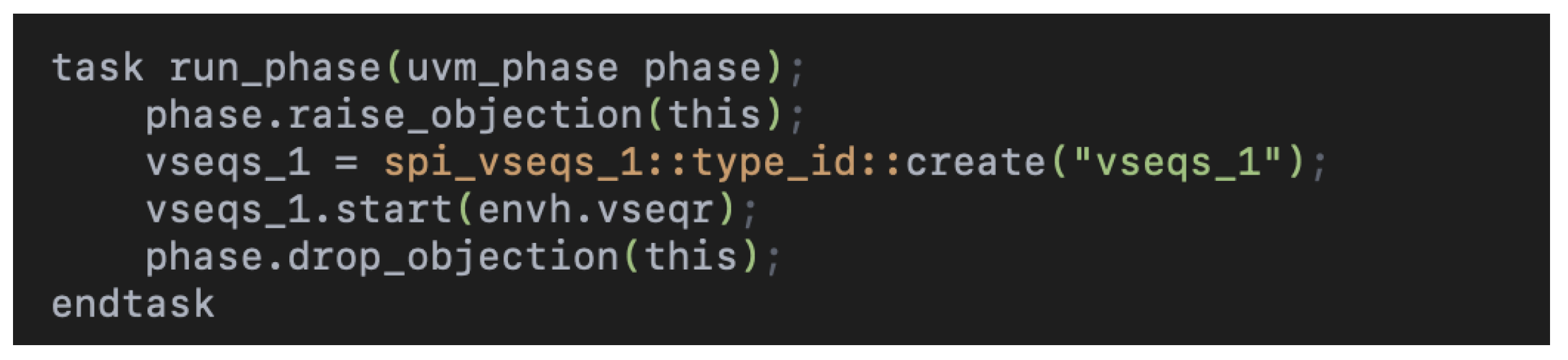

3.8. Run Phase: Execution of the Test

- Raise/Drop Objection: These methods synchronize the testbench phases. Raising an objection indicates that the test is still executing, while dropping it signals completion.

- Sequence Creation and Execution: The spi_vseqs_1 sequence is dynamically created and started on the virtual sequencer (envh.vseqr). This abstraction ensures that the generated transactions align with the defined protocol and environmental setup.

4. Results

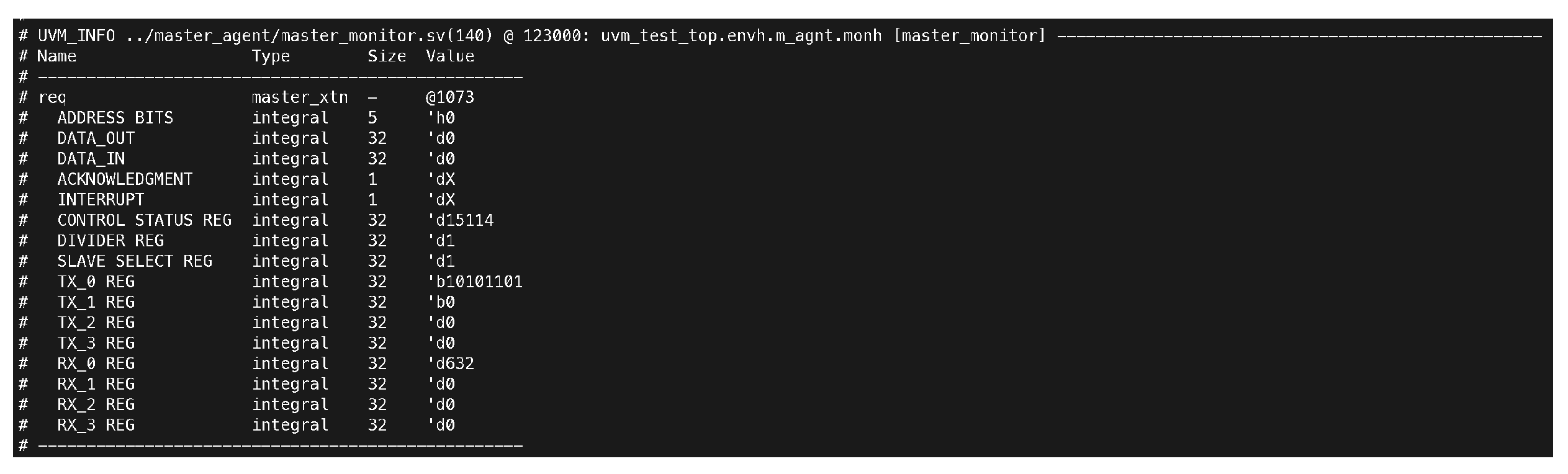

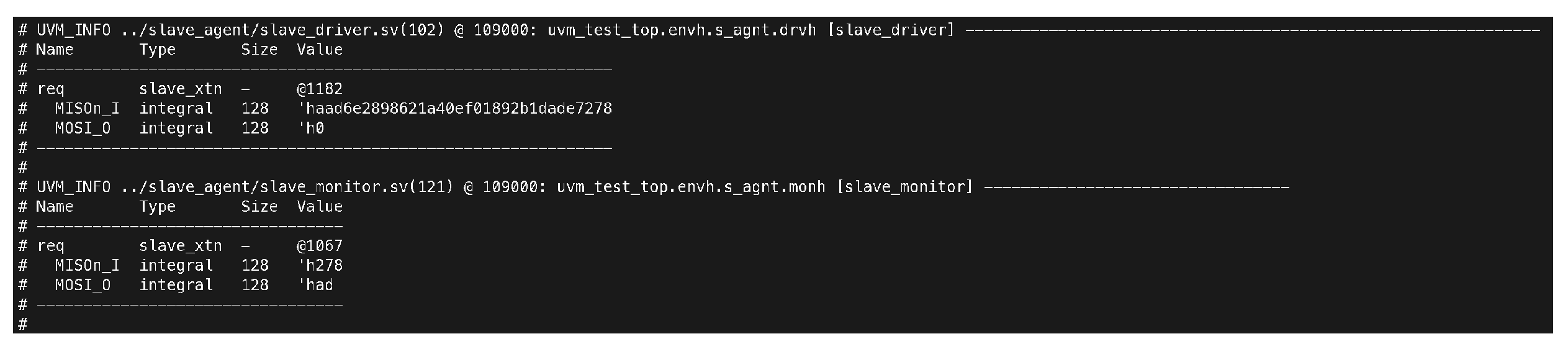

4.1. Master and Slave Devices Under the Testbench

4.2. Monitor and Driver Devices Under the Testbench

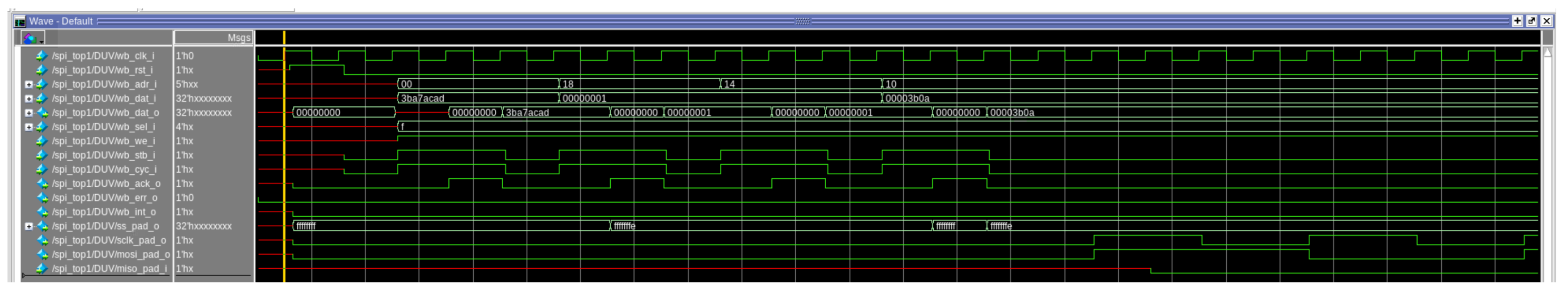

4.3. Waveform Demonstration on Result

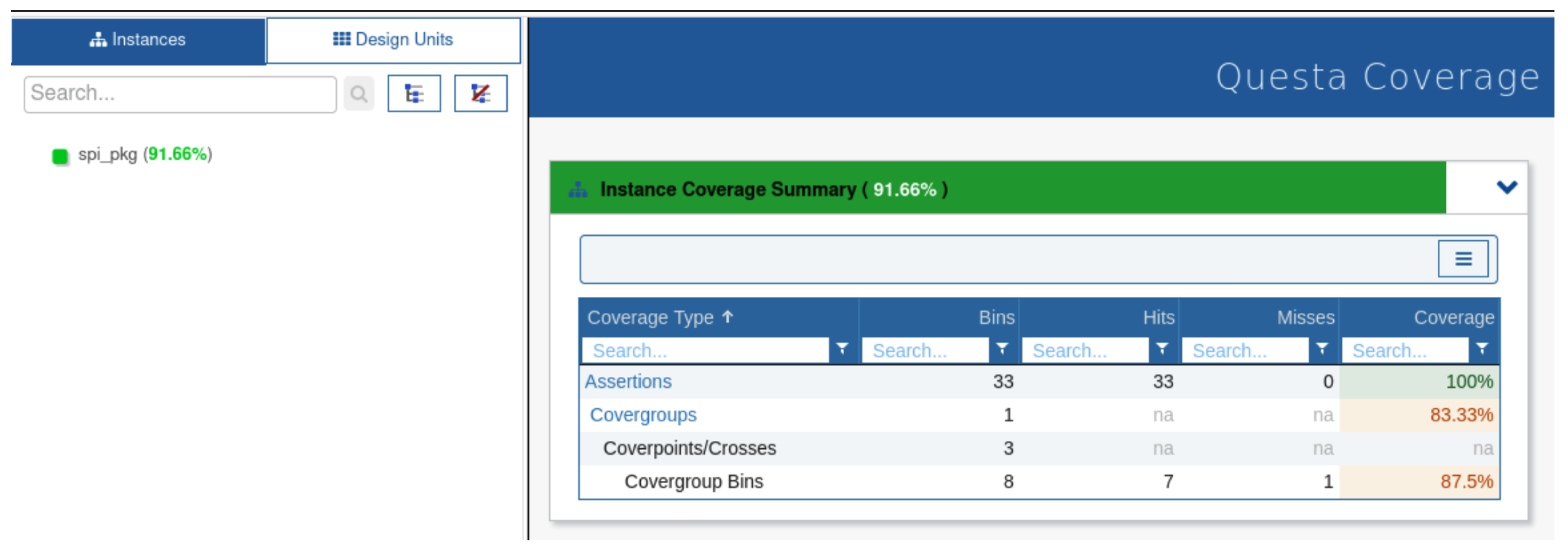

4.4. Coverage Analysis Summary

5. Discussion

5.1. Potential Areas for Improvement

- Additional Assertions: While the test effectively validates initial configurations and basic operation, it could benefit from assertions to monitor specific runtime conditions. For example, verifying that the GO BUSY flag clears after a transaction or that the MSB/LSB configuration aligns with transmitted data would enhance the test’s robustness.

- Coverage Metrics: The test does not explicitly mention functional coverage or code coverage metrics. Adding a coverage model that tracks key aspects, such as edge cases in character lengths or timing variations in TX/RX signals, would provide quantitative feedback on the test’s effectiveness.

- Error Injection: To further validate the SPI design, the test could introduce scenarios with intentional misconfigurations. For example, setting the reserved bits (cnt_reg[7] or cnt_reg[31:14]) to non-zero values could test the DUT’s resilience to unexpected inputs.

- Scalability to Larger Configurations: While the test focuses on a 10-bit character length, SPI designs often support configurable lengths (e.g., 8, 16, 32 bits). Expanding the test to dynamically handle multiple configurations would enhance its utility.

5.2. Educational Value and Industry Relevance

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| SPI | Serial Peripheral Interface |

| UVM | Universal Verification Methodology |

| IoT | Internet of Thing |

| RAL | Register Abstraction Layer |

| RTL | Register Transaction Level |

| DUT | Design Under Test |

References

- Dobrescu, C. C.; González, I.; Carneros-Prado, D.; Fontecha, J.; Nugent, C., "Direct Memory Access-Based Data Storage for Long-Term Acquisition Using Wearables in an Energy-Efficient Manner," Sensors, 2024, 24, 4982. [CrossRef]

- J. Chen and S. Huang, "Analysis and Comparison of UART, SPI and I2C," 2023 IEEE 2nd International Conference on Electrical Engineering, Big Data and Algorithms (EEBDA), Changchun, China, 2023, pp. 272–276, . [CrossRef]

- V. R. Kolagatla, A. Raveendran, and V. Desalphine, "A Novel and Efficient SPI enabled RSA Crypto Accelerator for Real-Time Applications," 2024 28th International Symposium on VLSI Design and Test (VDAT), Vellore, India, 2024, pp. 1–6, . [CrossRef]

- S. Mishra, A. Ray, M. Singh, S. Venkatesan, and A. S. Anand, "Automated Hardware Auditing Testbed for UART and SPI based IoT Devices," 2023 10th International Conference on Internet of Things: Systems, Management and Security (IOTSMS), San Antonio, TX, USA, 2023, pp. 75–82, . [CrossRef]

- Z. Hongxiang, "Research on Airborne Wireless Pressure Testing Network System Based on Zigbee," 2024 IEEE 2nd International Conference on Image Processing and Computer Applications (ICIPCA), Shenyang, China, 2024, pp. 211–215, . [CrossRef]

- X. He, K. Yuan, Y. Wang, and X. Sun, "Design of Industrial Hot Air Furnace Monitoring System Based on ZigBee," 2023 5th International Academic Exchange Conference on Science and Technology Innovation (IAECST), Guangzhou, China, 2023, pp. 1546–1550, . [CrossRef]

- J. P. Kadambarajan, P. Kadarkarai, B. Kalyani, M. R. Bathul, T. Sandhya, and M. Greeshma, "SPI Verification Monitor Module Using UVM," 2024 10th International Conference on Advanced Computing and Communication Systems (ICACCS), Coimbatore, India, 2024, pp. 1838–1843, . [CrossRef]

- P. Rajendra Prasad and S. P. Venu Madhava Rao, "Data Transactions from UART to SPI Slave Devices through UART-SPI Controller for an SOC," Advance in Electronic and Electric Engineering, ISSN 2231-1297, vol. 3, no. 4, pp. 413–420, 2013.

- S. Choudhury, G. K. Singh, and R. M. Mehra, "Design and Verification Serial Peripheral Interface (SPI) Protocol for Low Power Applications," International Journal of Innovative Research in Science, Engineering and Technology, ISSN 2319-8753, vol. 3, no. 10, pp. 1–6, October 2014.

- Y. R. Keesara, Y. Reddy, R. Vatsa, and S. Singh, "79 4K HDMI USB3 capture card reference design," Intelligent Circuits and Systems, 517. June 2020.

- Álvarez JL, Mozo JD, Durán E. Analysis of Single Board Architectures Integrating Sensors Technologies. Sensors. 2021;21(18):6303. doi:10.3390/s21186303.

- Sheba MA, Mansour DA, Abbasy NH. A new low-cost and low-power industrial internet of things infrastructure for effective integration of distributed and isolated systems with smart grids. IET Generation, Transmission & Distribution. Published August 12, 2023. doi:10.1049/gtd2.12951.

- He W. Design of supervisory controllers and ultra-low power data loggers for hybrid power systems. Master’s thesis, Memorial University of Newfoundland; 2024.

- C. K. Shaila, G. Manoj, P. S. Divya, and M. Vijila, "Functional Verification of SPI Protocol using UVM based on AMBA Architecture for Flash Memory Applications," 2023 4th International Conference on Signal Processing and Communication (ICSPC), Coimbatore, India, 2023, pp. 311–315, . [CrossRef]

- Sharma G, Bhargava L, Kumar V. Hybrid learning scenario path selection and abstraction framework for smart verification of complex SoCs. The Journal of Supercomputing. 2022:1-27.

- D’Souza KJ. Database-driven FPGA workflow for digital system verification. Master’s thesis, Universitat Politècnica de Catalunya; 2024.

- Kohútka L, Mach J. A new FPGA-based task scheduler for real-time systems. Electronics. 2023;12(8):1870.

- Liu C, et al. A universal-verification-methodology-based testbench for the coverage-driven functional verification of an instruction cache controller. Electronics. 2023;12(18):3821.

- Das S, et al. Synthesis of system Verilog assertions. In: Proceedings of the Design Automation & Test in Europe Conference. Vol. 2. IEEE; 2006.

- Khalil A, et al. Automatic generation of System Verilog assertions for verification of safety mechanisms. In: 2024 4th Interdisciplinary Conference on Electrics and Computer (INTCEC). IEEE; 2024.

- Dranga D, Dumitrescu C. Artificial intelligence application in the field of functional verification. Electronics. 2024;13(12):2361.

- Srot S. SPI controller core. 2002. Available at: http://www.opencores.org/projects/spi/.

- Koroteev MV. BERT: a review of applications in natural language processing and understanding. arXiv preprint. 2021;arXiv:2103.11943.

- Jawahar G, Sagot B, Seddah D. What does BERT learn about the structure of language? In: ACL 2019 - 57th Annual Meeting of the Association for Computational Linguistics; 2019.

- Zhou C, et al. A comprehensive survey on pretrained foundation models: A history from BERT to ChatGPT. International Journal of Machine Learning and Cybernetics. 2024;1-65.

- Soni S, Chouhan SS, Rathore SS. TextConvoNet: A convolutional neural network based architecture for text classification. Applied Intelligence. 2023;53(11):14249-14268.

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).