Submitted:

16 December 2024

Posted:

18 December 2024

You are already at the latest version

Abstract

Keywords:

1. Introduction

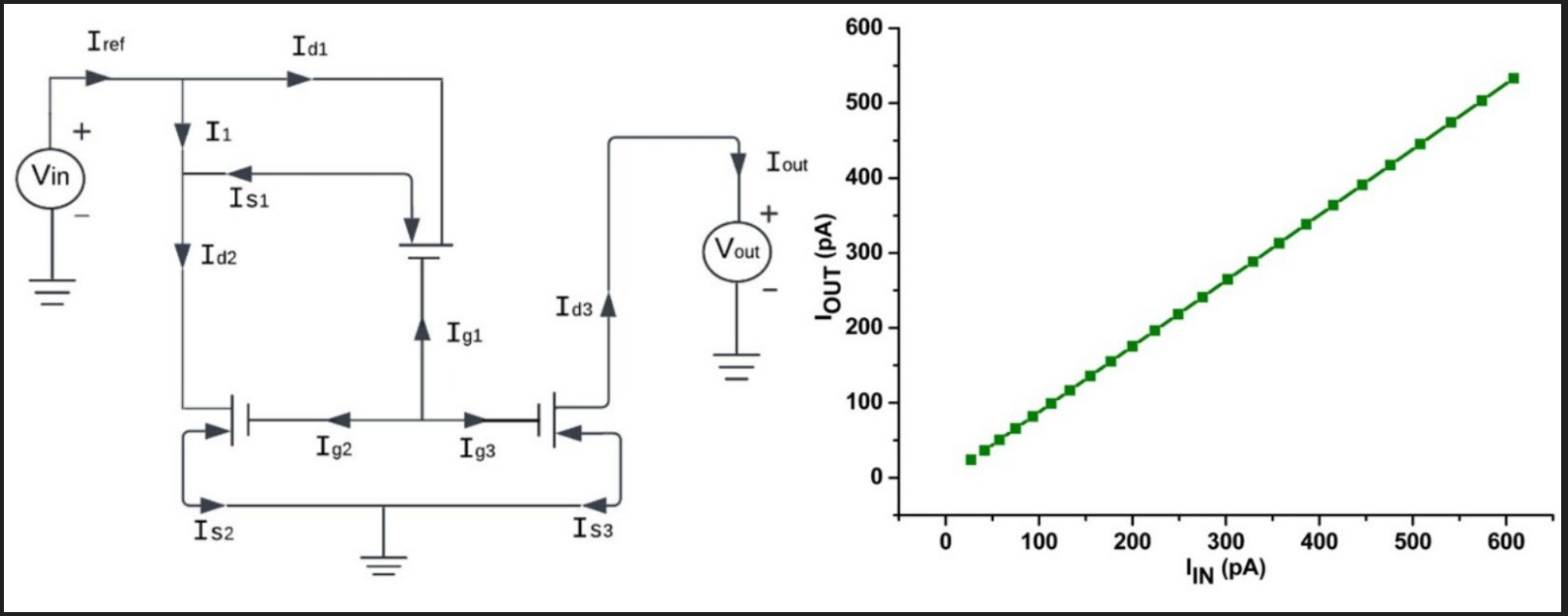

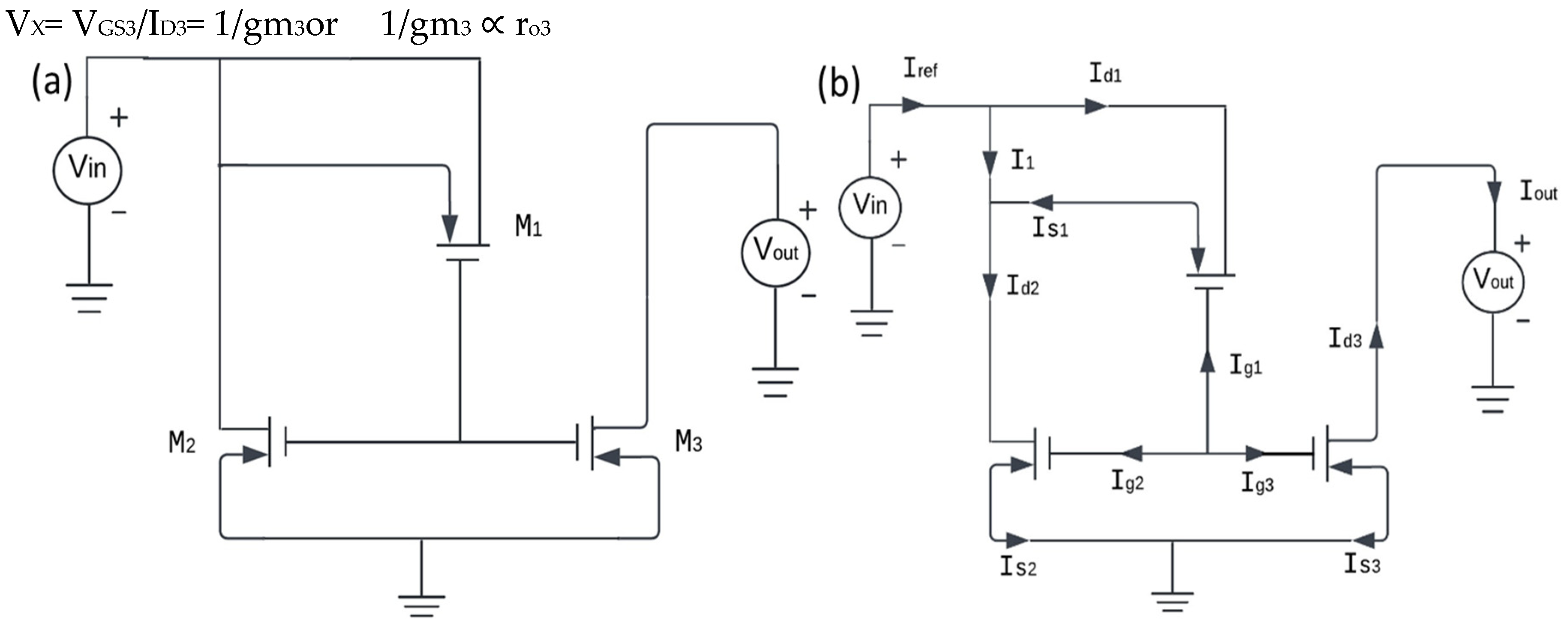

2. Device Simulation Data

3. Theoritical Analysis of Proposed Current Mirror

ID3 = IS3

IS2 + IS3 = 0

IS3 = - IS2

ID3 = IOUT = - IS2 = - ID2

ID2 = IS1 + I1

ID2 = ID1 + I1 = IREF

IOUT = - IREF

Vx= Ix/gm3

Output Impedance = 1/gm3 = 1/ (ID3/VGS3)

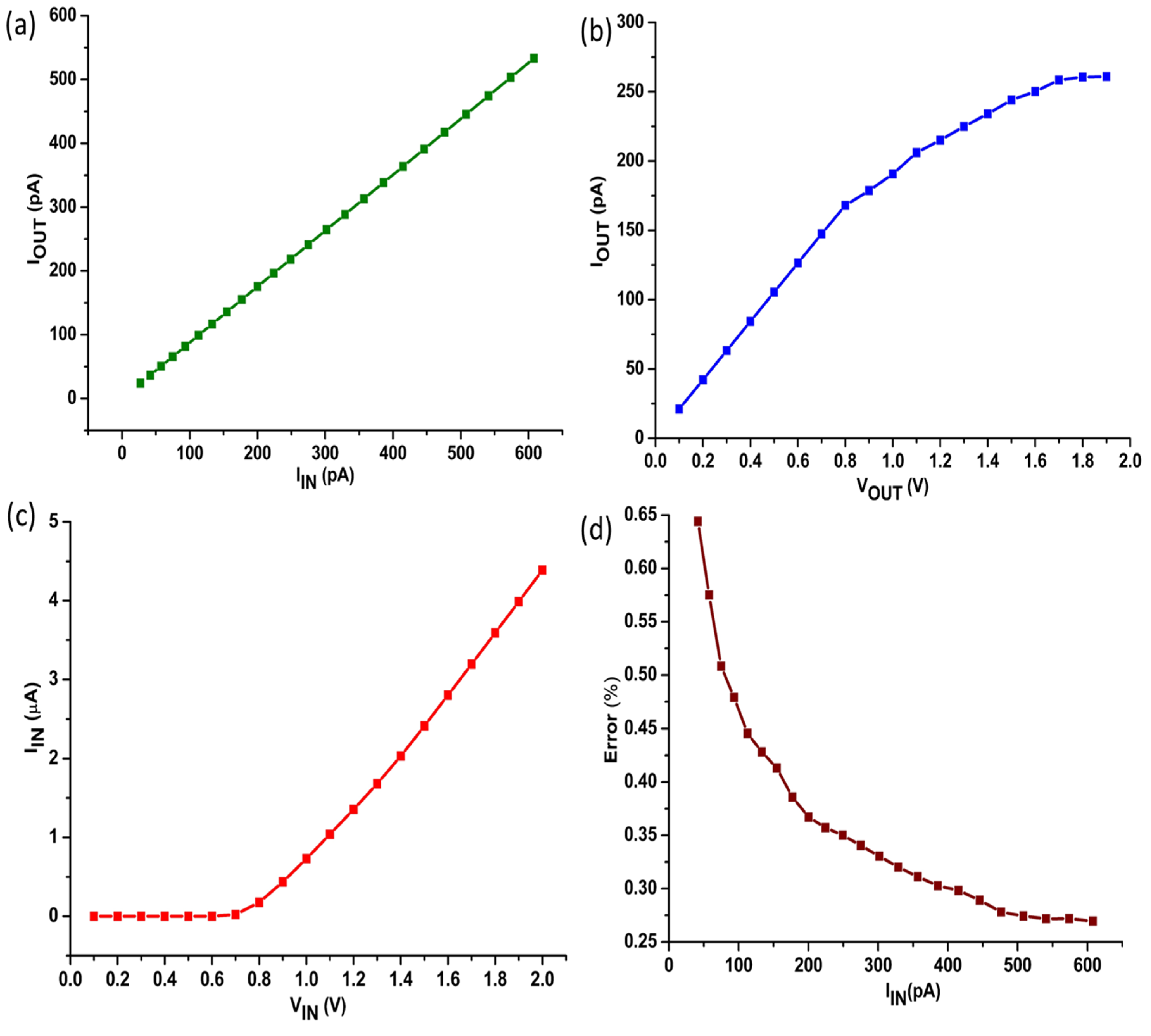

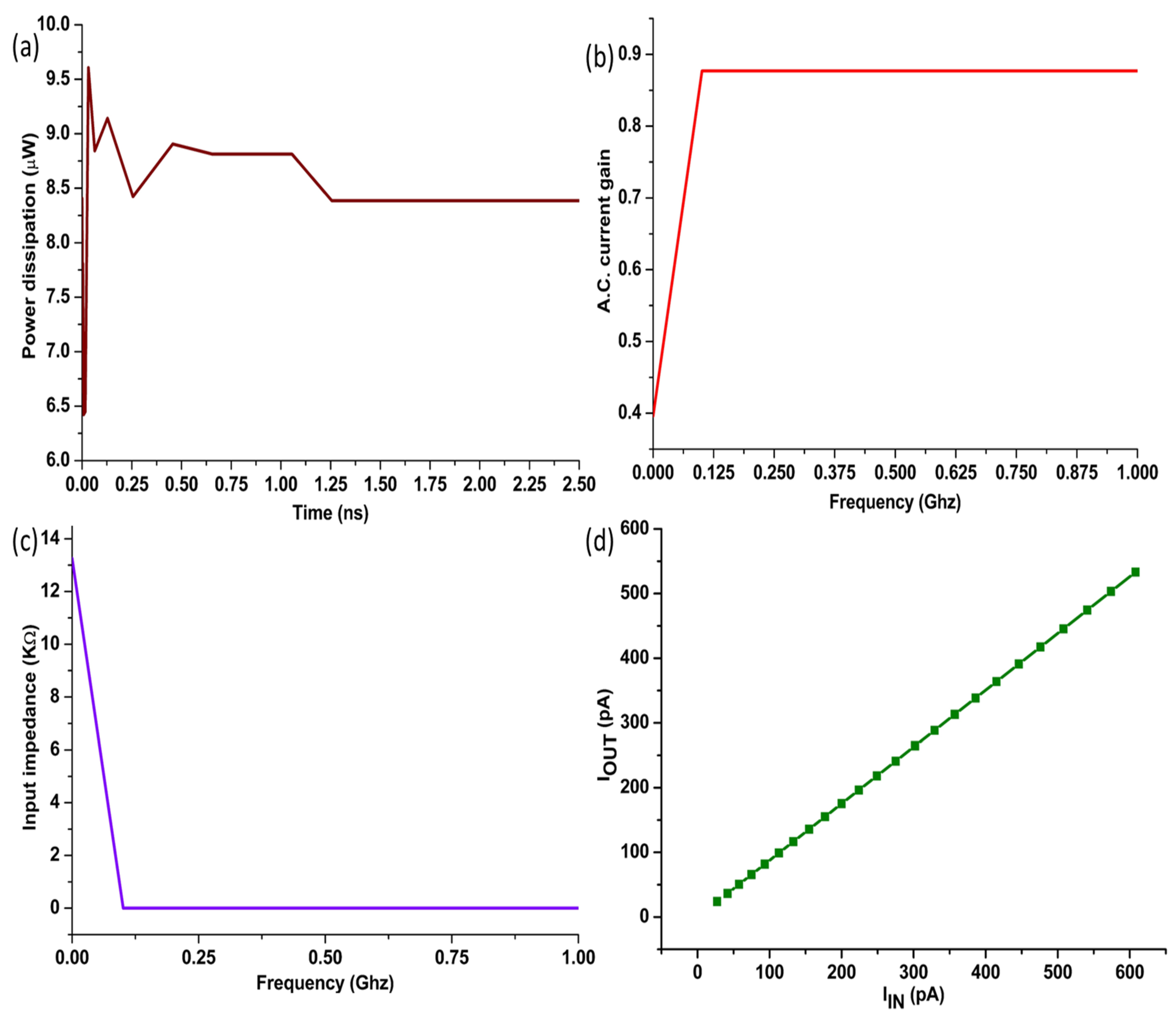

4. Result and Discussion

5. Conclusion

Notes

References

- Li, Y.; Wang, H.; Trik, M. Design and simulation of a new current mirror circuit with low power consumption and high performance and output impedance. Analog Integr Circuits Signal Process 2024, 119, 29–41. [Google Scholar] [CrossRef]

- Al-Absi, M.A. A novel highly accurate current mirror. International Journal of Electronics 2009, 96. [Google Scholar] [CrossRef]

- M. K. ; K. C. K. ; N. K. ; Atmakuri, C.M. Performance enhancement of flipped voltage follower current mirror in nanoscale technology. International Journal of Nano Dimension 2024, 15. [Google Scholar]

- Monfaredi, K.; Baghtash, H.F. An Extremely Low-Voltage and High-Compliance Current Mirror. Circuits Syst Signal Process 2020, 39, 30–53. [Google Scholar] [CrossRef]

- Tang, L.-S.; Huang, M.-H.; Kuo, P.-Y.; Yang, P.-H. Design of A Low Dropout Voltage Regulator Using Nested-Current-Mirror Rail-to-Rail-Output Single-Stage Amplifier. In Proceedings of the 2024 International Conference on Consumer Electronics - Taiwan (ICCE-Taiwan), Jul. 2024; IEEE; pp. 369–370. [Google Scholar] [CrossRef]

- Marani, R.; Perri, A.G. A Simulation Study of Noise Behavior in Basic Current Mirror using CNTFET and MOSFET. International Journal of Emerging Technology and Advanced Engineering 2021, 11, 13–18. [Google Scholar] [CrossRef] [PubMed]

- Pritty; Jhamb, M. A 0.8-Volt 29.52-μW Current Mirror-Based OTA Design for Biomedical Applications. Journal of Circuits, Systems and Computers 2023, 32. [Google Scholar] [CrossRef]

- Domala, N.; Sasikala, G. Low Power Low Voltage Current Mirror for Analog & Mixed Signal Applications. In Proceedings of the 2020 4th International Conference on Electronics, Communication and Aerospace Technology (ICECA), Nov. 2020; IEEE; pp. 465–470. [Google Scholar] [CrossRef]

- Domala, N.; Sasikala, G. Low Power Low Voltage Current Mirror for Analog & Mixed Signal Applications. In Proceedings of the 2020 4th International Conference on Electronics, Communication and Aerospace Technology (ICECA), Nov. 2020; IEEE; pp. 465–470. [Google Scholar] [CrossRef]

- Aggarwal, B.; Gupta, M.; Gupta, A.K. A comparative study of various current mirror configurations: Topologies and characteristics. Microelectronics J 2016, 53, 134–155. [Google Scholar] [CrossRef]

- Guran, I.-C.; Florescu, A.; Perisoara, L.A. A Novel Frequency Measurement Methodology for Clock Synchronization in SPICE-Based Simulators. IEEE Access 2023, 11, 117030–117039. [Google Scholar] [CrossRef]

- Guran, I.-C.; Florescu, A.; Perisoara, L.-A.; Vasile, A.; Oancea, C.-D. Fully Analog Clock Signal Generator for SPICE based simulators. In Proceedings of the 2022 14th International Conference on Electronics, Computers and Artificial Intelligence (ECAI), Jun. 2022; IEEE; p. 1. [Google Scholar] [CrossRef]

- Viman, L.; Chindris, G.; Pop, O. A new methodology for using OrCAD applications on a network. In Proceedings of the 24th International Spring Seminar on Electronics Technology. Concurrent Engineering in Electronic Packaging. ISSE 2001. Conference Proceedings (Cat. No.01EX492); IEEE; pp. 238–242. [CrossRef]

- Matousek, D.; Rejfek, L. Practical aspects of realisation of negative charge pumps. In Proceedings of the 2017 International Conference on Applied Electronics (AE), Sep. 2017; IEEE; p. 1. [Google Scholar] [CrossRef]

- Monfaredi, K.; Baghtash, H.F. An Extremely Low-Voltage and High-Compliance Current Mirror. Circuits Syst Signal Process 2020, 39, 30–53. [Google Scholar] [CrossRef]

- Chan, T.Y.; Chen, J.; Ko, P.K.; Hu, C. The impact of gate-induced drain leakage current on MOSFET scaling. In Proceedings of the 1987 International Electron Devices Meeting; IRE, 1987; pp. 718–721. [Google Scholar] [CrossRef]

- Yang, B.-D.; Shin, Y.-K.; Lee, J.-S.; Lee, Y.-K.; Ryu, K.-C. An accurate current reference using temperature and process compensation current mirror. In Proceedings of the 2009 IEEE Asian Solid-State Circuits Conference, Nov. 2009; IEEE; pp. 241–244. [Google Scholar] [CrossRef]

- Raguvaran, E.; Prasath, N.D.; Alexander, J.; Prithiviraj, N.; Santhanalakshmi, M. A very-high impedance current mirror for bio-medical applications. In Proceedings of the 2011 IEEE Recent Advances in Intelligent Computational Systems, Sep. 2011; IEEE; pp. 828–830. [Google Scholar] [CrossRef]

- Pritty; Jhamb, M. Ultra low power current mirror design with enhanced bandwidth. Microelectronics J 2021, 113, 105063. [Google Scholar] [CrossRef]

- Kawahito, S.; Tadokoro, Y. CMOS class-AB current mirrors for precision current-mode analog-signal-processing elements. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing 1996, 43, 843–845. [Google Scholar] [CrossRef]

- Chen, C.; Wu, X.; Yuan, X.; Zheng, X. A New Technique for the Subdomain Method in Predicting Electromagnetic Performance of Surface-Mounted Permanent Magnet Motors With Shaped Magnets and a Quasi-Regular Polygon Rotor Core. IEEE Transactions on Energy Conversion 2023, 38, 1396–1409. [Google Scholar] [CrossRef]

- Safari, L.; Minaei, S. A Low-Voltage Low-Power Resistor-Based Current Mirror and Its Applications. Journal of Circuits, Systems and Computers 2017, 26, 1750180. [Google Scholar] [CrossRef]

- Wang, G.; Wu, J.; Trik, M. A Novel Approach to Reduce Video Traffic Based on Understanding User Demand and D2D Communication in 5G Networks. IETE J Res 2024, 70, 5649–5665. [Google Scholar] [CrossRef]

- Yu, J.; et al. Synergistic piezoelectricity enhanced BaTiO3/polyacrylonitrile elastomer-based highly sensitive pressure sensor for intelligent sensing and posture recognition applications. Nano Res 2023, 16, 5490–5502. [Google Scholar] [CrossRef]

- Jindal, C.; Pandey, R. A high output resistance, wide bandwidth, and low input resistance current mirror using flipped voltage follower cell. International Journal of Circuit Theory and Applications 2021, 49, 3286–3301. [Google Scholar] [CrossRef]

| Parameters | C. Chen et al. [21] | L. Safari et al. [22] | G. Wang et al. [23] | J. Yu et al. [24] | C. Jindal et al. [25] | This work |

| Current range (A) | 1 | 100 µ | NA | 0.7 | 300 µ | 500 p |

| Minimum input voltage (V) | 1.8 | 0.04 | 0.7 | 1.2 | 0.34 | 0.8 |

| Minimum output voltage (V) | 1.8 | 0.1 | NA | 91 m | 0.83 | 1.2 |

| Input resistance (Ω) | 6.4 | 496 | NA | 500 | 161.34 | 3.643 K |

| Output resistance (Ω) | 0.362 M | 1 M | NA | 1980 M | 19.83 G | 20 G |

| Power dissipation (μW) | 0.35 | 154 | 3.1 | 1.56 | 94 | 8.39 |

| Current transfer error (%) | 4 | 0.6 | 3 | 5 | 0.52 | 0.2743 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).