Submitted:

14 December 2024

Posted:

17 December 2024

You are already at the latest version

Abstract

Keywords:

1. Introduction

1.1. Related Work

2. Materials and Methods

2.1. Background

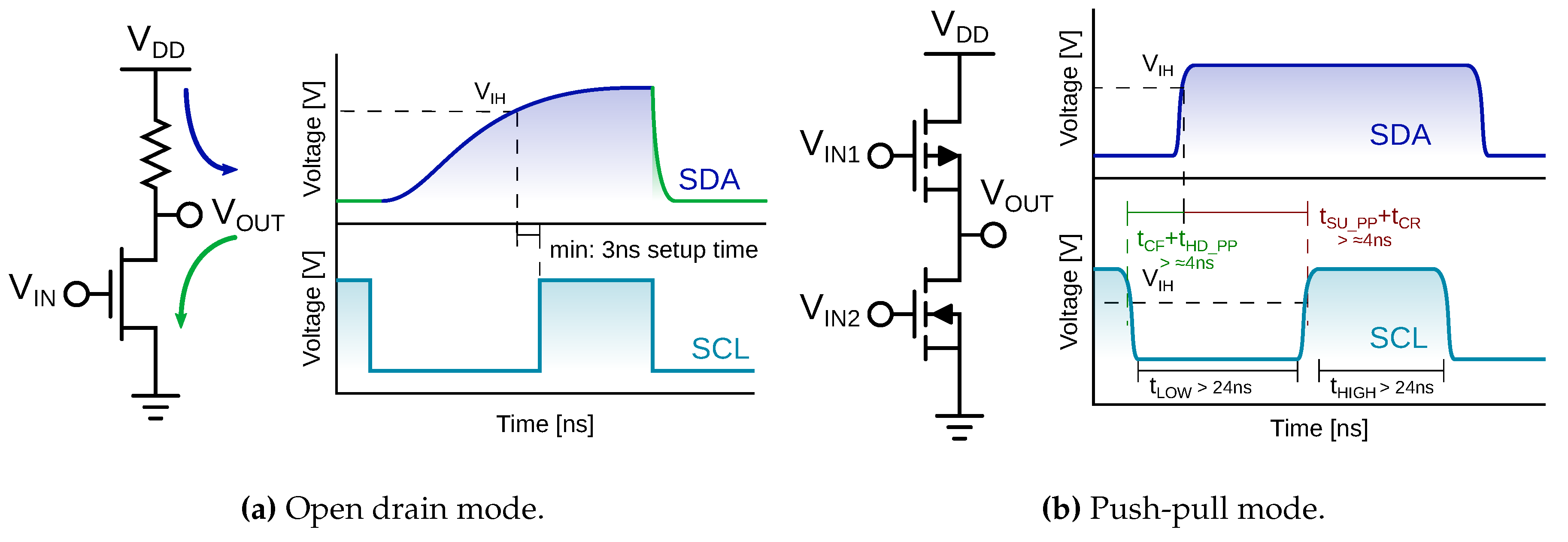

2.1.1. Standard Data Rate

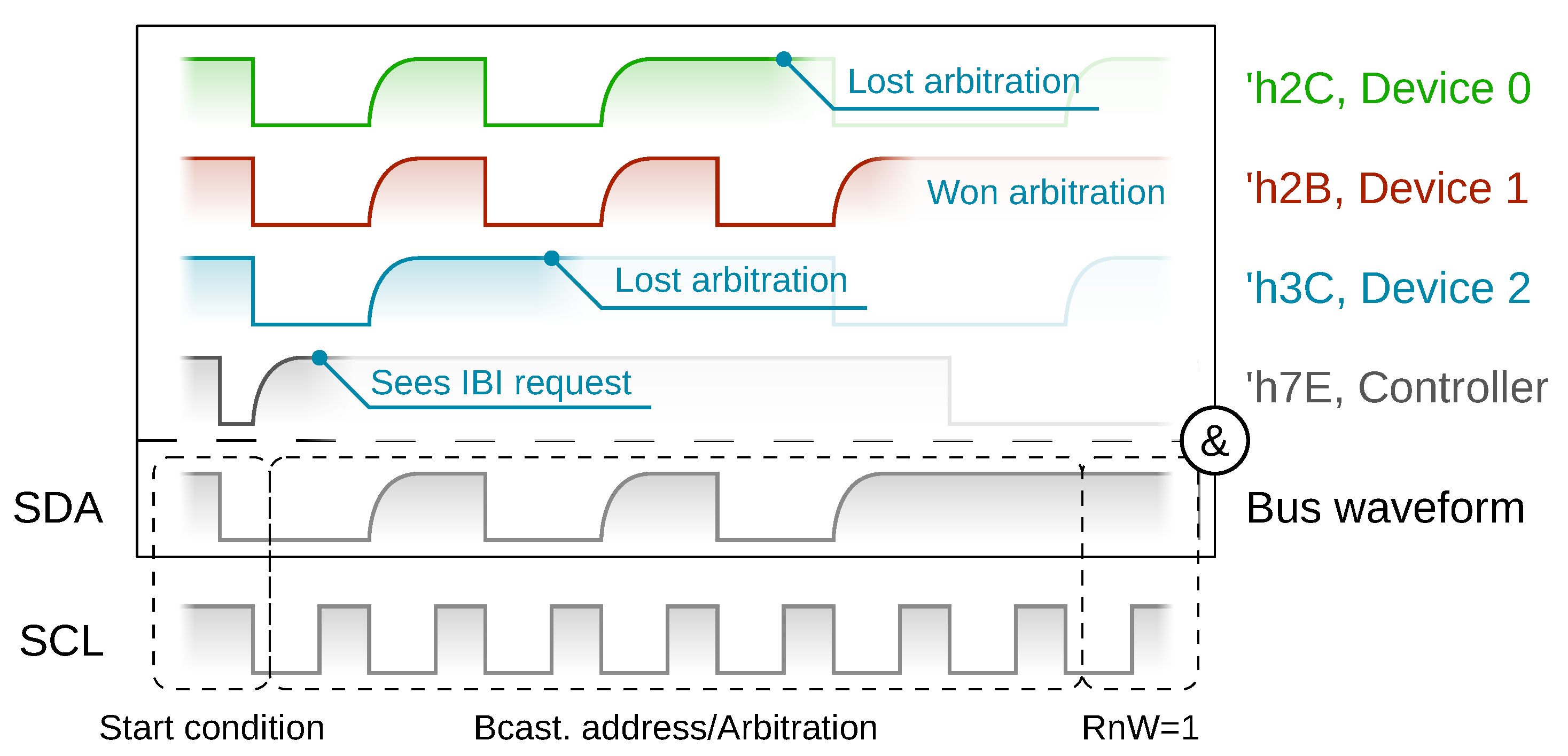

2.1.2. In-Band Interrupt

- 1.

- The controller initiates a transfer with a Start, followed by the I3C Broadcast Address or a target device address; the interrupt sender drives the SDA with its own address.

- 2.

- The bus is in bus available condition and the interrupt issuer pulls the SDA line low, the controller notices, pulls the SCL line low (completing a Start), and provides clocks cycles for the peripheral to send its address.

2.1.3. Dynamic Address Assignment

2.1.4. Hot-Join

- 1.

- The device is connected to the bus, but is unpowered until needed. This is useful in applications where power usage management is critical.

- 2.

- The device is connected physically to the bus after the bus has been configured.

2.1.5. High Data Rate Modes

- 1.

- Double Data Rate.

- 2.

- Bulk Transfer.

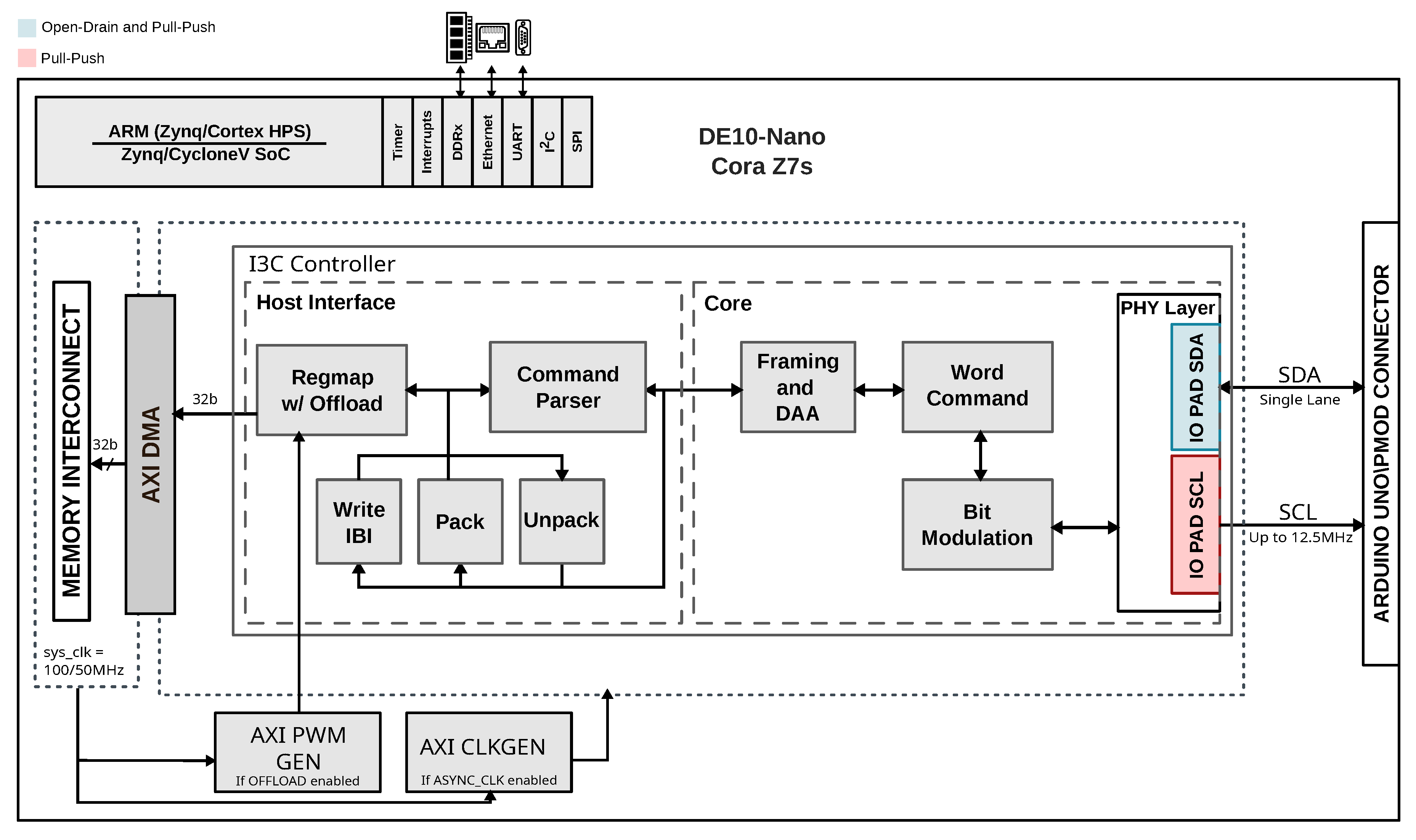

2.2. Implementation

2.2.1. Project Structure

2.2.2. Selected I3C Features

- Single Data Rate mode.

- In-Band Interrupt.

- Dynamic address.

- I²C backward compatibility.

2.2.3. Hardware and tools

2.2.4. HDL Implementation

2.2.5. Linux Solution

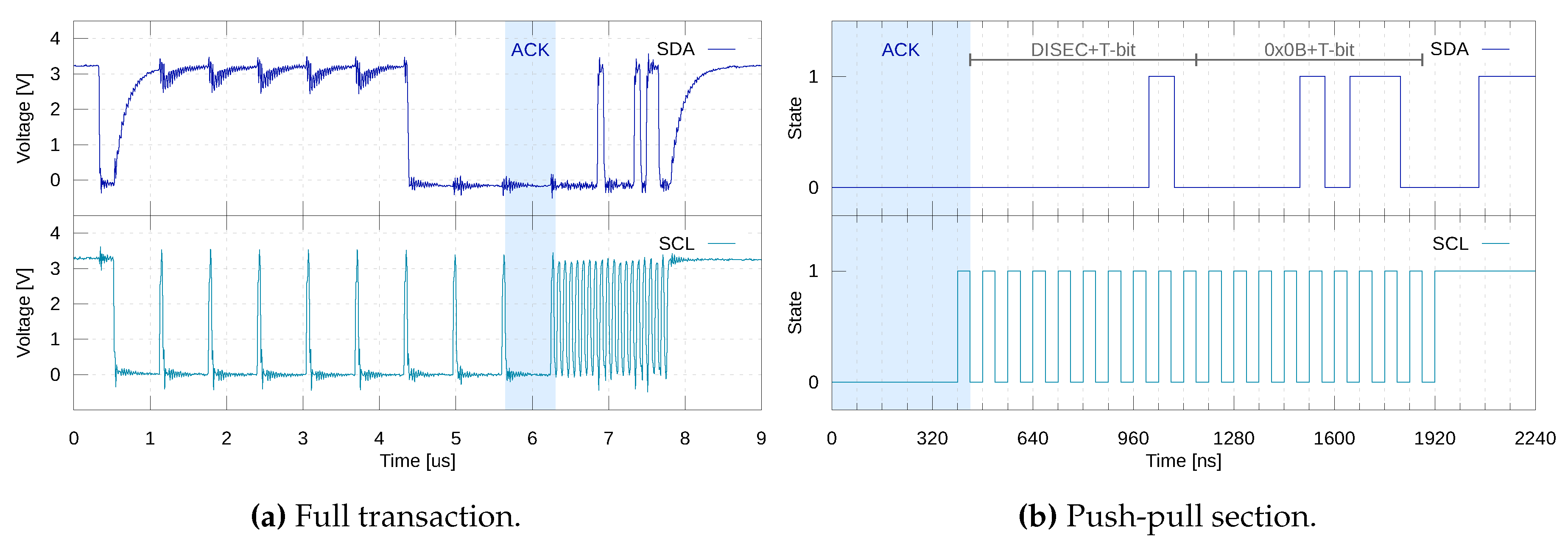

3. Results

4. Discussion

Author Contributions

Funding

Data Availability Statement

-

HDL (library):github.com/analogdevicesinc/hdl (38037641af3a52bb2e61cadaf95fc9f2cf9c96ef)

-

HDL (sample project):github.com/gastmaier/hdl-i3c-bus (d7711b8a832aeb190095a98d4caf4f3687ea8b45)

-

HDL testbench:github.com/analogdevicesinc/testbenches (9bbb0f541cf0aaec40f3831f6c7e5a32e79bcc0b)

-

Linux driver:github.com/analogdevicesinc/linux/tree/i3c (67ede2dc76345c1a8ec50933a45eb6b58be7be3c)

Conflicts of Interest

Abbreviations

| ACK-bit | Acknowledge-bit. |

| ARM | Advanced RISC Machines. |

| AXI | Advanced eXtensible Interface |

| CCC | Common Command Code. |

| DAA | Dynamic Address Assignment. |

| DMA | Direct Memory Access. |

| FPGA | Field-programmable Gate Array. |

| HDL | Hardware Description Language. |

| I²C | Inter-Integrated Circuit. |

| I3C | Improved Inter-Integrated Circuit. |

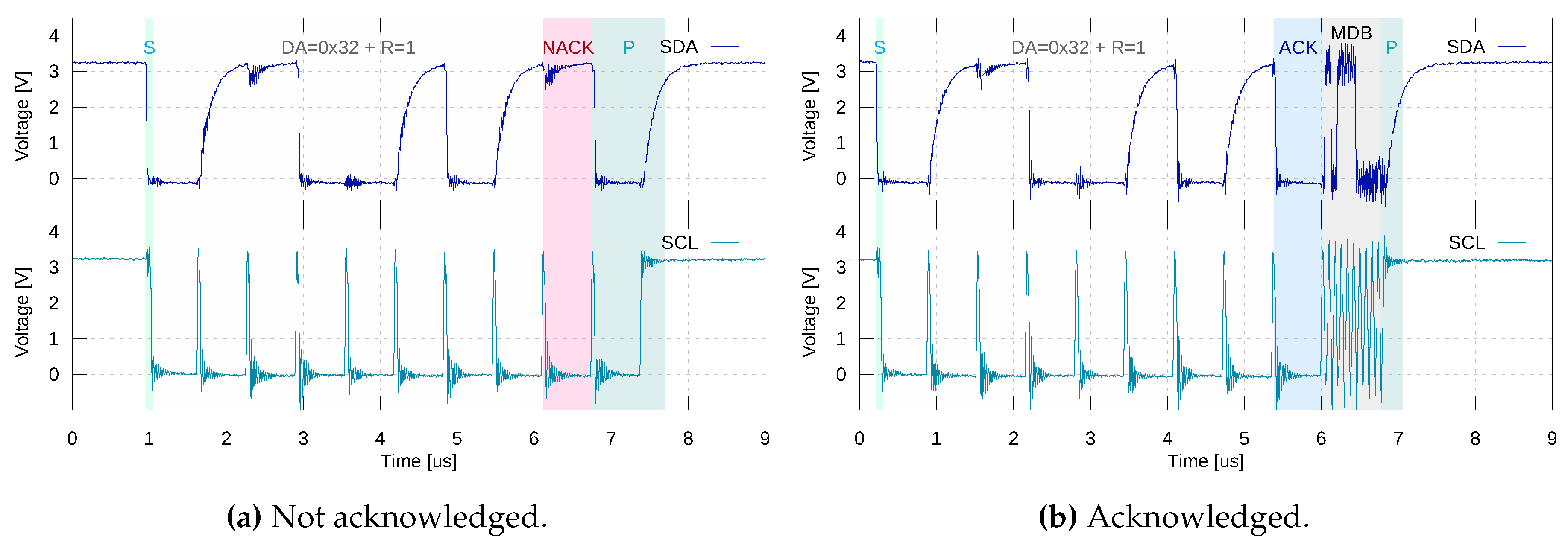

| IBI | In-Band Interrupt. |

| IP | Intellecutal-Property. |

| MDB | Mandatory Data Byte. |

| MIPI | Mobile Industry Processor Interface. |

| PID | Provisioned ID. |

| RnW-bit | Read-or-Write-bit. |

| SCL | Serial Clock. |

| SDA | Serial Data. |

| SDR | Single Data Rate. |

| SoC | System-on-Chip. |

| SPI | Serial-Peripheral Interface. |

| T-bit | Parity-bit. |

References

- I²C Quick Guide. Available online: https://www.analog.com/media/en/technical-documentation/product-selector-card/i2Cb.pdf (accessed on 12 October 2024).

- MIPI I3C Slave. Available online: https://github.com/NXP/i3c-slave-design (accessed on 12 October 2024).

- LPC553x. Available online: https://www.nxp.com/docs/en/data-sheet/LPC553x.pdf (accessed on 12 October 2024).

- STM32H503xx. Available online: https://www.st.com/resource/en/datasheet/stm32h503eb.pdf (accessed on 12 October 2024).

- DRA829 Jacinto Processors. Available online: https://www.ti.com/lit/ds/symlink/dra829v.pdf (accessed on 12 October 2024).

- Mahale, A.; Kariyappa, B.S. Architecture Analysis and Verification of I3C Protocol. ICECA 3rd 2019, Coimbatore, India, 2019, pp. 930-935. [CrossRef]

- Chauhan, S.N.; Andurkar, G.K. Development of UVM Testbench for I3C protocol. ICCCNT 14th 2023, Delhi, India, 2023, pp. 1-4. [CrossRef]

- Neng, P.G.; Xu, N.; Zheng, X.; etc. Design Implementation and Verification of a Flexible I3C Hardware Architecture. ICCCAS 13th 2024, Xiamen, China, 2024, pp. 148-153. [CrossRef]

- Golubic, M.; Kundrata, J.; Baric, A. Verification of the Legacy Compatibility of the MIPI I3C Master. MIPRO 44th 2021, Opatija, Croatia, 2021, pp. 160-165. [CrossRef]

- Krishnan, Y. Krishnan, Y.S; Bhakthavatchalu, R. Design and Implementation of MIPI I3C master controller SubSystems. CONIT 3rd 2023, Hubli, India, 2023, pp. 1-6. [CrossRef]

- MIPI I3C Basic Specification Version 1.1.1. Available online: https://www.mipi.org/specifications/i3c-sensor-specification (accessed on 12 October 2024).

- I3C MDB Values - Implementers Table. Available online: https://www.mipi.org/MIPI_I3C_mandatory_data_byte_values_public (accessed on 29 July 2023).

- Generic device tree bindings for I3C busses. Available online: https://github.com/torvalds/linux/blob/54820b4a6627e87afc0425c8b4ce338d3dbdbb80/Documentation/devicetree/bindings/i3c/i3c.txt (accessed on 27 October 2024).

- I3C - Improved Inter-Integrated Circuit Module, 37.2.8 Hot-Join Mechanism. Available online: https://onlinedocs.microchip.com/oxy/GUID-598A6CC5-BA9B-433D-BAFE-893E2A72A7A3-en-US-14/GUID-25CE5360-2033-447B-BF99-7739E1365410.html?hl=hot-join (accessed on 12 October 2024).

- Coraz7s Reference Manual. Available online: https://digilent.com/reference/programmable-logic/cora-z7/reference-manual (accessed on 12 October 2024).

- Zynq-7000 SoC Data Sheet: Overview. Available online: https://docs.xilinx.com/v/u/en-US/ds190-Zynq-7000-Overview (accessed on 12 October 2024).

- DE10-Nano User Manual (rev. B2/C Hardware). Available online: https://www.terasic.com.tw/cgi-bin/page/archive_download.pl?Language=English&No=1046&FID=f1f656bb5f040121c36f2f93f6b107ff (accessed on 12 October 2024).

- Cyclone V Device Overview. Available online: https://cdrdv2.intel.com/v1/dl/getContent/666729?fileName=cv_51001-683694-666729.pdf (accessed on 12 October 2024).

- ADALM2000 - Advanced Active Learning Module. Available online: https://www.analog.com/en/design-center/evaluation-hardware-and-software/evaluation-boards-kits/ADALM2000.html (accessed on 12 October 2024).

- SPI Engine Offload FPGA Peripheral. Available online: https://analogdevicesinc.github.io/hdl/library/spi_engine/spi_engine_offload.html (accessed on 12 October 2024).

- Interrupts, High-Speed DMA Controller Peripheral. Available online: https://analogdevicesinc.github.io/hdl/library/axi_dmac/index.html (accessed on 12 October 2024).

- Vivado Design Suite 7 Series FPGA and Zynq 7000 SoC Libraries Guide (UG953). Available online: https://docs.xilinx.com/r/en-US/ug953-vivado-7series-libraries/OBUFT (accessed on 12 October 2024).

- Vivado Design Suite Properties Reference Guide (UG912). Available online: https://docs.xilinx.com/r/en-US/ug912-vivado-properties/IOB (accessed on 12 October 2024).

- ALTIOBUF IP Core User Guide. Available online: https://cdrdv2-public.intel.com/666402/ug_altiobuf-6PWM83471-666402.pdf (accessed on 12 October 2024).

- MMCM and PLL Dynamic Reconfiguration (XAPP888). Available online: https://docs.xilinx.com/v/u/en-US/xapp888_7Series_DynamicRecon (accessed on 12 October 2024).

- i3c-master-cdns.c, Linux Kernel. Available online: https://github.com/torvalds/linux/blob/master/drivers/i3c/master/i3c-master-cdns.c (accessed on 29 July 2023).

- SPI-Engine SPI controller driver, Linux Kernel. Available online: https://github.com/torvalds/linux/blob/master/drivers/spi/spi-axi-spi-engine.c (accessed on 26 January 2024).

- Control Interface, I3C Controller. Available online: http://analogdevicesinc.github.io/hdl/library/i3c_controller/interface.html (accessed on 12 October 2024).

- Register map access API, Linux Kernel. Available online: https://github.com/torvalds/linux/blob/master/include/linux/regmap.h (accessed on 12 October 2024).

- SD Card flashing, Kuiper Linux. Available online: https://analogdevicesinc.github.io/documentation/linux/kuiper/sdcard/index.html (accessed on 12 August 2024).

- scp(1) - Linux man page. Available online: https://linux.die.net/man/1/scp (accessed on 12 October 2024).

- Libiio, Analog Devices Inc. Available online: https://analogdevicesinc.github.io/documentation/software/libiio/index.html (accessed on 27 October 2024).

| Name | Range | Description |

| 31:23 | Reserved. | |

| Is CCC | 22:22 | Indicate if it is a CCC transfer (1) or not (0). |

| Bcast. header | 21:21 | Include broadcast header in private transfer (1) or not (0). |

| Sr | 20:20 | Yield a Repeated Start (1) or Stop (0) at the end of the transfer. |

| Buffer length | 19:08 | Unsigned 12-bits payload length, direction depends on rnw value. |

| DA | 07:01 | 7-bit device address (don’t care in broadcast mode). |

| RnW | 00:00 | If should retrieve data from device (1) or not (0). |

| Name | Range | Description |

| Type | 07:07 | Direct (1) or broadcast (0), except SETXTIME and VENDOR. |

| ID | 06:00 | CCC to transfer; identifier matches the payload to be sent in the bus. |

| File | Description |

| adi-i3c-controller.c | I3C Controller driver, methods for the I3C Linux abstractions. |

| dev/dev_core.c | Test device driver, agnostic to the communication protocol. |

| dev/dev_i3c.c | Test device driver, specific to the I3C variant. |

| adi,adi-i3c-controller.yaml | I3C Controller driver documentation. |

| -*-dev-i3c.dts | Devicetree file (template). |

| I3C | I3C | SPI | |

| Resource | Utilization % | Utilization | Utilization |

| LUT | 22.45 | 3234 | 2369 |

| LUTRAM | 14.15 | 849 | 131 |

| FF | 10.92 | 3145 | 3645 |

| BRAM | 4.0 | 2 | 4.5 |

| IO | 10.0 | 10 | 13 |

| BUFG | 3.12 | 1 | 3 |

| MMCM | 0 | 0 | 1 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).