Submitted:

18 November 2024

Posted:

18 November 2024

You are already at the latest version

Abstract

Keywords:

1. Introduction

2. PDF Test Primer

2.1. Delay Defect and Delay Test

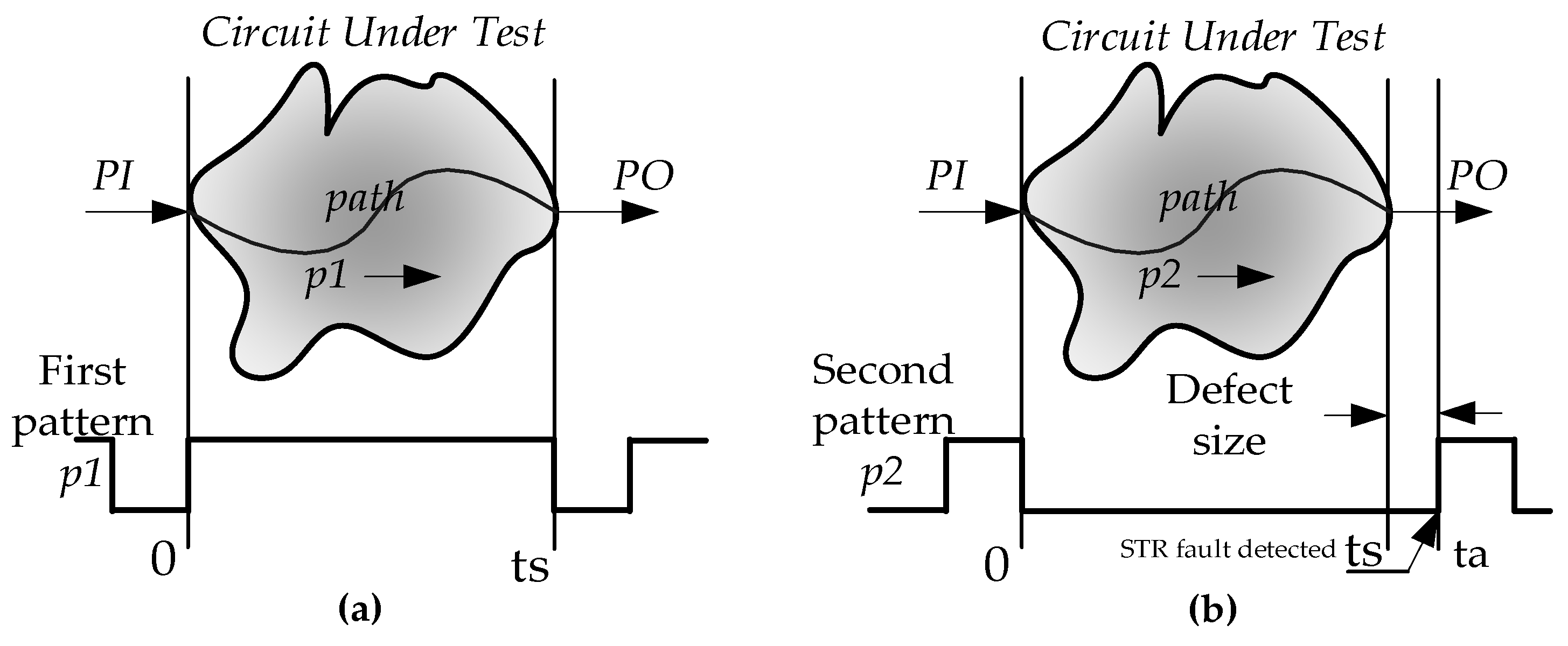

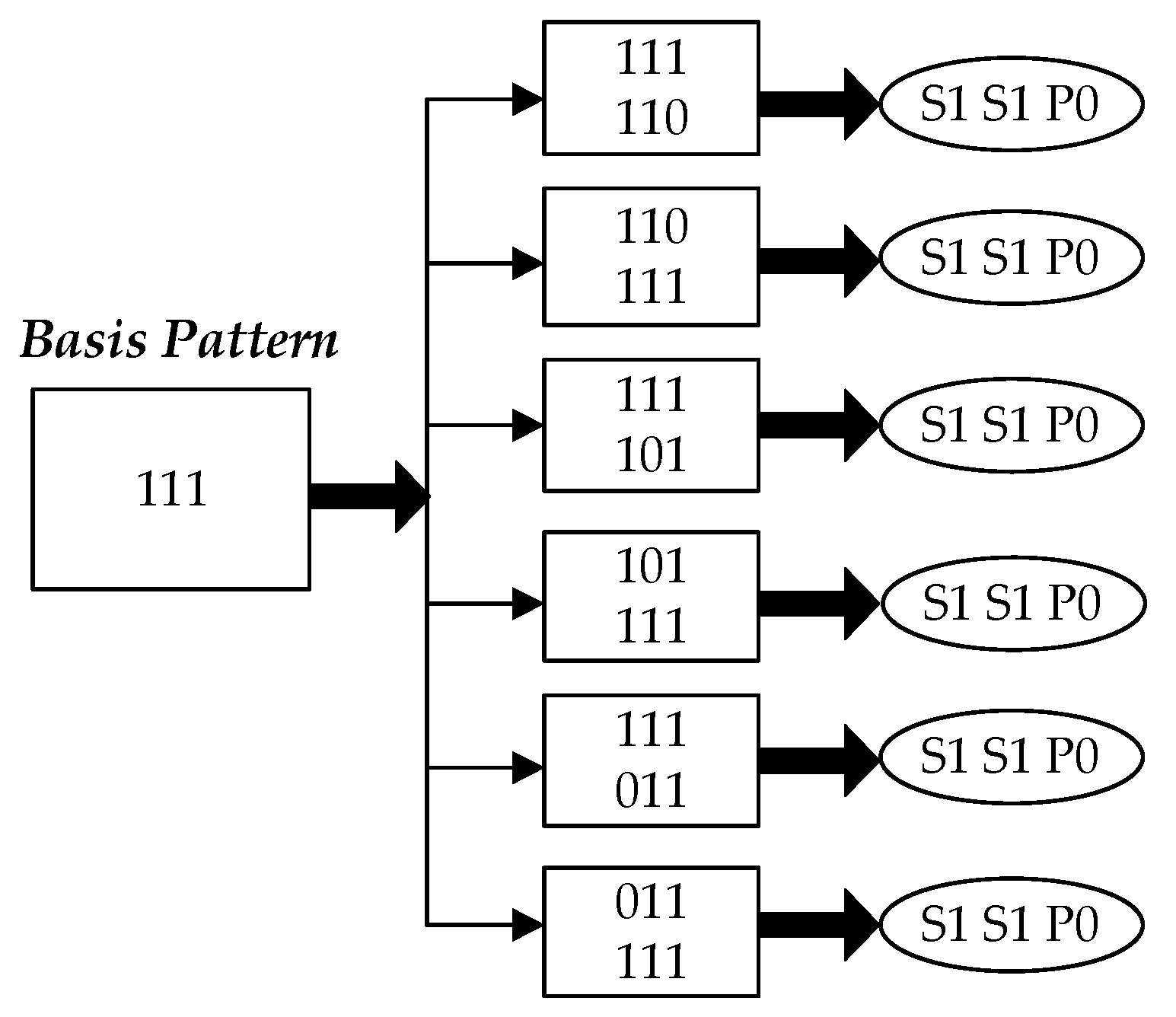

2.2. Fundamentals of PDF Test

- Apply the first pattern (p1), which launches an initial transition and establishes the initial state of the circuit;

- Apply the second pattern (p2) after a time interval, launching the second transition in a path and propagating the signal value toward the output;

- Capture the response at the primary output after a pre-determined time interval. If there is a delay defect, an incorrect response will be captured;

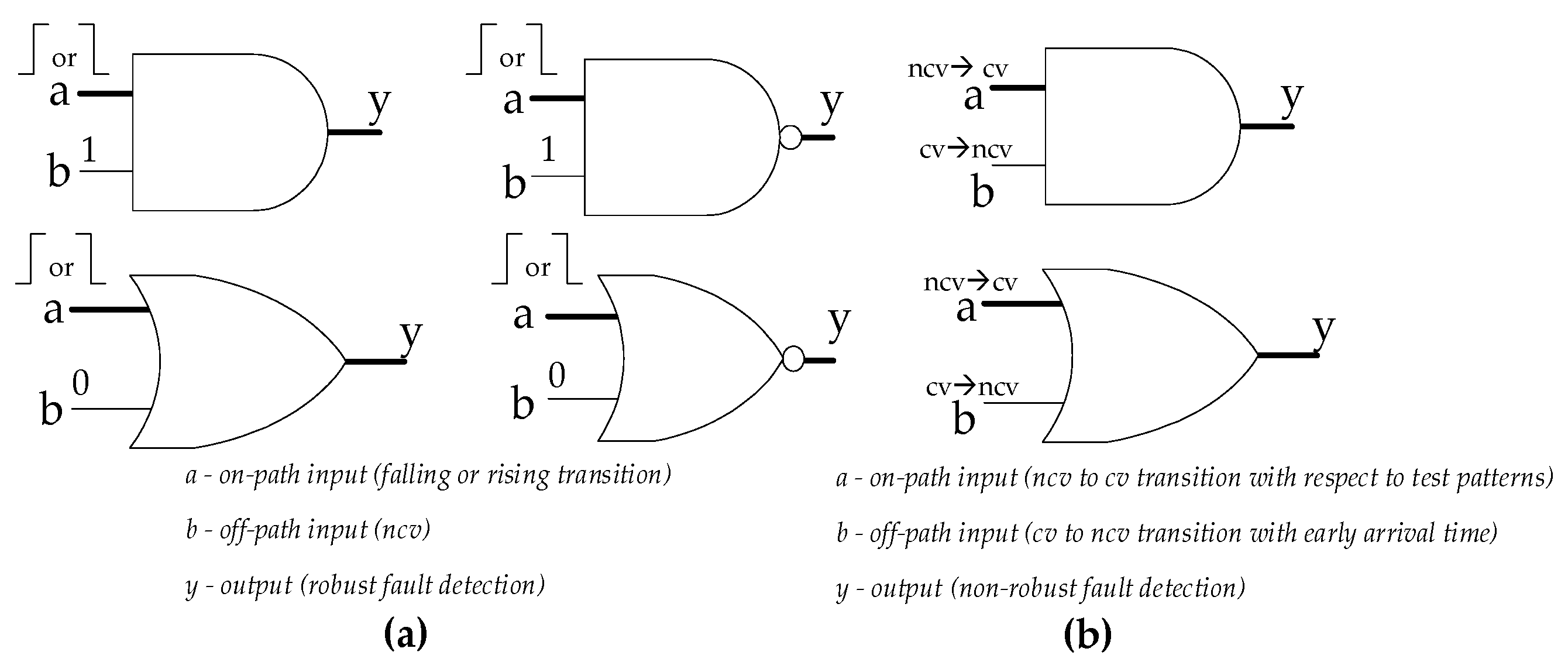

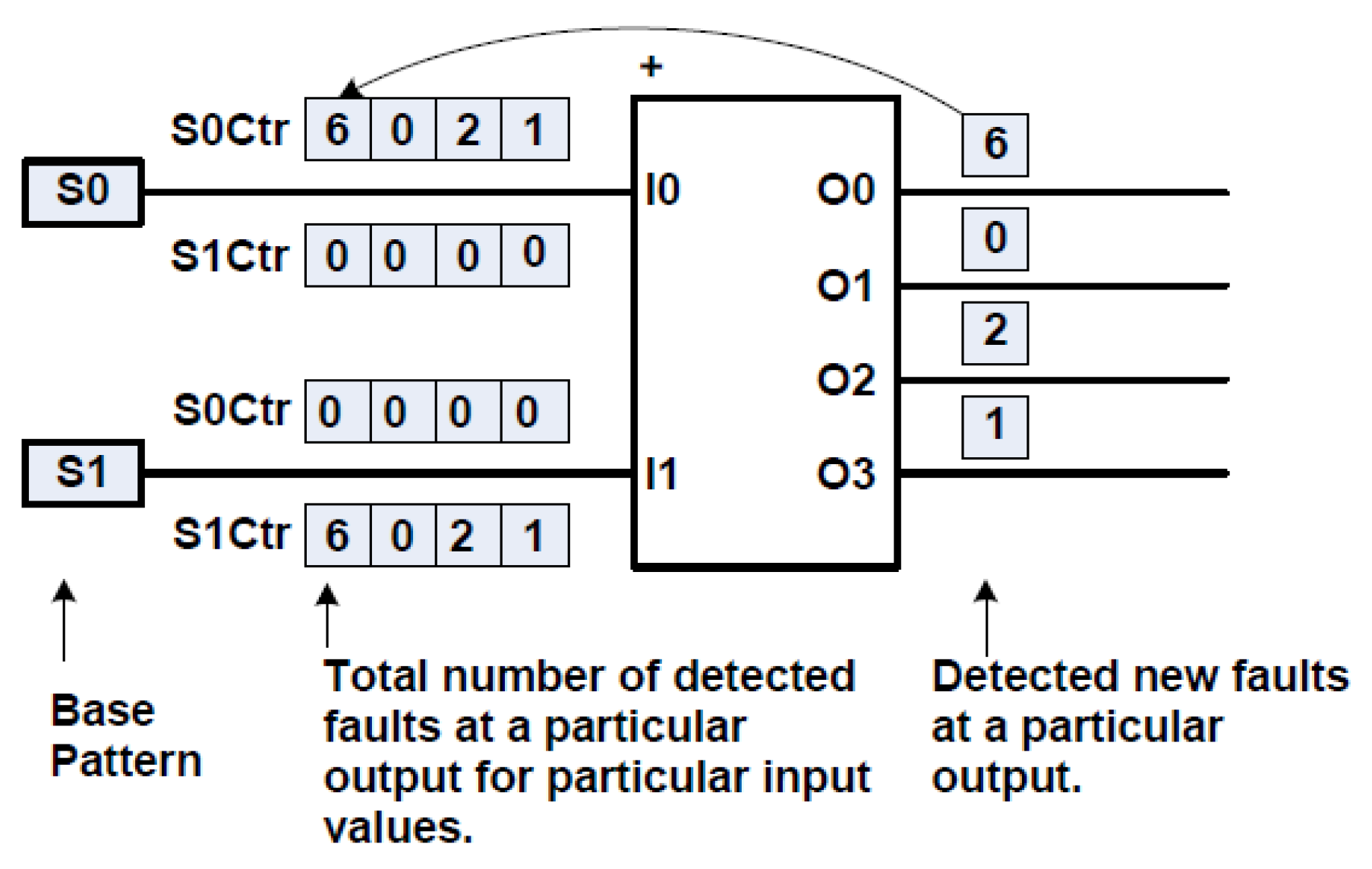

2.3. Faults Detection in a Gate-Level Circuit

3. Path Selection of PDF Testing

3.1. Path Selection: Term Analysis

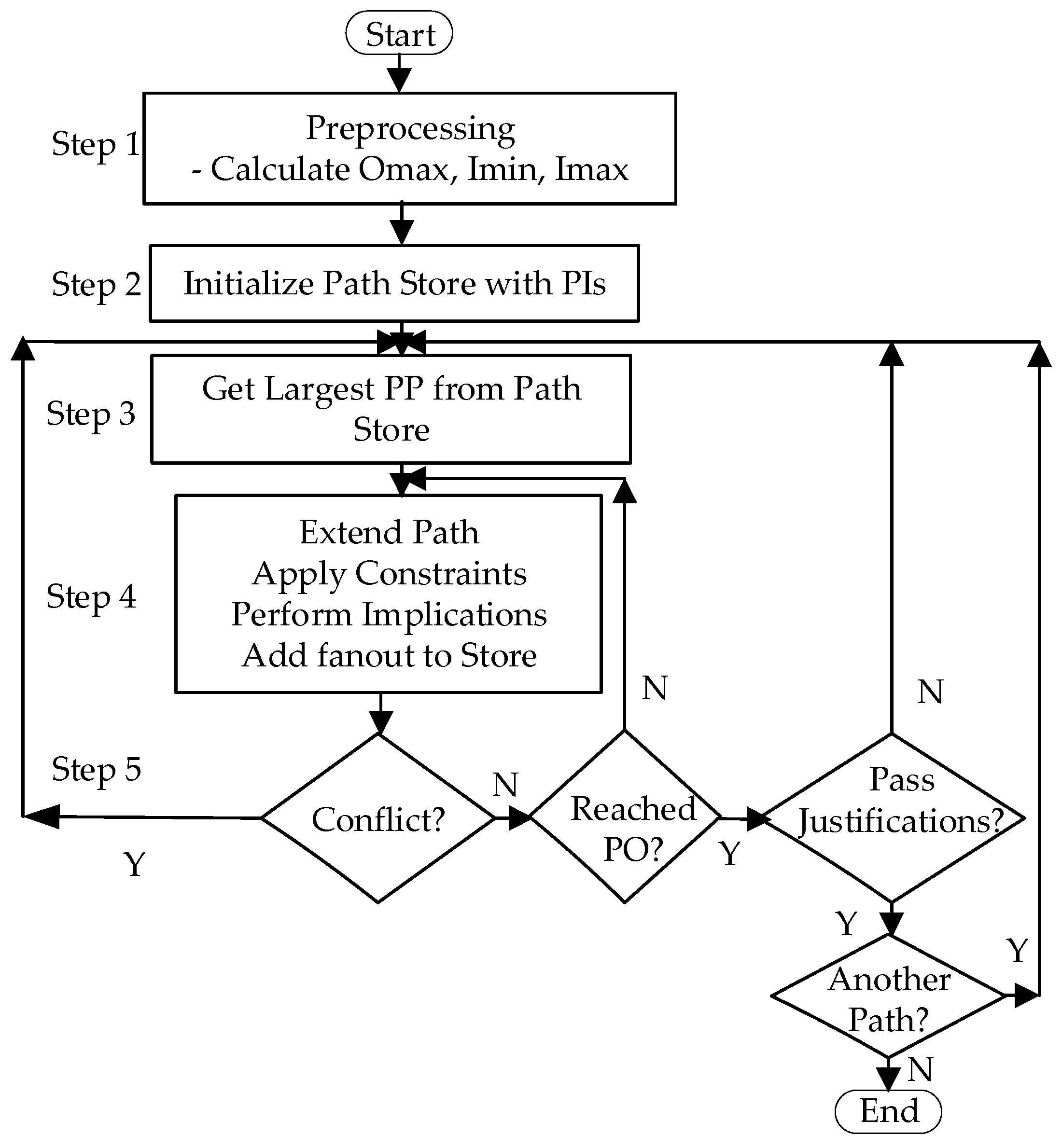

3.2. An Overview of Path Selection in ATPGs

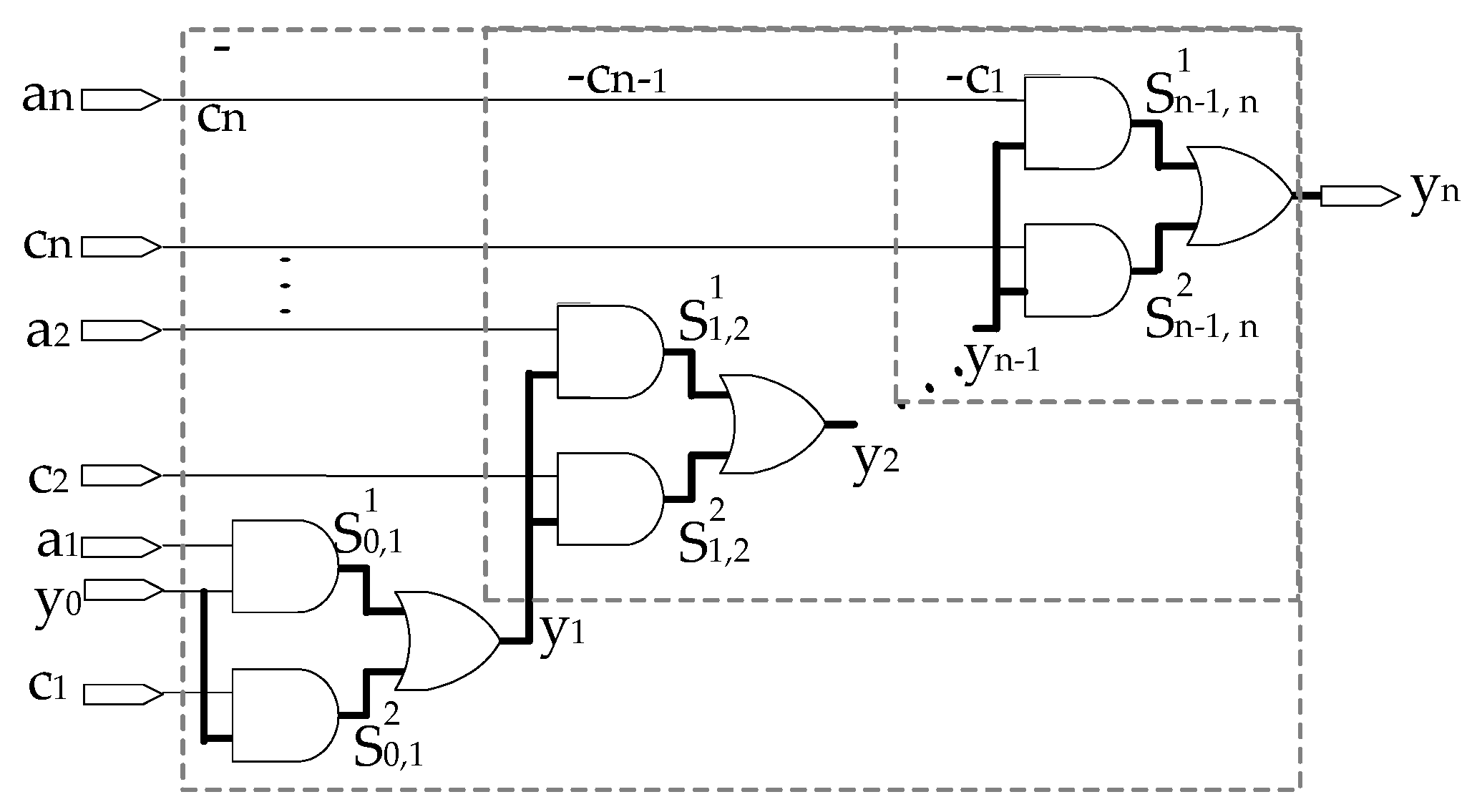

3.3. Paths Selection/Generation Procedure

3.4. Observations

4. Test Generation for PDF Testing – Non-Scan Technique

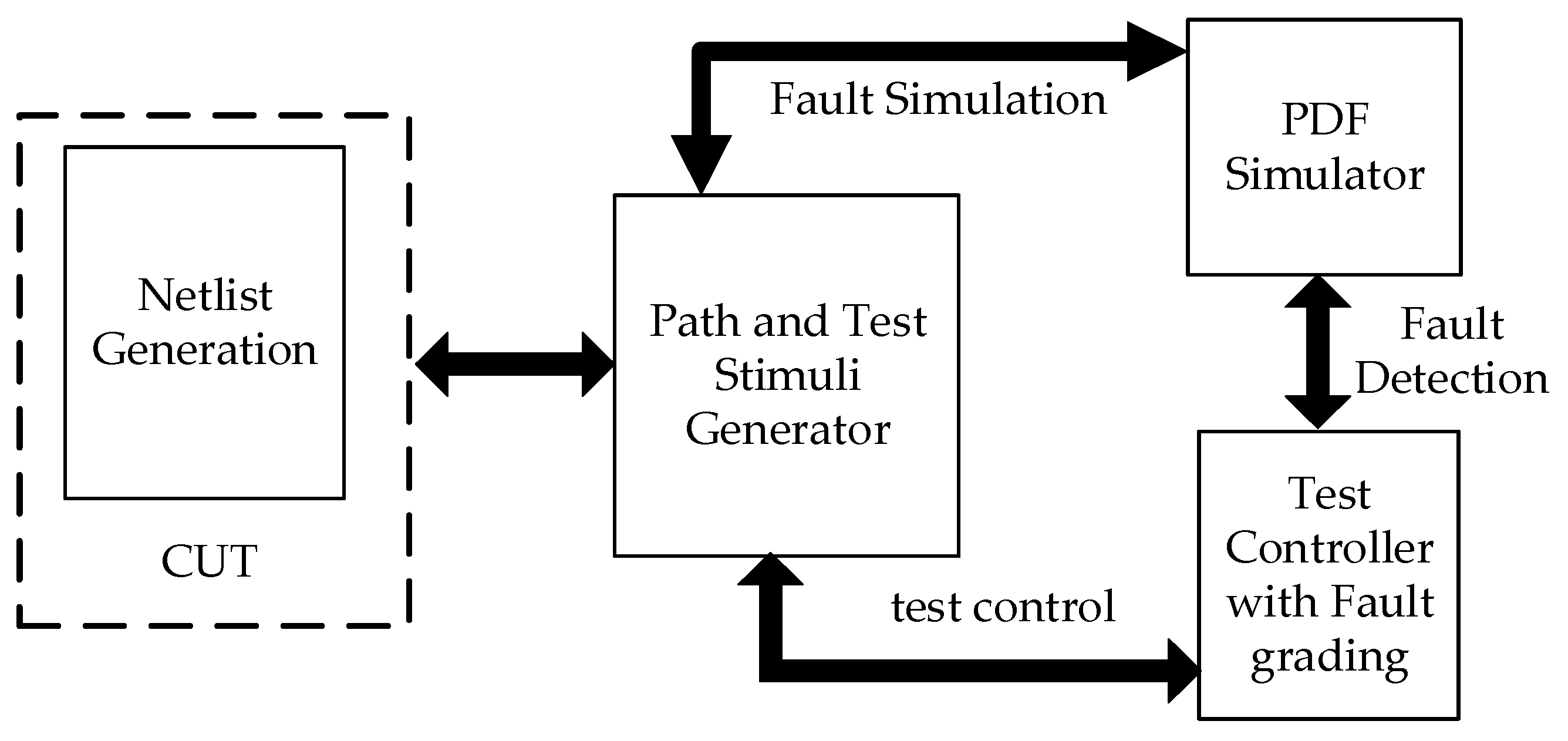

4.1. Non-Scan Based PDF Test Setup

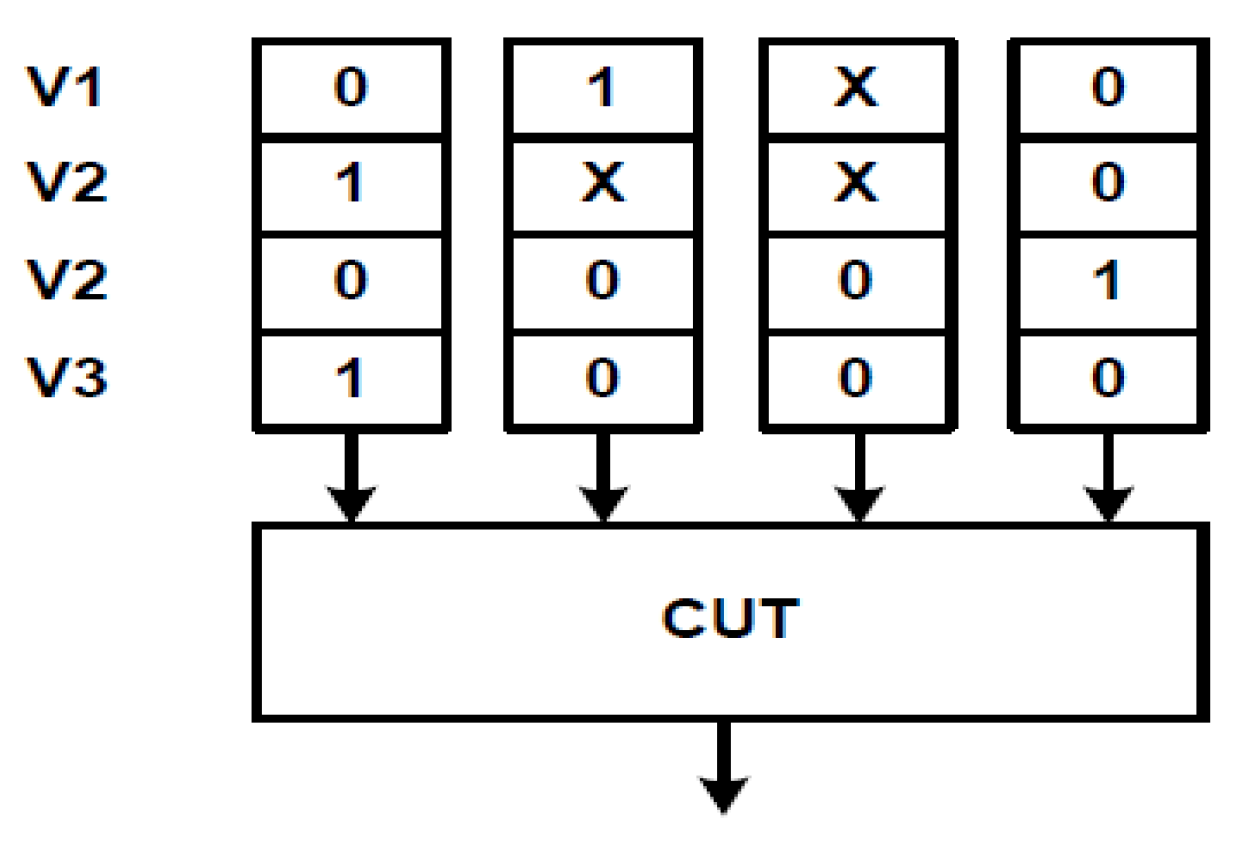

4.2. PDF Test Stimuli Generation Techniques

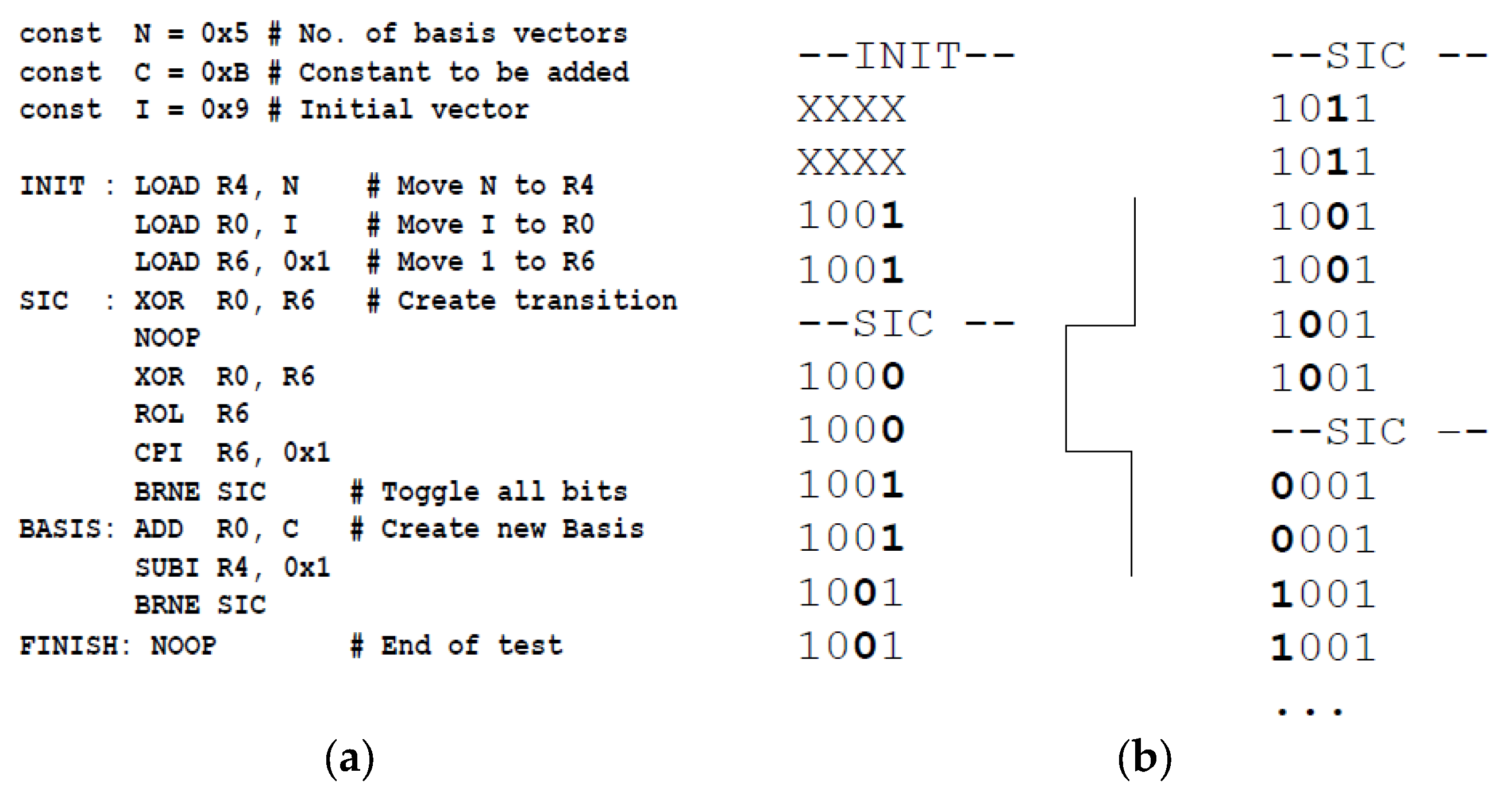

4.2.1. Pseudo Exhaustive Technique

- ACC-FIXED: Optimal accumulator-based generators for single size subspaces: Arithmetic Built-In Self-Test (ABIST) [87] is a term introduced by Rajski and Tyszer. They pointed out the existing components in today’s complex integrated circuits often contain ALUs and memory that can be reused for testing purposes. One efficient way to generate stimuli (measured in the number of clock cycles needed to generate a new vector) is to accumulate a constant as shown in the below equation.

- ACC-RANGE: The best accumulator-based generators for subspaces within a range of sizes. The number of inputs to the partitions often varies, and in such cases a generator made for subspaces with fixed size might be suboptimal. However, It is not possible to synthesize values for C and I for equation 1 in such cases.

4.2.2. Pseudo-Random Technique

- TWISTER - Mersenne twister pseudo random generator: Mersenne Twister [74] is a pseudo-random generator which has a period of 219937 − 1. The generator is fairly complex and is not suitable for use in built-in self-test. However, there are many pitfalls when designing pseudo-random generators, and the Mersenne twister may thus be used as a verification tool in the design phase. If, for instance, an LFSR based generator in a BIST environment performs much poorer than the Mersenne twister, it may be caused by some structural or linear dependencies.

- MAC - Multiply and accumulate based generator: In order to reduce the test application time of large sequential circuits with scan, the scan chain is usually broken down into several scan chains. These scan chains must then be fed by the test generator. LFSRs may, due to structural and linear dependencies, fail to produce some test patterns. Instead one can use a generator based on multiply and accumulate (MAC) operations.

4.3. Weight Technique

4.3.1. Deterministic Test Set Based Weight Computation (DTW)

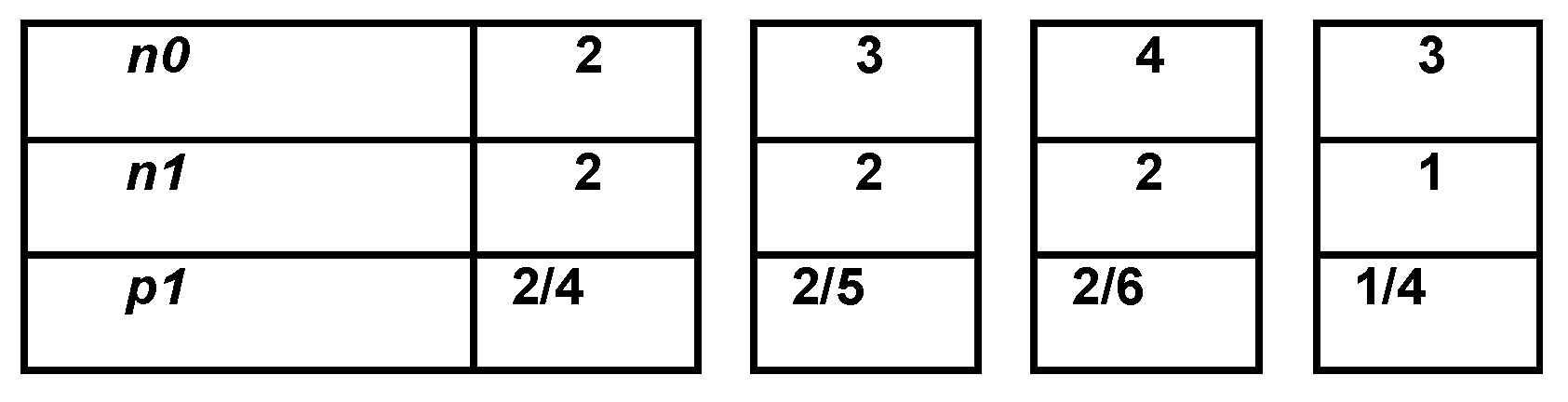

4.3.2. Counting Based Weight Computation (CBW)

4.3.3. Fault Subset Based Weight Computation (FSW)

4.4. Implementation of PDF Test Stimuli Generators

5. PDF Testing in Hardware Security

5.1. HT Detection Principle

5.2. Experimental Results

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Rajski, J.; Tyszer, J.; Kundu, S. Delay Testing: Principles and Recent Advances. IEEE Design & Test 2021, 38, 31–41. [Google Scholar] [CrossRef]

- Zou, X.; Girard, P.; Wen, X.; Marinissen, E.J.; Tang, Z.; Lee, S. Analysis and generation of stimuli for small-delay-defect testing. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 2020, 28, 2724–2735. [Google Scholar] [CrossRef]

- Shi, S.; Miura, Y.; Yasuura, H. A comprehensive delay fault model to improve test quality for deep-submicron circuits. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 2017, 25, 2098–2111. [Google Scholar] [CrossRef]

- Blanton, R.D.; Dworak, J.A. Delay-independent faults: How to effectively target them using stuck-at test patterns. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 2016, 35, 1521–1532. [Google Scholar] [CrossRef]

- Kundu, S.; Al-Hashimi, B.M. Delay testing for small delay defects in nanometer technologies. IEEE Design & Test 2018, 35, 22–31. [Google Scholar] [CrossRef]

- Chatterjee, D.; Mukherjee, N.; Rajski, J. Segment delay fault model for delay testing. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 2016, 35, 603–616. [Google Scholar] [CrossRef]

- De Micheli, G.; Benini, L.; Macii, E. Path delay fault test generation: An overview. IEEE Design & Test 2017, 34, 18–30. [Google Scholar] [CrossRef]

- Hsiao, M.S.; Chakravarty, S. Timing-aware test generation for small-delay defects. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 2020, 28, 2054–2062. [Google Scholar] [CrossRef]

- Qin, H.; Cheng, K.T. Timing-aware path delay fault testing for nanometer ICs. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 2016, 35, 963–976. [Google Scholar] [CrossRef]

- Hu, Z.; Liu, T.; Wen, X.; Chakravarty, S. Process-variation-aware delay fault testing. IEEE Design & Test 2018, 35, 22–30. [Google Scholar] [CrossRef]

- Piuri, V.; Sami, M. Delay fault modeling and simulation in deep-submicron CMOS technologies. IEEE Transactions on Circuits and Systems II: Express Briefs 2020, 67, 422–435. [Google Scholar] [CrossRef]

- Alizadeh, N.; Yaghmaee, S.; Gholami, M. Path delay testing and modeling for advanced node technologies. IEEE Transactions on Circuits and Systems I: Regular Papers 2021, 68, 2224–2235. [Google Scholar] [CrossRef]

- Chen, J.; Cai, W.; Zhou, Y. Path delay test challenges in modern ICs. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 2020, 39, 1595–1605. [Google Scholar] [CrossRef]

- Sharma, S.; Malik, S. Efficient delay test pattern generation using path clustering. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 2021, 40, 1450–1462. [Google Scholar] [CrossRef]

- Piuri, V.; Femia, N.; Yang, C. Path delay test automation and evaluation in sequential circuits. IEEE Transactions on Circuits and Systems II: Express Briefs 2019, 66, 2110–2118. [Google Scholar] [CrossRef]

- Yang, K.; Zhang, M. Delay fault detection for high-speed circuits with pipelining. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 2019, 38, 980–990. [Google Scholar] [CrossRef]

- Lehtonen, T.; Lin, D.; Plosila, J. Path delay fault testing in networks-on-chip. IEEE Transactions on Circuits and Systems II: Express Briefs 2020, 67, 921–929. [Google Scholar] [CrossRef]

- Qin, H.; Ghasempour, A.; Sapatnekar, S.S. Path delay fault diagnosis and test generation. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 2019, 38, 1205–1217. [Google Scholar] [CrossRef]

- Islam, M.; Bayoumi, M.; Yeasin, M. Automated test pattern generation for path delay faults using machine learning. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 2021, 40, 1785–1798. [Google Scholar] [CrossRef]

- Pan, D.; Zhang, X.; Bhunia, S. Path delay fault testing using non-robust delay tests and critical path selection. IEEE Transactions on Circuits and Systems I: Regular Papers 2022, 69, 322–335. [Google Scholar] [CrossRef]

- Alizadeh, N.; Wen, X.; Yoshida, H. A review of delay fault testing for CMOS circuits. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 2018, 26, 377–389. [Google Scholar] [CrossRef]

- Li, Y.; Wei, X.; Xie, C. Sensitization and propagation of robust and non-robust delay faults. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 2020, 39, 2135–2147. [Google Scholar] [CrossRef]

- Le, D.H.; Liu, J.; Radu, S. Detection of non-robust delay faults in high-speed circuits. IEEE Transactions on Circuits and Systems I: Regular Papers 2023, 70, 865–876. [Google Scholar] [CrossRef]

- Zhang, Y.; Wang, J.; Huang, X. Statistical path delay fault testing: A comprehensive review. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 2020, 39, 347–358. [Google Scholar]

- Chen, L.; Zhang, Z.; Kim, S. Recursive learning for delay fault testing in deep sub-micron circuits. Journal of Electronic Testing 2019, 35, 55–69. [Google Scholar]

- Nguyen, V.; Chen, P.; He, X. K-longest path selection techniques for delay fault testing in high-speed circuits. IEEE Transactions on Circuits and Systems I: Regular Papers 2018, 65, 3270–3281. [Google Scholar]

- Gupta, A.; Kumar, A.; Shukla, A. Path delay testing of combinational circuits: Challenges and solutions. VLSI Design 2017, 2017, 1–12. [Google Scholar]

- Wang, Z.; Li, F.; Han, Y. Global longest path testing under process variation. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 2020, 28, 92–103. [Google Scholar]

- Kim, S.; Park, J.; Choi, M. Fault propagation under sensitization constraints for path delay fault testing. IEEE Transactions on Device and Materials Reliability 2021, 21, 405–417. [Google Scholar]

- Liu, G.; Sato, M. Path selection algorithms for industrial circuits: A comparative study. Journal of Testing and Verification 2022, 8, 68–85. [Google Scholar]

- Gaur, A.; Narayanan, A. Recursive path selection for ATPG optimization. ACM Transactions on Design Automation of Electronic Systems 2019, 24, 1–23. [Google Scholar]

- Sharma, K.; Roy, P. Timing analysis for path selection in fault detection. IEEE Transactions on Computers 2016, 65, 2410–2421. [Google Scholar]

- Zhang, H.; Yuan, H. Nonenumerative path delay fault detection using labeling techniques. Microelectronics Reliability 2018, 84, 114–124. [Google Scholar]

- Liu, S.; He, L.; Zhang, T. DYNAMITE: An ATPG tool for handling poorly testable circuits. Journal of Integrated Circuits 2023, 42, 355–370. [Google Scholar]

- Johnson, C.; Zhang, Q.; Li, X. RESIST: A novel recursive path selection technique for efficient ATPG. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 2020, 28, 1121–1134. [Google Scholar]

- Park, S.; Ahn, H. VIPER: Advanced path delay ATPG for industrial applications. Microelectronics Journal 2022, 97, 213–225. [Google Scholar]

- Kim, J.; Choi, Y. KLPG: K-longest path generation algorithm for ATPG tools. IEEE Transactions on Circuits and Systems II: Express Briefs 2019, 66, 759–764. [Google Scholar]

- Singh, R.; Tomar, A. Recursive path delay fault detection using correlation analysis. IEEE Transactions on Circuits and Systems I: Regular Papers 2020, 67, 1322–1334. [Google Scholar]

- Ye, H.; Li, W. Branch-and-bound algorithm for statistical path delay fault testing in VLSI circuits. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 2017, 25, 3432–3445. [Google Scholar]

- Miller, S.; Li, J. Timing analysis for gate-level circuit delay fault testing. Microelectronics Reliability 2019, 93, 192–206. [Google Scholar]

- Narayan, V.; Verma, D. Critical path analysis and delay modeling for high-speed VLSI circuits. IEEE Transactions on Circuits and Systems I: Regular Papers 2020, 67, 2990–3002. [Google Scholar]

- Zhang, Y.; Ma, L. Critical path selection in complex VLSI circuits: A machine learning-based approach. ACM Journal on Emerging Technologies in Computing Systems 2021, 17, 1–16. [Google Scholar] [CrossRef]

- Hu, Z.; Zhou, X. A timing-aware path selection strategy for delay fault testing in nanometer technologies. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 2015, 23, 726–735. [Google Scholar] [CrossRef]

- Liu, C.; Zhang, P.; Xie, Y. Dynamic path selection for efficient delay testing in advanced nodes. IEEE Transactions on Device and Materials Reliability 2019, 19, 467–475. [Google Scholar] [CrossRef]

- Wu, Z.; Zhu, L.; Wang, D. Statistical timing analysis for path selection in delay testing of nanometer circuits. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 2018, 26, 897–910. [Google Scholar] [CrossRef]

- Huang, T.; Li, X.; Ma, H. A novel algorithm for path selection in delay fault testing based on timing correlation. Journal of Electronic Testing 2019, 35, 189–202. [Google Scholar] [CrossRef]

- Kulkarni, K.; Patel, P. Recursive fault propagation techniques for delay test in multi-clock domain circuits. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 2019, 38, 1699–1712. [Google Scholar] [CrossRef]

- Tang, H.; Zhang, X.; Zhang, M. Adaptive path selection for delay fault testing with timing uncertainty. IEEE Transactions on Circuits and Systems I: Regular Papers 2020, 67, 1379–1389. [Google Scholar] [CrossRef]

- Yang, L.; Jiang, W.; Wang, D. Delay fault testing of critical paths using ATPG with timing constraints. IEEE Transactions on Circuits and Systems II: Express Briefs 2018, 65, 1721–1725. [Google Scholar] [CrossRef]

- Sun, W.; Chen, H.; Chang, C.H. Fast and efficient ATPG for path delay faults in digital circuits. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 2018, 37, 764–775. [Google Scholar] [CrossRef]

- Chakraborty, A.; Bhunia, S. Power-aware path delay fault testing using adaptive test pattern generation. IEEE Transactions on Circuits and Systems I: Regular Papers 2019, 66, 2703–2712. [Google Scholar] [CrossRef]

- Rahman, M.; Islam, S. ATPG for robust path delay fault testing using enhanced sensitization criteria. Journal of Electronic Testing 2020, 36, 311–325. [Google Scholar] [CrossRef]

- Tang, K.; Liu, J. Recursive learning-based ATPG for testing of critical paths in digital circuits. IEEE Transactions on Circuits and Systems I: Regular Papers 2019, 66, 3946–3954. [Google Scholar] [CrossRef]

- Lee, J.; Song, H. Dynamic path selection for delay fault testing using statistical correlation analysis. Journal of Electronic Testing 2020, 36, 159–170. [Google Scholar] [CrossRef]

- Wei, Z.; Zhang, X. Efficient recursive path delay fault testing in digital circuits using machine learning techniques. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 2021, 29, 921–931. [Google Scholar] [CrossRef]

- Sun, H.; Zhao, X. A novel recursive ATPG technique for robust path delay testing in complex digital circuits. IEEE Transactions on Circuits and Systems II: Express Briefs 2022, 69, 3456–3460. [Google Scholar] [CrossRef]

- Sekar, S. Logic Encryption Methods for Hardware Security. PhD Dissertation, University of Cincinnati, 2017. [Google Scholar]

- Bell, D.J.; Walker, D.M. Timing Analysis of Logic-Level Digital Circuits Using Mixed-Mode Delay Fault Simulation. Journal of Electronic Testing: Theory and Applications 2018, 34, 560–577. [Google Scholar]

- Majhi, A.K.; Agrawal, V.D. Algorithms for Test Generation and Fault Simulation of Path Delay Faults. IEEE Design & Test of Computers 2017, 34, 58–67. [Google Scholar]

- Krishnamachary, A. Timing Analysis and Delay-Fault Test Generation Using Recursive Path Functions. Proceedings of International Conference on Computer Aided Design 2020, 18, 152–165. [Google Scholar]

- Xie, Q.; Zhang, Y. Efficient Test Generation for Path Delay Faults in Sequential Circuits. Journal of Electronic Testing 2019, 35, 495–508. [Google Scholar]

- Rajski, J.; Tyszer, J.; Mukherjee, S. Longest path analysis in digital circuits for delay fault testing. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 2015, 34, 463–475. [Google Scholar] [CrossRef]

- Li, X.; Zhao, M.; Li, W. Advanced path selection techniques for delay fault testing in high-performance circuits. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 2017, 25, 2512–2523. [Google Scholar] [CrossRef]

- Zhang, Y.; Wu, W.; Sun, G. A novel ATPG framework for path delay fault testing based on modified longest path selection. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 2019, 38, 688–698. [Google Scholar] [CrossRef]

- Xu, H.; Lin, Y. Built-in self-test methodology for path delay fault testing using recursive ATPG techniques. IEEE Transactions on Circuits and Systems I: Regular Papers 2020, 67, 1564–1574. [Google Scholar] [CrossRef]

- Peng, J.; He, Y. Efficient built-in self-test schemes for delay fault detection in digital circuits. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 2019, 27, 2599–2610. [Google Scholar] [CrossRef]

- Tehranipoor, M.; Koushanfar, F.; Chakraborty, R. Hardware Trojan detection: Methods and challenges. IEEE Design & Test 2017, 34, 58–69. [Google Scholar] [CrossRef]

- Bhunia, S.; Hsiao, M.S. A survey on hardware Trojan detection techniques. IEEE Design & Test 2017, 34, 10–25. [Google Scholar] [CrossRef]

- Xu, R.; Wang, H.; Zhang, X. Trustworthy design and detection of hardware Trojans in digital circuits: A comprehensive survey. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 2021, 40, 1647–1660. [Google Scholar] [CrossRef]

- Hasan, M.H.; Mishra, P. Trojan-aware path delay fault testing in integrated circuits. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 2019, 27, 1616–1629. [Google Scholar] [CrossRef]

- Bhunia, S.; Hsiao, M.; Forte, D. Hardware Trojan detection by statistical path delay analysis. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 2020, 39, 2777–2790. [Google Scholar] [CrossRef]

- Jin, Y.; Makris, Y. Hardware Trojan detection using delay-based statistical techniques. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 2020, 28, 2498–2509. [Google Scholar] [CrossRef]

- Xu, M.; Lee, D.; Yang, H. A three-level approach for efficient path delay fault testing. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 2019, 38, 1376–1388. [Google Scholar] [CrossRef]

- Jiang, W.; Wei, Y.; Huang, J. Efficient test pattern generation for path delay faults using arithmetic and Mersenne Twister-based methods. IEEE Access 2020, 8, 105493–105504. [Google Scholar] [CrossRef]

- Liu, J.; Zhang, X. Test pattern generation for delay fault detection using pseudo-random and weighted random methods. IEEE Transactions on Semiconductor Manufacturing 2022, 35, 145–154. [Google Scholar] [CrossRef]

- Ghosh, A.; Ganguly, S. A skip-list based approach for efficient path delay fault detection. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 2018, 26, 1308–1317. [Google Scholar] [CrossRef]

- Yang, H.; Xu, M.; Huang, J. Open-source skip-list implementation for fault detection in delay testing. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 2019, 38, 1681–1692. [Google Scholar] [CrossRef]

- Bell, J.A. Timing Analysis of Logic-Level Digital Circuits Using Uncertainty Intervals. MS Thesis, Department of Computer Science, Texas A&M University, 1996. [Google Scholar]

- Qiu, W.; Walker, D.M.H. An Efficient Algorithm for Finding the K Longest Testable Paths Through Each Gate in a Combinational Circuit. In Proceedings of the IEEE International Test Conference; 2003; pp. 592–601. [Google Scholar]

- Qiu, W.; Wang, J.; Walker, D.M.H.; Reddy, D.; Lu, X.; Li, Z.; Shi, W.; Balachandran, H. K Longest Paths Per Gate (KLPG) Test Generation for Scan-Based Sequential Circuits. In Proceedings of the IEEE International Test Conference; 2004; pp. 223–231. [Google Scholar]

- Sharma, M.; Patel, J. Finding a small set of longest testable paths that cover every gate. In Proceedings of the International Test Conference; 2002; pp. 974–982. [Google Scholar]

- Gjermundnes, Ø. Exploiting Arithmetic Built-In Self-Test Techniques for Path Delay Fault Testing. PhD Thesis, NTNU, Norway, 2006. [Google Scholar]

- Manikandan, P.; Aas, E.J.; Larsen, B.B. An enhanced Path Delay Fault Simulator for Combinational Circuits. Proceedings of IEEE International Conference on DSD-2011; 2011; pp. 375–381. [Google Scholar]

- Manikandan, P.; Aas, E.J.; Larsen, B.B. Experiments with ABIST Test Methodology Applied to Path Delay Fault Testing. In Proceedings of the IEEE International Conference on EWDTS-2010; 2010; pp. 110–115. [Google Scholar]

- Pomeranz, I.; Reddy, S.M.; Uppaluri, P. NEST: A Nonenumerative Test Generation Method for Path Delay Faults in Combinational Circuits. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 1995, 14, 1505–1515. [Google Scholar] [CrossRef]

- Kagaris, D.; Tragoudas, S. On the nonenumerative path delay fault simulation problem. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 2002, 21, 1095–1101. [Google Scholar] [CrossRef]

- Rajski, J.; Tyszer, J. Arithmetic Built-In Self-Test for Embedded Systems; Prentice Hall: Upper Saddle River, NJ, USA, 1998. [Google Scholar]

- Smith, G.L. Model for Delay Faults Based Upon Paths. In Proceedings of the IEEE International Test Conference; 1985; pp. 342–349. [Google Scholar]

| S0 | S1 | P0 | P1 |

|---|---|---|---|

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| Instruction | Description |

|---|---|

| LOAD Rd, k LOADI Rd, k |

Set the content of register Rd to [data stored in memory address k - immediate] |

| MOV Rd, Rr | Move content of Rr to Rd |

| ADD Rd, Rr ADDI Rd, k |

Add the content of [reg. Rr — immediate] to Rd. Store the result in Rd |

| ADDC Rd, Rr ADDCI Rd, k |

Add the content of [reg. Rr—immediate] with carry to Rd. Store the result in Rd |

| AND Rd, Rr ANDI Rd, k |

Bitwise AND operation of [reg. Rr — immediate] and Rd. Result is stored in Rd |

| OR Rd, Rr ORI Rd, k |

Bitwise OR operation of [reg. Rr—immediate] and Rd. Result is stored in Rd |

| XOR Rd, Rr | Bitwise XOR operation of Rr and Rd. Result is stored in Rd |

| NOT Rd | Invert the bits in Rd |

| ROL Rd | Rotate left the content of Rd |

| BRNE k | Set program counter to k if the equal flag is not set |

| CPI Rd, k | Compare register with immediate |

| Benchmark | Circuit type | Inputs/Outputs | Gates/Levels | Considered paths / Upper bound | Case 1: PDF Coverage (Before HT insertion) | Case 2: PDF Coverage (After HT insertion) |

|---|---|---|---|---|---|---|

| c432 | Channel Interrupt Controller | 36/7 | 203/18 | 10K/132K | 100% | 84.2% |

| c880 | 8-bit ALU | 60/26 | 469/25 | 10K/16652 | 100% | 89.1% |

| c1355 | 32-bit SEC Circuit | 41/32 | 619/25 | 10K/1110K | 100% | 82.3% |

| c1908 | 16-bit SEC Circuit | 33/25 | 938/41 | 10K/355K | 98.8% | 78.1% |

| c2670 | 12-bit ALU and Controller | 233/140 | 1566/33 | 10K/1306K | 89.5% | 72.2% |

| c3540 | 8-bit ALU | 50/22 | 1741/48 | 10K/12330K | 97.8% | 75.4% |

| c5315 | 9-bit ALU | 178/123 | 2608/50 | 10K/353K | 98.7% | 78.3% |

| c7552 | 32-bit adder/comparator | 207/108 | 3827/44 | 10K/282K | 98.3% | 81.1% |

| Benchmark | PDF coverage variation in % | ||

|---|---|---|---|

| Statistical Simulation trials | |||

| VMax | VMin | VAve | |

| c432 | 18.6% | 15.1% | 17.5% |

| c880 | 14.3% | 11.9% | 12.7% |

| c1355 | 19.3% | 17.4% | 19% |

| c1908 | 20.1% | 19.2% | 19.6% |

| c2670 | 18.4% | 14.3% | 17.8% |

| c3540 | 23.1% | 18.6% | 19.5% |

| c5315 | 21.6% | 17.2% | 18.9% |

| c7552 | 17.8% | 16.1% | 16.8% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).