1. Introduction

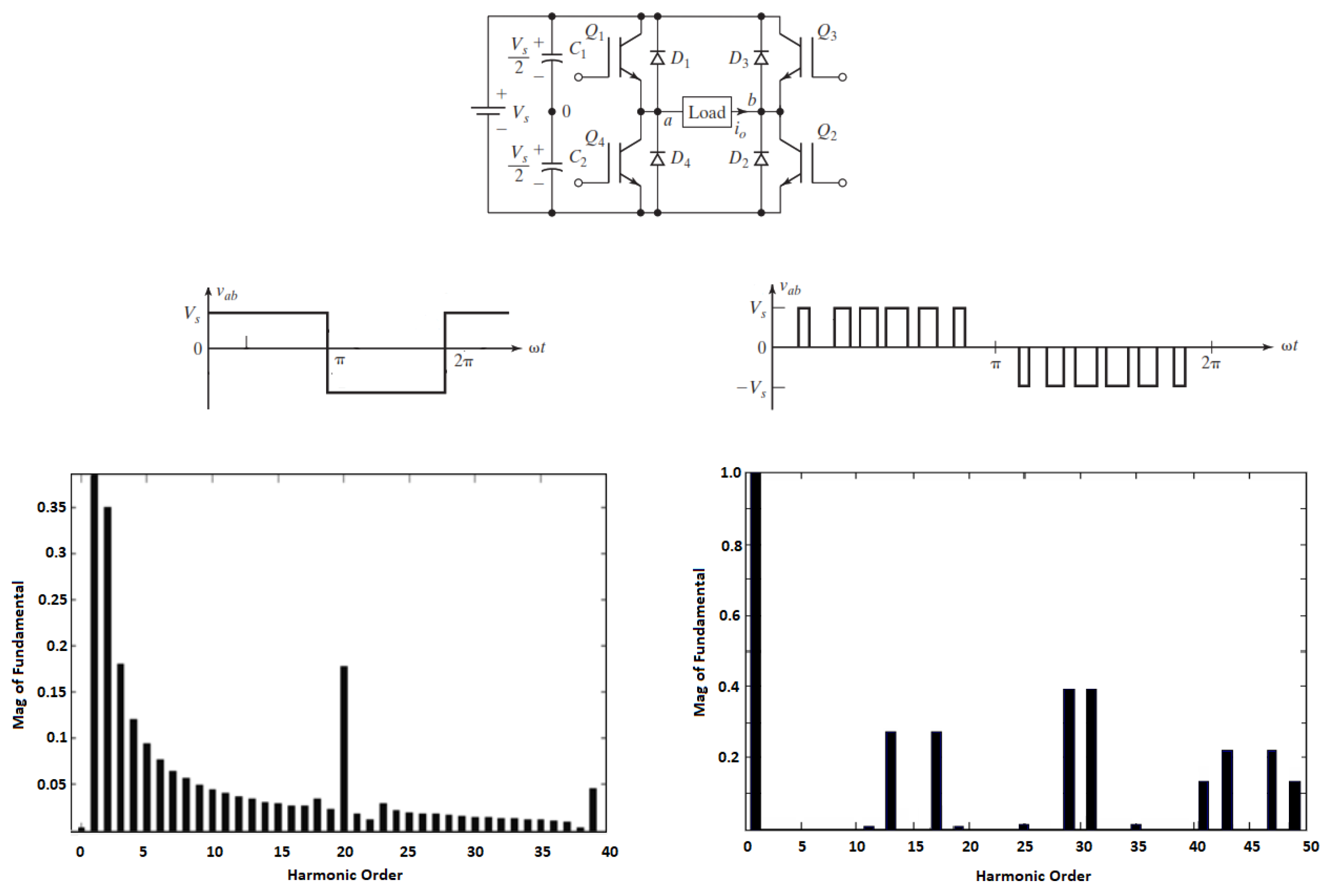

At present, electrical energy from renewable energy sources is one of the main research topics, especially the use of solar energy captured by photovoltaic panels. To integrated this systems into the electrical power system, it is necessary to use an inverter, power converters that allow obtaining an AC voltage from a DC voltage; the simplest and most commonly used topology is known as PWM inverter, it produces a square voltage waveform where the fundamental sinusoidal component predominates. The disadvantage of this topology is the harmonic content with a THD of 48.43%. Modulation strategies improve the pwm inverter output such as sinusoidal pulse width modulation (SPWM), which reduces the harmonic content with a THD of 41% and allows voltage amplitude control, however, it increases switching losses, limiting the switching frequency [

1]. THD is an importan factor in High power applications, harmonics can generate undesired operation effects, electromagnetic interference, low efficiency, In

Figure 1 the output waveform and frequency spectrum of a PWM and SPWM inverter are showed, the difference in the harmonic content can be appreciated.

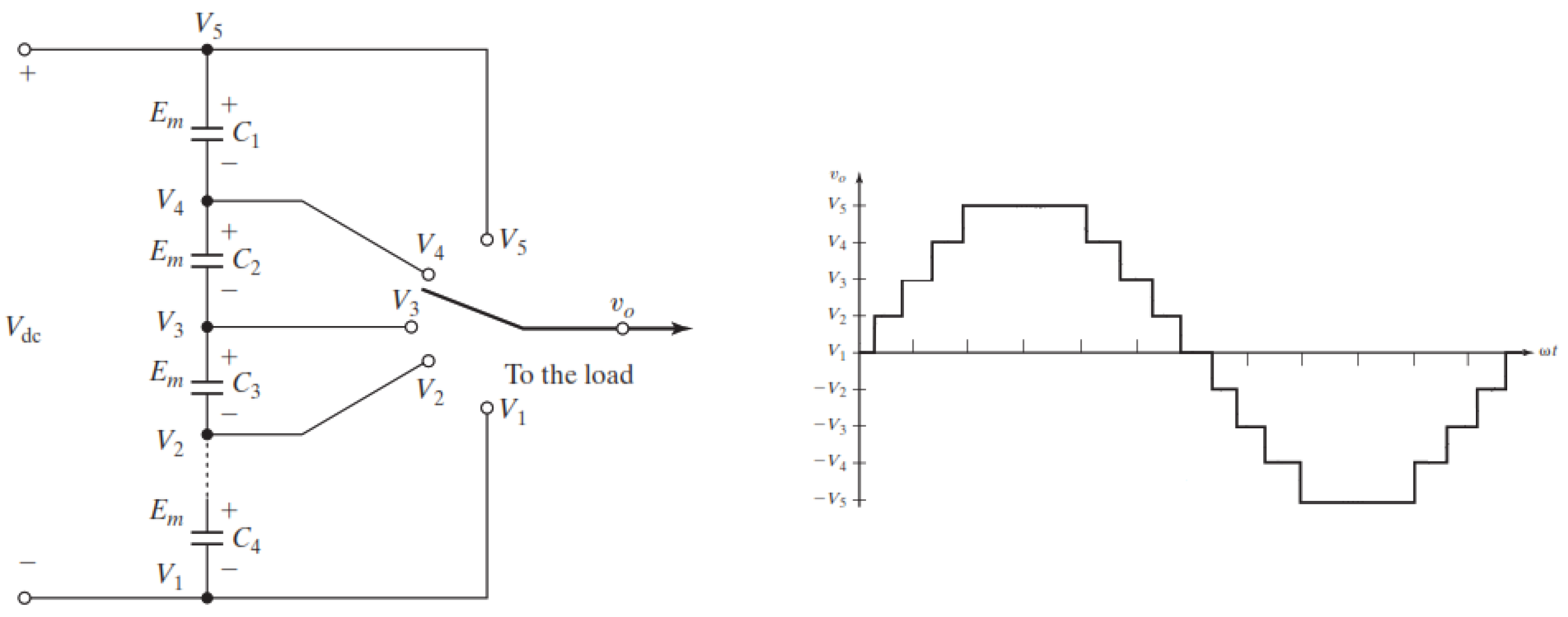

Multilevel inverter topologies can deal with these drawbacks, they have a topology in which a stepped voltage waveform is obtained and a low harmonic content can be reached because the waveform is more similar to a sinusoidal. The THD can be controlled with the quantity of levels, it can be said that more levels less THD. [

2]

The stepped voltage waveform is obtained with energy bank implemented with series connected capacitors to provide nodes where controlled switches are connected. Each capacitor has a voltage according to Equation (

1), where m represents the number of levels or accesible nodes form tue energy bank .

A conceptual topology is showed in

Figure 2, the stepped voltage waveform is generated from each energy bank node

to a reference node

, if

the positive half period output waveform is generated when switching from

to

and return to

with appropiate control signals. The negative half period is generated in opposite way when

and switching starts in

[

3]. In

Figure 2 the output voltage waveform is showed.

The harmonic distorsion can be reduced with a high number of voltage level in the waveform,

Figure 3 shows the harmonic spectre in a nine level inverter. Compared to the harmonic spectre in

Figure 1, a considerable reduction in the number of harmonics and its amplitude can be noted, without the need to use a modulation technique.

Multilevel inverter topologies seek to use low breakdown voltage power switches in high voltage applications, commonly used topologies are clamping diode, floating capacitor and cascaded inverters, the first two topologies require a large number of power switches, in addition to other electronic components whose number will increase depending on the number of levels in its output, additionally they introduce static and dynamic unbalances in the blocking voltages of each device, so external damping networks must be added to equalize the blocking voltages. Single-phase cascaded inverters present a similar disadvantage in terms of the number of components, however, they present an easier implement design, but the control of each inverter must be adjusted each time that change the number of output voltage levels. In general terms, a multilevel AC waveform increases the amount of static and dynamic losses in power converters, so it is common implement inverters of 15 levels as maximum. In

Table 1 the electric components number is showed, it can be noted that the higher the number of levels, the more complex the circuit becomes in the number of devices as well as the control [

5].

In [

7] a clamping diode configuration is used, where THD values of 28.58% are obtained using a 5-level inverter. Tests are performed where the THD decreases to a value of 2.53% when using a 15-level inverter implemented with 28 switches per phase. [

8] implements a basic unit of a switched capacitor topology utilizing a cascaded H-bridge to generate 13 and 31 level output voltage with a lower number of components, a THD 0f 2.63% was achieved. [

9] shows a cascaded module configuration where the number of switches will be

for

levels at the output, the THD obtained for an 11-level configuration (12 static switches in the bridge) is 8.61%. These works evidence the use of a large number of semiconductor elements, moreover, in three-phase systems the number of semiconductors triples and requires the use of complex controllers running extensive algorithms.

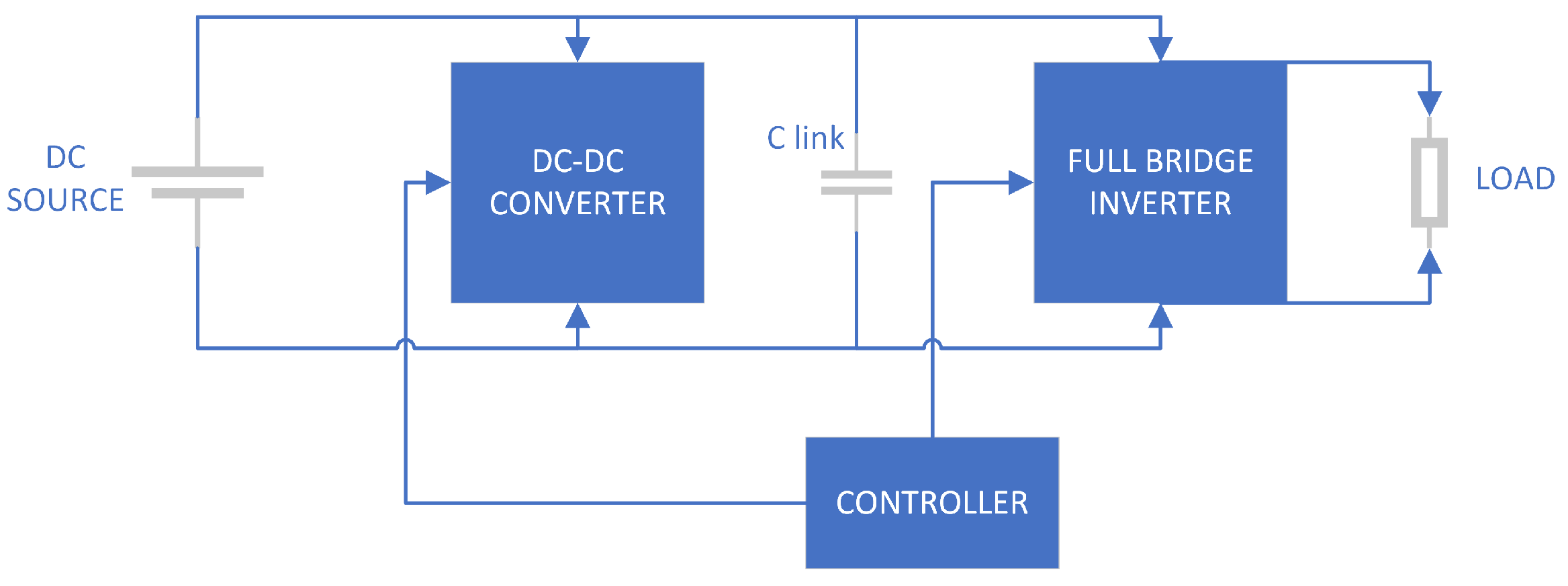

In [

10,

11,

12] a topology called inifinite level inverter (ILI) is proposed, where a DC-DC converter is cascaded with a single-phase full-bridge inverter. This topology is mentioned in [

13] as variable inverter with DC link, a stepped wave can be obtained by controlling the output voltage of the DC-DC converter while the inverter switches its switches in conduction at 180° A topology scheme is showed in

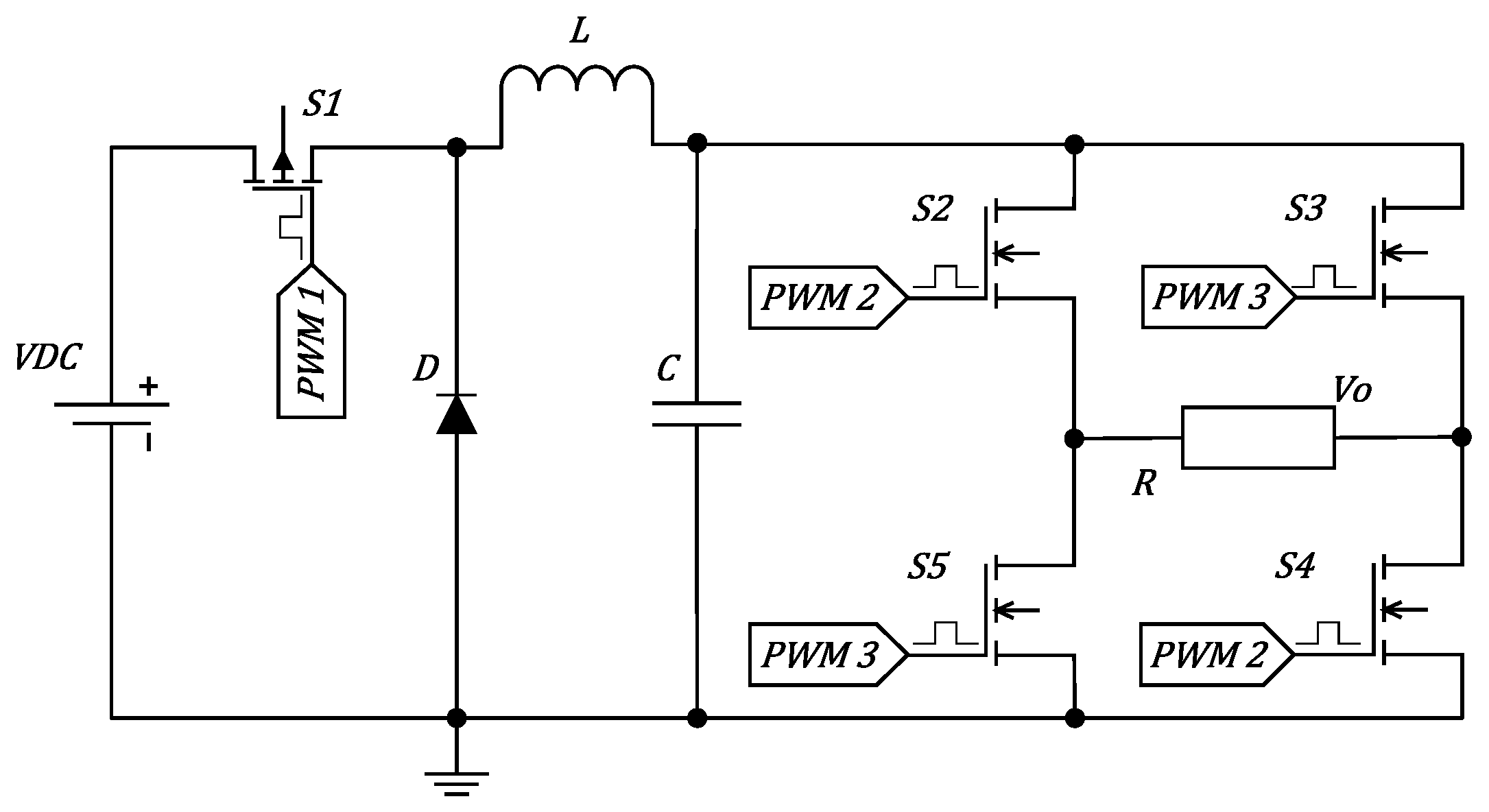

Figure 4. Through this type of operation, an infinite-level inverter can be obtained where several levels can be reached with fewer electronic devices, reducing losses, costs, size, complexity and increasing efficiency.

In [

14,

15] a buck-type step-down DC-DC converter with variable duty ratio in steps according to a sampled sine wave is used as a DC link, generating at the inverter output a step wave with a THD of 2.36% at a switching frequency of 10 KHz. Similar results are obtained in [

16] with a THD of 1.2% and 98% efficiency in an evaluation with resistive load. In [

17,

18] a buck-boost converter is used to make more efficient use of the DC voltage at the input of the converter. In these works there is no voltage feedback so the levels depend exclusively on the reference signal generated, and can be affected by disturbances, introducing distortion in the output voltage waveform. In the case of [

18] a THD that varies from 2% to 8.20% depending on the load associated with the circuit at a switching frequency of 10KHz is obtained. [

19] presents a novel topology to develop a three phase infinite level inverter, it use less semiconductors than traditional inverter topologies and in combination with third harmonic injectio PWM technique can achieve a THD of 0.39%.

ILI has been investigated in applications such as motor management, voltage restoration and reactive compensation, in all these works the inverter works in open loop and the transient response to disturbances is not evaluated [

16,

20,

21]. For Infinite levels operation, the DC-DC converter output voltage must follow a sinusoidal signal reference, being necessary to consider the dynamics of the DC-DC converter, which has been little or nothing explored. If there is a speed error, there will be a phase shift in the inverter voltage signal, which would complicate control signals synchronization, especially if it works integrated into a power electrical system (PES). Also a poor transient response could result in a poor response to disturbances or primary control strategies within a PES [

22,

23,

24,

25].

Power converters in closed loop could improve its dynamic response in time and over impulse throught a controller [

26]. There are some works that include a cascade controller in DC-DC converters such as [

22,

27,

28], they implements PID, GPI and H

∞ controllers on high-end processors such as DSP and FPGA, GPI controller presents a lower settling time compared to PID,

vs.

respectively. In addition, GPI control shows an output shorter recovery time against sudden RL load switching and showed a higher noise decrease in the response. H

∞ controller has adaptive characteristic as it changes the

parameter based on the degree of error present in the output, this controller obtains a settling time of

.

Modern control straegies have been explored in DC-DC converters, [

29] implements a Particle Swarm Optimization (PSO) algorithm to tune PID controller parameters and compared it with conventional Ziegler-Nichols method. Investigation concludes that the latter strategie provides a better dynamic response, however, it is noted that this technique is effective as long as system parameters like input voltage and load don’t change too much. Algorithms such as SMC (Sliding Mode Control) implemented in [

30] are a good nonlinear control strategy applied to power converters, it presents better performance compared to a dual-loop PI controller. Complex control algorithms require higher computational load, requiring complex control systems to improve system robustness but slowing down dynamic response.

In this article a monophasic multilevel inverter with DC-DC link is implementes trought a single-phase full-bridge inverter energized from a Buck converter, it includes closed loop operation in the BUCK converter, the contribution given is the analysis of closed loop operation to reduce the speed error and provide immunity to disturbances, compared with open loop operation in order to determine the suitability or not of this operation mode.

3. Results

To obtain data for open and closed loop evaluation of the BUCK converter within the infinite level inverter, the circuit described in the section is implemented, the output voltage is analyzed and recorded using an oscilloscope, with numerical storage capability, and then the data is analyzed with the FFT powergui tool of the simscape library of MATLAB R2023b,

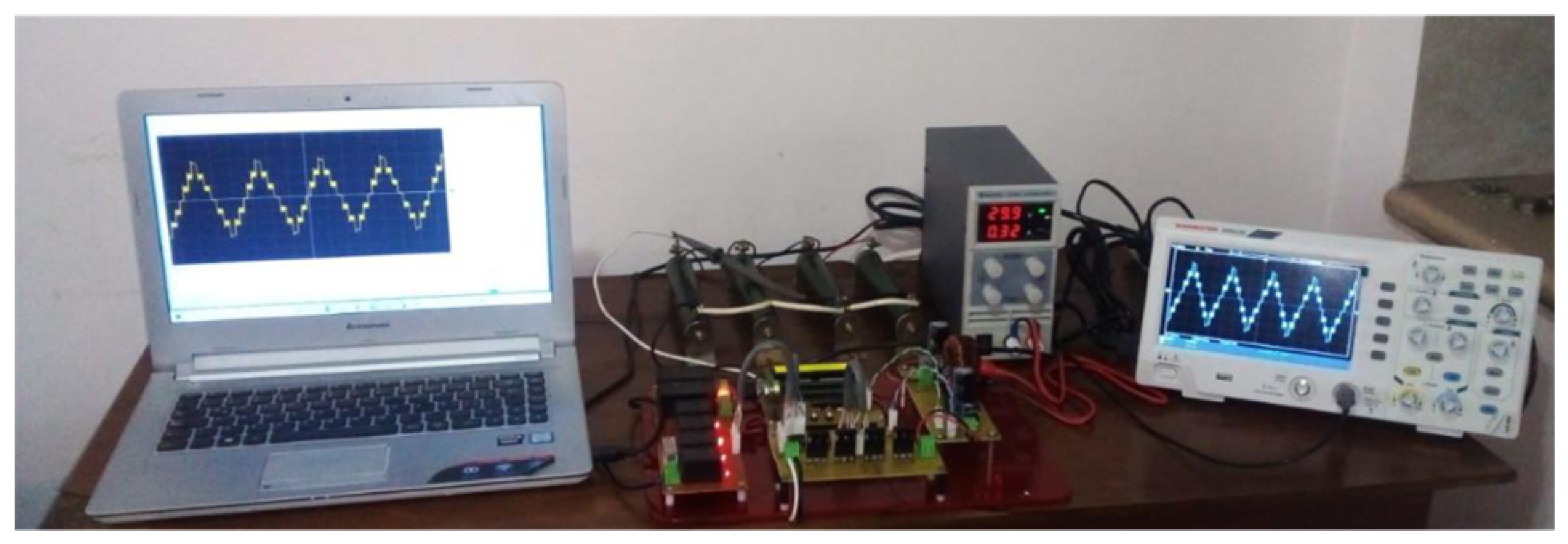

Figure 10 shows the implemented hardware.

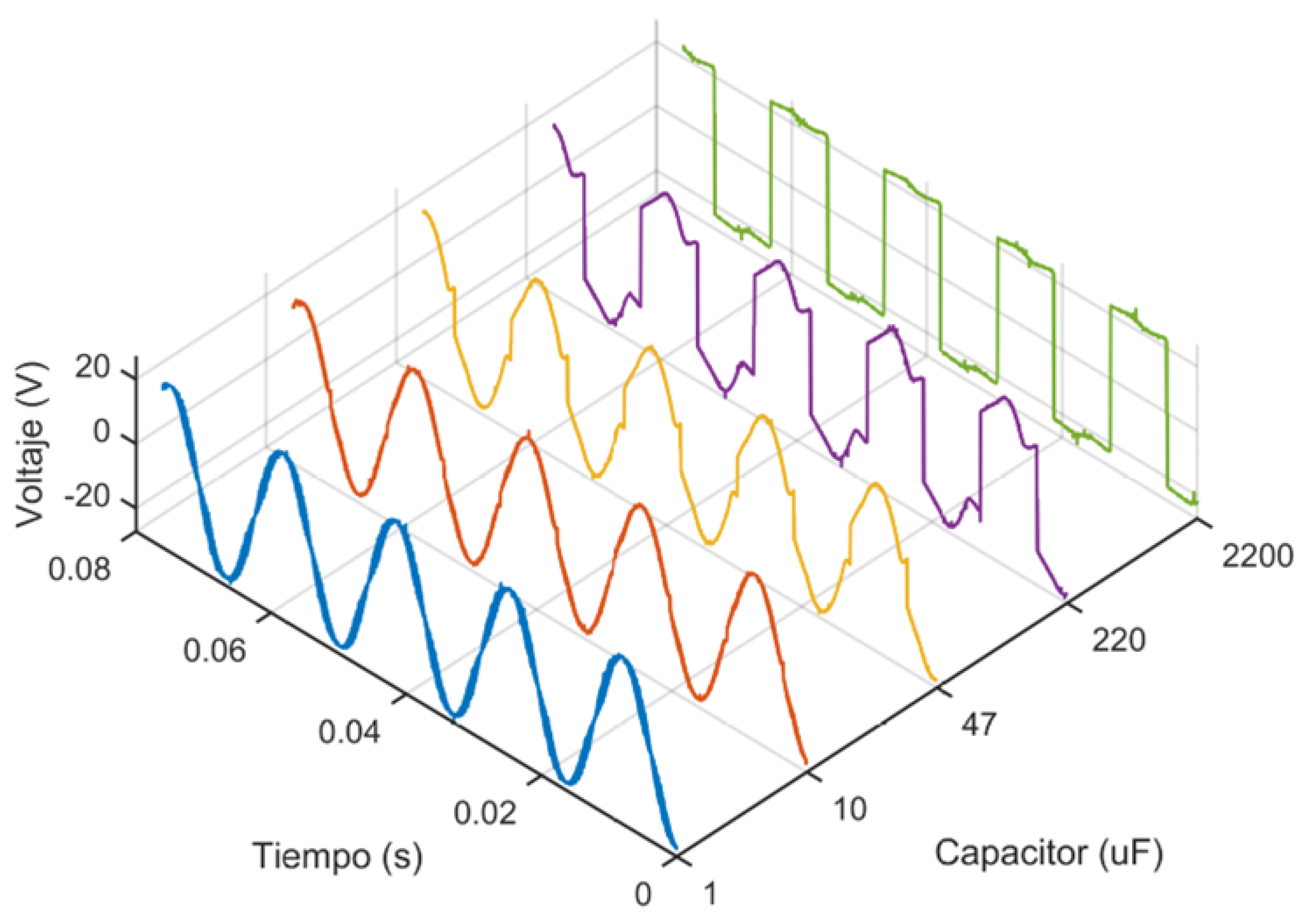

First open-loop operation is evaluated to form a sine wave of infinite levels, for this duty ratio

varies with

for a complete period. A square waveform is obtained because the BUCK converter presents a slow dynamics, with a settling time (

) of

. According to [

18], the

depends on equation 17, so the value of

C is modified, the results are synthesized in

Figure 11, where it can be appreciated that with

a sine wave is obtained and

. BUCK converter for an infinite level inverter must be designed with a low capacitance and so that this doesn’t affect

ripple, it must be designed with a small value of

.

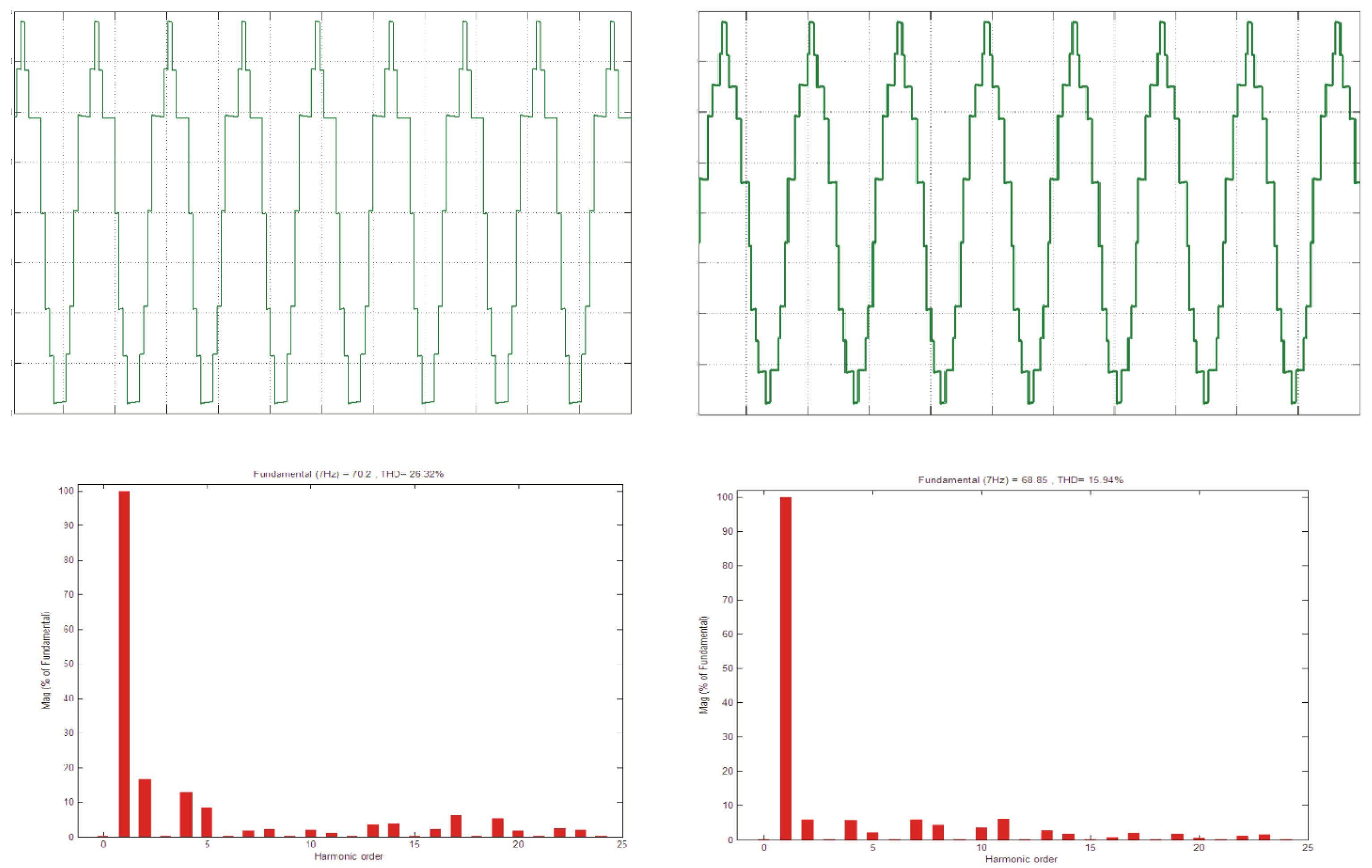

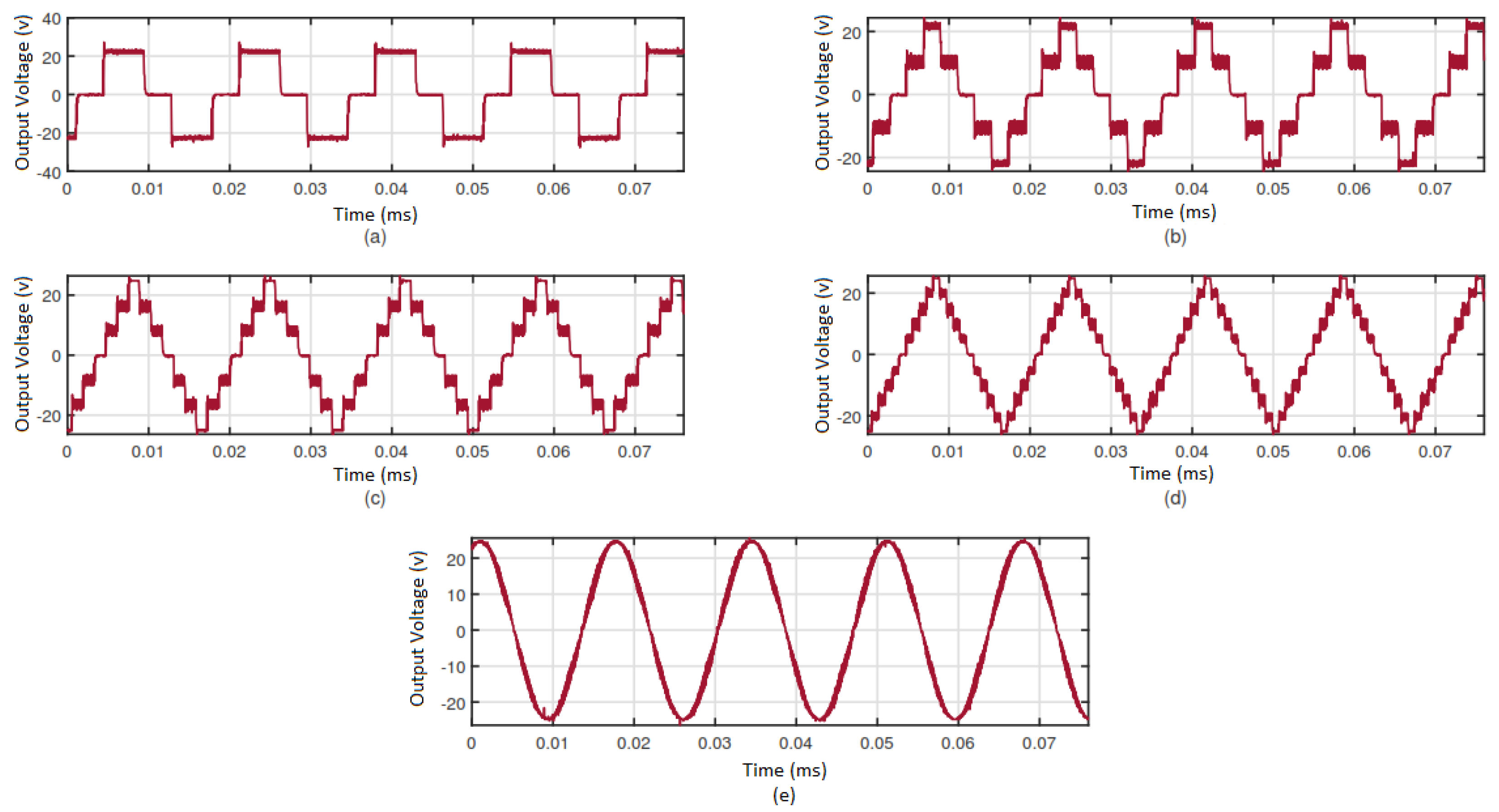

The operation is evaluated with

for

C, to form a stepped waveform of 3,5,7 and 9 levels. Obtained results can be seen in

Figure 12, where it is possible to appreciate the ripple presence in the levels of the stepped wave, this is due to the low value of capacitance.

Each wave is analyzed in MatLab to determine the distortion, obtaining the values shown in

Table 3, where a decrease in the harmonic content with respect to the increase of levels can be appreciated, obtaining a distortion

for infinite levels and increasing to

for three levels. In the case of infinite levels, a low harmonic content

in the third harmonic and less than

for the rest. THD percentage value obtained for infinite levels is within the ranges allowed by IEEE std.519 for low voltage applications.

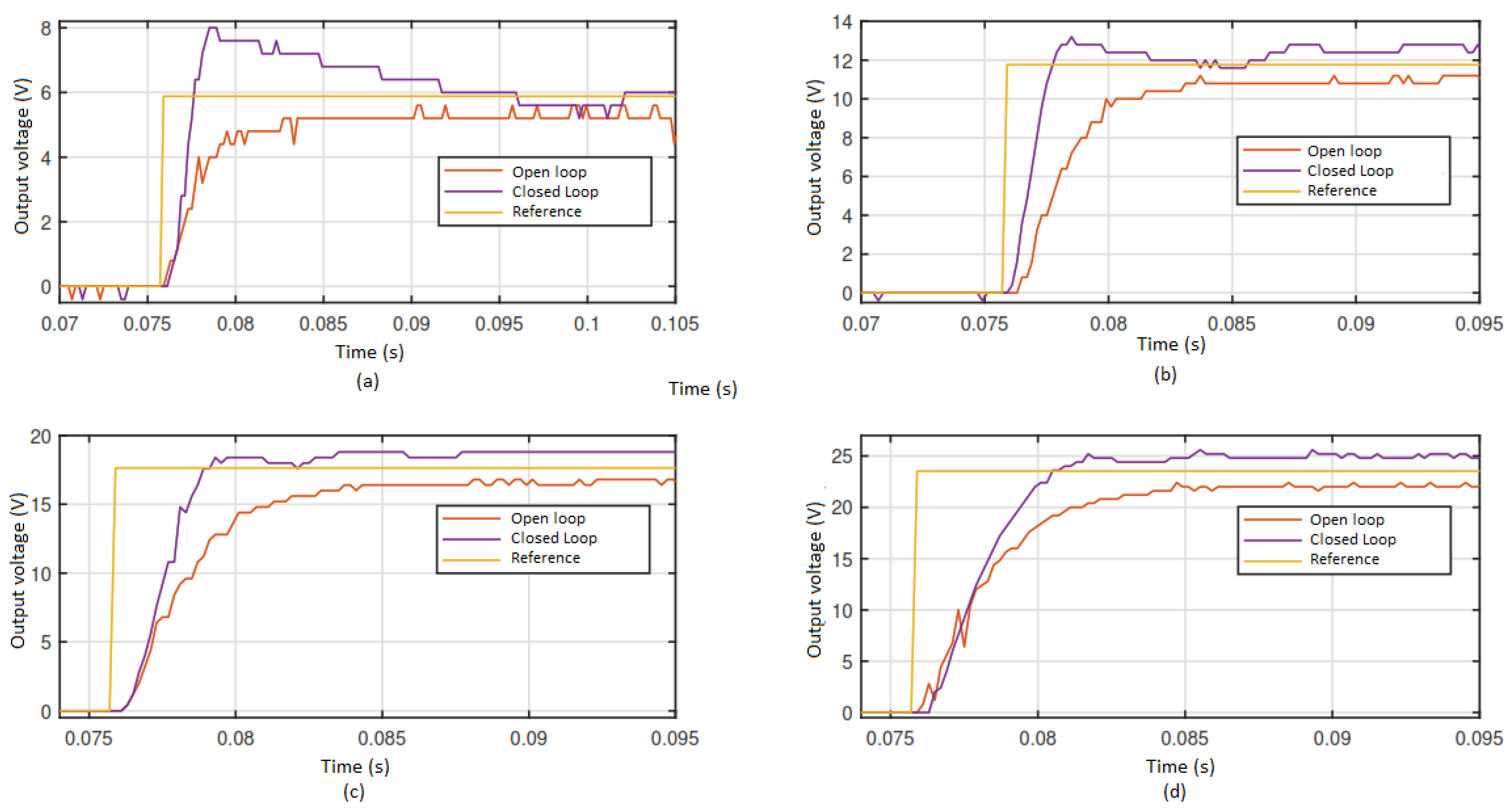

Before evaluating the infinite-level inverter closed-loop operation, isolated BUCK converter closed-loop is evaluated to observe the compensator influence. The test is performed for four reference values

,

,

and

. A comparison between open-loop and closed-loop dynamics is performed with the test results as can be seen in

Figure 13.

For each reference value the maximum over impulse

, settling time

and rise time

are measured. To measure

, 10% criterion is taken into account while

is measured between 10% and 90% of the voltage final value. For the

, the maximum value of the response is compared to the steady-state response value in uderdamped response. Measured parameters for the four scenarios are shown in

Table 4. There is an improvement in the

for closed loop operation, as the settling time

is reduced with larger reference change. The designed compensator allows to reduce steady state error so that in closed loop is maximum

, while in open loop the errors reaches

for reference variations from

to

.

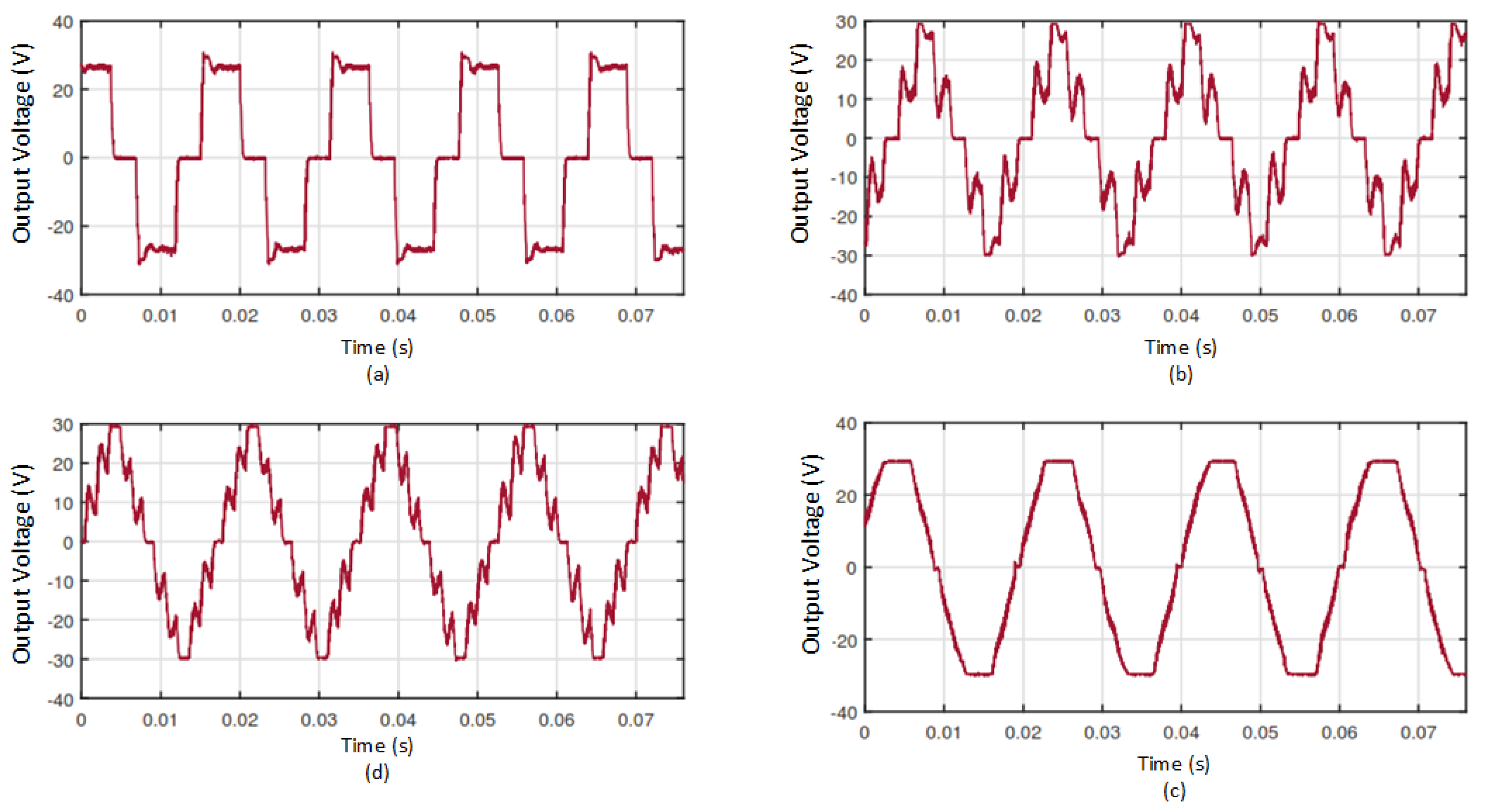

Finally closed-loop operation of the infinite level inverter is evaluated, the evaluation conditions are the same as in the open-loop test in order to contrast the results. Results obtained can be seen in

Figure 14, where a frequency of 60 Hz is achieved for the fundamental. When there is an increase of levels there is not a considerable improvement in THD as can be seen in

Table 5. The best result is presented for 3 levels with a THD of 33.51% which increases to 58.04% for infinite levels. The infinite level test measures a high presence of odd and even harmonics, so the resulting voltage waveforms have high THD and asymmetry values. As in open-loop, output voltage waves present peaks due to the low value of

C and it can be said that due to the fast dynamics in open-loop, the compensator does not help to improve the THD, compensator introduces latency in the inverter operation.

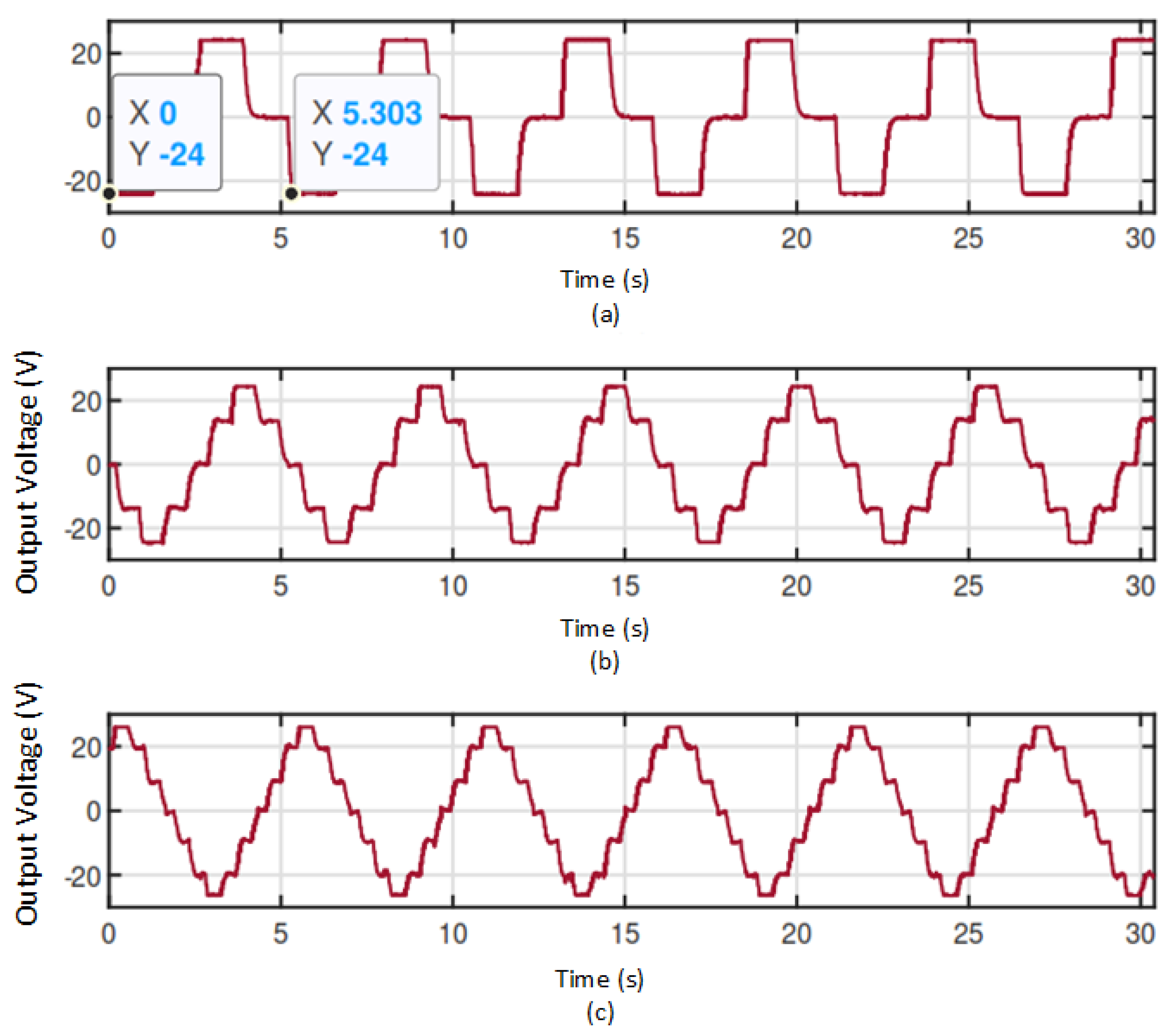

Additionally, Compensator behavior with 2200 uF in the BUCK converter output was evaluated, results shows that it isn’t possible to generate an output voltage with frequencies in 50Hz to 60Hz range, due to the converter slow dynamics. Changes in the reference at frequencies close to 60Hz generate system instability due to the output capacitor charging and discharging times. The frequencies generated under these test parameters allowed to generate alternating voltage waves at the output frequency up to

and a THD of 14.24% in the best case, there are no voltage peaks and compensator improve the transient, these results can be seen in

Figure 15 .

4. Conclusions

Open-loop test results are better than closed-loop tests results, open-loop harmonic distortion of 3.47% was obtained, which is a distortion value accepted by IEEE std 519 in low voltage applications, on the other hand, closed-loop showed high levels of harmonic distortion as well as the presence of even harmonics revealing a low quality in the output voltage waveform generated. This shows that for an infinite level inverter designed with a fast dynamic DC-DC converter it is not convenient to close the loop with the DC output voltage, as future research would be to evaluate the behavior by closing the loop with the rms voltage at the inverter output.

The use of the controller allows decreasing the rise times in the converter response, however, the converter output continues presenting a slow transient response, which does not satisfy the dynamics requirement for an inverter of infinite levels, so it is not possible to generate output AC voltages with frequencies between 50-60 Hz that are applicable to common loads. The converter presents instability when working with slow dynamics (high output capacitance) to rapid changes in the reference.

In similar works, PI controllers are used in the control loop, due to simplicity, and the problems that could cause the use of more complex controllers in their execution time. The implemented digital PI controller, in spite of improving the dynamics in open loop, did not present good results for this type of applications. Modern digital compensators require high processing times, which requires that they be developed on multicore embedded or FPGA-based systems to avoid introducing speed error- due to latency in this application where there is fast dynamic. The increasing use of high-end microprocessor systems operating at speeds of the order of GHz in power electronics applications will allow the development and execution of more precise control algorithms that can take advantage of different power conversion circuit topologies in more efficient ways.

The current development of more stable, fast, efficient and high blocking voltage semiconductor devices will allow the more frequent use of DC-DC converter topologies to obtain inverters with low distortion at high voltages, leaving aside the common inverter topologies (anchored diode, floating capacitor and cascade bridge) due to their size, number of semiconductor elements and control complexity.

The discharge time of a capacitor depends on the value of the capacitor and the value of the load, which can be on the order of nanoseconds (ns), milliseconds (ms) or seconds (s). For small times, the compensator has almost no effect on the dynamics of the system because the controller can use longer sampling times, also must be added the execution times used by the controller to perform mathematical floating point operations and control of other peripherals.

Author Contributions

Conceptualization, N.G.V.P., A.A.T., J.R.U., V.T.O and E.G.; Methodology, N.G.V.P., A.A.T., J.R.U. and V.T.O.; Software, MATLAB R2023b, N.G.V.P., A.A.T., J.R.U. and E.G.; Validation, N.G.V.P., A.A.T., J.R.U, V.T.O and E.G.; Formal analysis, N.G.V.P., A.A.T., J.R.U., V.T.O and E.G.; Investigation, N.G.V.P., A.A.T., J.R.U. and E.G.; Resources, N.G.V.P. and A.A.T.; Data curation, N.G.V.P., A.A.T. and J.R.U.; Writing—original draft, N.G.V.P., A.A.T., J.R.U., and V.T.O.; Writing—review & editing, N.G.V.P., A.A.T., J.R.U., V.T.O and E.G.; Visualization, N.G.V.P. and A.A.T.; Supervision, A.A.T. and J.R.U.; Project administration, A.A.T.; Funding acquisition, A.A.T. All authors have read and agreed to the published version of the manuscript.

Figure 1.

Inverter Topologý, output waveform and harmonic spectre. Left, PWM inverter. Right, SPWM inverter.

Figure 1.

Inverter Topologý, output waveform and harmonic spectre. Left, PWM inverter. Right, SPWM inverter.

Figure 2.

Multilevel inverter conceptual topology and output waveform.

Figure 2.

Multilevel inverter conceptual topology and output waveform.

Figure 3.

Harmonic spectre in 5 and 9 level inverter.[

4]

Figure 3.

Harmonic spectre in 5 and 9 level inverter.[

4]

Figure 4.

Infinite level inverter schematic.

Figure 4.

Infinite level inverter schematic.

Figure 5.

BUCK converter topology.

Figure 5.

BUCK converter topology.

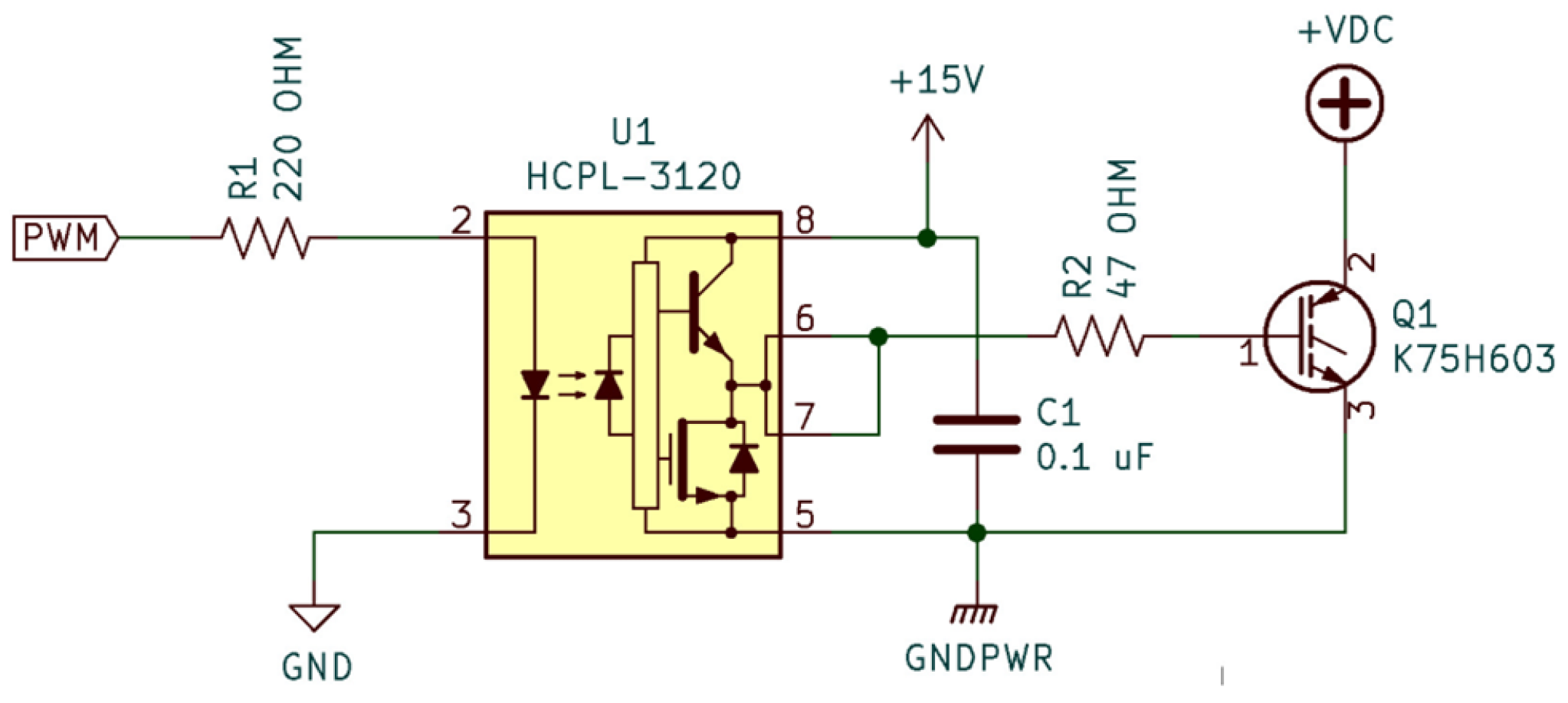

Figure 6.

BUCK converter topology.

Figure 6.

BUCK converter topology.

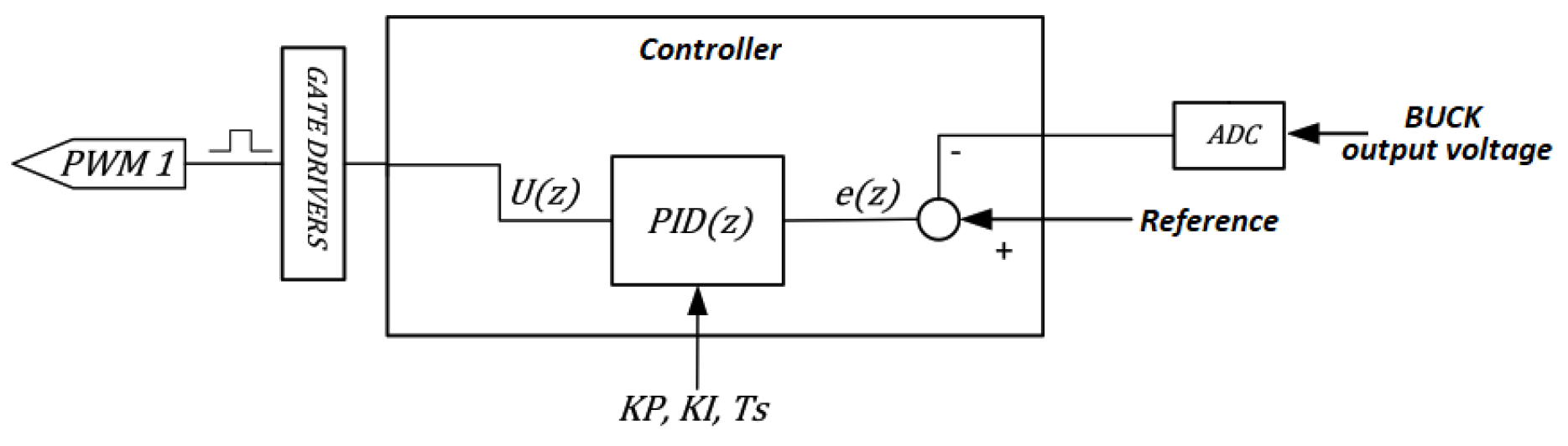

Figure 7.

Controller schematic

Figure 7.

Controller schematic

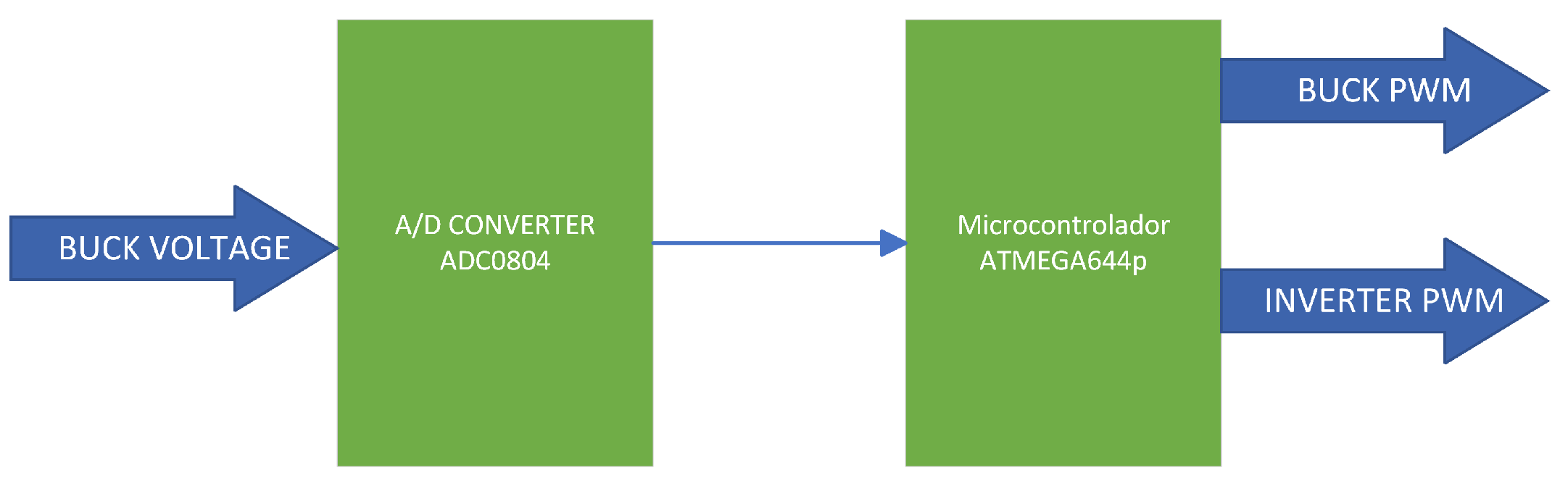

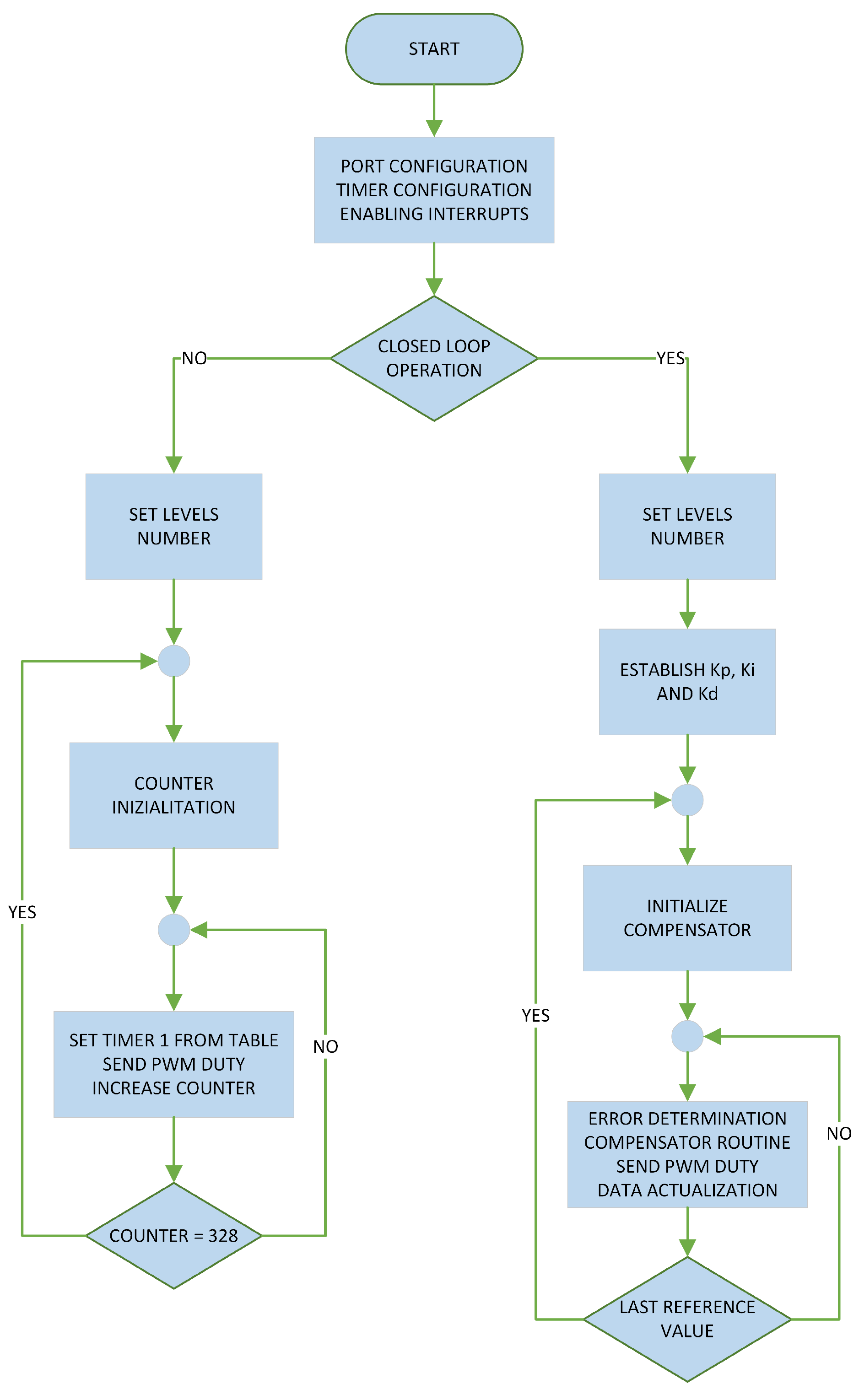

Figure 8.

ATMEGA644 program flow chart

Figure 8.

ATMEGA644 program flow chart

Figure 9.

Controller scheme

Figure 9.

Controller scheme

Figure 10.

Experimental hardware

Figure 10.

Experimental hardware

Figure 11.

Capacitance effect on Voltage output waveform

Figure 11.

Capacitance effect on Voltage output waveform

Figure 12.

Inverter output voltage waveform for 3, 5, 7, 9 and infinite level

Figure 12.

Inverter output voltage waveform for 3, 5, 7, 9 and infinite level

Figure 13.

BUCK converter in closed lopp operation

Figure 13.

BUCK converter in closed lopp operation

Figure 14.

Results in an infinite level inverter in closed loop operation for 3, 5, 7 and ∞ levels

Figure 14.

Results in an infinite level inverter in closed loop operation for 3, 5, 7 and ∞ levels

Figure 15.

Results in an infinite level inverter in closed loop operation for 3, 5, 7 and ∞ levels with

Figure 15.

Results in an infinite level inverter in closed loop operation for 3, 5, 7 and ∞ levels with

Table 1.

Electric components number in m-multilevel inverter topologies [

6].

Table 1.

Electric components number in m-multilevel inverter topologies [

6].

| Topology |

Number of Switches |

Number of Diodes |

Number of Capacitors |

| Clamping Diode |

|

|

|

| Floating Capacitor |

|

0 |

|

| Cascaded inverters |

|

0 |

|

Table 2.

BUCK converter design conditions.

Table 2.

BUCK converter design conditions.

| Parameter |

Symbol |

Value |

| Input Voltage |

|

|

| Duty ratio |

|

|

| Output voltage ripple |

|

|

| Inductor current ripple |

|

|

| Switching frequency |

|

|

Table 3.

Characteristics and percentage of harmonic content of voltage signals.

Table 3.

Characteristics and percentage of harmonic content of voltage signals.

| |

3 Levels |

5 Levels |

7 Levels |

9 Levels |

∞ Levels |

| THD(%) |

34.28 |

28.63 |

20.93 |

15.70 |

3.47 |

| Fund. (Vrms) |

16.42 |

12.68 |

14.24 |

14.21 |

17.35 |

| DC (V) |

0.05 |

0.16 |

0.13 |

0.14 |

0.08 |

| Fundamental(%) |

100 |

100 |

100 |

100 |

100 |

| h2(%) |

0.32 |

0.64 |

0.46 |

0.51 |

0.39 |

| h3(%) |

12.32 |

14.04 |

11.78 |

11.30 |

1.26 |

| h4(%) |

11.11 |

1.18 |

0.79 |

0.80 |

0.16 |

| h5(%) |

24.08 |

10.72 |

6.19 |

4.28 |

0.16 |

| h6(%) |

0.90 |

0.20 |

0.23 |

0.08 |

0.32 |

| h7(%) |

5.46 |

12.91 |

3.88 |

2.31 |

0.59 |

| h8(%) |

0.56 |

1.56 |

0.52 |

0.25 |

0.08 |

| h9(%) |

10.18 |

10.78 |

4.62 |

1.24 |

0.36 |

| h10(%) |

1.23 |

0.04 |

0.05 |

0.06 |

0.17 |

| h11(%) |

8.23 |

2.84 |

8.77 |

1.02 |

0.26 |

| h12(%) |

0.42 |

0.54 |

1.33 |

0.27 |

0.17 |

| h13(%) |

2.36 |

4.31 |

6.27 |

0.72 |

0.24 |

| h14(%) |

1.08 |

0.29 |

0.12 |

0.13 |

0.05 |

| h15(%) |

6.66 |

4.81 |

1.80 |

1.58 |

0.26 |

Table 4.

BUCK converter in open and closed loop comparison

Table 4.

BUCK converter in open and closed loop comparison

| |

Closed loop |

Open loop |

| Voltage Reference () |

|

|

(%) |

|

|

|

| 5.880 |

1 |

28.9 |

36.05 |

3.2 |

9.21 |

− |

| 11.76 |

1.2 |

19.1 |

12.24 |

4.4 |

9.01 |

− |

| 17.64 |

2 |

9.61 |

− |

5.2 |

8.41 |

− |

| 23.52 |

3 |

6.41 |

− |

4.8 |

9.61 |

− |

Table 5.

Harmonic content for infinite level inverter in closed loop operation

Table 5.

Harmonic content for infinite level inverter in closed loop operation

| |

3 Levels |

5 Levels |

7 Levels |

∞ Levels |

| THD(%) |

33.51 |

34.54 |

32.77 |

58.04 |

| Fund. (Vrms) |

19.83 |

15.55 |

17.01 |

6.246 |

| DC (V) |

0.469 |

0.285 |

0.328 |

1.907 |

| Fundamental(%) |

100 |

100 |

100 |

100 |

| h2(%) |

1.58 |

0.44 |

5.90 |

11.76 |

| h3(%) |

6.89 |

14.08 |

7.72 |

4.73 |

| h4(%) |

2.57 |

1.05 |

1.71 |

8.83 |

| h5(%) |

17.85 |

15.70 |

0.75 |

4.27 |

| h6(%) |

2.61 |

0.47 |

0.79 |

2.29 |

| h7(%) |

4.83 |

12.67 |

1.57 |

2.21 |

| h8(%) |

0.36 |

3.43 |

1.62 |

2.25 |

| h9(%) |

2.54 |

12.21 |

1.31 |

4.23 |

| h10(%) |

0.78 |

0.45 |

0.43 |

3.21 |

| h11(%) |

0.38 |

3.51 |

1.85 |

1.73 |

| h12(%) |

0.13 |

1.38 |

1.67 |

1.61 |

| h13(%) |

0.11 |

1.72 |

1.38 |

1.54 |

| h14(%) |

0.43 |

0.56 |

0.83 |

1.03 |

| h15(%) |

1.36 |

0.36 |

0.29 |

0.16 |