1. Introduction

Supplying and conditioning power are the most fundamental functions of an electrical system. In modern electronics, it is very important to adapt the voltage and current levels coming from an external source to a user with different voltage-current characteristics. As the use of battery-powered portable devices such as mobile phones, laptops, and various handheld devices has rapidly increased, power management should be one of the most important issues for maximizing the battery lifetime and providing energy to multiple on-chip blocks [

1]. Most electronic systems need a stable voltage to obtain performance in different operating conditions, especially in medical, military, and space fields. Sources like transformers, generators, batteries, and other offline supplies incur substantial voltage and current variations across time and they are normally noisy and jittery not only because of their inherent nature but also because high-power switching circuits like central-processing units (CPUs) and digital signal processing (DSP) circuits usually load it. These rapidly changing loads cause transient excursions in the supposedly noise-free supply, the results of which are undesired voltage drops and frequency spurs where only a DC component should exist.

A voltage regulator is an integral part of the power management system (PMS) of all electronic devices and it has been the focal point of research over the past few years [

2]. The role of the voltage regulator is to convert these unpredictable and noisy supplies to stable, constant, accurate, and load-independent voltages, attenuating these ill-fated fluctuations to lower and more acceptable levels. A simple and cheap solution to regulate an output voltage powered by a higher input consists of using Low-dropout (LDO) regulators. An LDO creates a drop voltage by a series element between the input and the output. Due to their inherent simplicity, LDO is ideal off-chip and on-chip solutions for powering noise-sensitive loads, such as phase-locked loops, analog-to-digital converters, and sensor interfaces, because they convert voltage through a linear operation with no output voltage ripples [

3]. An LDO requires no bulky components such as inductors, and therefore multiple of them can be integrated on a chip. Furthermore, since an LDO can create an independent voltage domain, each core/block of an SoC can operate at the optimal voltage, maximizing performance and energy efficiency [

4]. The primary role of an LDO is to provide a regulated voltage by filtering the residual ripples from the switching converters. with low ripple to the individual functional blocks in an SoC [

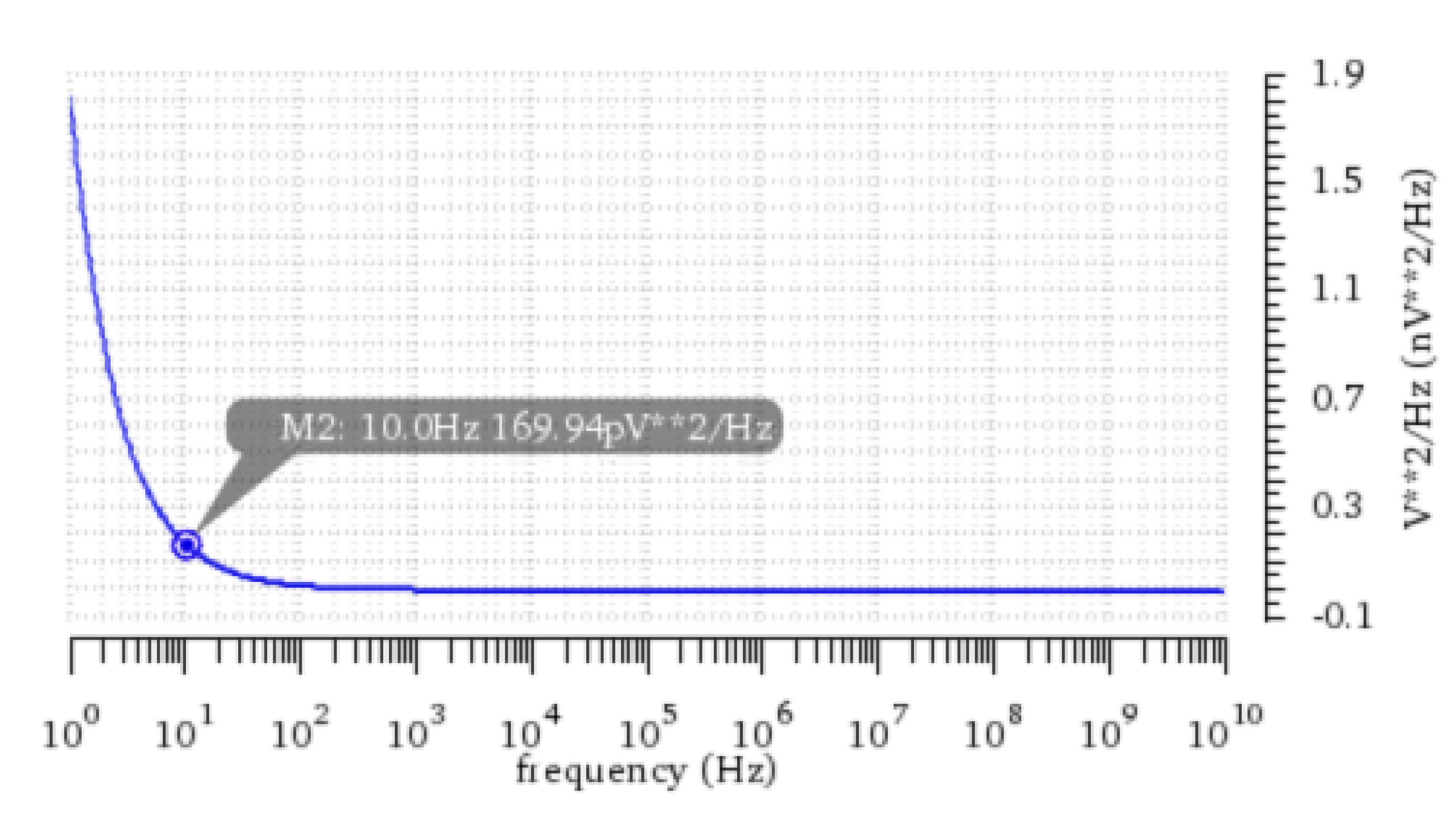

5]. The main issues concerning the LDO design consist of noise minimization and robustness against parameters’ variations.

Typical LDO uses a resistive divider to set the output voltage, so the noise gain is equal to the AC closed-loop gain, which as it turns out, is the same as the DC closed-loop gain [

6]. LDO voltage regulators result in small voltage drops across the power transistor and provide a well-regulated low-noise voltage [

7]. There are many sources of intrinsic noise in LDO. The major types of intrinsic noise include the following: thermal noise, 1/f noise, shot noise, and burst, or popcorn, noise [

8]. To suppress thermal and flicker noise, conventional LDOs utilize highly filtered voltage references at their inputs and bypass capacitors at their outputs. However, with technology scaling, noise increases significantly. Since the corner frequency is a weak function of most transistor parameters, suppression of low-frequency noise from supply regulators in sub-micron CMOS processes is becoming a critical design [

9].

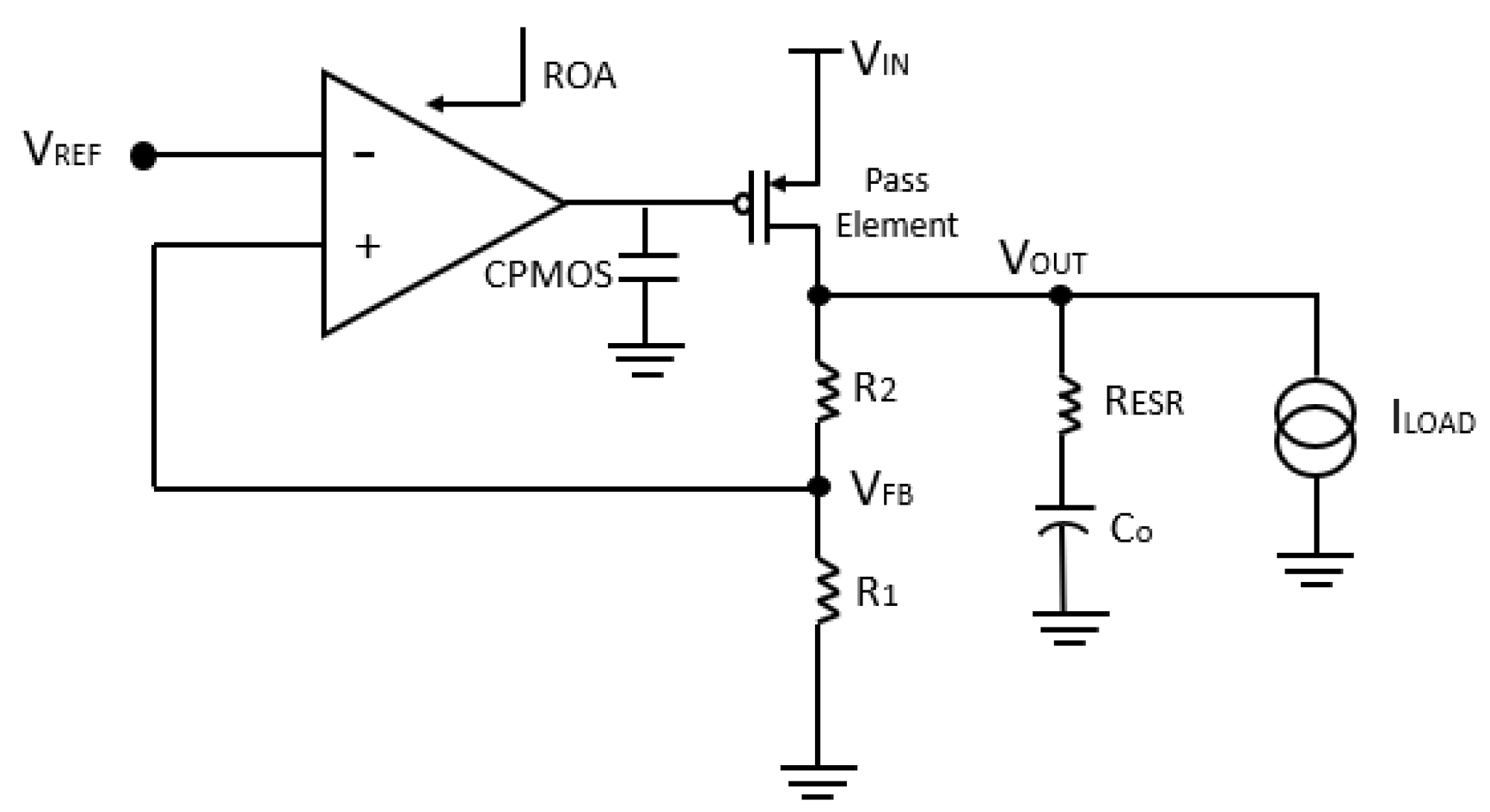

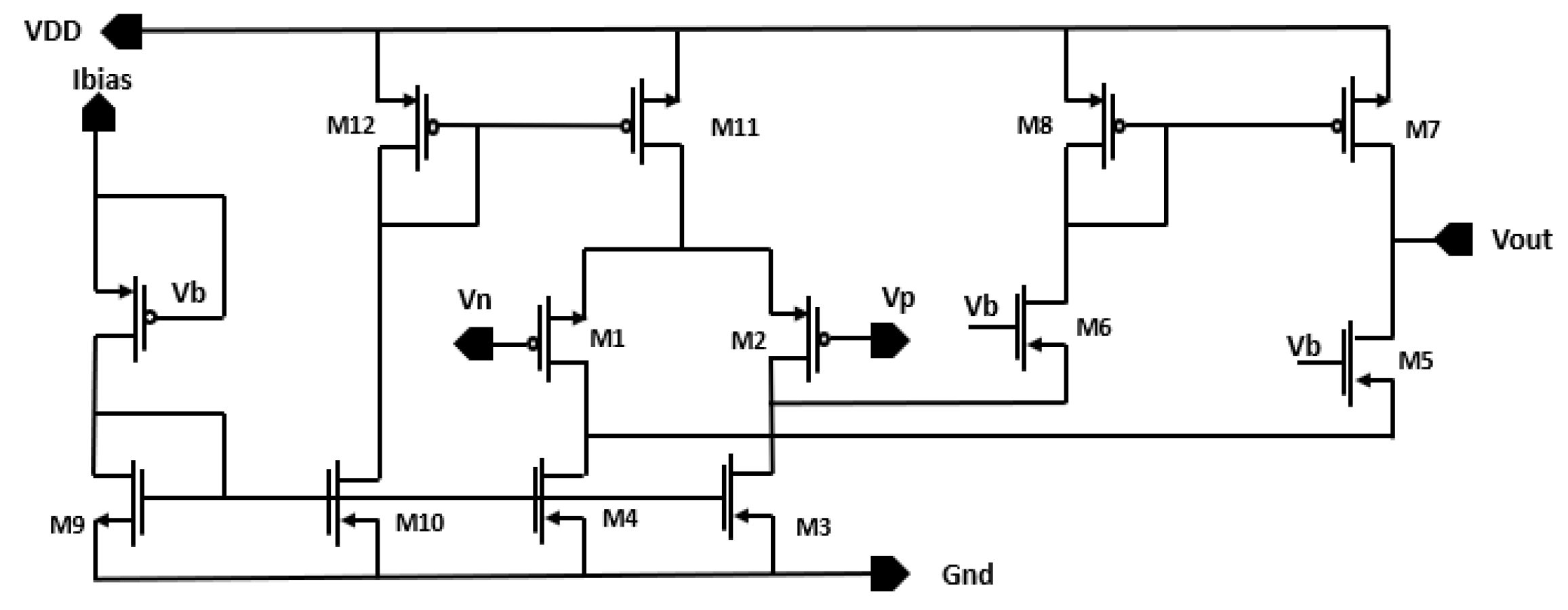

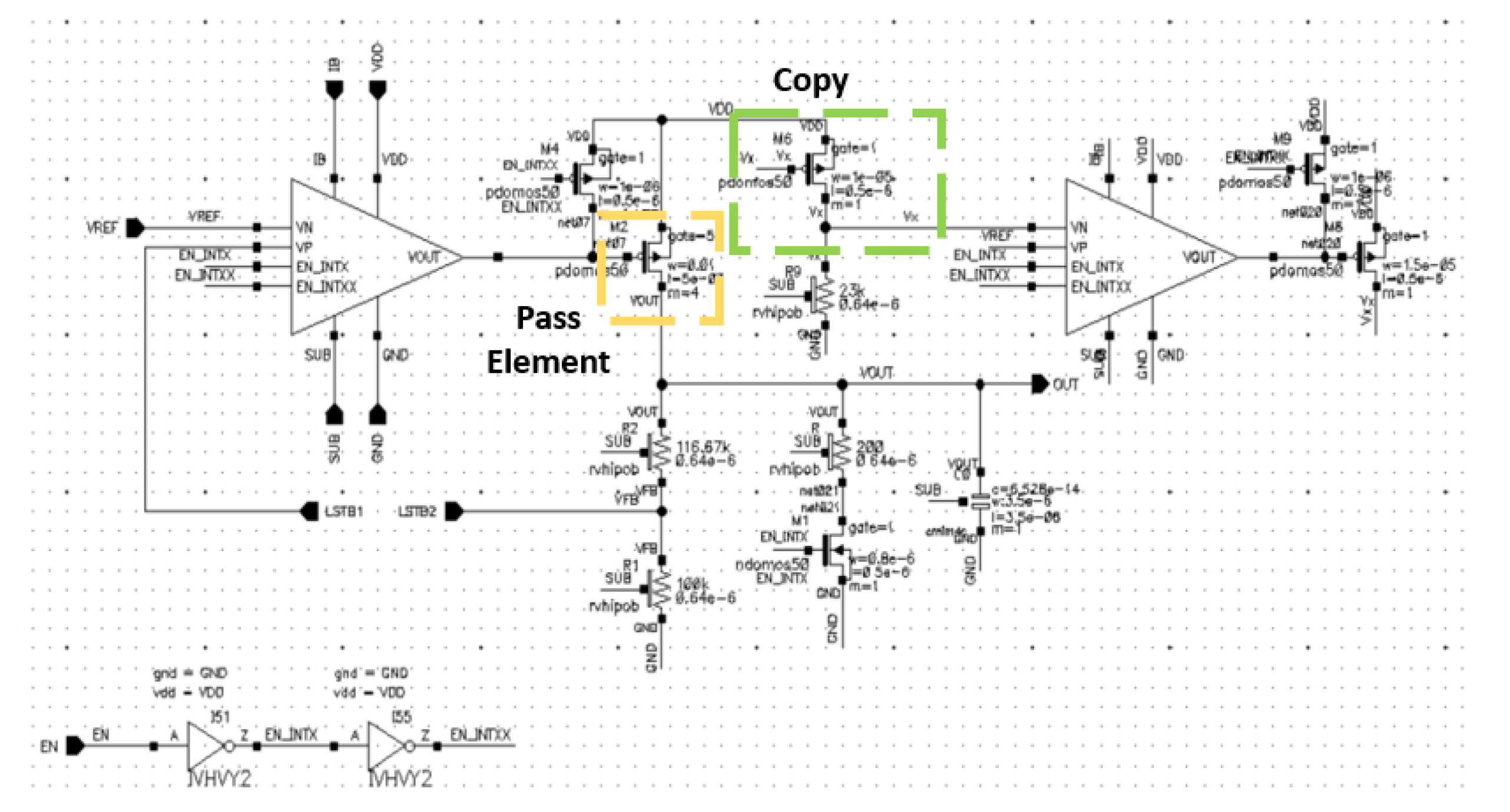

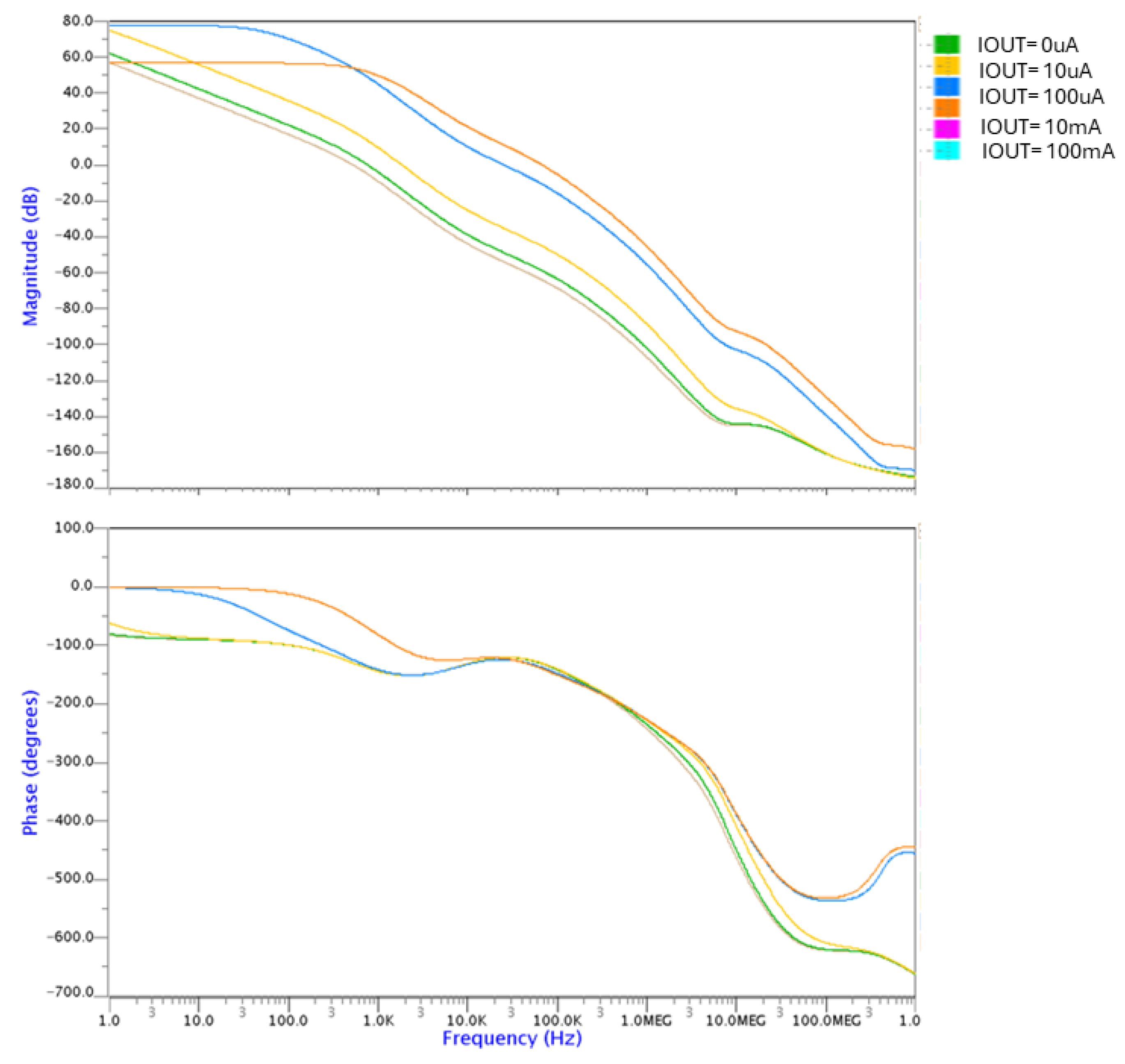

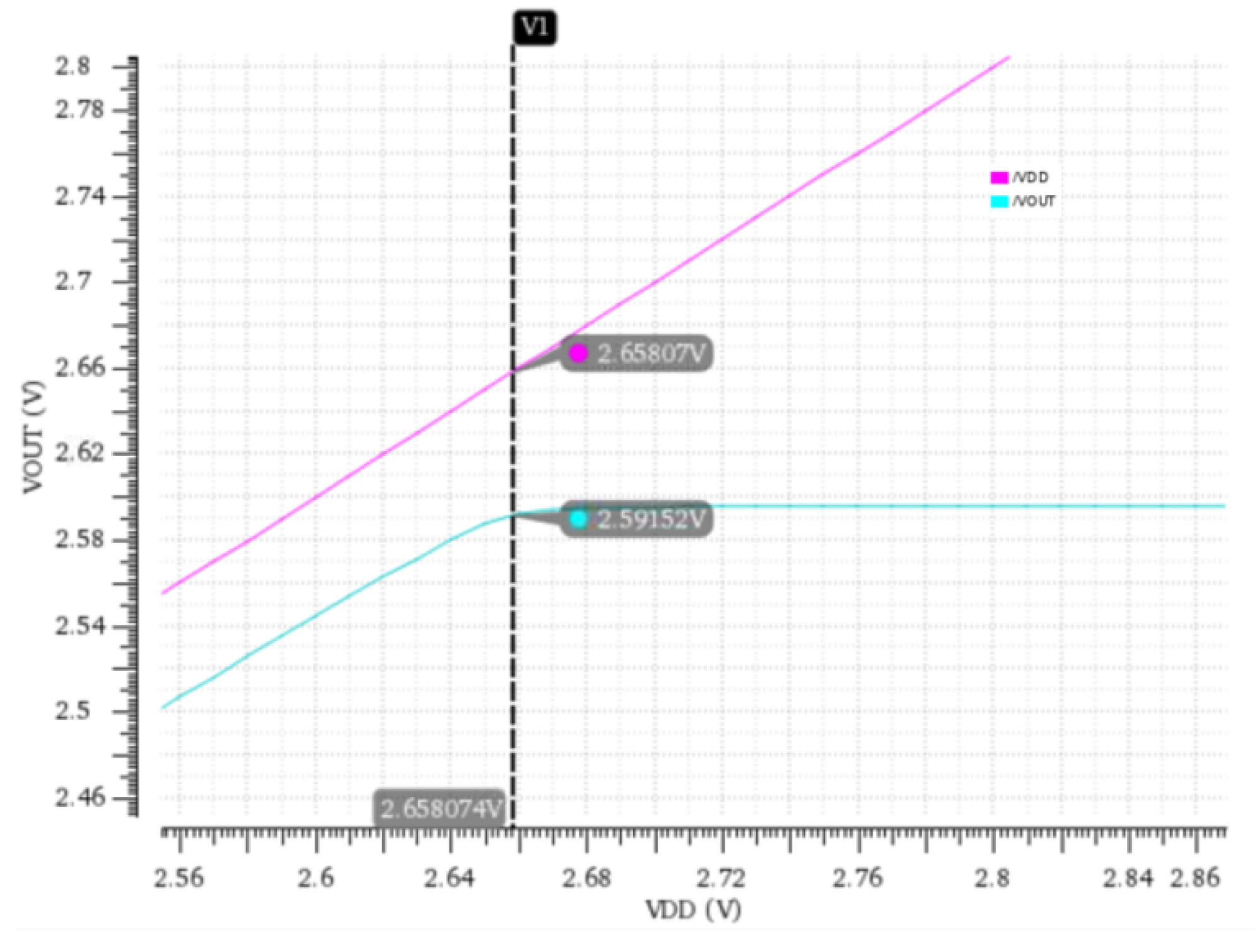

The purpose of this work is the design a Low Drop Regulator (LDO) with low noise specifications to provide its final user with a stable voltage independent within certain limits of the voltage, process variations of its components, and the temperature. The LDO is designed in such a way as to have a low dropout voltage, low noise, high efficiency, good transient response, and stability over a wide range of frequencies. An optimal way of folded cascode op-amp is designed to ensure high gain, single pole, good noise performance, and large output swing as compared to other architectures of operational amplifiers since op-amp is one of the major sources of noise in LDO. Moreover, the noise performance is further reduced from the point of view of the process, by the implantation of a layer of fluorine on the poly-silicon which reduces the 1/f noise by 30%.

After a brief introduction of the fundamentals of these devices, all the phases of the design at the transistor level will be described to obtain low noise performances in all supply voltage ranges, processes, mismatches, and temperature conditions. LDO regulators find extensive use in system-on-chip (SoC) solutions where there are incorporate numerous functions, many of which switch simultaneously with the clock, demanding both high-power and fast response times in short consecutive bursts. The bandwidth performance of such a regulator guarantees the ability to respond quickly to these transient variations of the above circuits. Regulators also protect and filter integrated circuits (ICs) from exposure to voltages exceeding junction-breakdown levels.

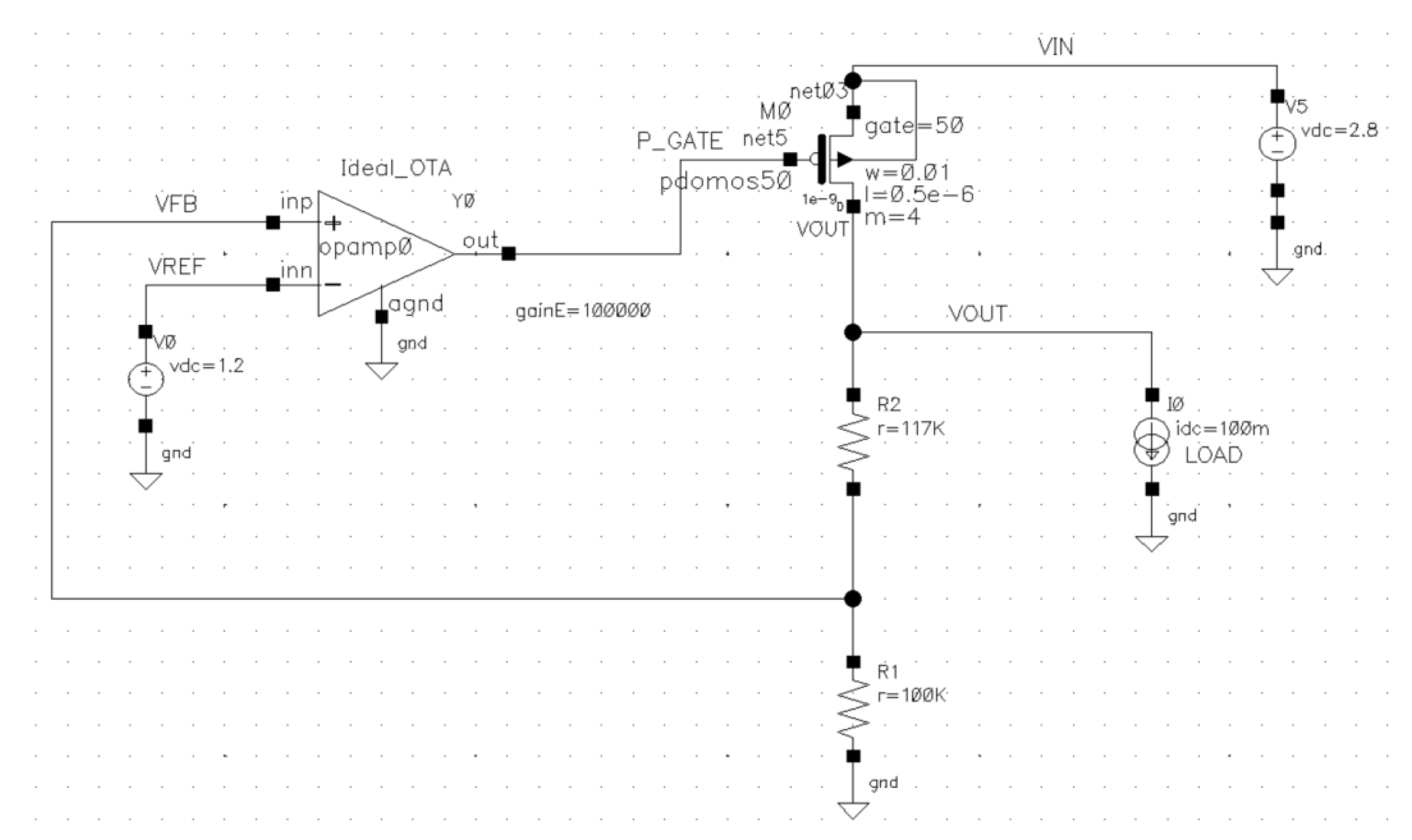

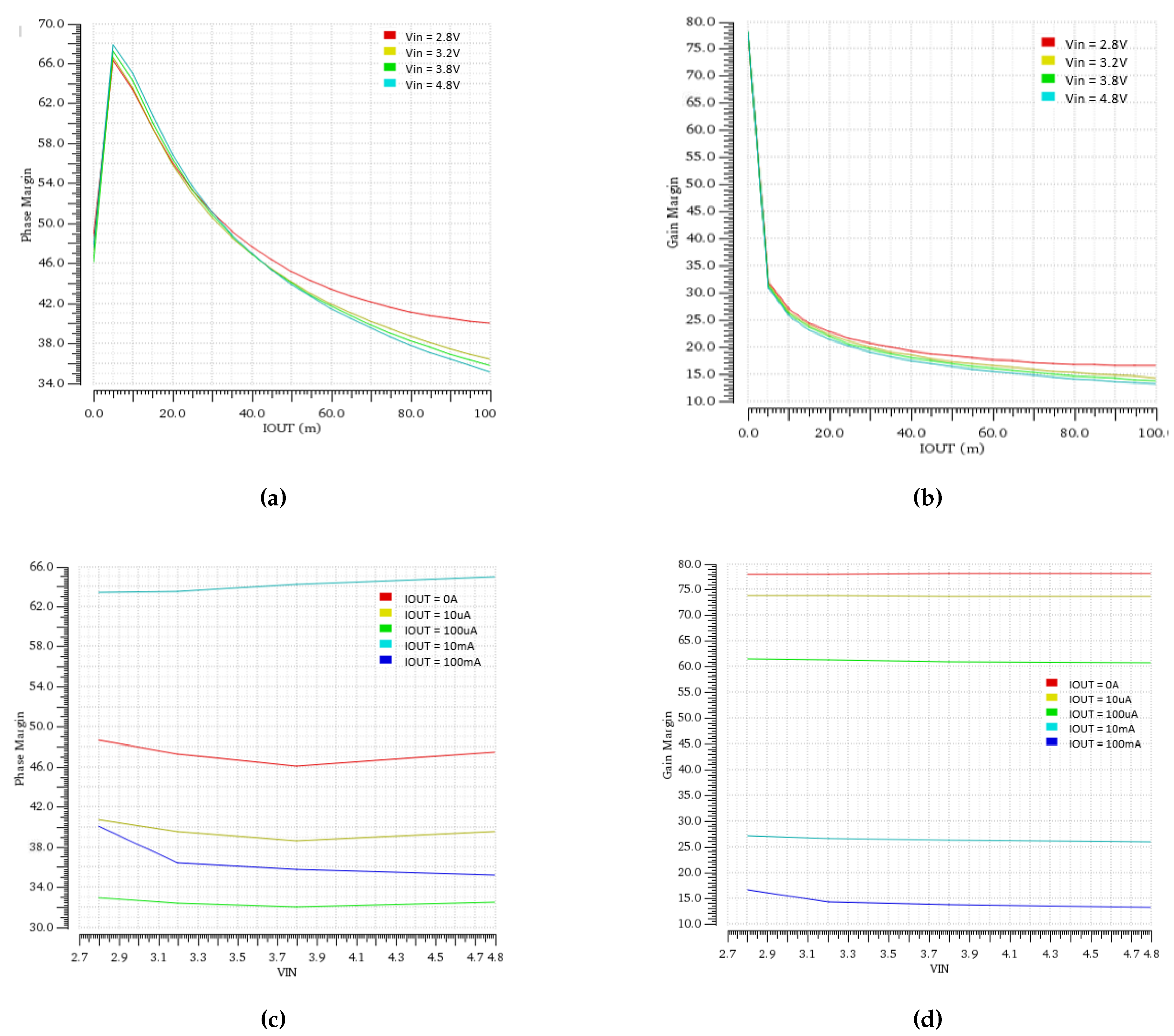

The work is organized as follows. In section II, the LDO fundamentals and literature review are presented. In section III, the simulation of LDO with ideal components except for the pass element, the size of the pass element is designed in such a way to provide regulation in all operating conditions. In section IV, the design of the folded cascode operational amplifier and its frequency compensation is presented with a source follower buffer. The op-amp designed provide huge noise reduction. In section V, the test results are presented with different input voltage and load conditions, and in section VI conclusions are presented. The novel topology of LDO ensures low dropout voltage, fast transient response and minimized power dissipation to achieve high power efficiency, maintain output voltage in the presence of fast load changes, and to lower the power loss across the pass element especially at high load.

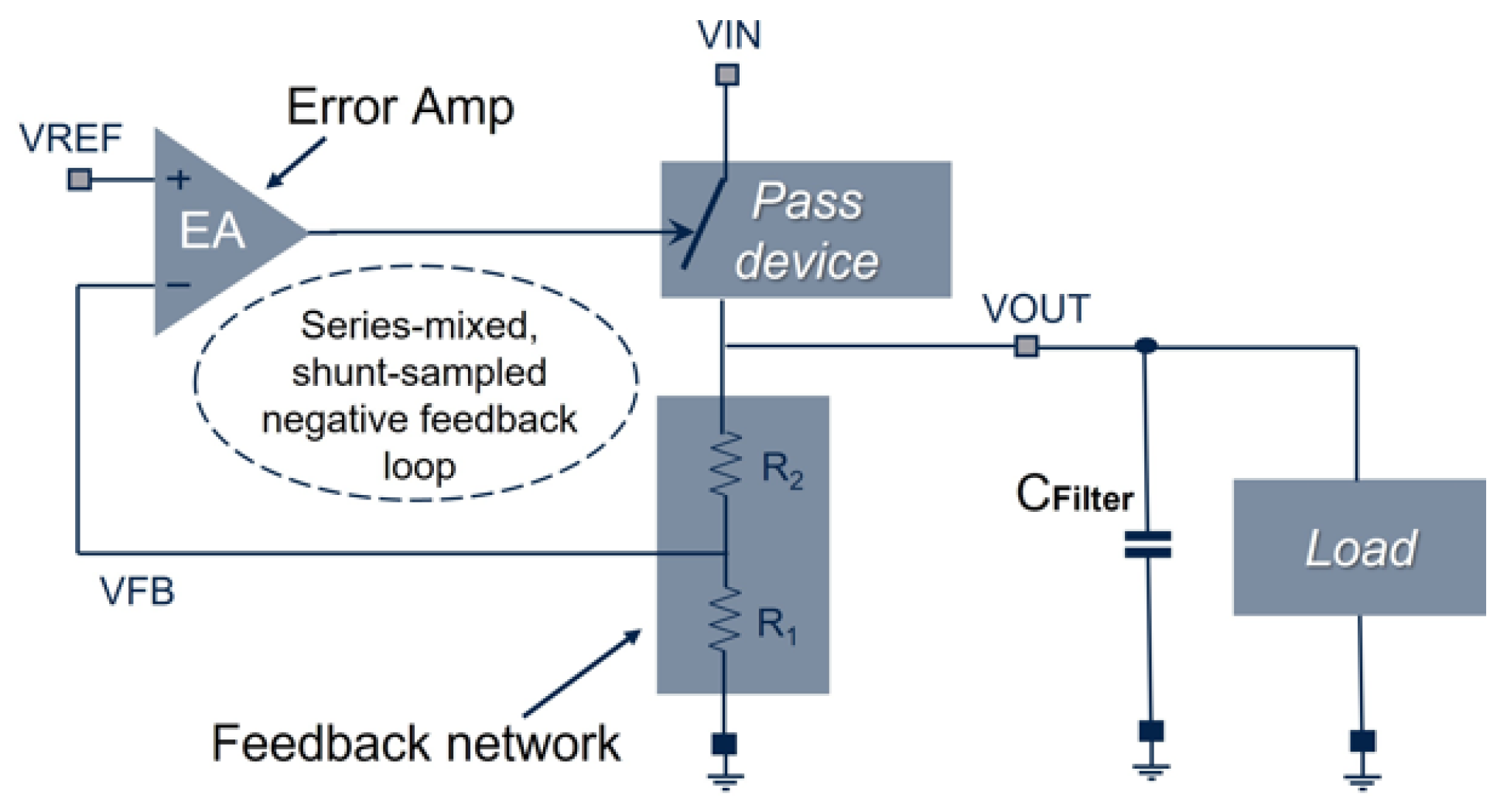

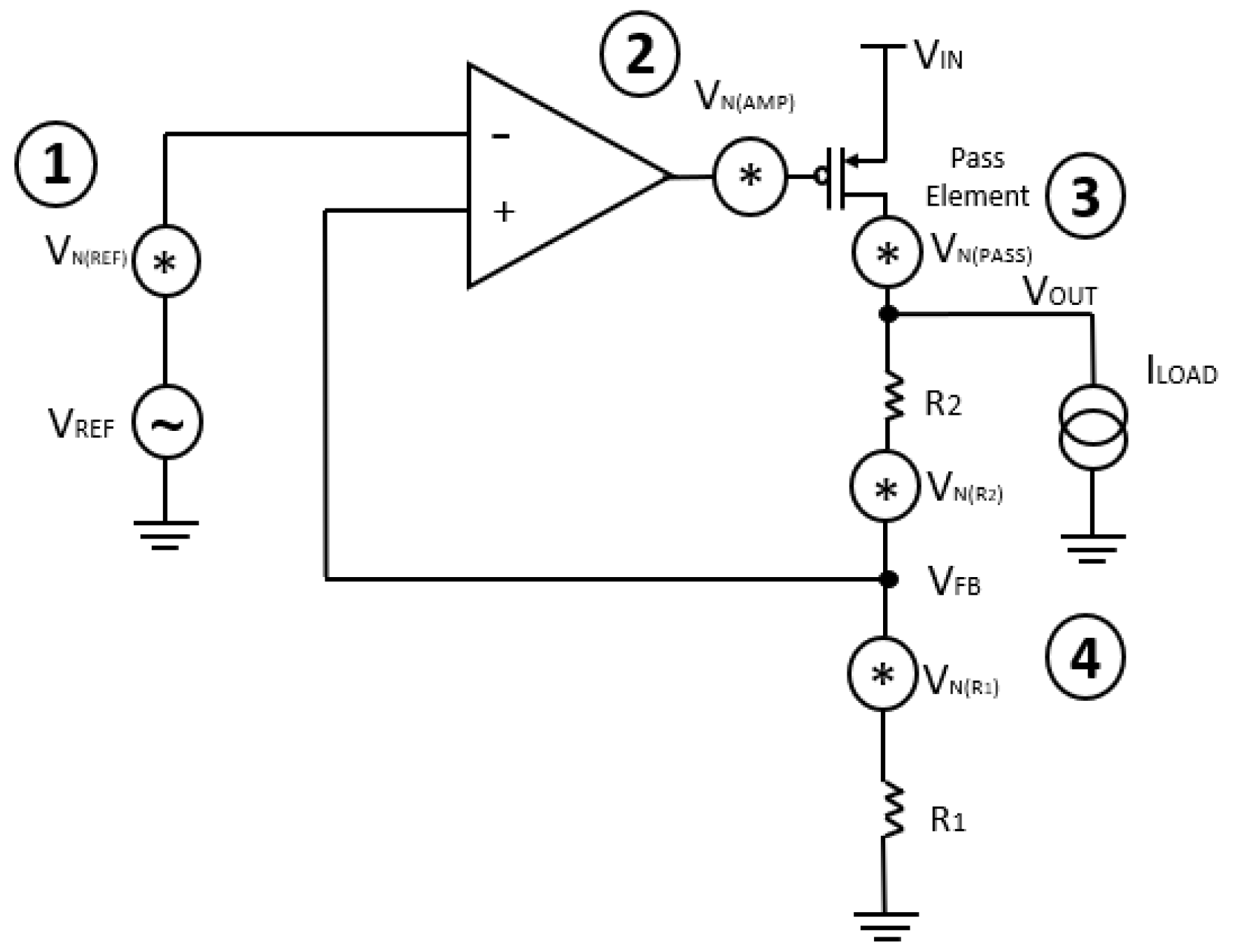

Figure 1.

Basic structure of an LDO.

Figure 1.

Basic structure of an LDO.