Submitted:

29 April 2024

Posted:

01 May 2024

Read the latest preprint version here

Abstract

Keywords:

1. Introduction

1.1. Medical Significance of EEG Signals Acquisition

1.1.1. EEG Fundamentals: Understanding Medical Relevance

1.1.2. EEG’s Role in Patient Monitoring

1.1.3. Representatives Examples in Realistic Cases in Diagnosing Brain-Related Conditions

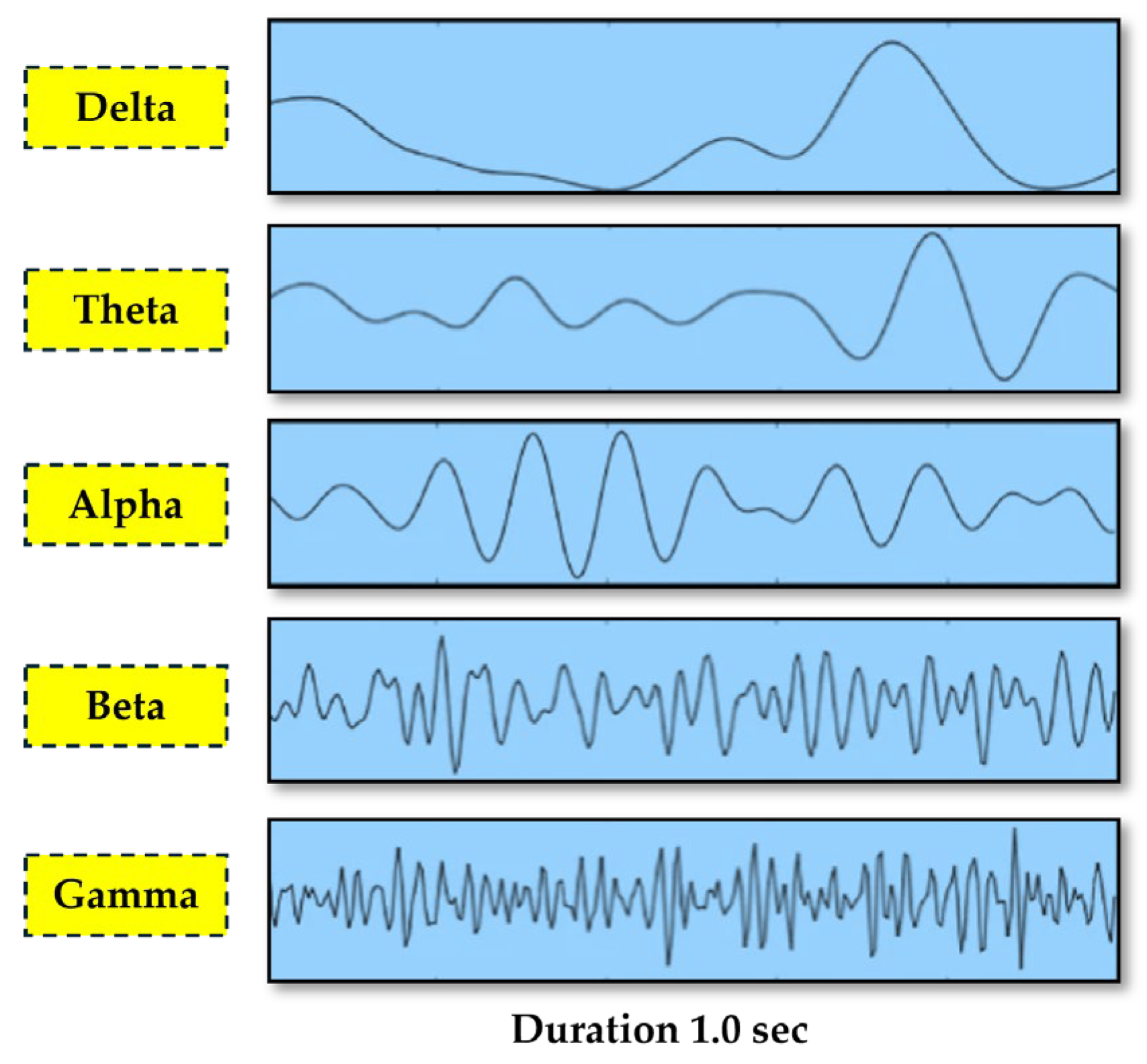

1.2. EEG Signals into Frequency Sub-bands: Comprehensive Categorization

1.3. Noise Interference in EEG Signal Acquisition

1.4. Design Specifications in Medical-Grade and Research-Grade EEG Generic Circuits Design

1.5. The Structure of the Present Study

- Section 1 (Introduction) highlights the medical importance of acquiring an EEG signal and its role in patient monitoring. It also discusses the sub-bands of frequencies into which the EEG signal is classified and introduces the challenges that noise brings in an acquired EEG signal. This section contains the following sub-sections:

- Section 1.1, Medical Significance of EEG Signals Acquisition: It is highlighted that EEG is a non-invasive technique used to diagnose a variety of neurological disorders.

- Section 1.2, EEG Signals into Frequency Sub-bands: It describes the significance and key topics related to various frequency bands of EEG.

- Section 1.3, Noise Interference in EEG Signal Acquisition: It includes the sources and effects of noise to the acquired EEG signals, together with the reduction measures that can be taken to minimize their effects.

- Section 1.4, Design Specifications in Medical-Grade and Research-Grade EEG Generic Circuits Design: It details the assembly and function of key EEG circuit components—filters, amplifiers, and protection circuits—raising both signal integrity and adaptability among diverse neuroscience applications.

- Section 2 (Related Works in EEG Circuit Design Analog Front-End Architectures) discusses design specifications on medical and research-grade EEG circuits. The selected case studies are elaborated with respect to the comparative analysis of various architectures of EEG AFE. Sub-sections of this Section are:

- Section 2.1, Low-Cost Circuit Design of EEG Analog Front-ends: Case ’1’ elaborates cost-effective designs for EEG AFE.

- Section 2.2, Battery-Powered, Low-Noise Amplifier Circuit Design of EEG Analog Front-ends: Case ’2’ presents the design of a battery-operated, low-noise EEG AFE.

- Section 2.3, Double Notch Filter Circuit Design of EEG Analog Front-ends: Case ’3’ deals with the design and performance of a high-performance EEG AFE having dual-notch filter circuitry.

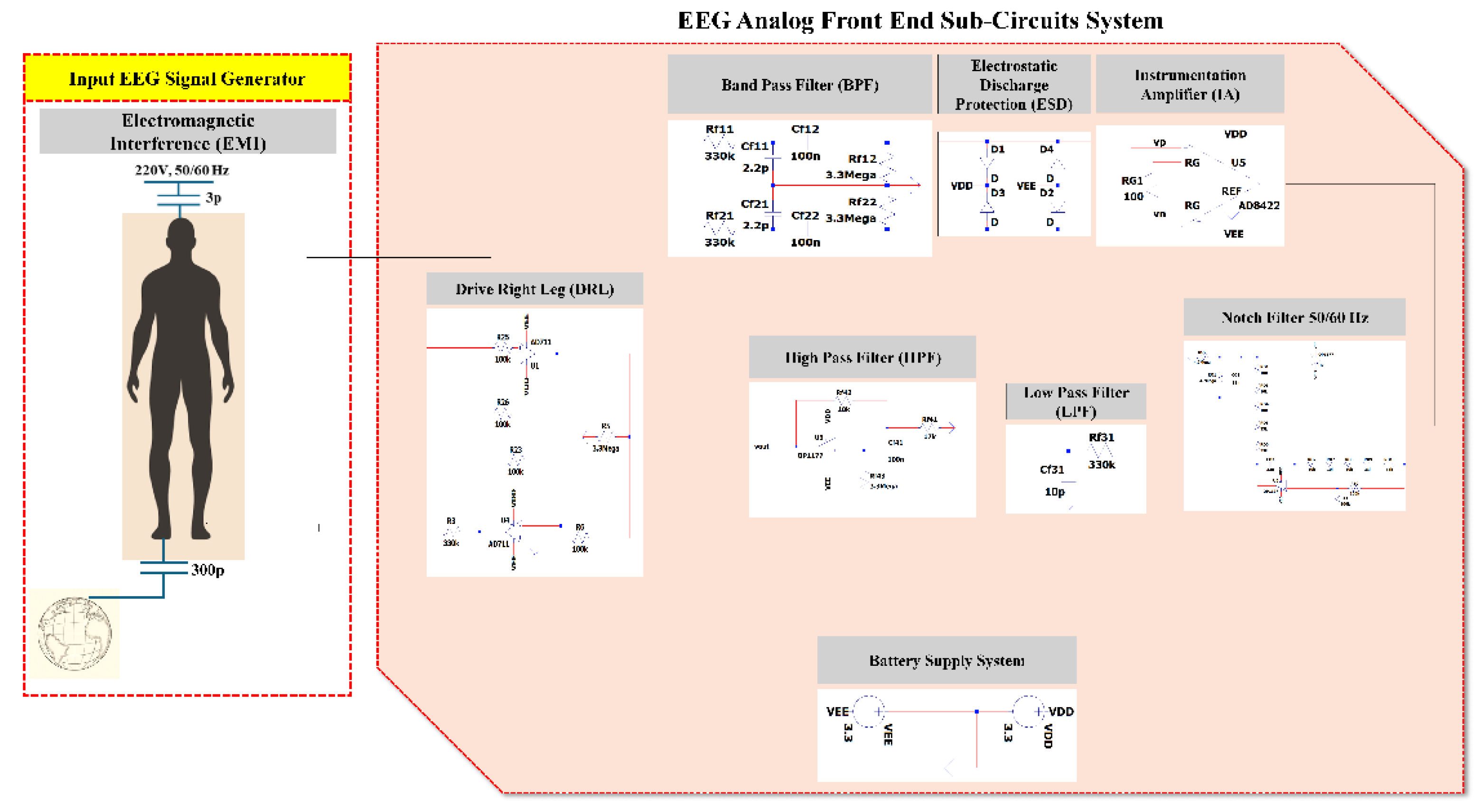

- Section 3 (Materials and Methods: Novel Proposed EEG Analog Front End Circuit System) puts forth a novel methodology for simulating and evaluating the novel EEG AFE circuitry design against practical cases using MATLAB. This section is organized into several sub-sections:

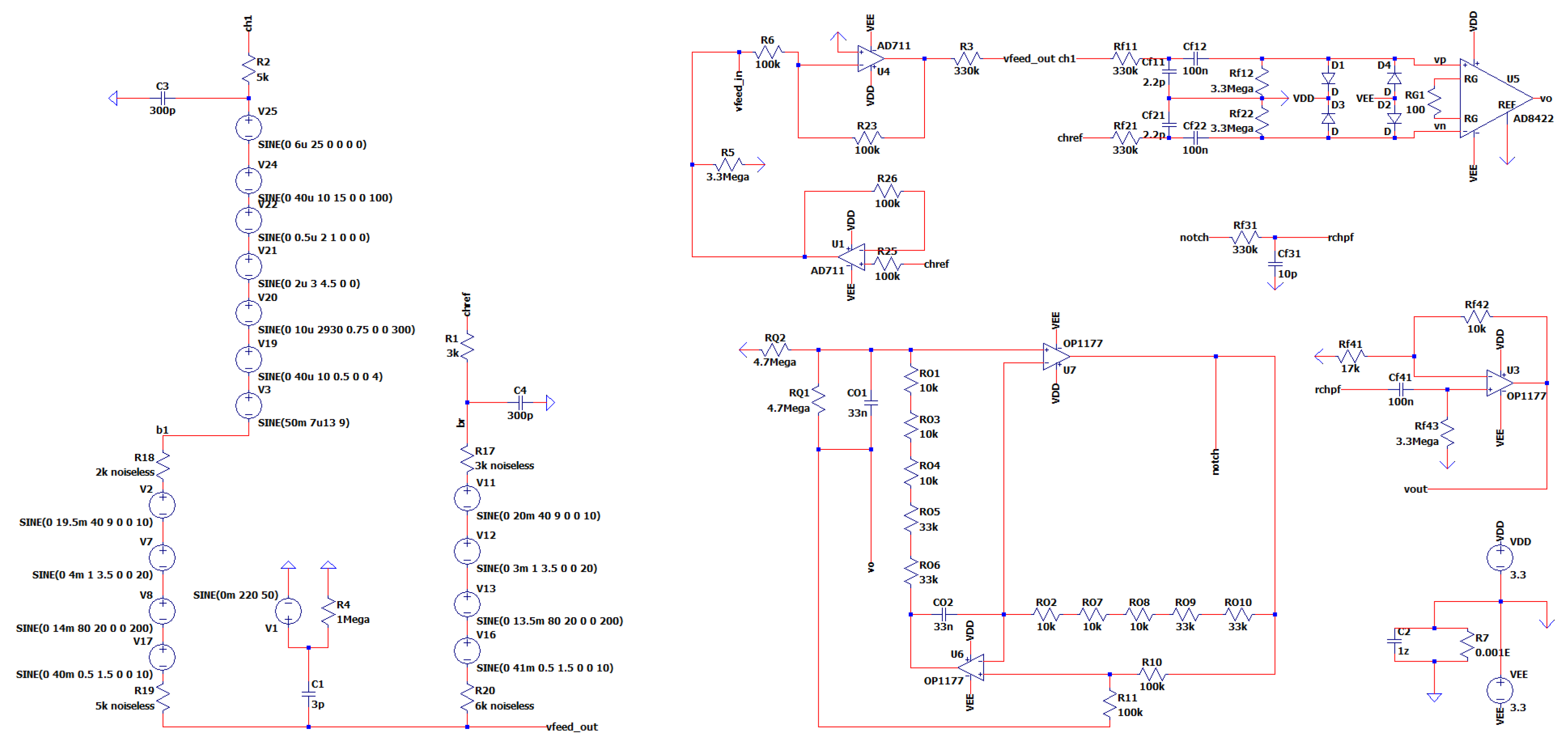

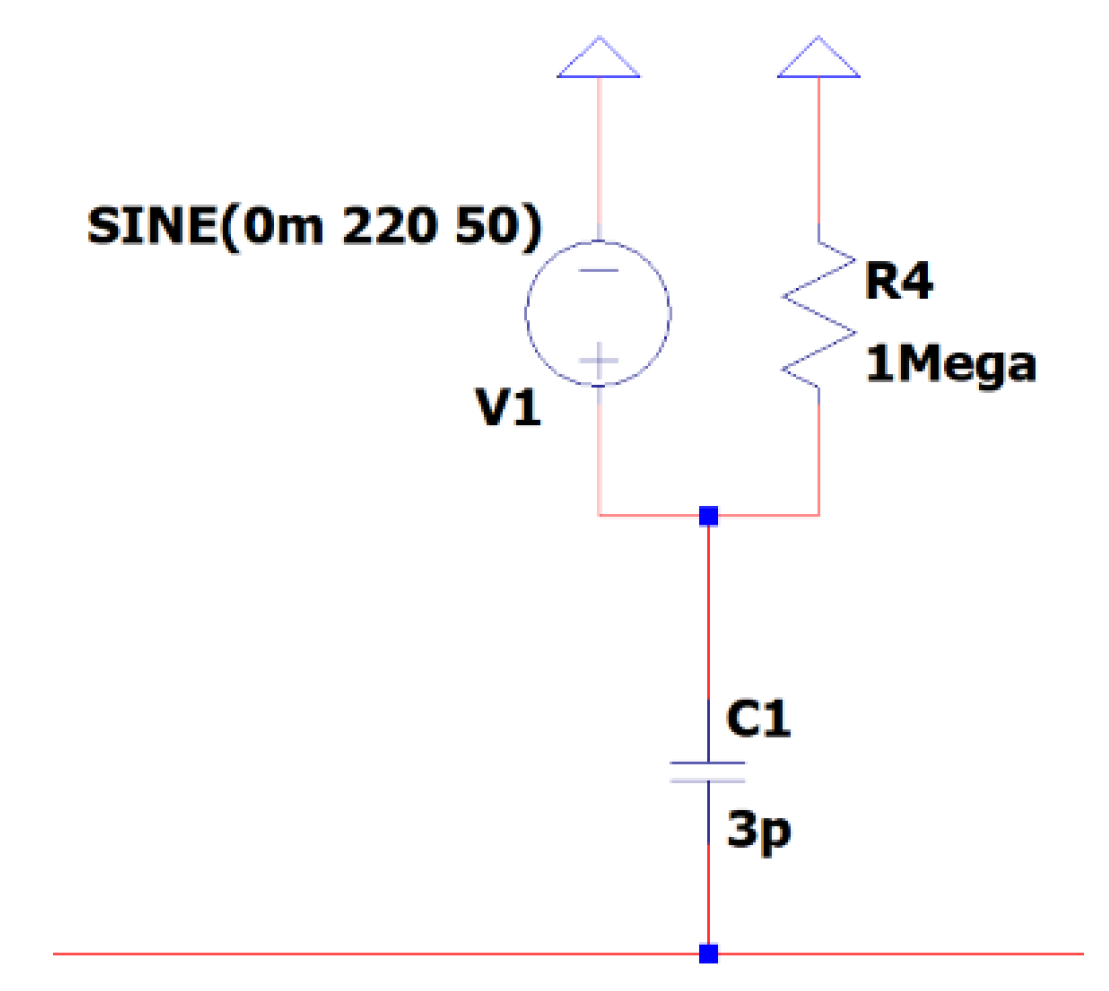

- Section 3.1, EEG Sub-Circuit Modeling the Electromagnetic Interference of Electric Grid with the Human Body: It presents the modeling of the electromagnetic interference of an electric grid with the human body and its application in designing the sub-circuit for replicating the voltage effect the adjacent electrical grids have on the human body.

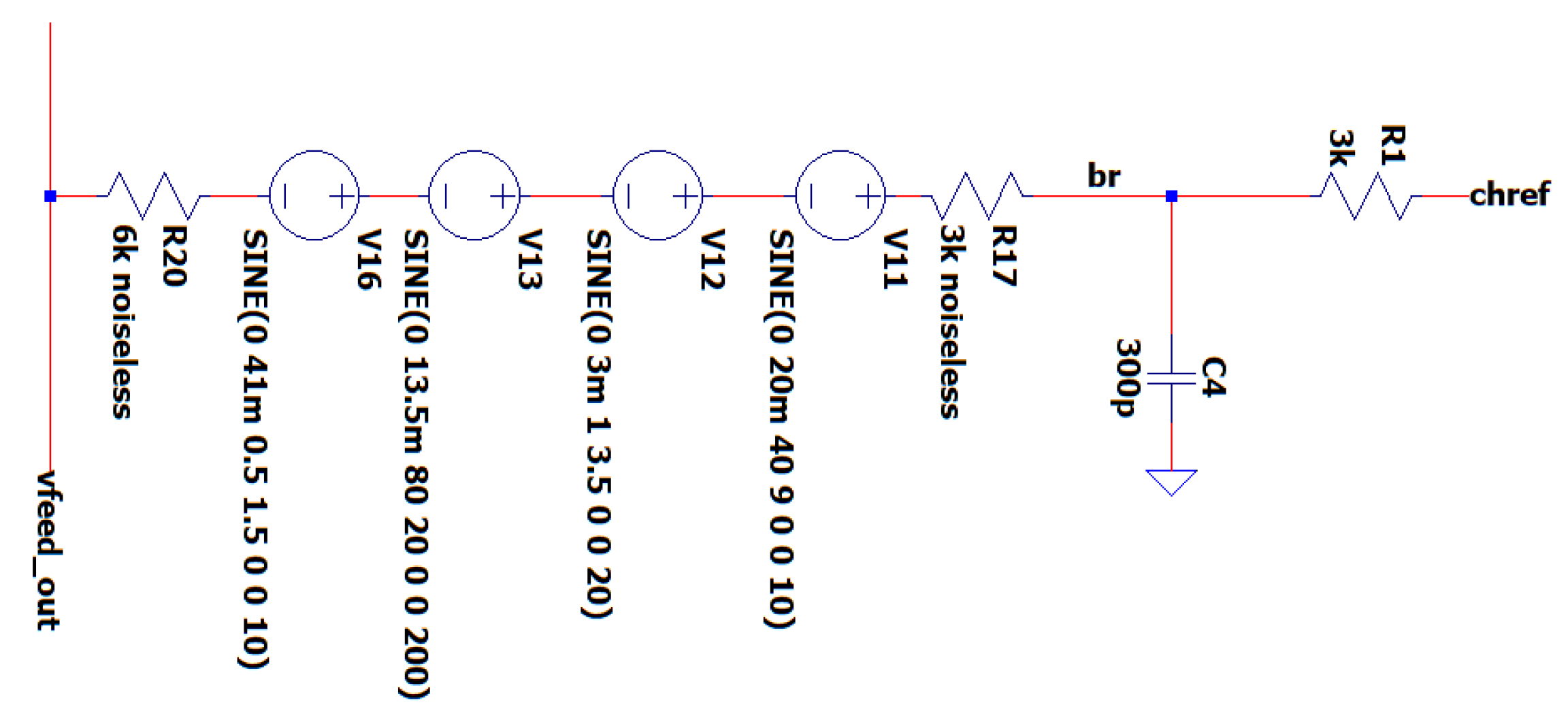

- Section 3.2, EEG Sub-circuit Modeling the Human Body Apart from the Brain and Earth: It describes the sub-circuit that simulates the physiological electrical circuits and muscle movement.

- Section 3.3, EEG sub-Circuit Modeling the Brain and the Electrode: It explains how the brain signal voltage could be simulated in any desired circuitry and how the electrode picks up the brain signals.

- Section 3.4, EEG Sub-Circuit Modeling the Battery Supply of the System: It details the design of the battery supply sub-circuit for the EEG circuitry so that the total overall EEG system may be both portable and yet remain very stable.

- Section 3.5, EEG Sub-Circuit Modeling the Driven Right Leg (DRL) Circuit: The DRL circuit function is to maintain signal integrity and user safety.

- Section 3.6, EEG Sub-Circuit Modeling the First Band-Pass Filter: It describes the role of the band-pass filter in the users’ protection and ensuring that there is always the accurate capture of the EEG signal.

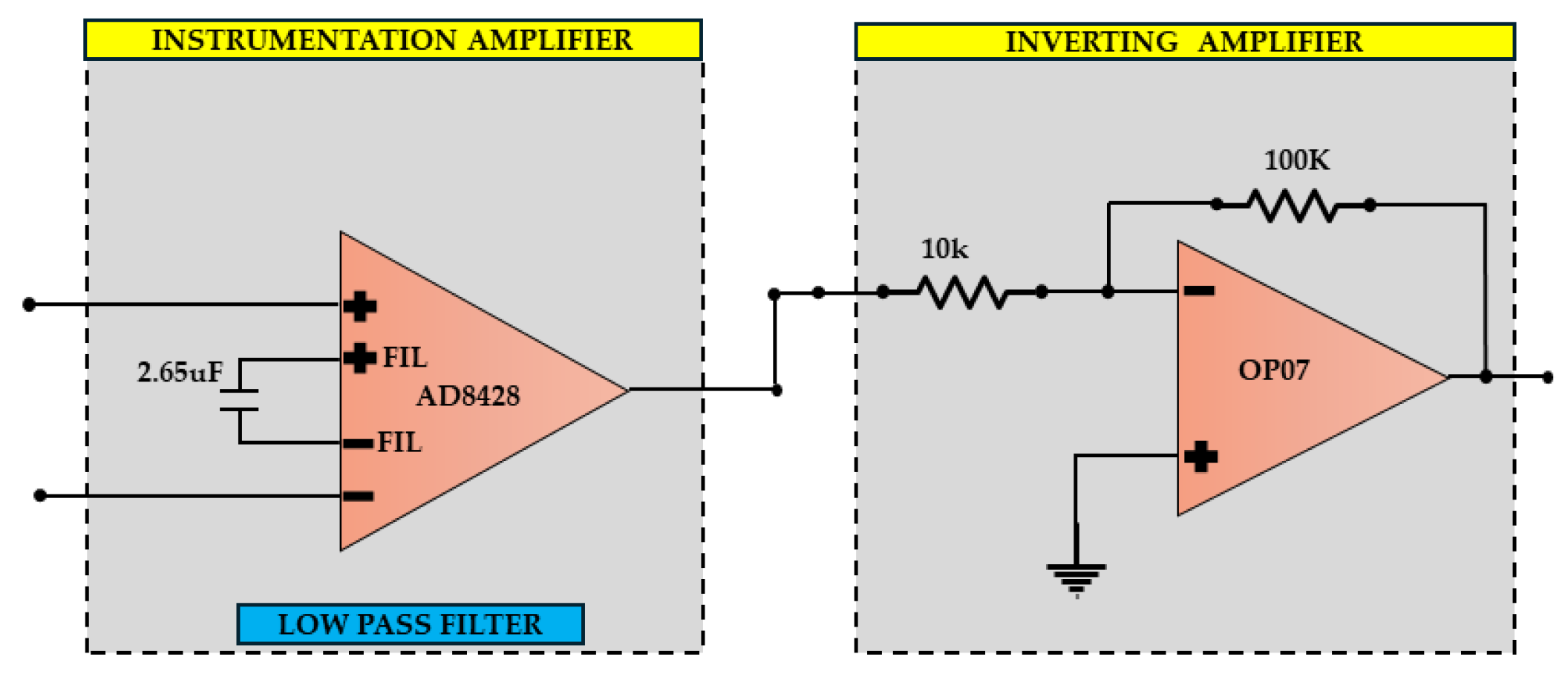

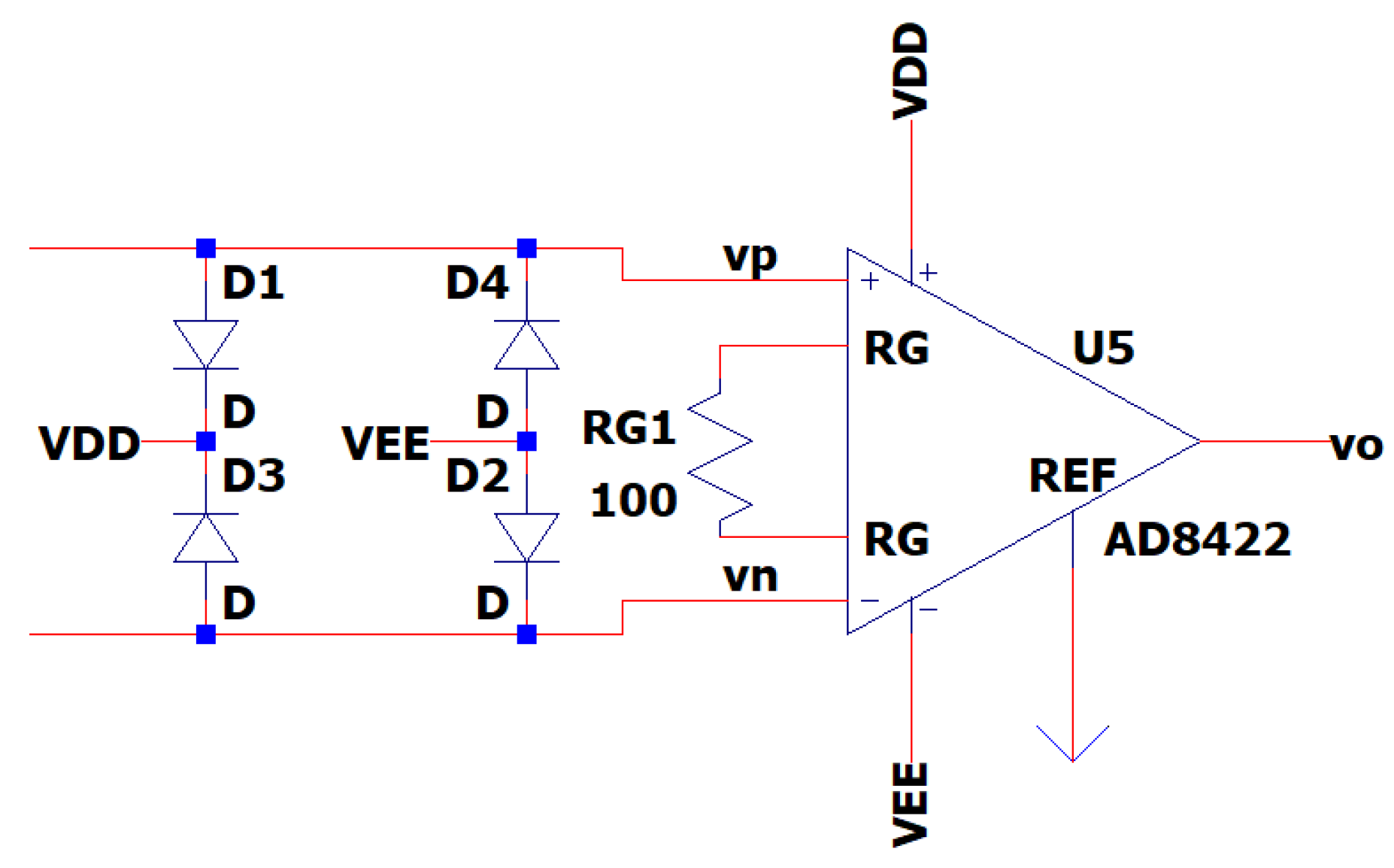

- Section 3.7, EEG Sub-Circuit Modeling the ESD Protection and the Instrumentation Amplifier: It will cover the addition of ESD protection and the details of the Instrumentation Amplifier in the EEG circuitry.

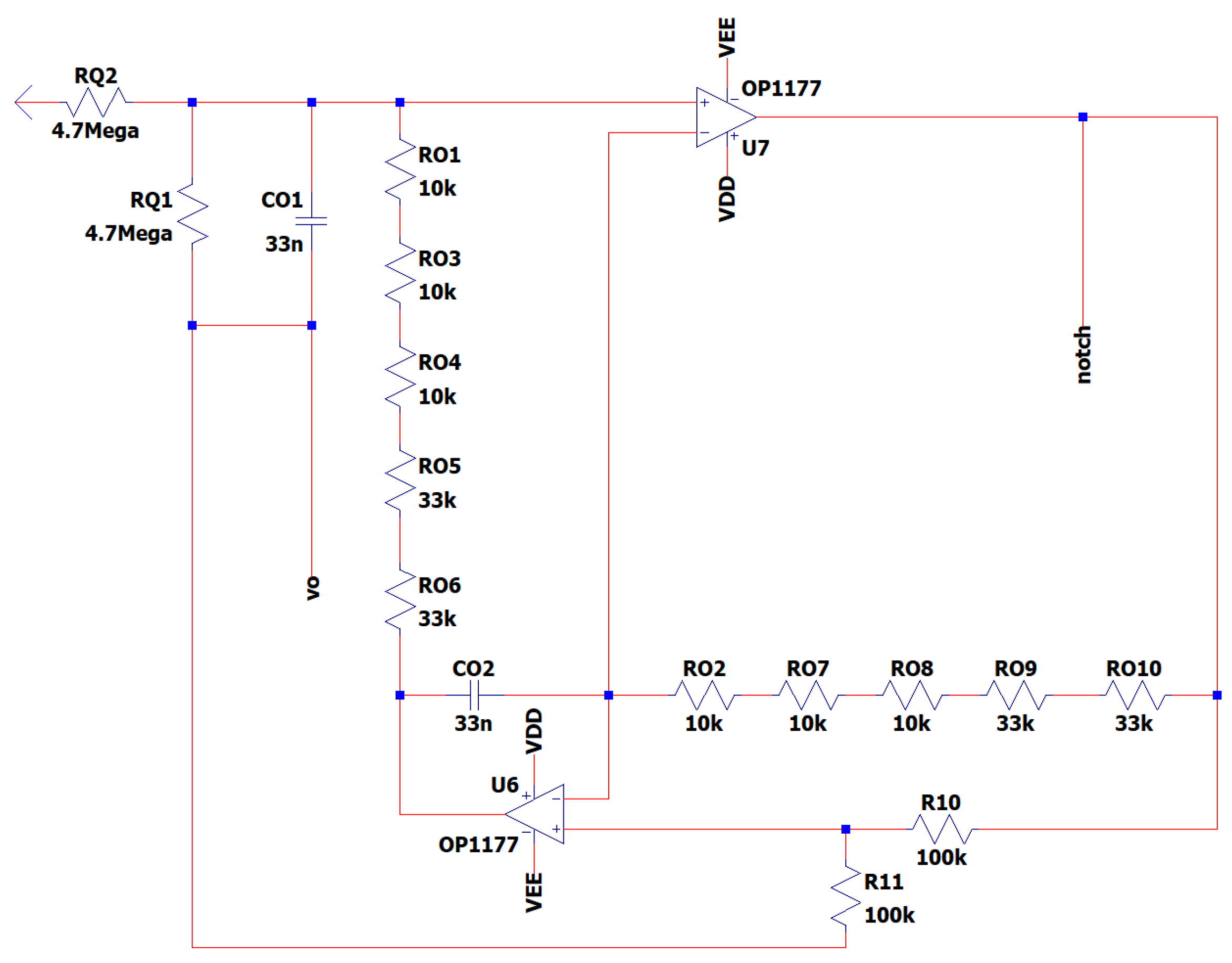

- Section 3.8, EEG Sub-Circuit Modeling the Fliedge Notch Filter 50Hz or 60Hz: It analyses how the notch filter will be designed so that the power grid interference is reduced to a minimum.

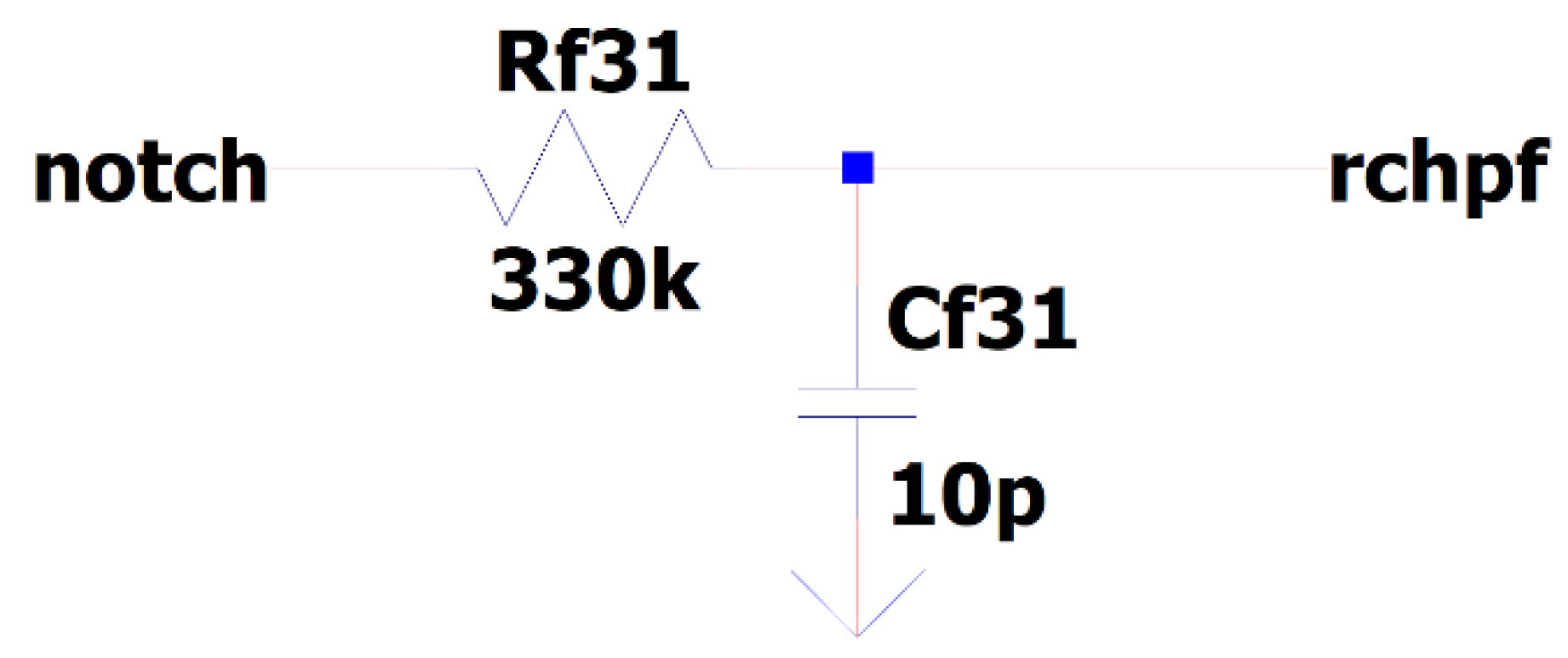

- Section 3.9, EEG Sub-Circuit Modeling the Second Low Pass Filter: It details of the second low pass filter design and cutoff frequency will be laid down in relation to an actual EEG signal processing system.

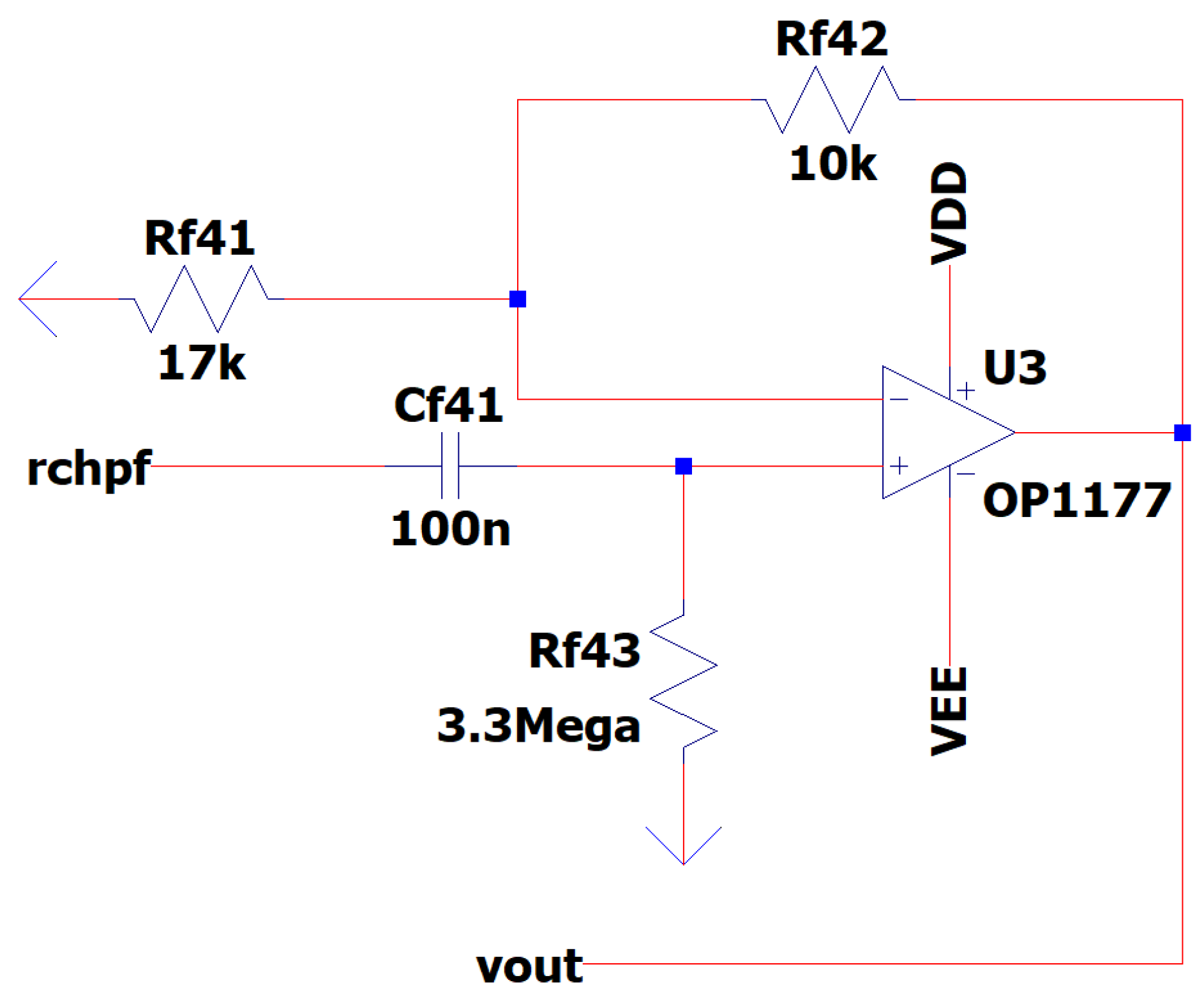

- Section 3.10, EEG Sub-Circuit Modeling the Second High Pass Filter before the Analog to Digital Conversion: It describes why, before the analog signal can be converted to digital, there is a need for a second high pass filter to make sure it does not degrade the quality of the signal.

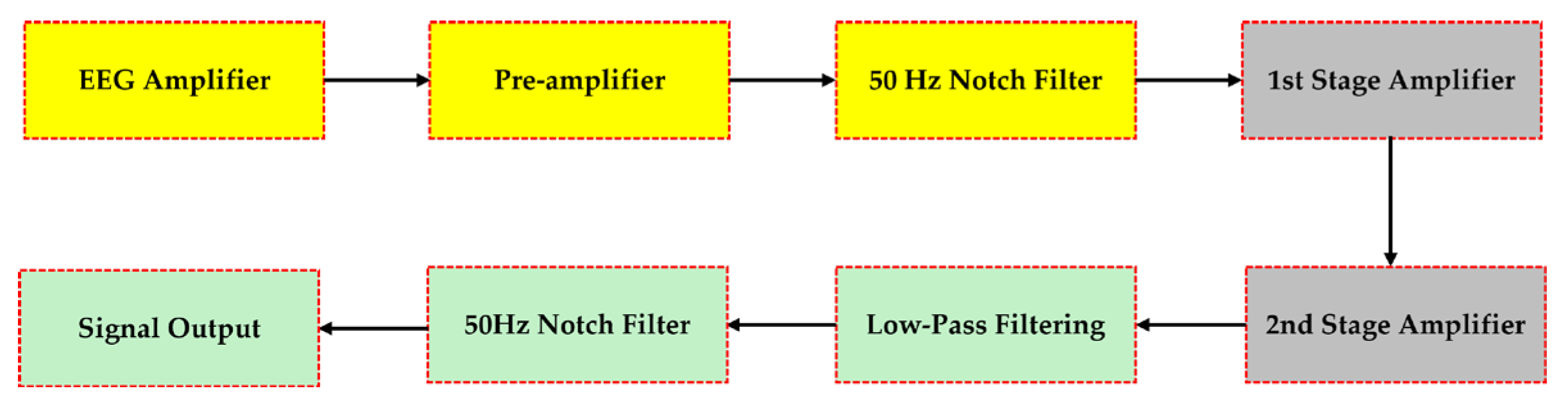

- Section 311, The Overall Novel EEG-B3VS7C1 Circuit Design: A general overview of the entire circuit design for EEG is presented, emphasizing features incorporated and intended performance outcomes.

- Section 4 (Simulation and Results: Comprehensive Analysis) is presented with the objective to compare the theoretical values with the simulated values in a real-world scenario for the given circuit design EEGB3VS7C1. The circuit’s performance is simulated into two of the commonest EEG measurement scenarios: the 50Hz and 60Hz power grid environments that exist outside the shielded lab conditions. This section contains the following sub-sections:

- Section 4.1, Simulation of Novel EEGB3VS7C1 Circuit Design: It provides one example of the simulation of the electronic behavior of the EEGB3VS7C1 circuit model and its assessment against the authors’ pre-defined circuit requirements, which included bandwidth, CMRR, notch depth of the notch filter, and signal integrity of the overall signal in a muscle movement environment. This sub-section contains information about the Simulation in a 50 Hz Electrical Grid Environment, as well as the Simulation in a 60 Hz Electrical Grid Environment.

- Section 4.2, Comparative Analysis of the Simulated EEGB3VS7C1 with Case Studies "1", "2", "3": The novel circuit is compared to the case studies "1", "2", and "3". Specifically, quantities and characteristics CMRR, Bandwidth, Signal Quality and Notch Depth are the bases of comparison.

- Section 5 (Discussion) discusses the practical implications, potential limitations, and future perspectives of the proposed EEG circuit design. Its sub-sections are:

- Section 5.1, Practical Considerations: It considers the practical limitations of the EEG circuit implementation in real-world scenarios.

- Section 5.2, Future Perspectives and Trends: It lists the possible improvement angles for the proposed circuit and its potential applications in BCI Systems.

- Section 6 (Conclusions) summarizes the entire article.

- This study is accompanied by the Appendix A: it is the provision of an in-depth detail on many more EEG applications neither presented in detail in Section 2 nor used for comparisons in Section 4.

- Lastly, a list of the references and relevant bibliographies used in the present study to validate the findings.

2. Related Works: EEG Circuit Design Analog Front-End Architectures

2.1. Low-Cost Circuit Design of EEG Analog Front ends: Case ’’1’’

2.1.1. Description of Topology and Connectivity

2.1.2. Comparative Evaluation with EEG Generic Circuit Design

2.1.3. Requirements and Specifications in the EEG Circuit: Case ’’1’’

2.1.4. Usage-Centric Justification for Design Differentiation: Case ’’1’’

2.1.5. Simulation - Experimental Results: Case ’’1’’

2.2. Battery-Powered, Low-Noise Amplifier Circuit Design of EEG Analog Front ends: Case ’’2’

2.2.1. Description of Topology and Connectivity

2.2.2. Comparative Evaluation with EEG Generic Circuit Design

2.2.3. Requirements and Specifications in EEG Circuit: Case ’’2’’

2.2.4. Usage-Centric Justification for Design Differentiation: Case ’’2’’

2.2.5. Simulation - Experimental Results: Case ’’2’’

2.3. Double Notch Filter Circuit Design of EEG Analog Front ends: Case ’’3’’

2.3.1. Description of Topology and Connectivity

2.3.2. Comparative Evaluation with EEG Generic Circuit Design

2.3.3. Requirements and Specifications in EEG Circuit: Case ’’3’’

2.3.4. Usage-Centric Justification for Design Differentiation: Case ’’3’’

2.3.5. Simulation - Experimental Results: Case ’’3’’

3. Materials and Methods: A Novel Proposed EEG Analog Front End Circuit System

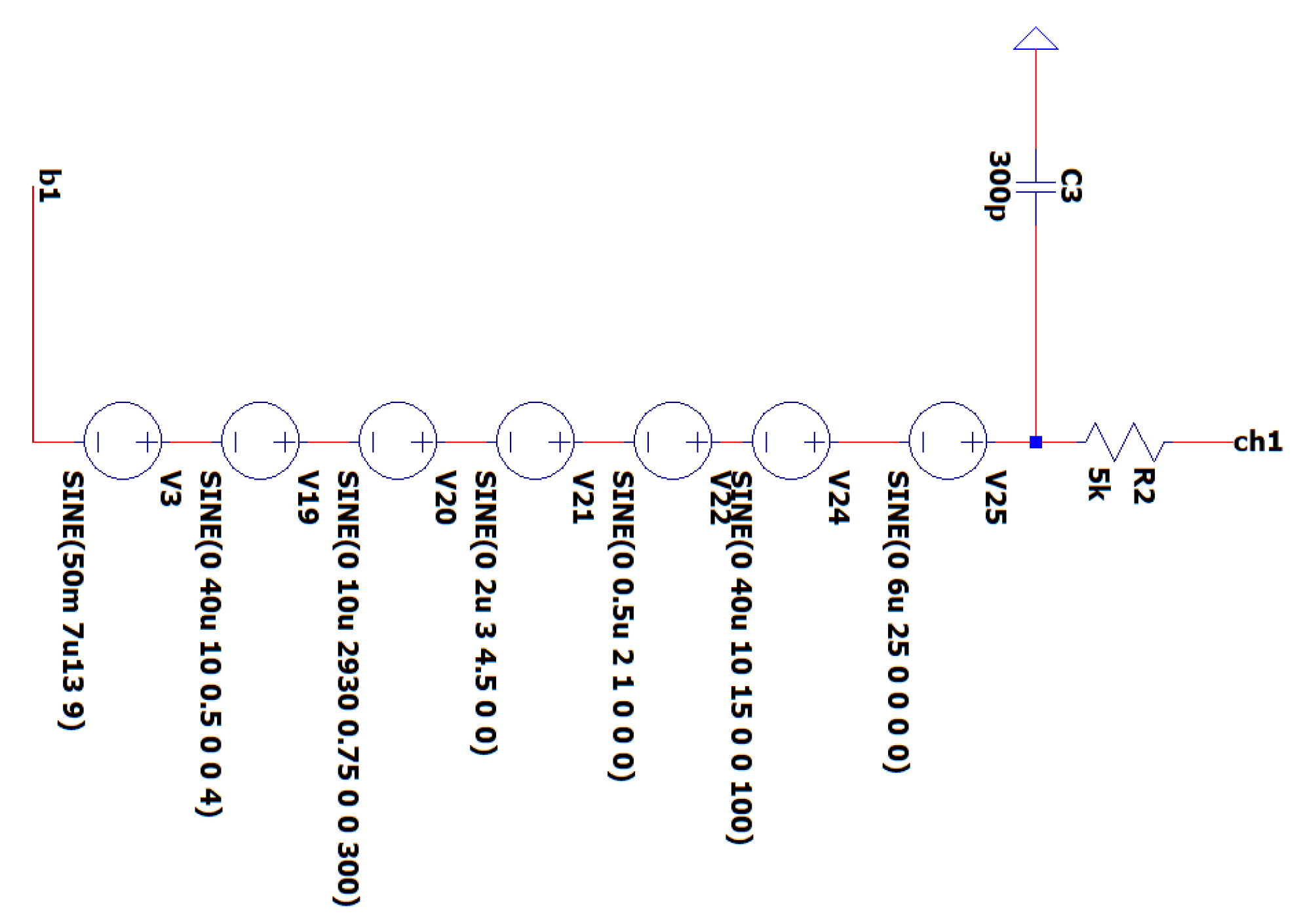

3.1. EEG Sub-Circuit Modeling the Electromagnetic Interference of Electric Grid with the Human Body

3.2. EEG Sub-circuit Modeling the Human Body Apart from the Brain and Earth

3.3. EEG sub-Circuit Modeling the Brain and the Electrode

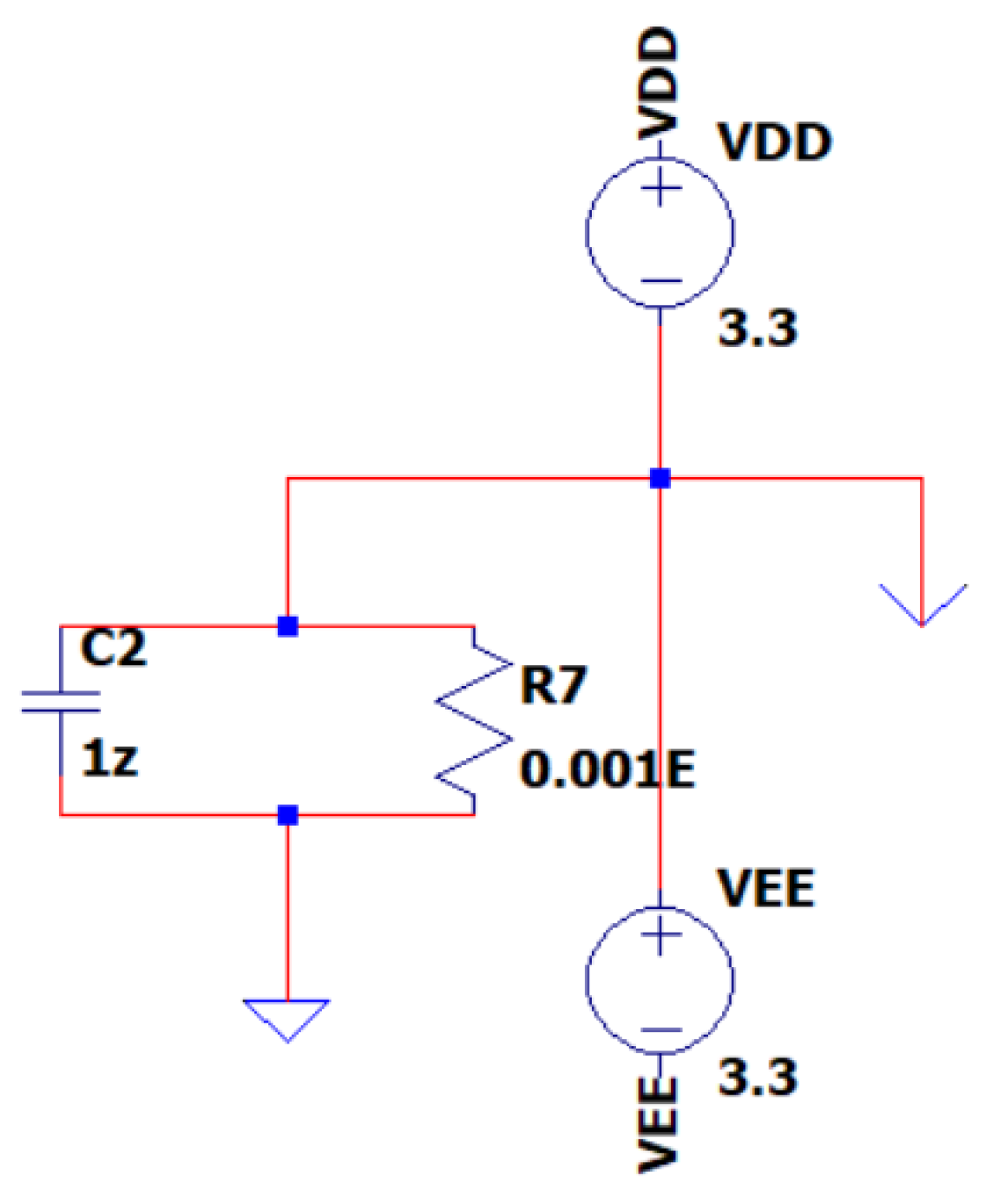

3.4. EEG Sub-Circuit Modeling the Battery Supply of the System

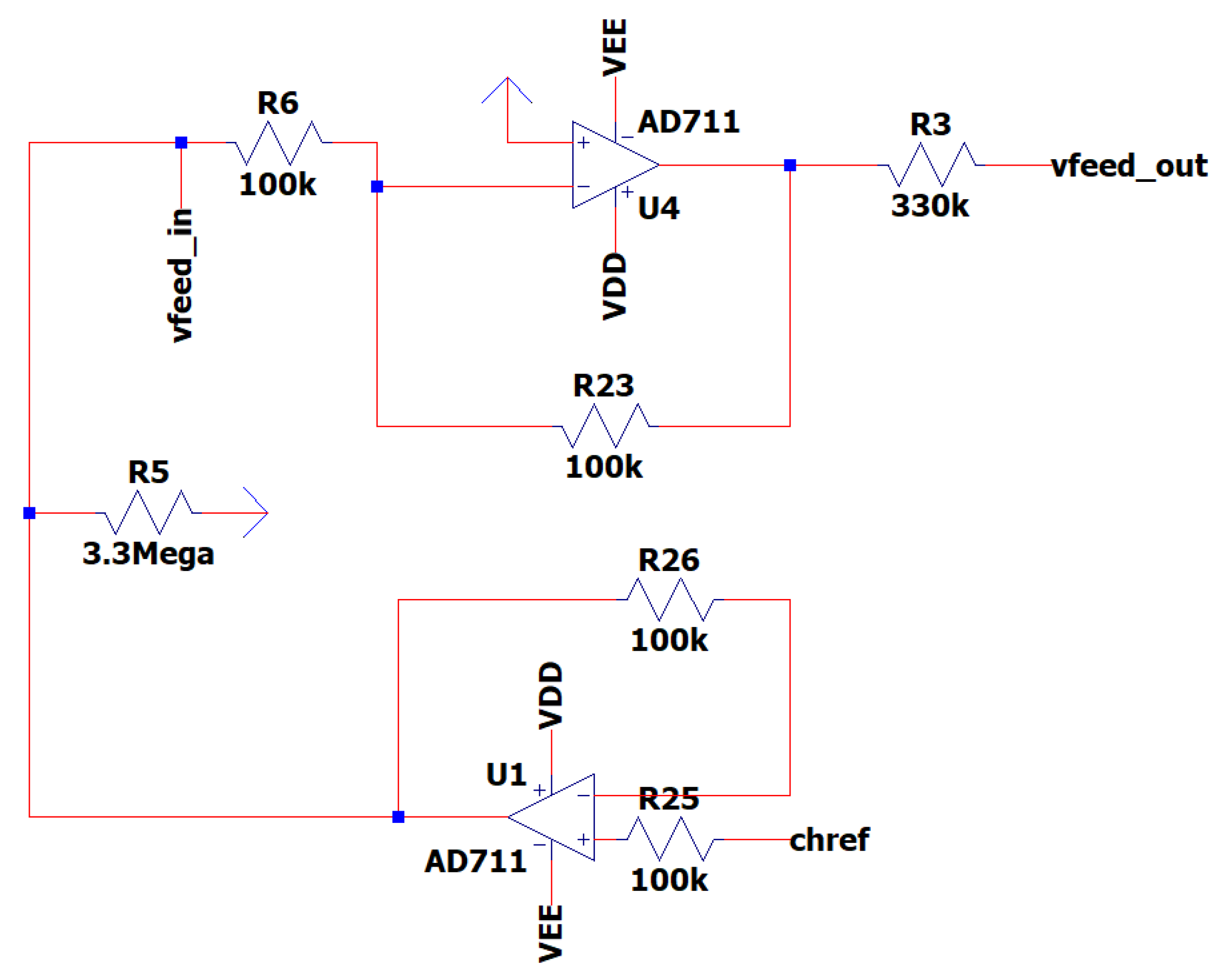

3.5. EEG Sub-Circuit Modeling the Driven Right Leg (DRL) Circuit

3.6. EEG Sub-Circuit Modeling the First Band-Pass Filter

3.7. EEG Sub-Circuit Modeling the ESD Protection and the Instrumentation Amplifier

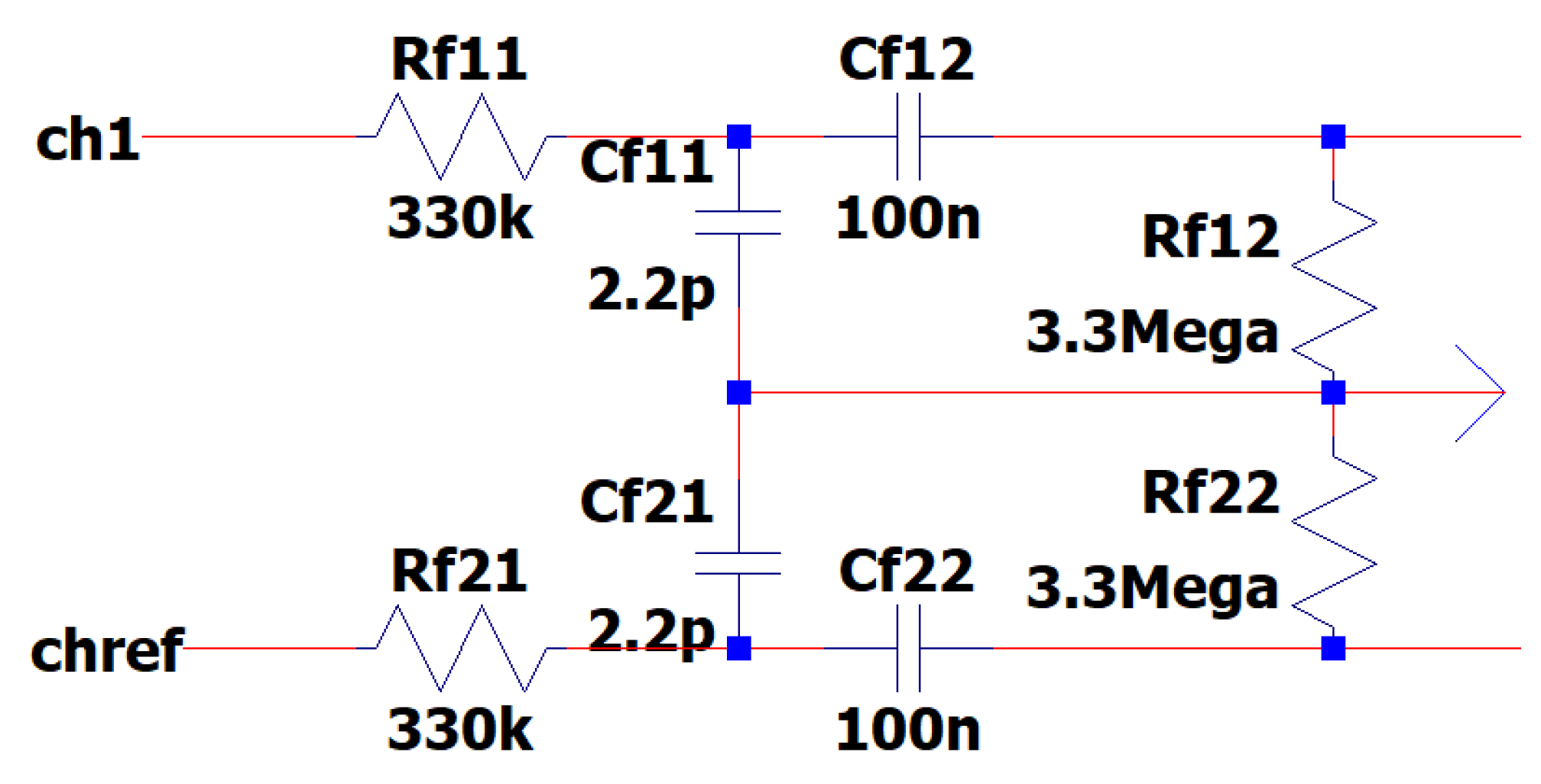

3.8. EEG Sub-Circuit Modeling the Fliedge Notch Filter 50Hz or 60Hz

3.9. EEG Sub-Circuit Modeling the Second Low Pass Filter

3.10. EEG Sub-Circuit Modeling the Second High Pass Filter before the Analog to Digital Conversion

3.11. The Overall Novel EEG-B3VS7C1 Circuit Design

- kB is the Boltzmann’s constant,

- T is absolute temperature in Kelvin in our case at room temperature (usually 25oC) and

- R is the real part of the band-pass filter’s impedance.

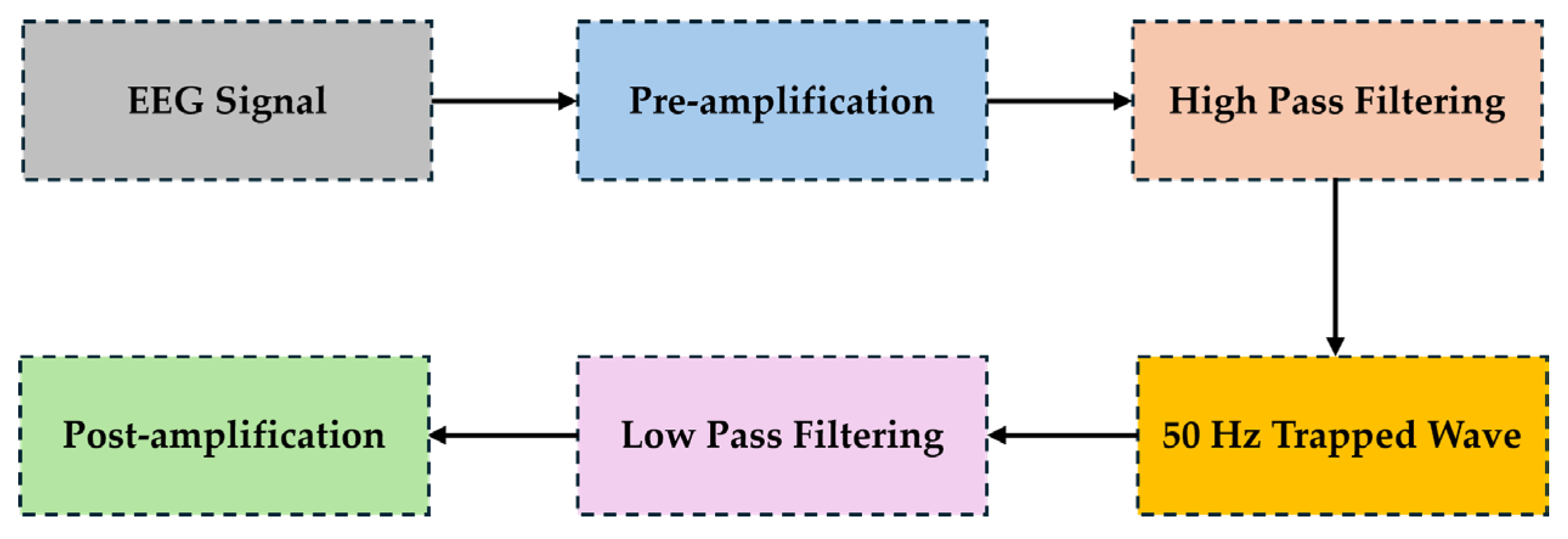

4. Simulation and Results: Comprehensive Analysis

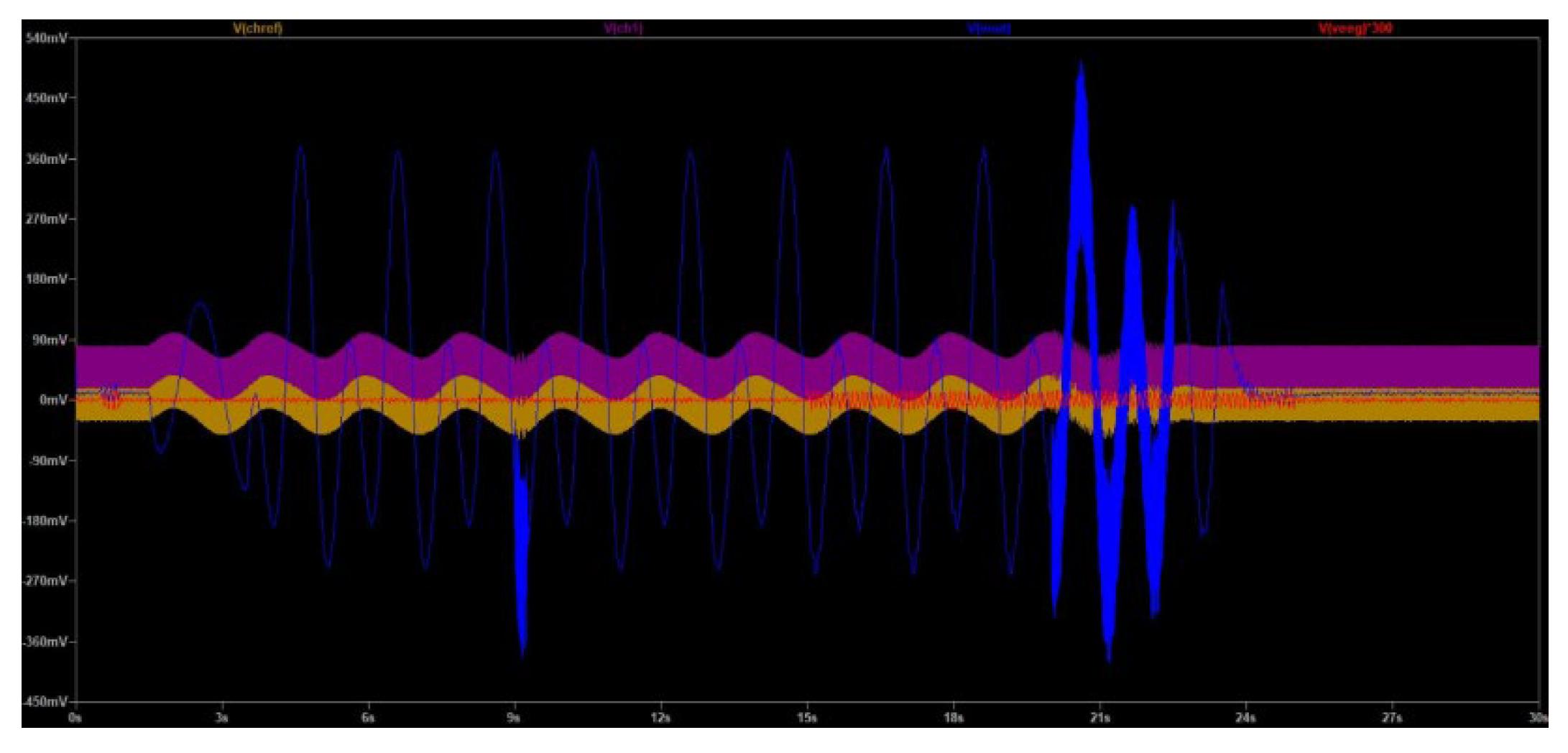

- Time domain to make a qualitative commenting in regard to CMRR, power consumption, gain, and noise level before the first amplification.

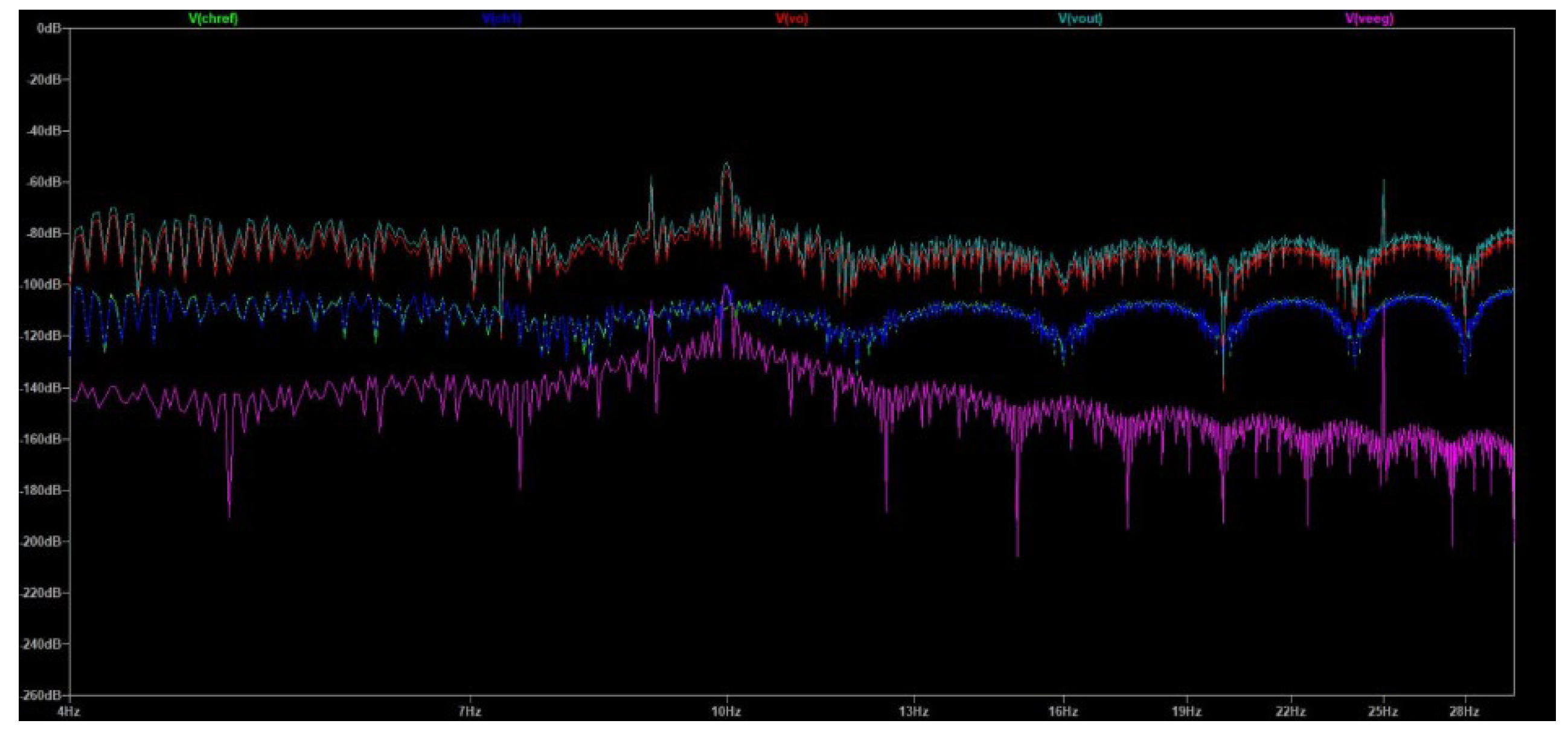

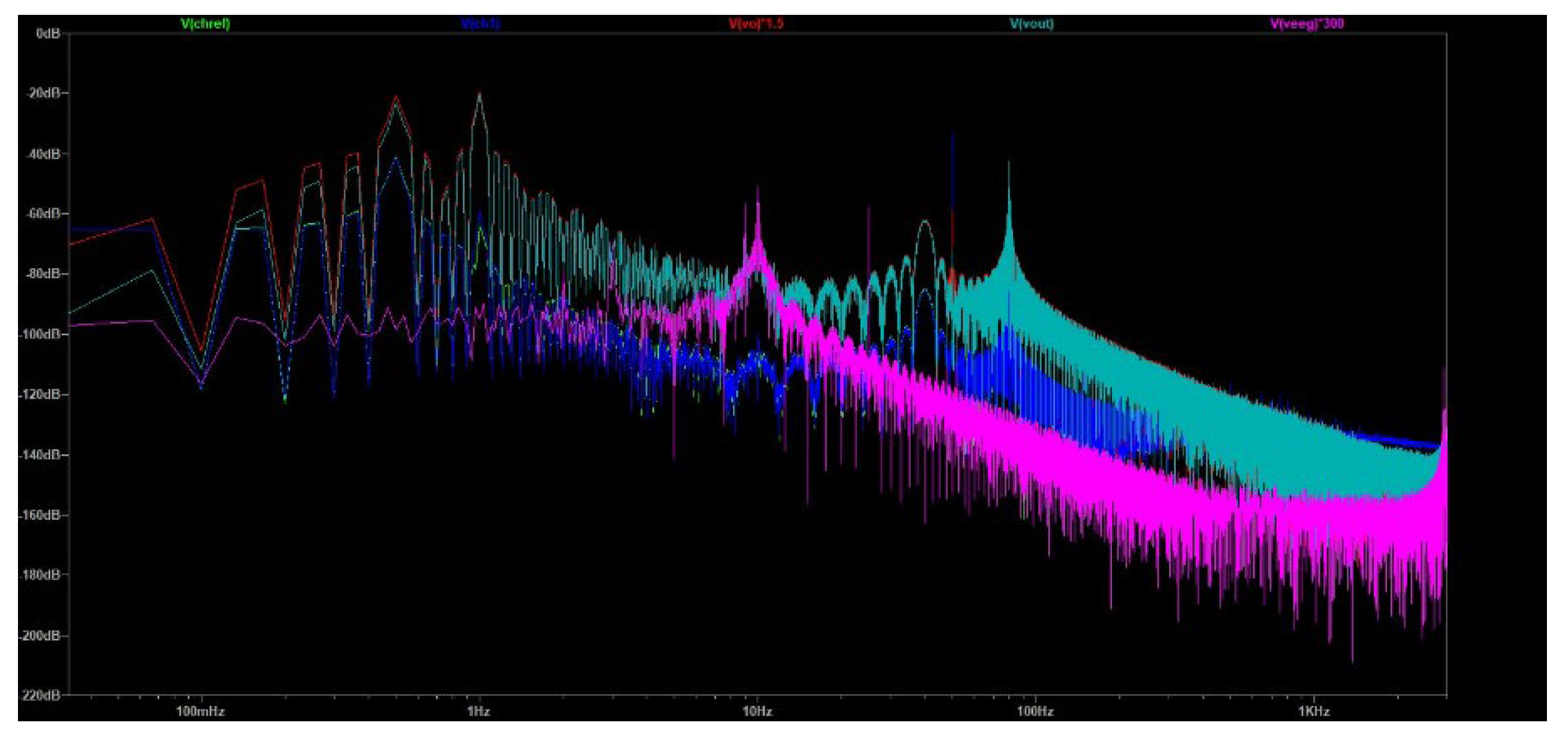

- Fourier frequency spectrum to validate if the information in the alpha, beta and theta wave bands is preserved.

- Fourier frequency spectrum and time domain to validate that the compound muscle movement artifacts are sufficiently suppressed.

4.1. Simulation of Novel EEGB3VS7C1 Circuit Design

4.1.1. Simulation in a 50 Hz Electrical Grid Environment

- Simulation at a 50 Hz Electrical Grid Environment in the Time Domain

- Simulation at 50 Hz Electrical Grid Environment at the Fourier’s Spectrum

4.1.2. Simulation in an Environment with an Electrical Grid with Frequency 60 Hz

4.2. Comparative Analysis of the Simulated EEG-B3VS7C2 with the Cases 1, 2, 3

5. Discussion

5.1. Observed Limitations of the Proposed EEG Circuit Design

5.2. Future Perspectives: Possible Updates and Real-World Applications of the Proposed EEG Circuit Design

6. Conclusions

Supplementary Materials

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Appendix A

| Feature | Description |

|---|---|

| Common Mode Rejection Ratio (CMRR) | The AD620 instrumentation amplifier used in the design has a high CMRR of 110 dB, crucial for minimizing noise and interference in EEG signals. |

| Signal Bandwidth/Frequency Range | Targets neonatal EEG signals, predominantly delta waves, with frequencies from 0.5 to 2 Hz, 100μV amplitude. |

| Gain | Total gain of 17776 V/V. ndividual stage gains:

|

| Filter Characteristics | High pass and low pass filters with cutoff frequencies of 0.16 Hz and 50 Hz, respectively to remove DC offset and power line interference |

| Feature | Description |

|---|---|

| Common Mode Rejection Ratio (CMRR) | High CMRR suitable for EEG applications |

| Signal Bandwidth | 0.5 to 40 Hz |

| Variable Gain | Between 100 and 7000 |

| Power Consumption | Low |

| Portability | Designed for portability |

| Components | Uses commercially available components |

| Cost | Cost-effective |

| Signal Quality Metrics | Detailed metrics not directly provided |

| Feature | Description |

|---|---|

| Common Mode Rejection Ratio (CMRR) | 102 dB, effective in reducing noise and interference from common-mode signal |

| Amplifier Gain | Variable, with options for 5000, 10000, 20000, or 30000 V/V |

| Pass-Band Frequency | Ranges from 0.12Hz to 35.4Hz, accommodating the typical frequency range of EEG signals |

| Input Impedance | 113MΩ, ensuring that the circuit does not significantly load the signal source, preserving signal integrity |

| Feature | Description |

|---|---|

| Common Mode Rejection Ratio (CMRR) | 100 dB for gains ≥ 100, aiming for effective common-mode noise rejection |

| Amplifier Gain | G≥100V/V |

| Modified High-Q Factor Active Twin-T Notch Filter |

60 Hz and a rejection level of -38 dB. |

| PCB Size | Less than 5.5 cm2 |

References

- Sanei, S.; Chambers, J.A. Fundamentals of EEG Signal Processing. EEG Signal Processing 2007, 35–12. [Google Scholar] [CrossRef]

- Tatum, W.O. Ambulatory EEG. In Handbook of EEG Interpretation. Springer Publishing Company 2021. [CrossRef]

- Benbadis, S.R.; Beniczky, S.; Bertram, E.; MacIver, S.; Moshé, S.L. The role of EEG in patients with suspected epilepsy. Epileptic Disorders 2020, 22, 143–155. [Google Scholar] [CrossRef] [PubMed]

- Rubiños, C.; Godoy, D.A. Electroencephalographic monitoring in the critically ill patient: What useful information can it contribute? Medicina Intensiva (English Edition) 2020, 44, 301–309. [Google Scholar] [CrossRef]

- Asadzadeh, S.; Yousefi Rezaii, T.; Beheshti, S.; Delpak, A.; Meshgini, S. A systematic review of EEG source localization techniques and their applications on diagnosis of brain abnormalities. Journal of Neuroscience Methods 2020, 339, 108740. [Google Scholar] [CrossRef] [PubMed]

- Dhar, P.; & Garg, V.K. Brain-Related Diseases and Role of Electroencephalography (EEG) in Diagnosing Brain Disorders. Lecture Notes in Networks and Systems, Springer Singapore 2020, 317–326. [CrossRef]

- Ullah, H.; Mahmud, S.; Chowdhury, R.H. Identification of Brain disorders by Sub-band Decomposition of EEG signals and Measurement of Signal to Noise Ratio. Indonesian Journal of Electrical Engineering and Computer Science 2016, 4, 568. [Google Scholar] [CrossRef]

- Iscan, Z.; Dokur, Z.; Demiralp, T. Classification of electroencephalogram signals with combined time and frequency features. Expert Systems with Applications 2011, 38, 10499–10505. [Google Scholar] [CrossRef]

- Siuly, S.; Li, Y.; Zhang, Y. Electroencephalogram (EEG) and Its Background. EEG Signal Analysis and Classification 2016, 3–21. [Google Scholar] [CrossRef]

- Usakli, A.B. Improvement of EEG Signal Acquisition: An Electrical Aspect for State of the Art of Front End. Computational Intelligence and Neuroscience 2010, 1–7. [Google Scholar] [CrossRef]

- Elsayed, N.; Saad, Z.; Bayoumi, M. Brain Computer Interface: EEG Signal Preprocessing Issues and Solutions. International Journal of Computer Applications 2017, 169, 12–16. [Google Scholar] [CrossRef]

- Alkhorshid, D.R.; Molaeezadeh, S.F.; Alkhorshid, M.R. Analysis: Electroencephalography Acquisition System: Analog Design. Biomedical Instrumentation & Technology 2020, 54, 346–351. [CrossRef]

- Cohen, M.X. Where Does EEG Come From and What Does It Mean? Trends in Neurosciences 2017, 40, 208–218. [Google Scholar] [CrossRef] [PubMed]

- Tankisi, H.; Burke, D.; Cui, L.; de Carvalho, M.; Kuwabara, S.; Nandedkar, S.D.; Rutkove, S.; Stålberg, E.; van Putten, M.J.A.M.; Fuglsang-Frederiksen, A. Standards of instrumentation of EMG. Clinical Neurophysiology 2020, 131, 243–258. [Google Scholar] [CrossRef] [PubMed]

- Vanhatalo, S.; Voipio, J.; Kaila, K. Full-band EEG (FbEEG): an emerging standard in electroencephalography. Clinical Neurophysiology 2005, 116(1), 1–8. [Google Scholar] [CrossRef] [PubMed]

- Hari, R.; Parkkonen, L.; Nangini, C. The brain in time: insights from neuromagnetic recordings. Annals of the New York Academy of Sciences 2010, 1191, 89–109. [Google Scholar] [CrossRef] [PubMed]

- Sullivan, T.J.; Deiss, S.R.; Cauwenberghs, G. A Low-Noise, Non-Contact EEG/ECG Sensor. In Proceeding of IEEE Biomedical Circuits and Systems Conference, Nov. 2007. [Google Scholar] [CrossRef]

- Scheer, H.J.; Sander, T.; Trahms, L. The influence of amplifier, interface and biological noise on signal quality in high-resolution EEG recordings. Physiological Measurement 2005, 27, 109–117. [Google Scholar] [CrossRef] [PubMed]

- Jobert, M.; Wilson, F.J.; Ruigt, G.S.F.; Brunovsky, M.; Prichep, L.S.; Drinkenburg, W.H.I.M. Guidelines for the Recording and Evaluation of Pharmaco-EEG Data in Man: The International Pharmaco-EEG Society (IPEG). Neuropsychobiology 2012, 66, 201–220. [Google Scholar] [CrossRef] [PubMed]

- Wasade, V.S.; Spanaki, M.V. Understanding Epilepsy. Cambridge University Press, 2019. [CrossRef]

- Usakli, A.B. Improvement of EEG Signal Acquisition: An Electrical Aspect for State of the Art of Front End. Computational Intelligence and Neuroscience 2010, 1–7. [Google Scholar] [CrossRef]

- Gardella, P.J.; Baez, E.; Cesaretti, J.M. (2020). Design of ESD protections for ECG applications. In Proceeding of Conference on Electronics (CAE), Argentine, Feb 2020. [CrossRef]

- Kumar, S.C.P.; Chandrasekar, A.; Nagaraj, A.; Gupta, P.; Sekhar, S. Design of an ElectroEncephaloGram (EEG) amplification circuit for neonates. In Proceeding of International Conference on Communication and Signal Processing (ICCSP), Apr. 2016. [CrossRef]

- Whitchurch, A.K.; Abraham, J.K.; Lonkar, M.A.; Varadan, V.K. Design of a Compact Amplifier and Signal Conditioning Module for Wireless EEG Monitoring. In Proceeding of IEEE Region 5 Technical Conference, Apr. 2007. [CrossRef]

- Zhang, X.; Zhang, Z. Design on Sampling Circuit of EEG Signal Based on AT89C2051 Single-Chip. In Proceeding of Fourth International Conference on Innovative Computing, Information and Control (ICICIC), Dec. 2009. [CrossRef]

- Salahuddin Morsalin, S.M.; Lai, S.-C. Front-end circuit design for electroencephalography (EEG) signal. In Proceeding of 2nd International Conference on Computing, Analytics and Networks (ICAN), Indo – Taiwan, Feb 2020. [CrossRef]

- Xu, X.; Wang, P. Low-Cost Circuit Design for EEG Signal Amplification and Extraction. In Proceeding of IEEE Asia-Pacific Conference on Image Processing, Electronics and Computers (IPEC), Apr. 20212021. [CrossRef]

- Choudhary, S.K.; Bera, T.K. Designing of Battery-Based Low Noise Electroencephalography (EEG) Amplifier for Brain Signal Monitoring: A Simulation Study. In Proceeding of IEEE 6th International Conference on Condition Assessment Techniques in Electrical Systems (CATCON), 422-426, Durgapur, India, 2022). [CrossRef]

- Analog Devices, Inc. AD8428: High Gain, High Voltage Instrumentation Amplifier. Data Sheet. Available online: https://www.analog.com/media/en/technical-documentation/data-sheets/ad8428.pdf (accessed on 10 Feb. 2024).

- Yuge, Sun.; Ning, Ye.; Feng, Pan. A novel design of EEG signal amplifier. In Proceeding of 24th Chinese Control and Decision Conference (CCDC), May 2012. [CrossRef]

- Jobert, M.; Wilson, F.J.; Ruigt, G.S.F.; Brunovsky, M.; Prichep, L.S.; Drinkenburg, W.H.I.M. Guidelines for the Recording and Evaluation of Pharmaco-EEG Data in Man: The International Pharmaco-EEG Society (IPEG). Neuropsychobiology 2012, 66, 201–220. [Google Scholar] [CrossRef] [PubMed]

- Alizadeh-Taheri, B.; Smith, R.L.; Knight, R.T. An Active, Microfabricated, Scalp Electrode-array For EEG Recording. In Proceeding of the International Solid-State Sensors and Actuators Conference - TRANSDUCERS ’95. [CrossRef]

- Zhang, L.; Guo, X.; Wu, X.; Zhou, B. Low-cost circuit design of EEG signal acquisition for the brain-computer interface system. In Proceeding of 6th International Conference on Biomedical Engineering and Informatics, Dec. 2013. [CrossRef]

- Analog Devices, Inc. AD8422: 1.8 nV/√Hz, Rail-to-Rail, Low Power Instrumentation Amplifier. Data Sheet. Available online: https://www.analog.com/media/en/technical-documentation/data-sheets/ad8422.pdf. (accessed on 10 Feb. 2024).

- Zumbahlen, H. Analog Filters. Linear Circuit Design Handbook, H. Zumbahlen, Ed. Burlington: Newnes, 2008, 581–679. [CrossRef]

- Wang, J.; Tang, L.; E Bronlund, J. Surface EMG Signal Amplification and Filtering. International Journal of Computer Applications 2013, 82, 15–22. [Google Scholar] [CrossRef]

- Texas Instruments, INA333 Low-Power, Precision Instrumentation Amplifier. Available online: https://www.ti.com/lit/ds/symlink/ina333.pdf (accessed on 12 Feb. 2024).

| Frequency Band | Significance | Key Topics |

|---|---|---|

| Delta (0.5-4 Hz) | Deep Sleep, Unconsciousness | Basics and Beyond, Significance in Sleep and Memory, Methods, and Applications |

| Theta (4-8 Hz) | Creativity, Meditation, Drowsiness | Bridging Consciousness, Thalamic Origins, Practical Insights |

| Alpha (8-13 Hz) | Relaxation, Calmness, Decreased Attention | Indicators of Visual Activation, Enhancing Techniques and Benefits |

| Beta (13-30 Hz) | Active Thinking, Focus, Anxiety | Association with Alertness, Analysis to Application |

| Gamma (30-100 Hz) | Higher Mental Activity, Perception, Consciousness |

Cognitive Functions, Exploring High-Frequency Bands |

| Type of Noise | Frequency Range | Source/Characteristics | Impact on EEG Signal | Mitigation Measures |

|---|---|---|---|---|

| Hardware Noise (DC) | 0 Hz (DC) | Originates from wiring and electrical components of the recording system | Values up to a few μV | Use of special gear for noise reduction/isolation |

| Muscle Noise | 0-200 Hz (1-50 Hz most impactful) |

Caused by muscle activity, including minor movements like eye blinking |

Values may exceed 100 mV |

Careful electrode installation, skilled operators for reduction |

| Motion, Breath, Sweat and Cardiac Noise | 0-1.2 Hz | Due to normal physical activities |

Values may reach 10-80 μV |

Proper installation and setup |

| Eye Motion & Electromagnetic Field Noise | 0-16 Hz | Eye motion and intensity of electromagnetic fields | Values between 50-100 μV |

Correct electrode placement, skilled operators |

| Electromagnetic Interference (EMI) & Circuit Noise | 50 Hz (e.g. Greece), 60 Hz (e.g. USA) |

From electrical power lines and nearby electronic devices | Significant distortion possible |

Use of special filters for isolation |

| Category | Subcomponent | Function Description |

|---|---|---|

| Filter | Notch Filter | Eliminates power line interference, typically at 50 or 60 Hz. |

| Anti-Aliasing Filter | Prevents aliasing by removing high-frequency components before analog-to-digital conversion. | |

| High Pass Filter | Removes low-frequency components, typically below 0.1 Hz. | |

| Low Pass Filter | Cuts off frequencies higher than a certain threshold to remove high-frequency noise. | |

| Circuit | Chopper Circuit | Reduces low-frequency noise and drift in DC amplifiers by modulating and demodulating the input signal. |

| ESD Protection Circuit | Protects sensitive EEG electronics from static electricity. | |

| Amplifier | Operational Amplifier (Op-Amp) |

Amplifies the EEG signal with high gain and stability. |

| Programmable Gain Amplifier | Allows for adjustment of the amplification level of the EEG signal. |

|

| Instrumentation Amplifier with ntegrated Filter |

Provides high input impedance, and low noise, and includes integrated filters for signal conditioning. | |

| Other Subcomponents | Analog Mux (Multiplexer) | Selects one of several input signals and forwards it into a single line in multi-channel EEG systems. |

| Analog to Digital Converter (ADC) | Converts the analog EEG signal into a digital format for processing and analysis. |

|

| Drive Right Leg Circuit | Reduces common-mode interference in biopotential amplifiers. |

| Aspect | Medical-Grade EEG | Research-Grade EEG |

|---|---|---|

| Accuracy and Resolution | Higher accuracy and resolution for diagnostic purposes | Slightly lower resolution, suitable for studying brain patterns |

| Number of Electrodes | Higher number, standardized layouts (e.g., 10-20 system) |

Fewer electrodes, focusing on specific brain regions |

| Signal Quality and Noise Reduction | Advanced noise reduction for highly accurate readings | Noise reduction present, but may prioritize flexibility in analysis |

| Regulatory Compliance and Certification | Must meet strict regulatory standards (e.g., FDA approval) |

Not subjected to the same level of regulatory scrutiny |

| Durability and Robustness | Designed for frequent and sustained use, more durable | May not be as durable, focuses on flexibility for research |

| Common Mode Rejection Ratio (CMRR) | Circuit Bandwidth | Signal Quality | Common Mode Rejection Ratio (CMRR) |

|---|---|---|---|

| >120 dB | 0.3 to 40 Hz |

|

|

| Common Mode Rejection Ratio (CMRR) | Circuit Bandwidth | Signal Quality | Common Mode Rejection Ratio (CMRR) |

|---|---|---|---|

| 140 dB | 3.5 MHz |

|

|

| Common Mode Rejection Ratio (CMRR) | Circuit Bandwidth | Signal Quality | Common Mode Rejection Ratio (CMRR) |

|---|---|---|---|

| Estimated at 110 dB | 0.5 to 33.86 Hz |

|

|

| Common Mode Rejection Ratio (CMRR) | Circuit Bandwidth | Signal Quality | Common Mode Rejection Ratio (CMRR) |

|---|---|---|---|

| Greater than 90 dB | 0.5 Hz to 20 kHz |

|

|

| Requirements/ Specifications | Case ‘’1’’ | Case ‘’2’’ | Case ‘’3’’ | Proposed Circuit EEG Design |

|---|---|---|---|---|

| Common Mode Rejection Ratio (CMRR) | >120 dB | 140 dB | Estimated at 110 dB | Greater than 90 dB below 110Hz |

| Circuit Bandwidth | 0.3 to 40 Hz | 3.5 MHz | 0.5 to 33.86 Hz | 0.5 Hz to 48kHz min (0.5 Hz to 21kHz min 0 dB passband) |

| Signal Quality (Gain and Noise) |

|

|

|

|

| Circuits Comparison |

Case ‘’1’’ Limitation |

Case ‘’2’’ Limitation |

Case ‘’3’’ Limitation |

Proposed Circuit EEG Design Innovation |

|---|---|---|---|---|

| Point of interest |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions, or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).