1. Introduction

Variable attenuators represent an indispensable component in modern Radio Frequency (RF) devices or systems. Maintaining signal integrity while exerting control over signal power is a fundamental requirement for attenuators. Their predominant usage lies in applications demanding high linearity, low power consumption, and minimal temperature dependency, attributes that are almost unattainable with variable amplifiers [

1]. Additionally, these components must meet criteria such as high dynamic range, low insertion loss, wide attenuation range, and broad frequency bandwidth [

2].

Their applications span across automatic gain control amplifiers (AGC), impedance matching networks and broadband vector modulators [

3], and as a result, they are quite common in RF transceivers and front ends for full duplex wireless systems [

4] and measurement devices [

5]. In fact, attenuators are adopted in RF transceivers both at the transmitter and receiver side to correct variations in gain and signal strength [

6], whereas they are meant to improve the isolation between ports in full duplex systems [

7].

Concerning the current and future telecommunication scenario, variable attenuators play an important role in phased array antenna systems, a paradigm that characterizes the Multiple-Input-Multiple-Output (MIMO) antennas used in the base stations and in the small cells for the radio access the current 5G network [

8,

9].

In such phased-array systems, ensuring gain control in each element is crucial for compensating gain and suppressing sidelobes [

10]. A uniform array with identical gain in each element tends to exhibit a relatively high sidelobe level (SLL). Introducing gain tapering to the array elements results in reduced SLL, thereby reducing the impact of interfering signals, which is vital at least on the receiver’s side [

11]. A broad tuning range is generally necessary when aiming for significant sidelobe suppression. For instance, the Taylor method mandates a tapering range of about 21 dB for a linear array when targeting an SLL below -30 dB [

12,

13]. Additionally, as the number of elements increases, the required gain/amplitude tuning resolution must also rise to minimize quantitative errors during gain tapering. Passive and active gain control topologies are available, namely attenuators and variable gain amplifiers (VGA), and the key parameters governing their design include: the gain tuning range and resolution, the insertion loss (for attenuators) or power gain (for VGAs), the DC power consumption, the associated phase error, and the input and output matchings.

On one hand, the use of all-passive components in attenuators results in zero DC power consumption [

14], which is generally preferable, especially in case of large antenna arrays. On the other hand, the allocation of spectrum for the current and future telecommunications scenario led to growing frequency carriers and to growing amount of their bandwidth. This leads to an increasing miniaturization of both the radiating elements and raises the need for highly miniaturized and wideband components in their radio front ends [

15].

Traditionally, RF variable attenuators have been developed utilizing semiconductor device technologies, including RF complementary metal-oxide-semiconductor (CMOS) field-effect transistors [

16], monolithic microwave integrated circuits (MMICs) [

17], and PIN diodes [

18]. Despite their effectiveness, these semiconductor-device-based variable attenuators, as active components, face inherent drawbacks such as elevated power consumption, limited power handling and the generation of harmonics. These factors render them less favorable for applications demanding high linearity performance, especially at high frequencies [

19]. Power saving in both user terminal and base station adopting active antennas, for 5G and future mobile networks, is also a crucial objective. Devices based on materials like graphene, and vanadium oxide have been considered in recent times. However, in the case of graphene, the observed insertion loss does not exhibit sufficiently flat levels across the considered frequency band [

20], whereas, a high voltage is demanded to tune the attenuation of the structure based on vanadium oxide [

21].

The RF Micro Electro-Mechanical Systems (RF-MEMS) are becoming progressively more popular in the development of the devices that are commonly found in modern radio front ends, since their low power consumption, insertion loss, together with their superior isolation and wideband linearity, make them a favorable candidate for microwave and millimeter-wave (mmWave) applications [

22]. For this reason, different RF components have been developed in the past years, ranging from switching matrixes [

23], filters [

24], and impedance matching networks [

25], to phase shifters [

26] and attenuators [

27]. As compared to the other kind of devices, the field of RF-MEMS attenuators is the relatively less investigated to date. In fact, since the very first device presented in 2009 [

28], less than two dozen devices of this kind have populated the scientific literature. Both digital and analog [

2,

3] implementations have been considered for the developed RF-MEMS attenuators, with the former representing the vast majority. Reconfigurability, broadband behavior, and good linearity represent the most sought after features of RF MEMS attenuators. Within this context, the research effort has been put into increasing the number of attenuation states, while maintaining a flat and stable impedance value across a broad spectrum of frequencies and a minimal error as compared to the desired attenuation level [

29].

Generally, most of the existing RF-MEMS attenuators are based on a coplanar waveguide (CPW) transmission line and multiple metallic membranes, operated by electrostatic actuation and ohmic contact. They are meant to enable or disable the series or shunt resistors [

30] (or both, combined in a Pi-shaped topology [

27]) along the RF signal line, representing multiple and cascaded attenuation units. As an example, 8 units comprising series and shunt resistors are placed alternately along the signal line in [

31] to form a 256-states device. In some cases [

28,

32], such units are placed along different branches, selectable by Single-Pole-Double-Throw (SPDT) switches, while in others, sections consisting of two selectable RF lines (one attenuated and the other not attenuated) are cascaded [

27,

33,

34].

The analog and digital devices developed so far find application in multiple frequency bands, with some ranging from DC up to 20 GHz [

33,

34], and others reaching the 40 GHz [

32] or 80 GHz [

31]. Concerning the number of achievable attenuation states, most of the digital implementations consist in 3- or 4-bit architectures [

27,

33], while some reach the 8 bits [

31]. The maximum attenuation levels of the general-purpose devices developed so far are quite broad: most of the implementations attain almost -20 dB [

2,

28], while others achieving -35 dB [

34] or even -70 dB [

33]. Regarding the attenuation steps, they are quite small in case of analog devices (0.2 dB in [

2]) and ampler in digital implementations (e.g. 5 dB in [

34] and 10 dB in [

33]), with small Root-Mean-Square errors ranging from 0.2% [

2] to 5% [

34]. Despite such promising results, many of these general-purpose devices still present two limitations: on one hand, the pursue of an ever-growing number of attenuation states has led to devices with a substantial footprint or aspect ratio, while on the other hand, the use of electrostatic actuation often led to devices operated by a high bias voltage. In fact, if the 3.2 mm

2 area reported in [

34] is not alarming, footprints like 8.77 mm

2, 2.15x7.5 mm

2 or 8.28x2.37 mm

2 of the devices, reported in [

27,

28,

35] respectively, are not suitable for realistic mm-Wave MIMO systems. From a system level viewpoint, regardless the brick or tiling architecture of the array [

36], it may be problematic to fit such bulky devices in the current RF front ends or dense beamforming architectures serving array of small radiating elements [

37], each spaced by half-wavelength. Moreover, the integration of such attenuators with common CMOS-based electronic components (with driving voltages typically up to 6.5V) could be problematic because of their substantially higher driving voltage, which would imply the use of step-up DC converters in case of actuation voltages around 35 V [

33], 45 V [

31] or 51 V [

35]. Such need could be harmful especially in case of large mm-Wave arrays, both in terms of space and costs. For this purpose, commercial variable attenuators based on RF-MEMS usually feature low driving voltages (3.3 V in [

38]).

In this paper, we propose different variants of broadband and simple RF-MEMS attenuator modules featuring a reduced actuation voltage. The modules differ in their actuation voltage, topology, desired attenuation level and number of states. From the lowest (in the 5-9 V range) to the highest driving voltage (45 V), different topologies of resistors (series and shunt) have been optimized to attain different attenuation levels. Characterized by limited attenuation levels (-2, -3, -5 dB), the different modules have been assessed as building blocks to develop more complex attenuators for beamforming applications, operating in the 24.25-27.5 GHz range, the spectrum allocated to 5G communications in Europe. This paper is organized as follows: after the brief description regarding the fabrication technology adopted at our facilities of

Section 2, the electromechanical features of the membranes employed in the cells characterized by low actuation voltage are described in

Section 3. In

Section 4 basic attenuation cells featuring series and shunt resistors are described and critically assessed, both in their variants with low and more marked actuation voltages. Finally, some conclusive remarks conclude this first part of the present paper.

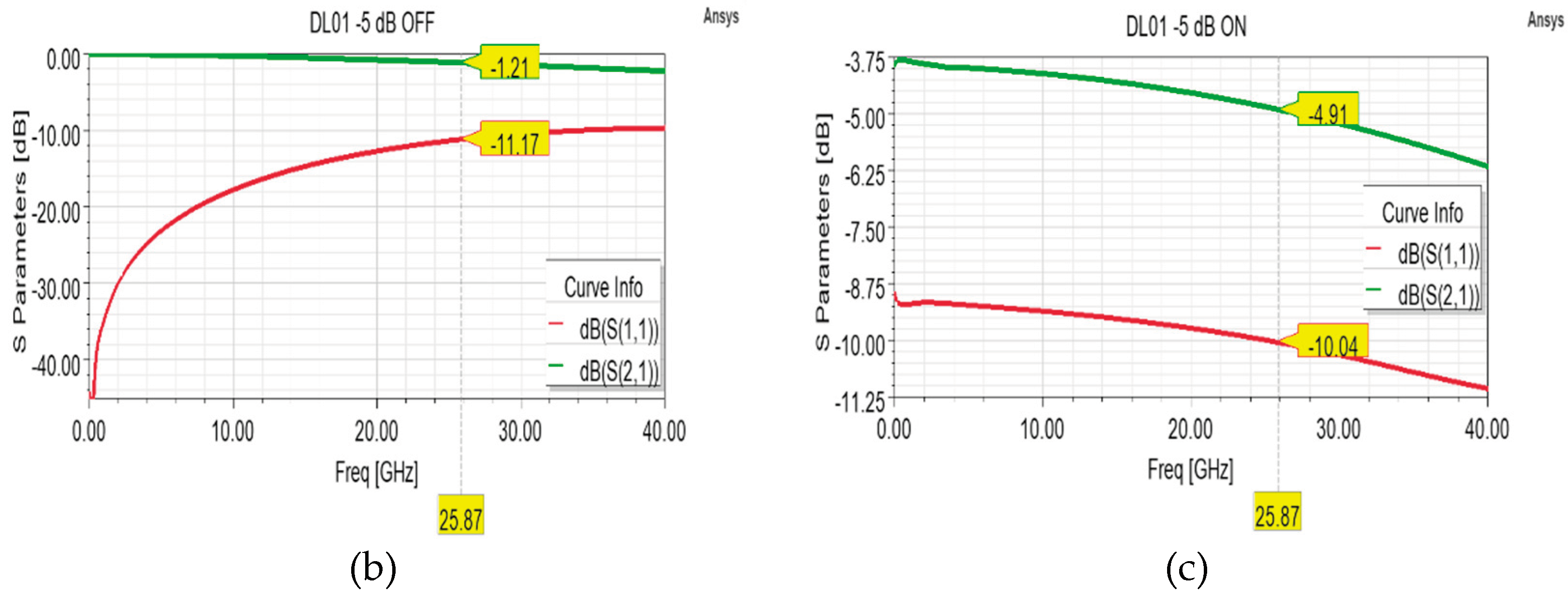

2. Fabrication

The manufacturing process at the FBK facility utilizes surface micromachining techniques and eight masks/layers [

39], as depicted in

Figure 1. The substrate is a 6-inch Silicon or Quartz wafer, onto which a layer of Silicon oxide is deposited. The initial layer is a 630 nm thick Poly-Silicon layer, deposited and patterned over areas designated for conductive paths or buried electrodes. The resistivity of this layer varies depending on the Boron dopant concentration, resulting in different possible resistivity values. The second layer consists of the subsequently deposited 300 nm Silicon oxide layer, and in the openings facilitating electrical connections to the underlying Poly-Silicon layer. These openings will be filled with the same material used in the third layer: a 630 nm thick Aluminum-based Multi-Metal layer. This Multi-Metal layer will be sputtered and patterned, and serve as either a buried conductive path for RF signals or an electrical connection with the first layer.

The openings etched into the subsequently deposited 100 nm Silicon oxide form the most important features of the fourth layer, necessary for establishing an electrical connection with the Multi-Metal. These openings will be filled with the material specified in the fifth layer. The fifth layer consists of 150 nm of Gold, evaporated onto the openings to serve as an electrical link between the Multi-Metal and the electroplated Gold layers composing the actual MEMS structure.

The sixth layer is characterized by a 3 μm photoresist sacrificial tier, patterned in areas where suspended MEMS structures will be located. The seventh mask involves a 2 μm thick electroplated Gold, positioned at RF signal lines, ground, various pads, and the suspended membrane, along with its anchoring points or surfaces. An additional and thicker (3 μm) layer of electroplated Gold constitutes the eighth and last layer, that is present on RF signal and ground surfaces enclosing the MEMS device, as well as on parts of the suspended membrane intended to be more rigid. In a subsequent phase, the sacrificial layer will be removed through Oxygen plasma etching, leading to the release of the RF-MEMS bridge.

The fabrication process described is slightly more intricate when compared to procedures outlined in recent studies [

40,

41]. However, it comes with substantial benefits, including an expanded range of design possibilities during the planning stage and the ability to maintain effective physical separation between the paths of the DC signal and the routed RF signals.

3. The Membranes

The adopted class of membranes rely on meandered supports to achieve a reduced spring constant along the vertical direction for the movable structure, and thus a reduced actuation voltage (or pull-in).

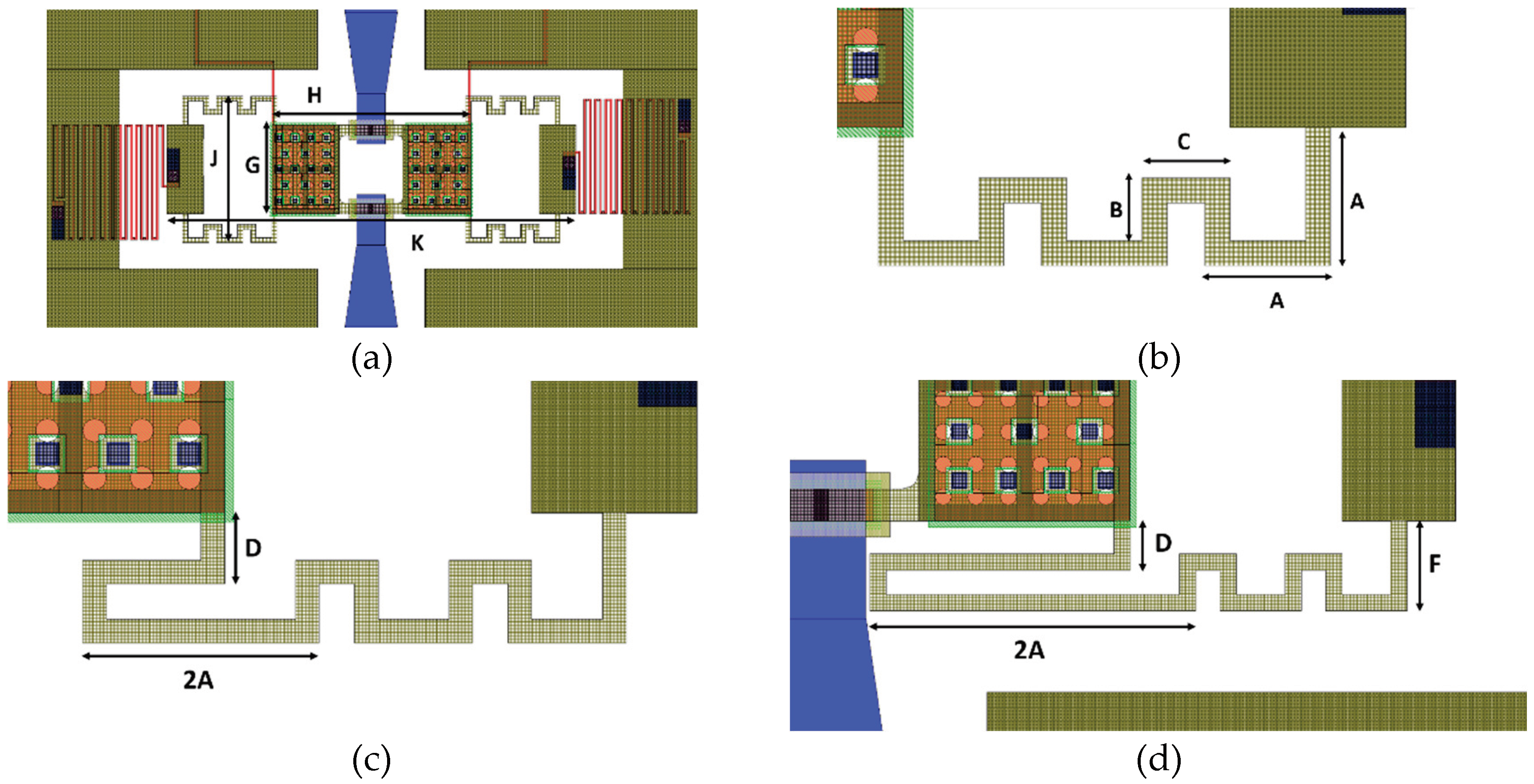

Commencing with the layout depicted in

Figure 2a, various critical layers can be discerned, with the initial layer of the fabrication process being the polycrystalline silicon. This layer constitutes both the central buried electrodes and the lateral decoupling resistors. The central buried electrodes, positioned beneath the membrane's perforated sections, are designed to induce the membrane's collapse. Meanwhile, the lateral decoupling resistors prevent the diversion of RF signals toward the ground planes when the membrane is activated.

The multi-metal layer is utilized for implementing both the central and interrupted RF signal lines, featuring terminals enclosed by rectangular contact pads made of evaporated gold. These regions serve as the contact surfaces with the collapsed membrane, constructed using two layers of electroplated gold. The first layer forms the primary structure of the central membrane, while the second, thicker layer is positioned specifically over surfaces intended to provide greater stiffness, such as anchors and borders of the movable membrane.

As visible in the following figures, the class of membranes is characterized by beams with uniform meanders, except for the terminal one, which has been elongated to achieve a progressively lower pull-in voltage. Three devices (Dev 1, Dev 2 and Dev 3) have been studied with modifications described in

Figure 2. In particular,

Figure 2a reports the overall footprint of the membrane (780x270 μm²), consisting of a central rectangular plate measuring 380x170 μm² and beams formed by uniformly meandering segments measuring 50 μm by 25 μm (as indicated by A and B in

Figure 2b) with a width of 10 μm. Such dimensions are the result of the desire to balance the elongation introduced by the meandered beams with size of the central plate, aiming at a movable structure characterized by a moderate footprint. The second device, partially shown in

Figure 2c, features non-uniform meandered beams achieved by doubling the length of each terminal meander. In the third device, depicted by the beam in

Figure 2d, the length of the terminal meander is increased to four times its original length, and the lateral dimension of the meanders (F in

Figure 2b) has been slightly enlarged to maintain a minimum distance of 10 μm between the contact pads and the beams. As a result, the target pull-in voltage of the three membranes has been progressively lowered without a substantial increase of the footprint. All the parameters reported in the following figures are detailed in

Table 1, while additional considerations concerning the discussed structures can be found in [

42].

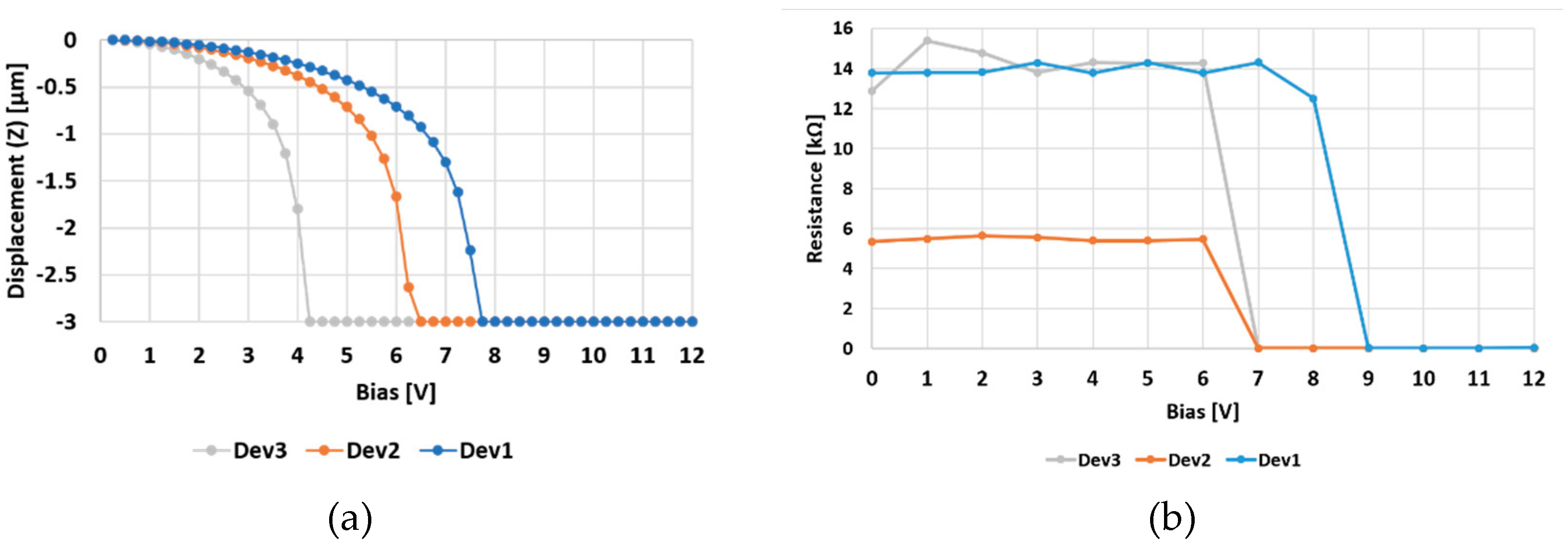

The devices were simulated by Finite Elements Method (FEM) in the Ansys Workbench software environment, while the measurements were conducted by a manual probe station and two digital multimeters. The initial multimeter supplied the DC bias voltage and established the ground reference for the device under test (DUT) pads. Simultaneously, the second multimeter maintained a restricted voltage drop between the input and output terminals of the central RF signal line. This was done to assess the resistance of the line and the level of DC current flowing. Specifically, when the DC bias attains the pull-in voltage, the membrane’s collapse induces a sudden decrease in resistance (accompanied by an increase in DC current) along the RF line.

Since the DC bias was applied by increments of 1 V, the values presented in

Figure 3 demonstrate a favorable agreement between the simulated and measured outcomes. Notably, while the measured pull-in voltages for Dev3 and Dev1 (9V and 7V) are slightly higher than the simulated values (8V and 5V, respectively), the measured actuation of Dev2 aligns with the anticipated performance.

The slight discrepancy observed in the Dev3 and Dev1 switches can be attributed to the heightened stiffness of their movable membranes, resulting from residual tensile stress introduced during the fabrication process. Initially, the measurements indicated pull-in voltages that exceeded those shown in

Figure 3b by 10-15V. Subsequently, a re-baking thermal treatment was applied, involving the devices being maintained at 200 °C for a few hours and then slowly cooled, resulting in the release of most of the initial residual stress. The reported measurements were conducted thereafter. Additional considerations concerning the electromagnetic behavior of the considered membranes can be found in [

42].

4. Series and Shunt Attenuation Cells

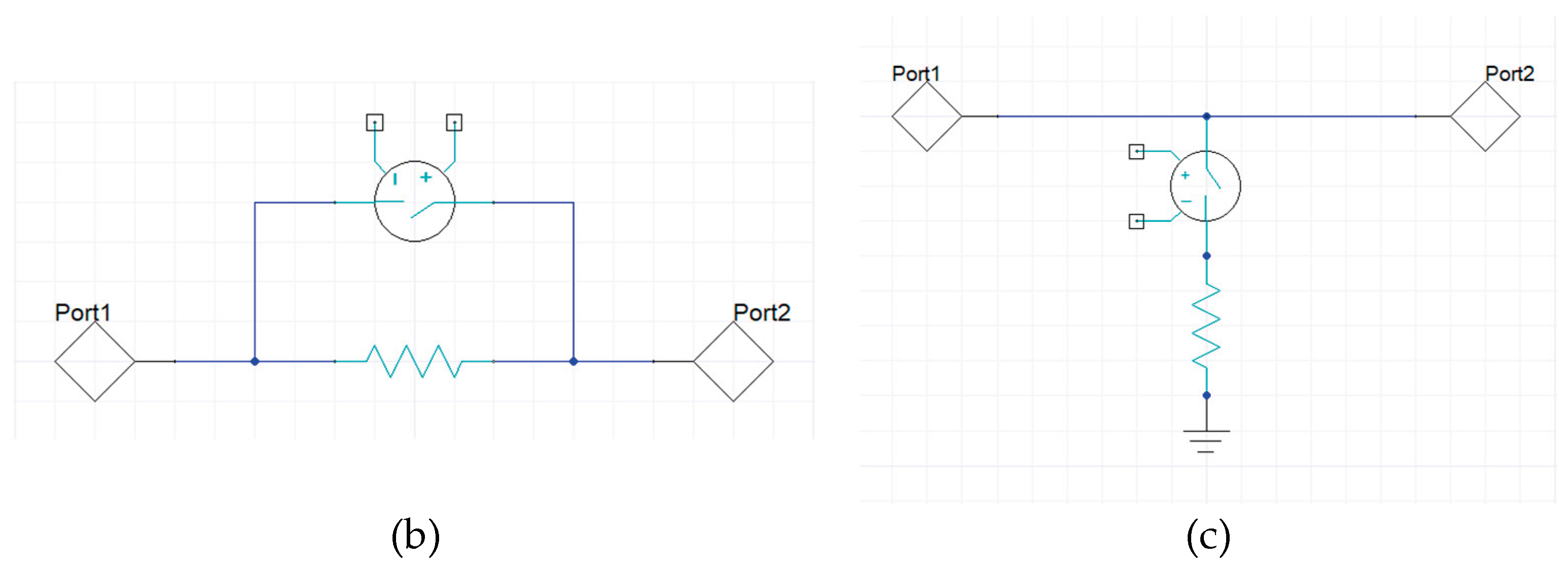

The discussed set of membranes has been adopted to develop the layout of different low-voltage attenuation cells. Concerning the topology of these cells, both series and shunt resistors has been considered, following the approach reported in [

30]. In such work, single attenuation cells are presented, each featuring a series or a shunt resistor loading the RF signal line. As reported in the schematics of

Figure 4, the resistors either load the line or are short-circuited based on the movement of clamped-clamped membranes. Depending on the architecture of the cell, the actuation of the membrane may short-circuit the series resistor or load the RF signal line with resistive shunt paths. Starting from the layout, 3D models of the two variants of cells have been developed and the width, length and sheet resistance of the resistors have been parametrized in order to optimize them.

4.1. Test Bench Cells

As starting point, the design of the abovementioned attenuation cells has been optimized to determine a specific values of attenuation (-2 dB, -3 dB and -5 dB) at the center frequency (25.87 GHz) of the 24.25-27-5 GHz band, which has been chosen as practical use case since it represents the higher frequency range allocated to 5G communications in Europe. As for the membranes reported in [

30], also the membranes employed in the cells displayed in

Figure 5,

Figure 7 and

Figure 8 are characterized by a substantial actuation voltage (~ 45V), since this topology has been used as initial test bench.

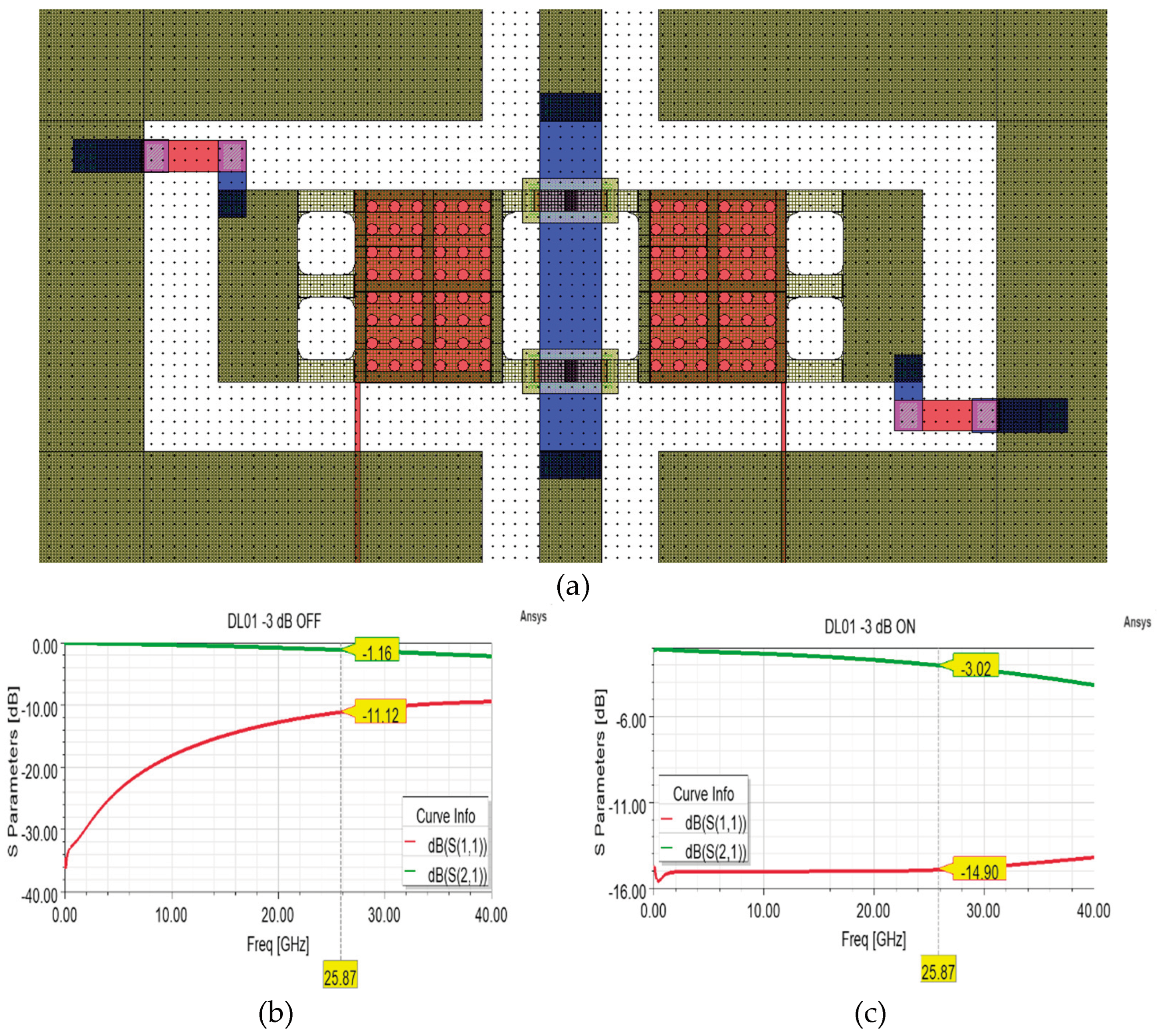

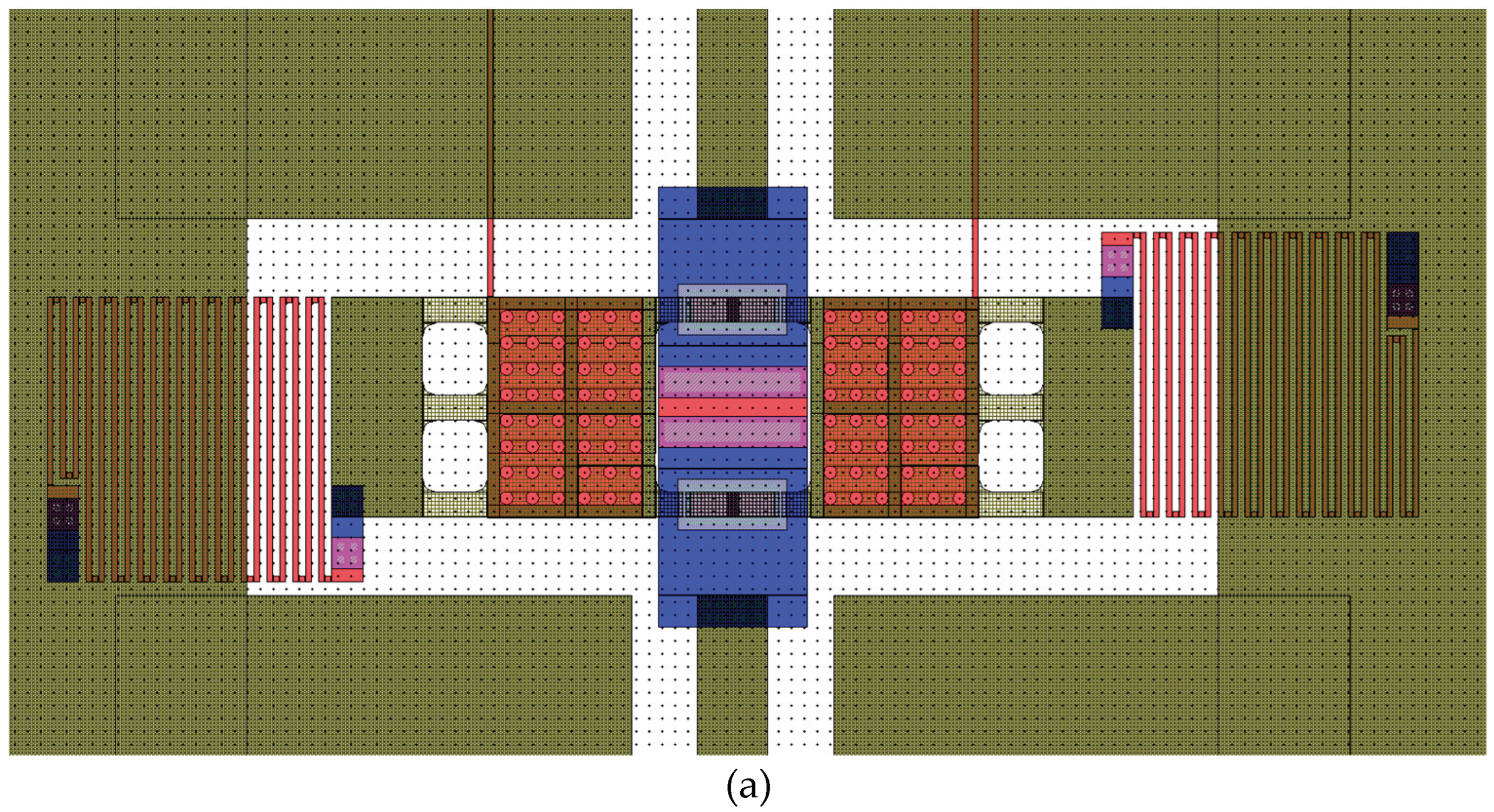

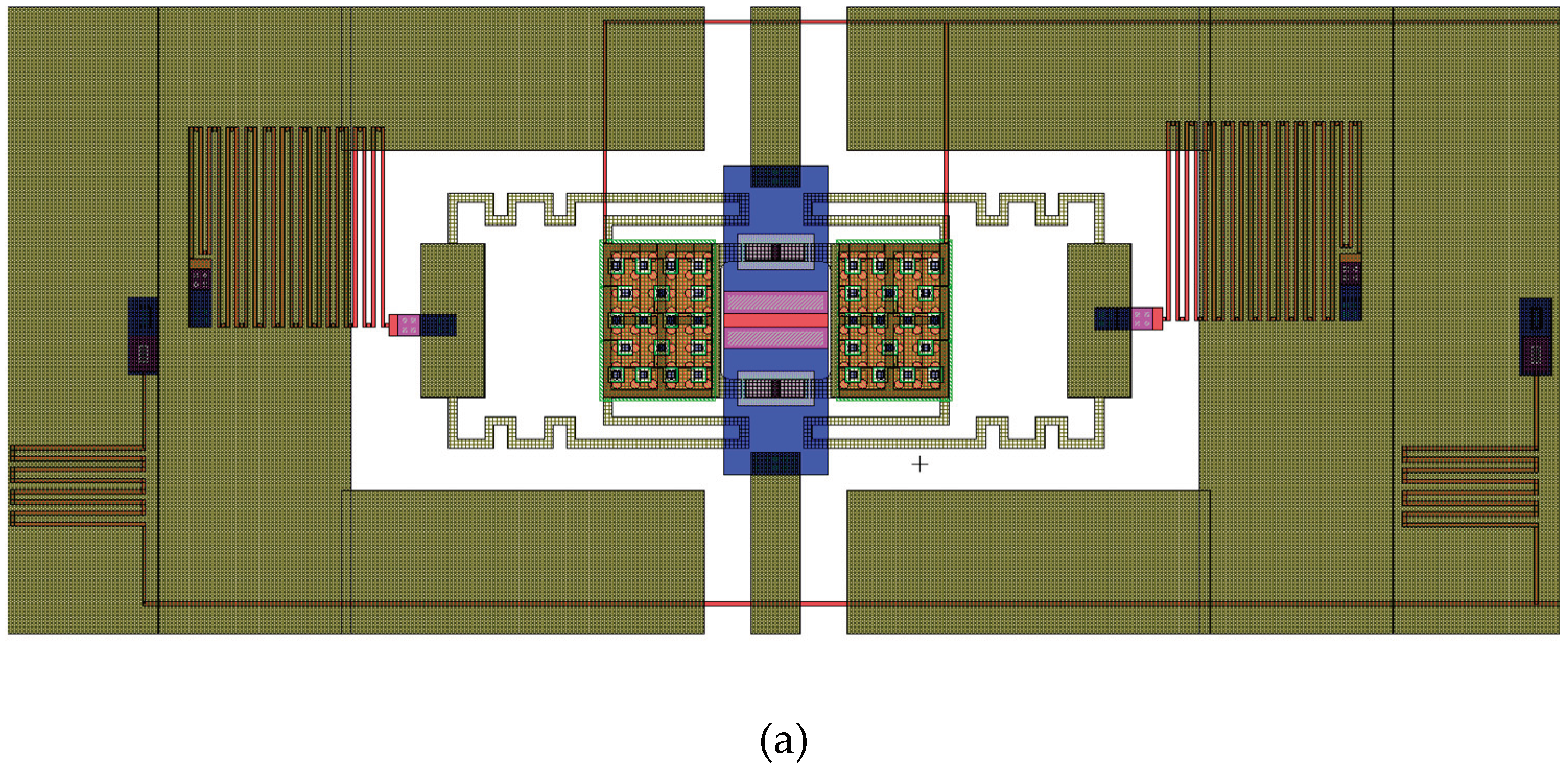

Among the most salient features of the layout reported in

Figure 5a, it is possible to distinguish the central and buried Poly-Silicon resistor (in red) along the RF signal line, which extends along the Multi-Metal buried sections (in blue) and the sections of electroplated Gold (in dark green). The operation of the device involves a default attenuation state due to the series resistor along the RF line, which can be short-circuited by actuating the membrane. As visible in

Figure 5b, in the default attenuation state this cell introduces an attenuation level of -2 dB thanks to its 63x113 µm

2 (length x width) resistor and a sheet resistance of 100 Ohm/Sq of the Poly-Silicon composing the resistor. The return loss and insertion loss curves are quite flat, and the range of their values is satisfying along the entire 30 GHz range (

Figure 5a,b).

Unfortunately, in order to fabricate this and other attenuation cells discussed in the following lines on the first available opportunity, they have been added to the wafer layout containing devices to be fabricated as part of another project. A proper doping of the Poly-Silicon layer was not important for the devices developed during that project, and delays during the fabrication process have caused the fact the Poly-Silicon layer of the devices contained in such wafer layouts underwent a coarse doping just to lower the basic sheet resistance of the basic Poly-Silicon. As a result, the sheet resistance of some of the following devices turned out to be in the 600-800 Ohm/Sq range, depending on the particular wafer, instead of the intended 100 Ohm/Sq, with a consequent alteration of the achieved performances.

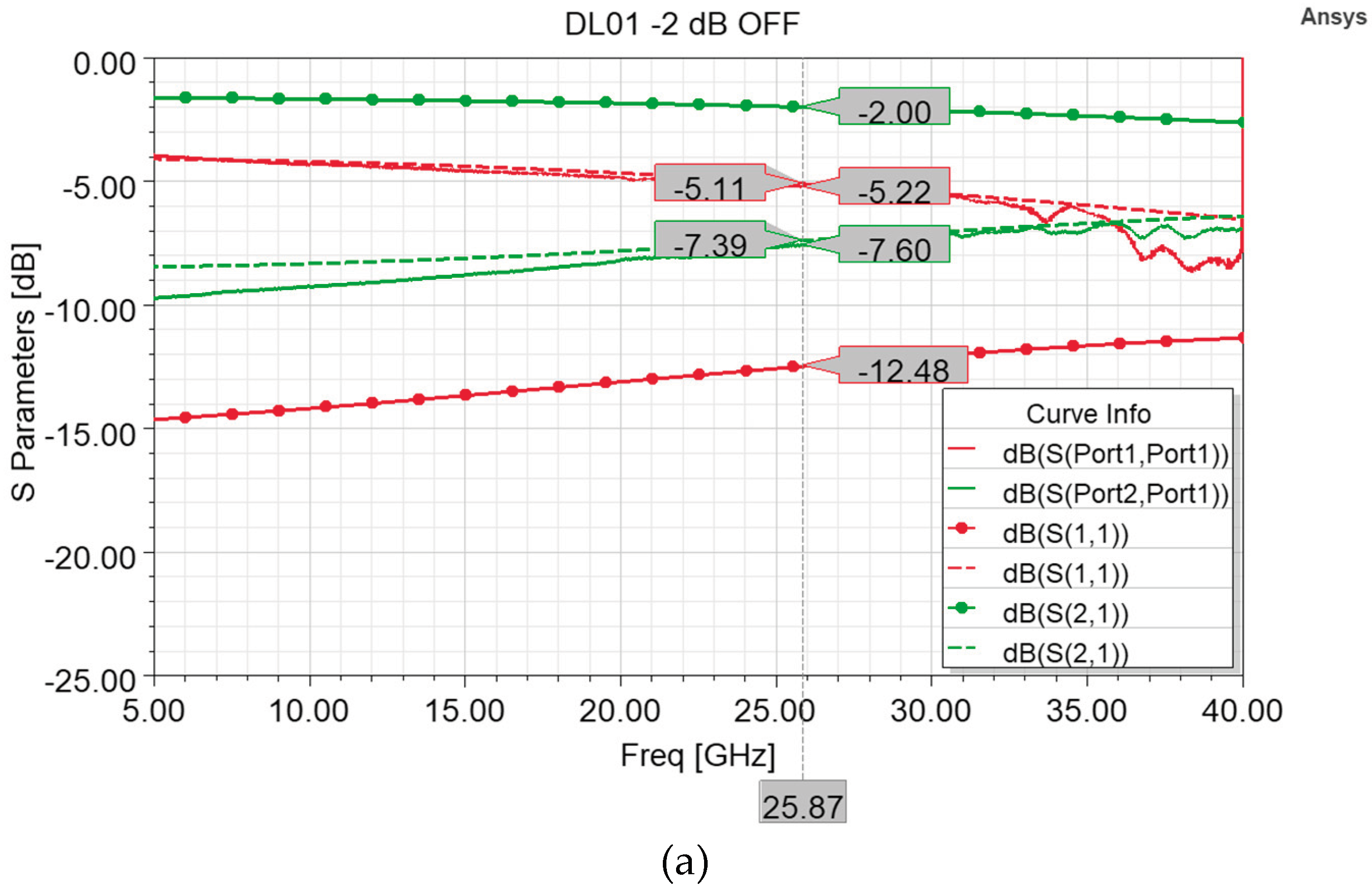

As visible in

Figure 6, the measurement conducted along the 5-40 GHz interval in both the OFF (resting membrane, attenuation) state and ON (actuated membrane) state displayed insertion loss values that are far from the ones of the optimized model of

Figure 5. In particular, the measured insertion loss in the OFF state (-7.6 dB) and the related excessive return loss curve (-5.22 dB) at 25.87 GHz are due to a sheet resistance of 800 Ohm/Sq of the Poly-Silicon composing the 63x113 µm

2 resistor. In fact, as visible in

Figure 6a, the attenuation cell simulated by taking into account a sheet resistance of 800 Ohm/Sq exhibits return loss and insertion loss curves that approximated the measured curves with a high degree of agreement. This proves that the measured performance is due to a different sheet resistance value characterizing the fabricated samples, and a doping of the Poly-Silicon layer in compliance with the intended value would have determined the desired performances. Beside such issue that affected the device behavior primarily in its attenuation state, it is possible to notice in

Figure 6b that the measured insertion loss (-0.69 dB) is better than the simulated one, even in case of the intended simulated behavior (-0.77 dB). In the other hand, the measured return loss is slightly worse (-14.07 dB) than the simulated ones, in both the cases of 100 and 800 Ohm/Sq, -17.75 dB and -18.47 dB respectively.

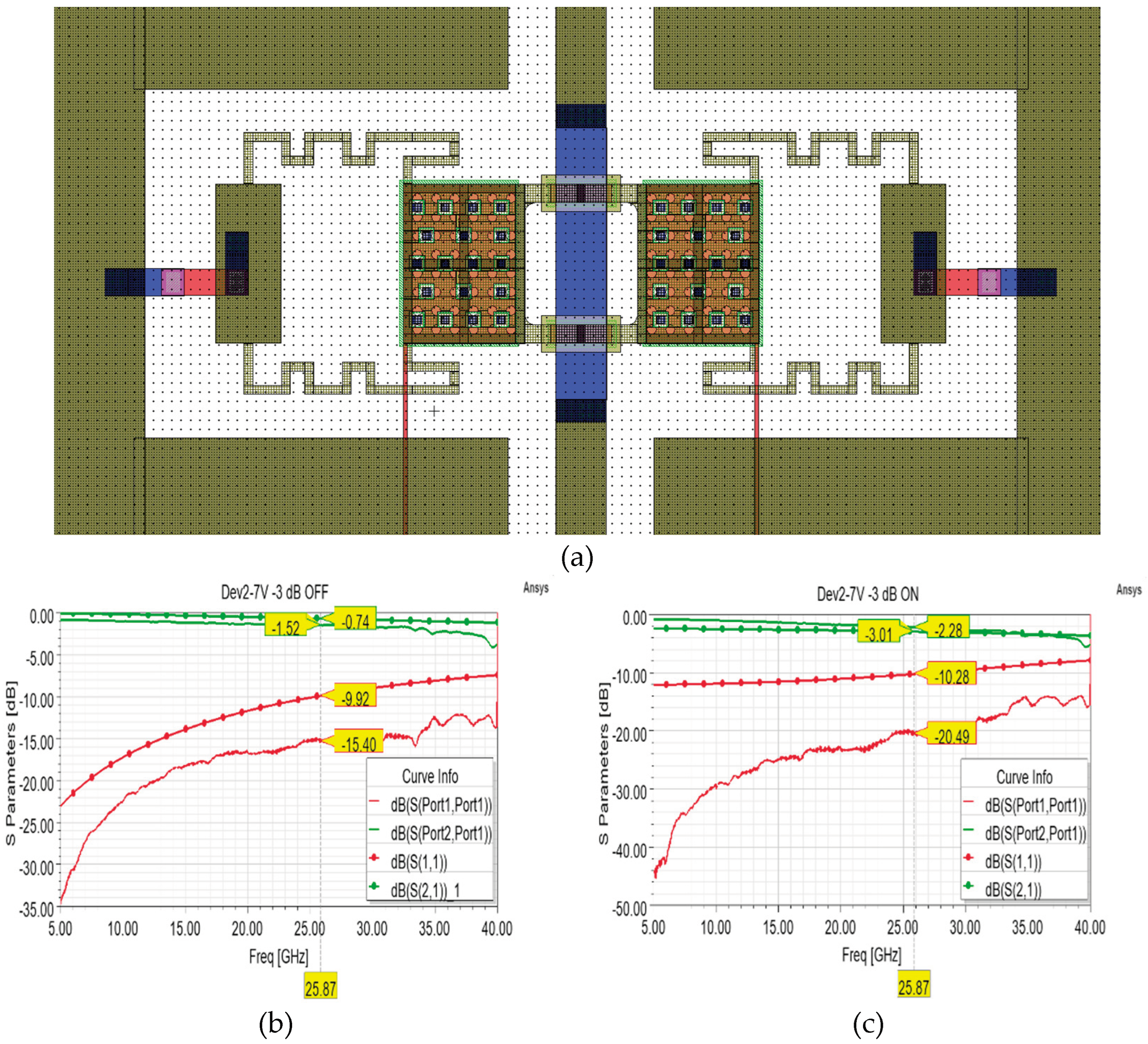

A cell featuring shunt resistors has been adopted in order to achieve a -3 dB attenuation level at the center frequency of the desired frequency interval. In this topology, the signal experiences no attenuation when the membrane is in rest position (OFF state), while part of the signal power is dissipated along the shunt resistors connecting the membrane to the ground planes when the membrane is actuated (ON state). As a result, the desired attenuation level can be achieved by controlling the dimensions and the sheet resistance of the Poly-Silicon resistors. In the case of the cell depicted in

Figure 7a, an attenuation level of -3 dB can be reached by 93x28 µm

2 (length x width) resistors and a sheet resistance of 100 Ohm/Sq. Concerning the simulated scattering curves of

Figure 7b,c, it is worth noticing the flatness of the return loss curve along the entire frequency interval and the precise attenuation level reached at the center frequency in the ON state. On the other hand, the return loss and insertion loss curves in the OFF state could be improved by a further optimization of the CPW structure.

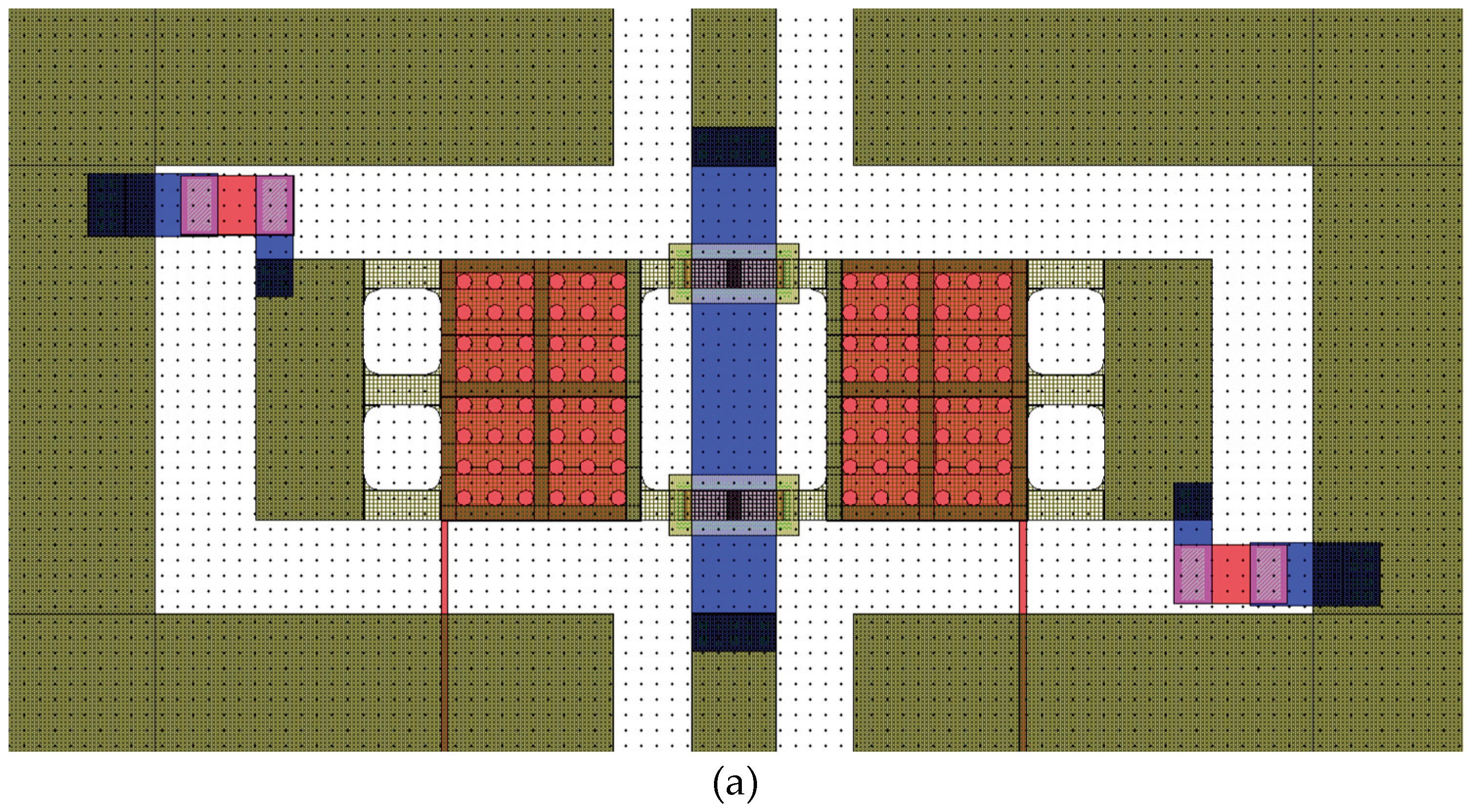

Another optimized version has been developed to verify the maximum attenuation level that can be achieved by means of this shunt topology used as test bench. The resulting layout is depicted in

Figure 8a, whose main feature is represented by the 39x74 µm

2 (length x width) shunt resistors, sized on the basis of a 100 Ohm/Sq sheet resistance. As visible in

Figure 8c, a maximum attenuation level of almost -5 dB can be reached by this topology, without substantial degradation of the return loss curve, which lies between -9.94 and -10.14 dB within the 24.25-27.5 GHz interval. Also, in this case, the return loss and insertion loss curves of the OFF state could be improved by further optimization of the CPW parameters.

Fabricated samples of both the -3 dB and the -5 dB cell variants have been characterized, and the post-measurement simulations have shown that also the sheet resistance of the fabricated -3 dB and -5 dB cell variants corresponds to 800 Ohm/Sq. Thus, just the simulated S parameters of the -3 and -5 dB variants have been reported for sake of brevity.

Figure 7.

(a) Overall layout of the attenuation cell featuring shunt resistors for a desired attenuation level of -3 dB, (b) simulated S parameter curves in the OFF state, and (c) ON state.

Figure 7.

(a) Overall layout of the attenuation cell featuring shunt resistors for a desired attenuation level of -3 dB, (b) simulated S parameter curves in the OFF state, and (c) ON state.

Figure 8.

(a) Overall layout of the attenuation cell featuring shunt resistors for a desired attenuation level of -5 dB, (b) simulated S parameter curves in the OFF state, and (c) ON state.

Figure 8.

(a) Overall layout of the attenuation cell featuring shunt resistors for a desired attenuation level of -5 dB, (b) simulated S parameter curves in the OFF state, and (c) ON state.

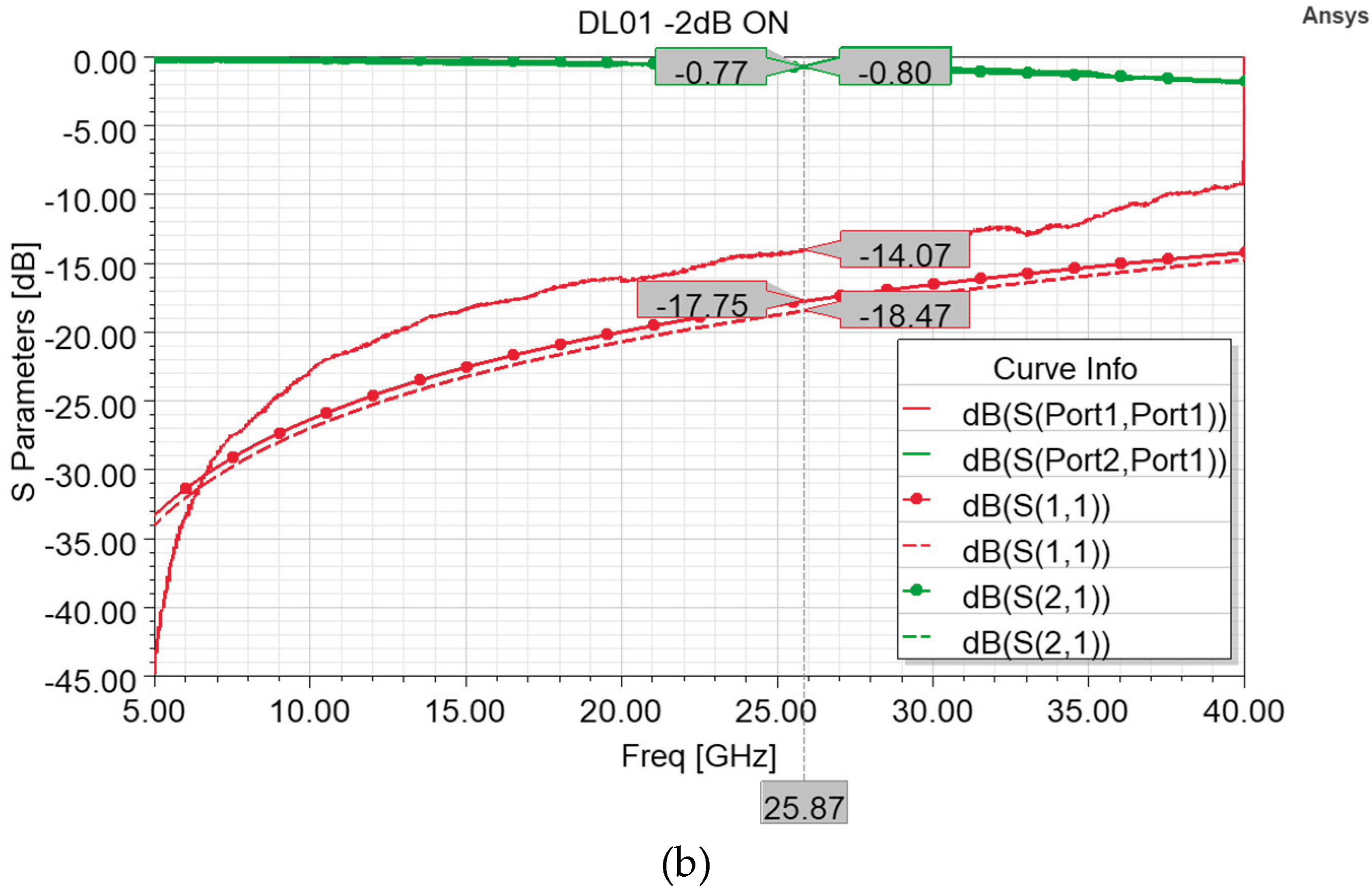

4.2. Low Pull-in Cells

For each of the abovementioned attenuation levels, variants equipped with the 5V, 7V and 9V membranes of

Figure 3 have been fabricated and characterized. The layout and the operation of the cell displayed in

Figure 9a does not substantially differ from the one displayed in

Figure 5, except for being a “dielectric-less” design. In fact, in this design the layers of silicon oxide covering the buried electrodes in correspondence of the squared areas of the movable membrane are meant to be removed in order to avoid the phenomenon of charge accumulation/trapping. In their place, quadrangular stopping pillars of Poly-Silicon, covered by the Multi-Metal and evaporated-Gold layers have been placed, to avoid the contact between the fixed electrodes and the movable membrane. The present attenuation cell has been optimized by maintaining the same dimensions of the series resistor (63x113 µm

2) and varying the sheet resistance of the Poly-Silicon. In particular, by a 130 Ohm/Sq sheet resistance this design can achieve an attenuation level of nearly – 2 dB (

Figure 9b), with rather flat curves of return loss and insertion loss along the whole considered interval. When the membrane is actuated and the resistor is short-circuited in its ON state (

Figure 9c), this variant shows a quite limited insertion loss and a return loss ranging between -11.46 and -10.15dB along the 24.25-27.5 GHz.

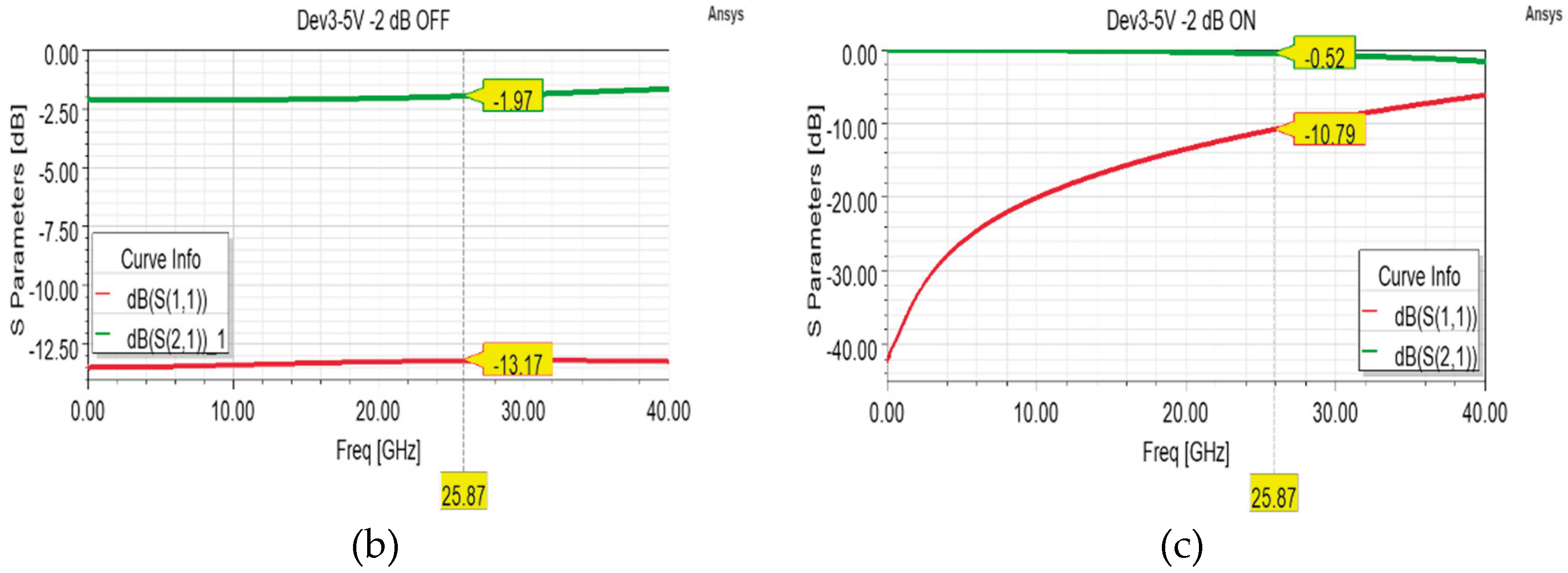

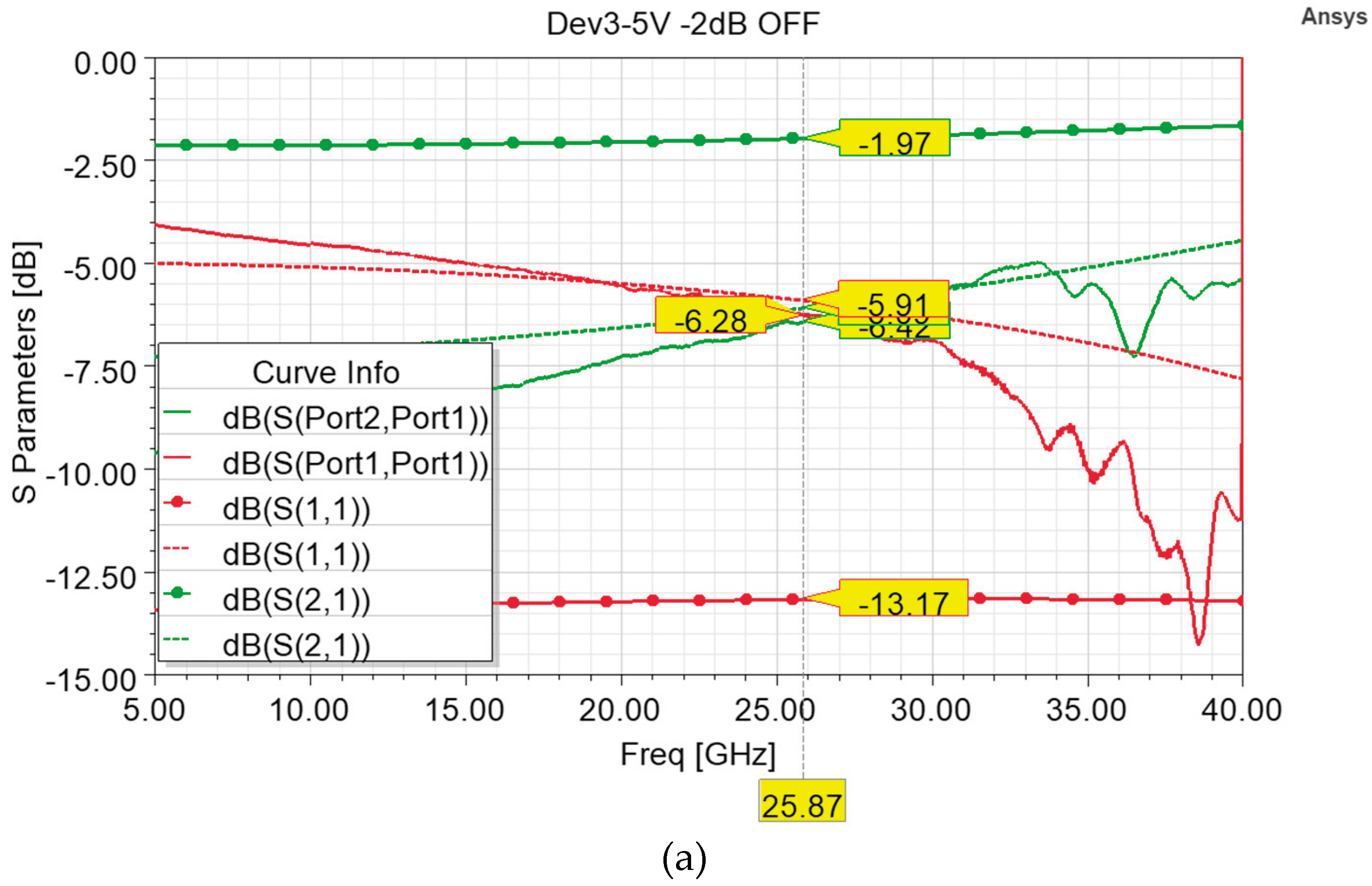

As for the previous cells, also the Poly-Silicon of the cells featuring the low pull-in membranes was subject to coarse doping. In particular, the Poly-Silicon on the wafer containing the fabricated samples that have been characterized is marked by a sheet resistance of 600 Ohm/Sq, instead of the planned 130 Ohm/Sq. Like for the abovementioned -2 dB variant, the measured performances inevitably differ from the planned ones and the outcomes of the model simulated by taking into account a 600 Ohm/Sq sheet resistance have a good agreement with the measurements. In particular, the simulated curves of the OFF state (

Figure 10a) qualitatively match the measurements up to 31 GHz, after which the measurements become noisier, and growing ripples appear. Unlike the previous -2 dB variant, when the series resistor is short-circuited in the ON state, the measured return loss is generally better the simulated ones (both the intended 100 Ohm/Sq, -10.79 dB, and the unplanned 600 Ohm/Sq, -10.80 dB) along the majority of the frequency interval. On the other hand, the measured insertion loss (-1.05 dB) is worse than the simulated ones.

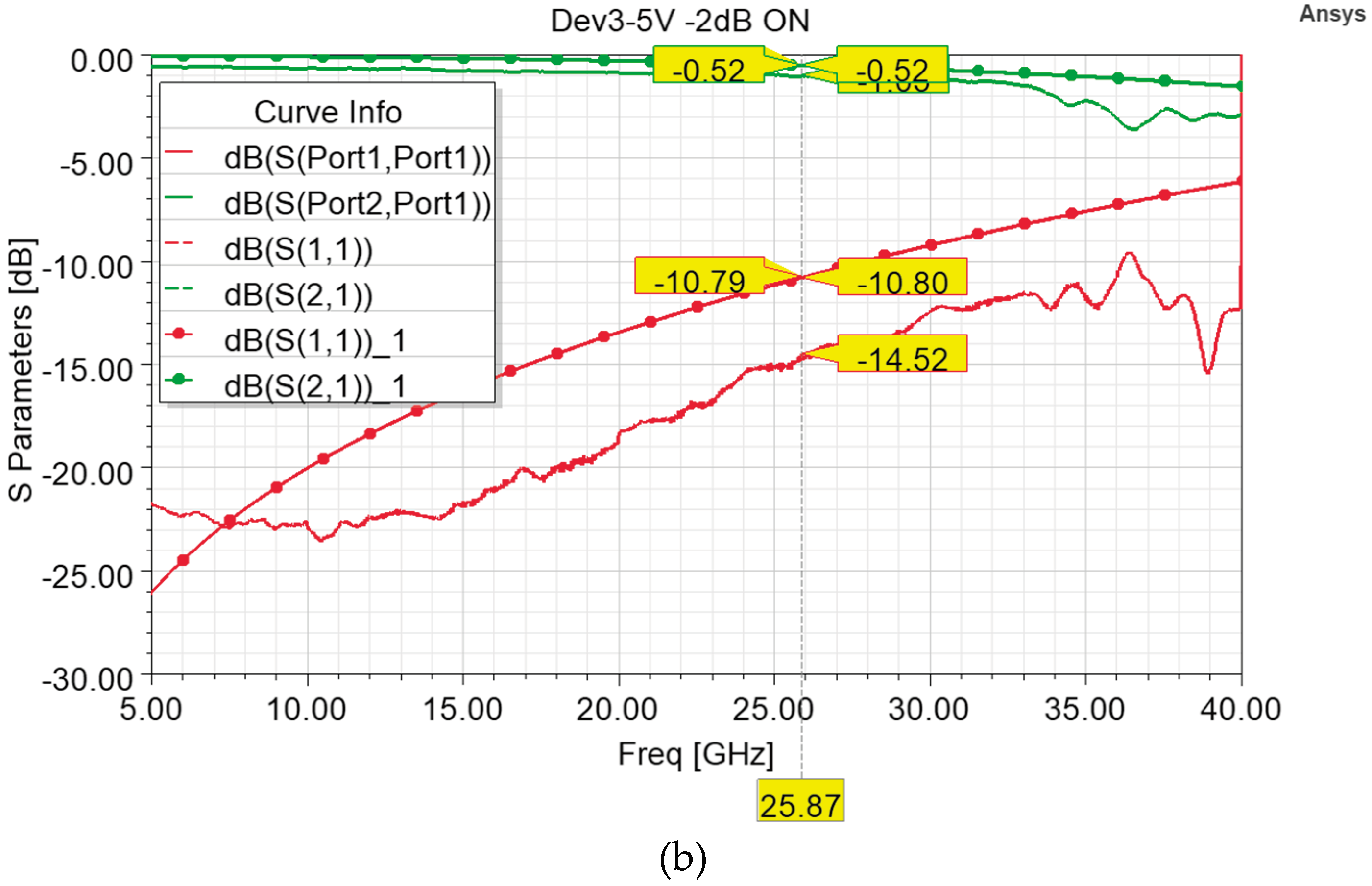

Concerning the variants aiming at a -3 dB attenuation level, a cell equipped with the membrane with a 7 V pull-in voltage is reported in

Figure 11a. Also in this case, during the design phase the dimension of the shunt resistors has been kept the same as the ones of the -3 dB test bench model and the sheet resistance has been varied to reach the attenuation of -3 dB at the desired frequency. As a result, 93x28 µm

2 (length x width) shunt resistors marked by 80 Ohm/Sq sheet resistance characterize this cell. Like the previous cell, when no attenuation is imposed to the signal (OFF state) the measured return loss is definitely better than the simulated one, while the measured insertion loss is generally greater than the simulated one (~ 0.7 dB), and a good qualitative agreement between the two curves can be noticed in

Figure 11b. The same trend marks the curves displayed in

Figure 11c: a discrepancy of ~ 0.7 dB can be seen among the attenuations, while the return loss of the fabricated sample is definitely better than the simulated one along the entire frequency interval.

Concerning such discrepancies, as a general remark, it is worth noticing that in case of electromagnetic full-wave simulations of devices meant for high frequencies, some simplifications are necessarily introduced to the 3D model to ease the meshing process and the convergence of solution. Starting from the emulation of the fabrication process, it is not always possible to faithfully replicate some operations (e. g. isotropic deposition), so that slight modifications to the thickness of some layers is performed to achieve an overall correct stacking. For the same reason, the deformation of the membrane due to the sacrificial layer cannot be easily reproduced, therefore flat membranes are adopted in the 3D model and moved to model the actuation and its rest position, which slightly alter the amount of capacitive coupling between the membrane and signal line during both states. In addition, bodies which are not strictly necessary to the functioning of the device (in its operations in the AC regime), such as the DC decoupling resistors, are suppressed to ease the meshing process and the convergence of the solution. All those simplifications can be cast as a set of distributed complex impedances that globally play a role as I/O mismatches (referring to the return loss) and/or adjunctive losses (referring to the insertion loss). Those effects, combined with possible non-idealities in the multi-step manufacturing process, motivate the differences between simulation and measurements, and can be investigated and mitigated in further steps of optimizations.

The abovementioned cells featuring low pull-in membranes display an interesting behavior, for which the return losses of the fabricated samples are significantly limited as compared to the simulation outcomes, despite a minimal discrepancy between the simulated and the measured insertion loss curves. However, the substantial agreement between the displayed performances of the different cells proves that the expected performance can be achieved for the considered designs, providing a faithful fabrication process.

From a critical perspective, the simulations and the measurement outcomes showed that by such basic design, maximum attenuation levels of about -3 dB and -5 dB can be achieved, by series and shunt design, respectively. For larger amounts, the other topologies and combinations described in the second part of the present paper should be considered.