Submitted:

19 November 2023

Posted:

20 November 2023

You are already at the latest version

Abstract

Keywords:

1. Introduction

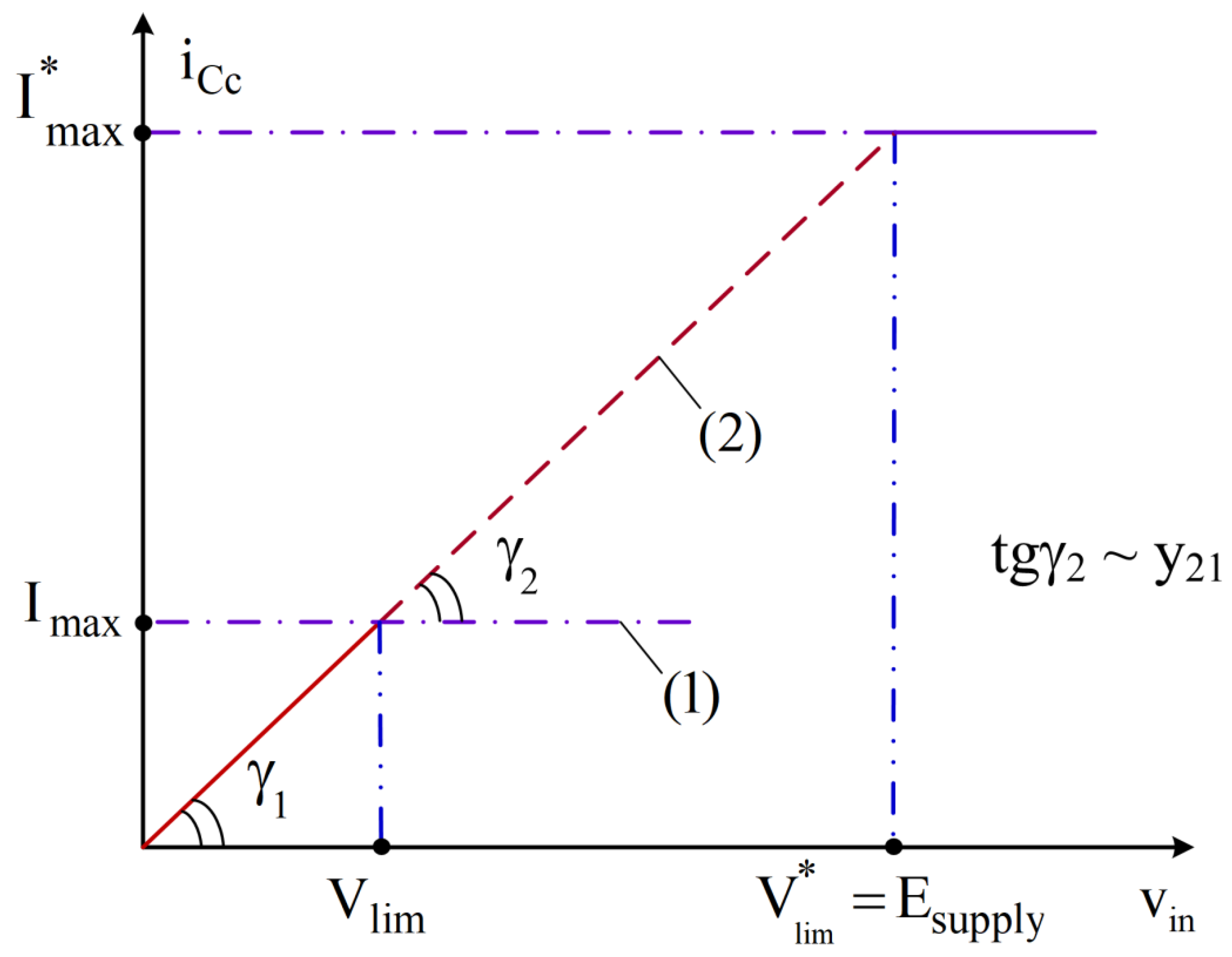

2. Energy limitations for input stages Op-Amp with maximum speed

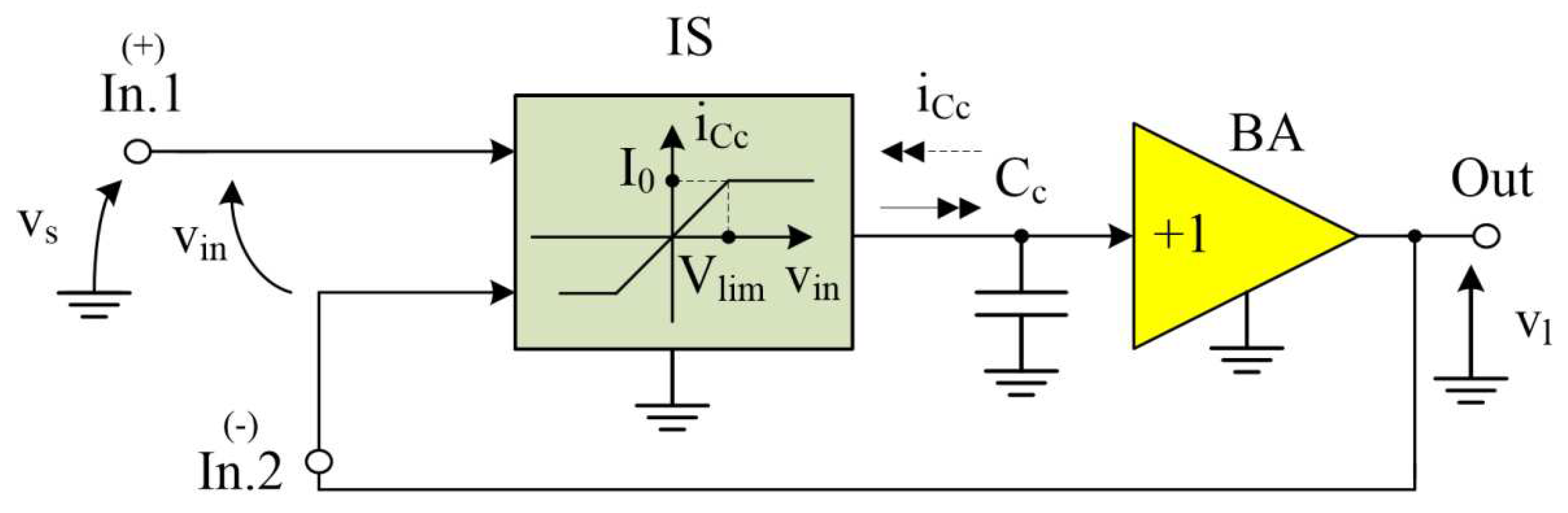

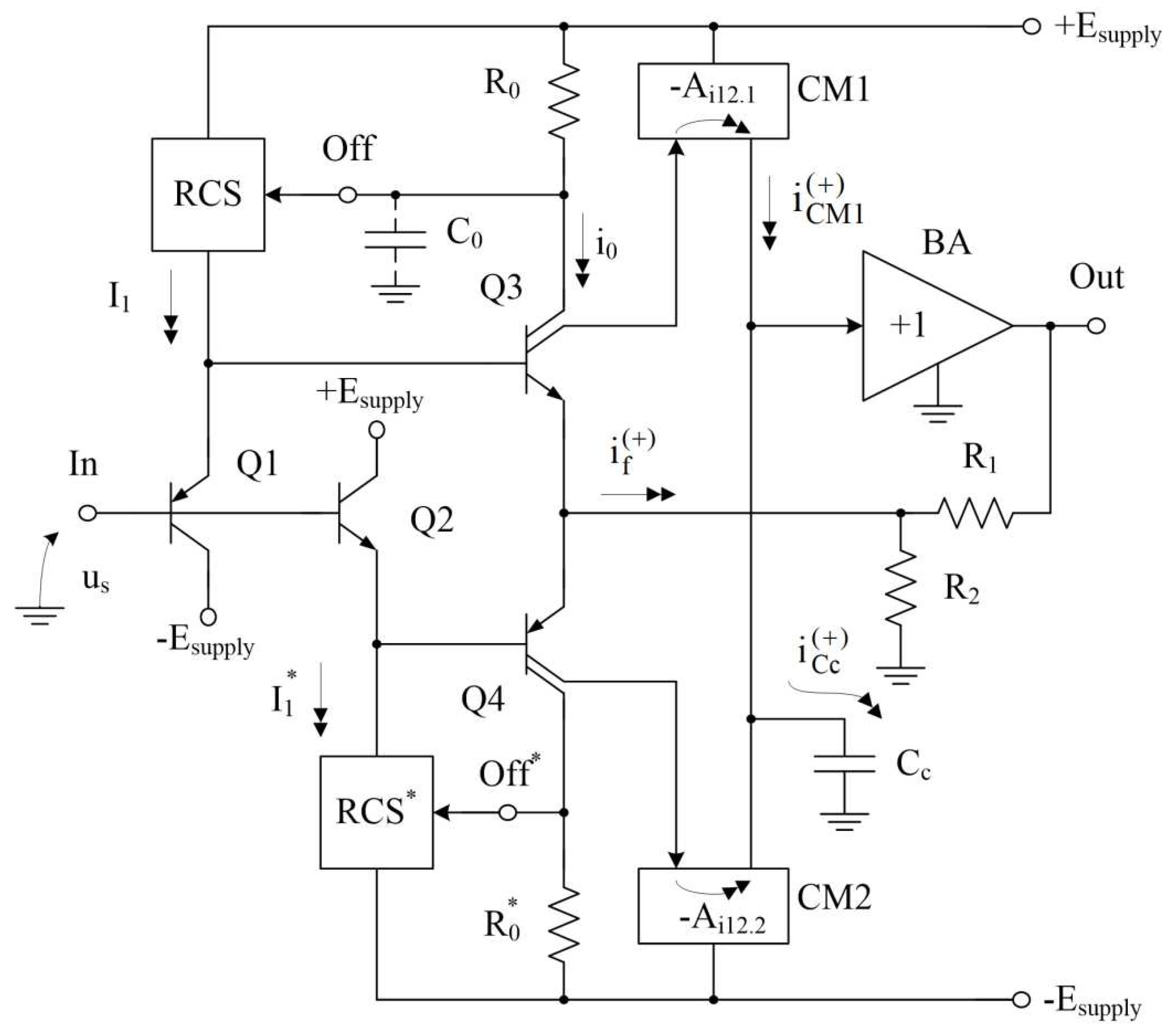

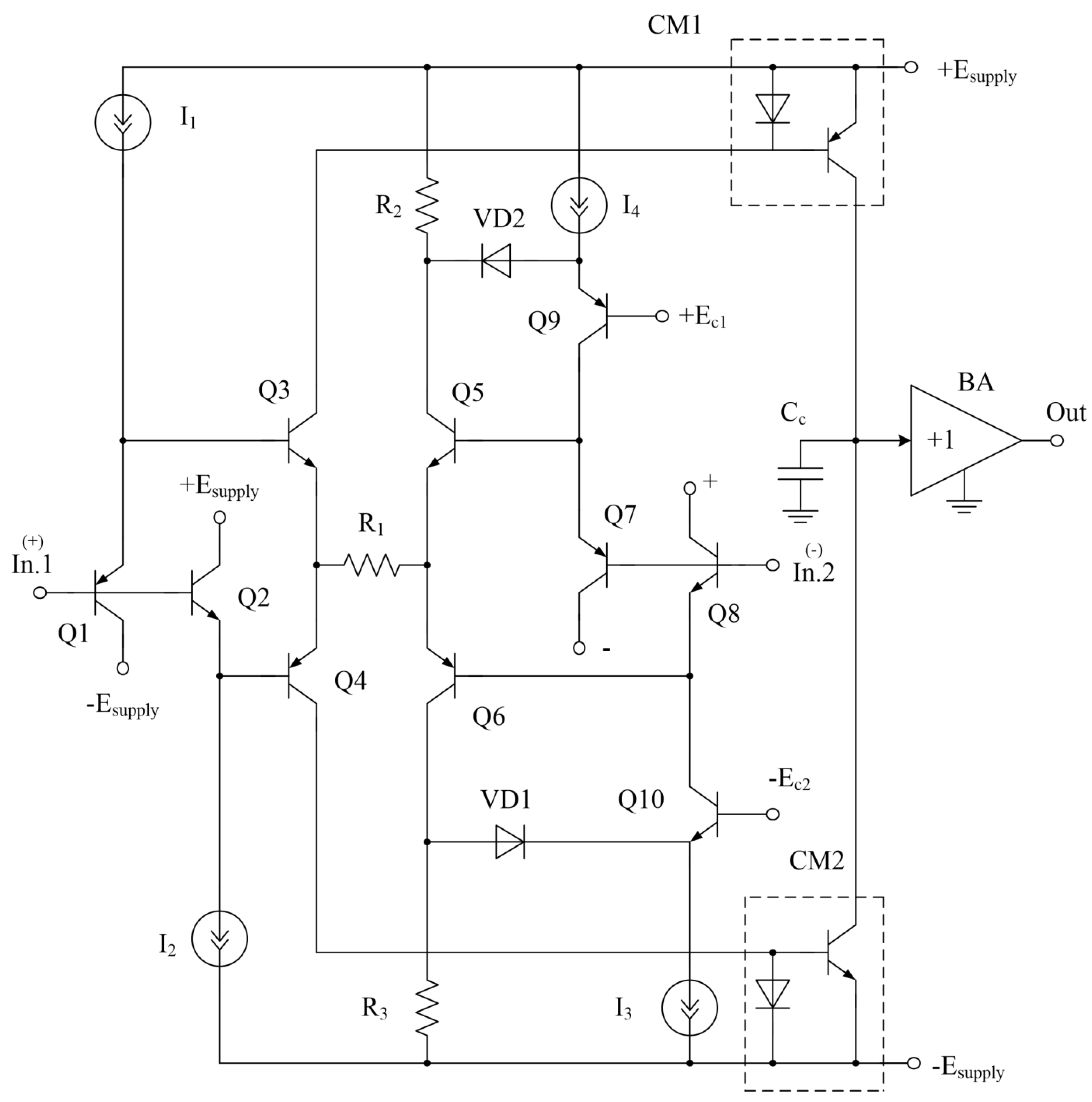

3. Intelligent protection against Trojans in Op-Amps with current feedback

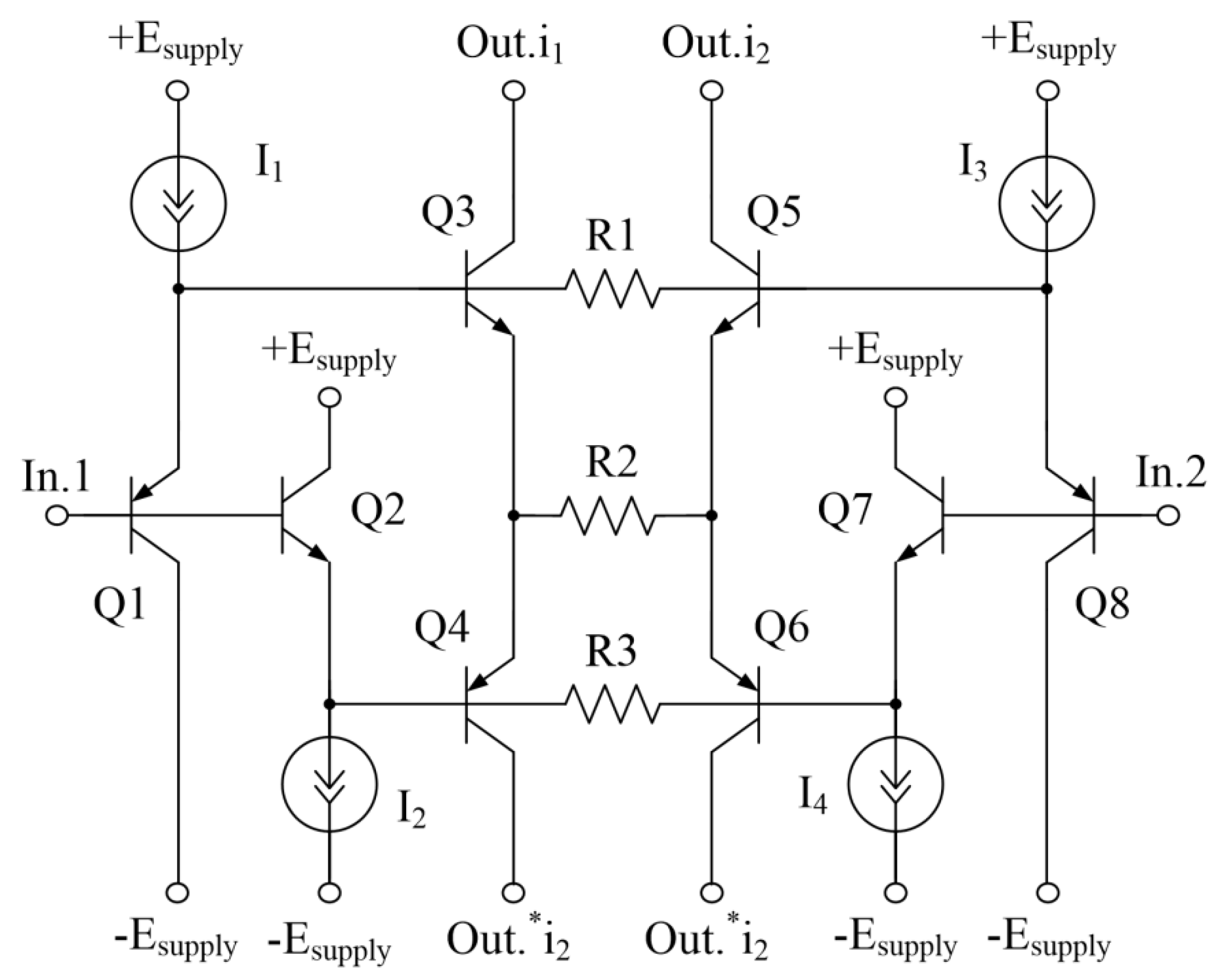

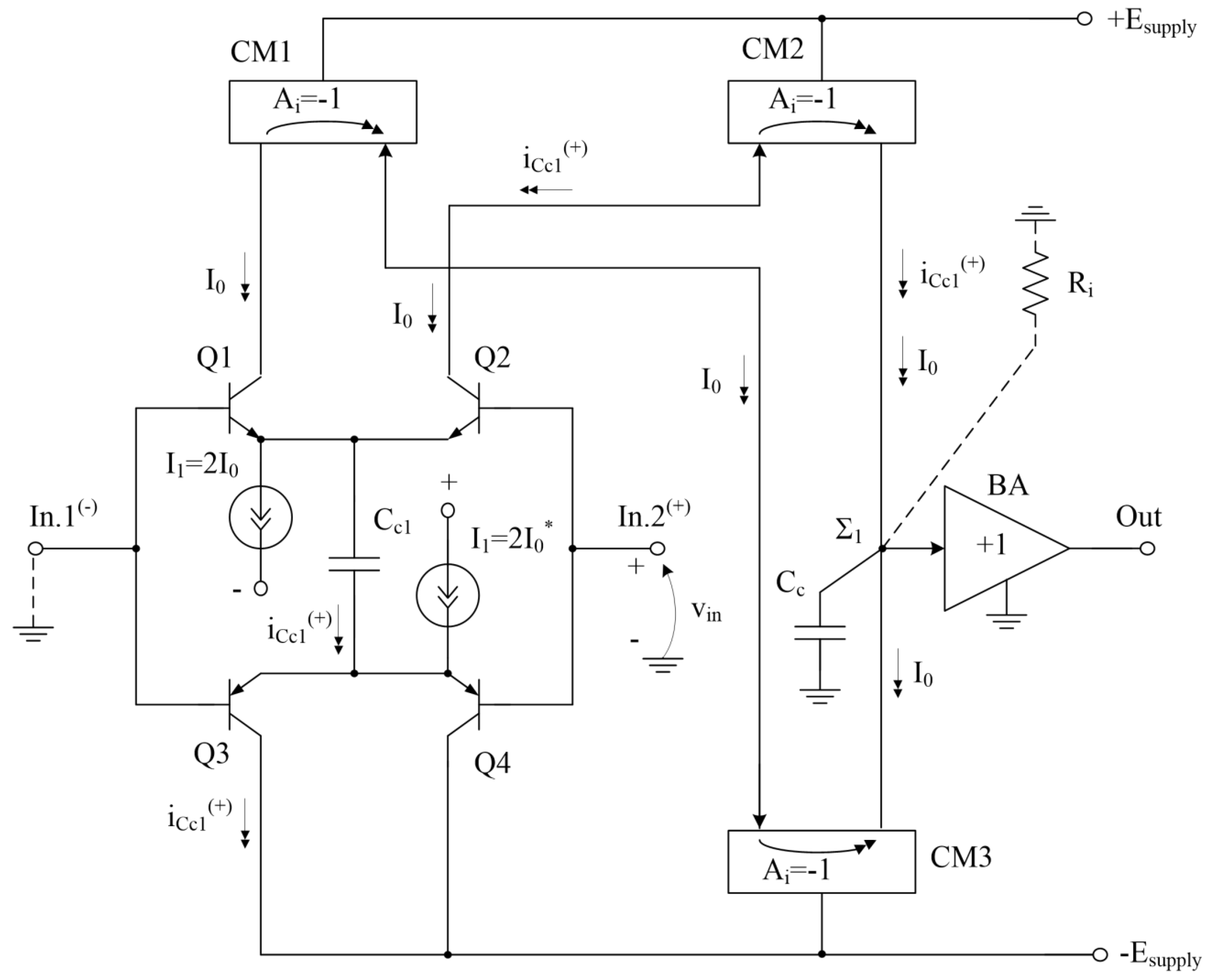

4. Method for limiting the maximum output current in quad-core differential stages

5. Current protection in bridge input stages of high-speed Op-Amps

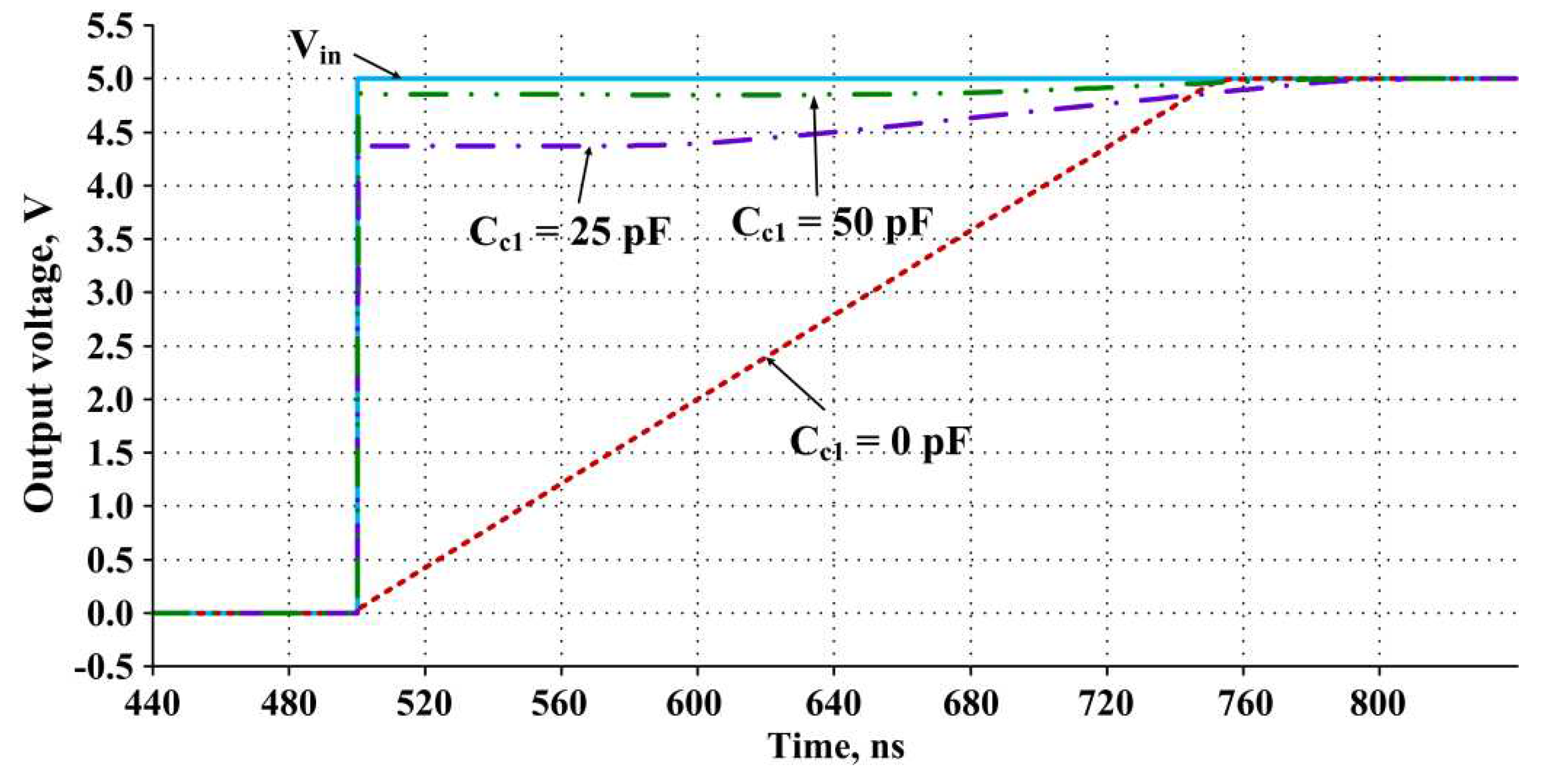

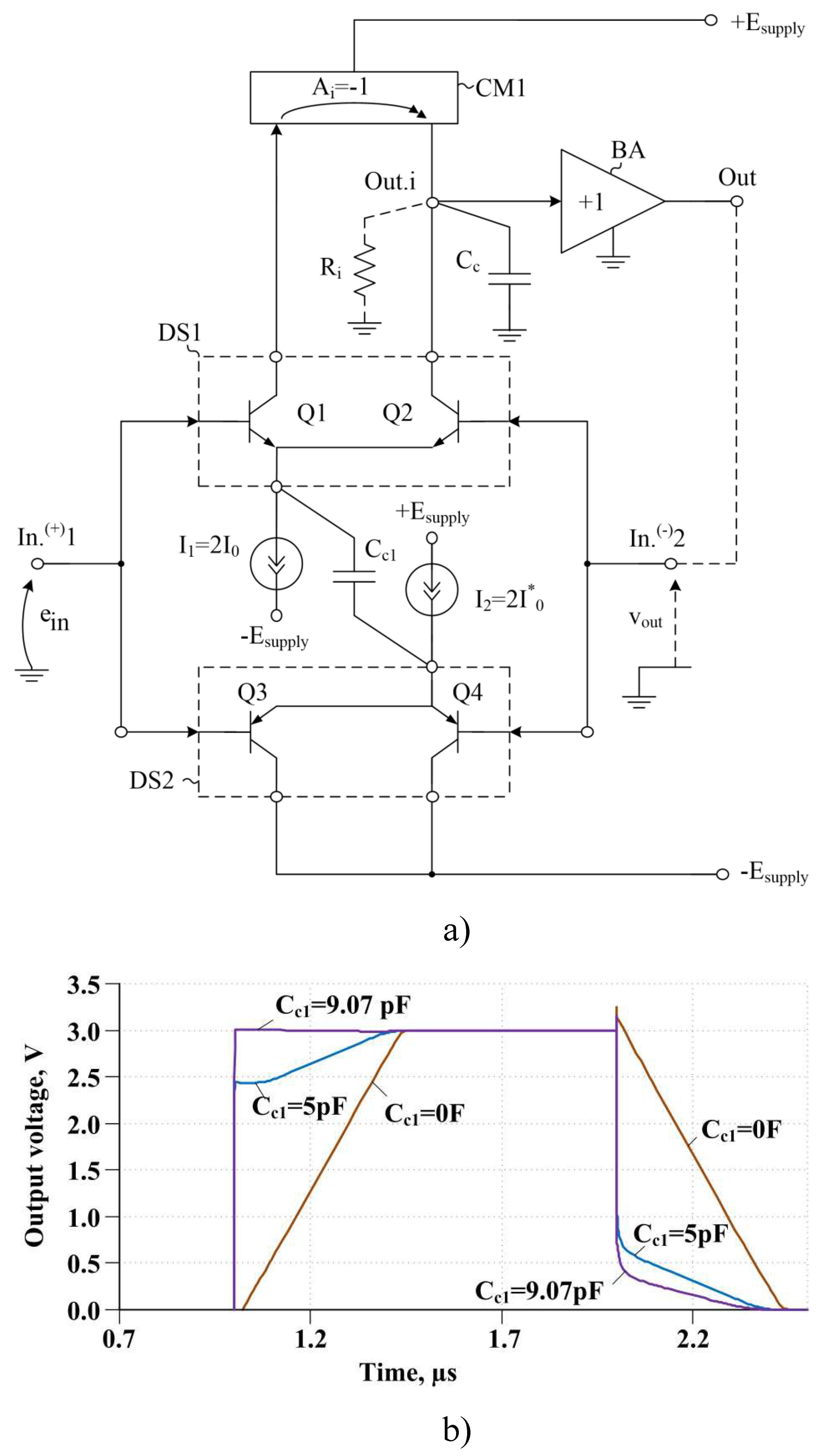

6. Trojan states in Op-Amps with differentiating transient correction circuits in large-signal mode

7. Conclusions

References

- C. Cai and D. Chen, “Performance enhancement induced Trojan states in op-amps, their detection and removal,” 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, Portugal, 2015, pp. 3020–3023. [CrossRef]

- C. Cai and D. Chen, “A slew-rate enhancement technique for fully differential amplifier without inducing Trojan state,” 2015 IEEE 58th International Midwest Symposium on Circuits and Systems (MWSCAS), Fort Collins, CO, USA, 2015, pp. 1–4. [CrossRef]

- A. J. Lopez-Martin, S. Baswa, Jaime Ramirez-Angulo and R. G. Carvajal, “Low-Voltage Super class AB CMOS OTA cells with very high slew rate and power efficiency,” in IEEE Journal of Solid-State Circuits, vol. 40, no. 5, pp. 1068–1077, May 2005. [CrossRef]

- Huang and, D. B. Chen, “A simple slew rate enhancement technique with improved linearity and preserved small signal performance,” 2014 IEEE 57th International Midwest Symposium on Circuits and Systems (MWSCAS), College Station, TX, USA, 2014, pp. 270–273. [CrossRef]

- M. G. Degrauwe, J. Rijmenants, E. A. Vittoz and H. J. De Man, “Adaptive biasing CMOS amplifiers,” in IEEE Journal of Solid-State Circuits, vol. 17, no. 3, pp. 522–528, June 1982. [CrossRef]

- B. W. Lee and B. J. Sheu, “A high slew-rate CMOS amplifier for analog signal processing,” in IEEE Journal of Solid-State Circuits, vol. 25, no. 3, pp. 885–889, June 1990. [CrossRef]

- R. Harjani, R. Heineke and Feng Wang, “An integrated low-voltage class AB CMOS OTA,” in IEEE Journal of Solid-State Circuits, vol. 34, no. 2, pp. 134–142, Feb. 1999. [CrossRef]

- Y. -T. Wang, D. Chen and R. L. Geiger, “Practical methods for verifying removal of Trojan stable operating points,” 2013 IEEE International Symposium on Circuits and Systems (ISCAS), Beijing, China, 2013, pp. 2658–2661. [CrossRef]

- Z. Liu, Y. Li, R. L. Geiger and D. Chen, “Auto-identification of positive feedback loops in multi-state vulnerable circuits,” 2014 IEEE 32nd VLSI Test Symposium (VTS), Napa, CA, USA, 2014, pp. 1–5. [CrossRef]

- Z. Liu, Y. Li, Y. Duan, R. L. Geiger and D. Chen, “Identification and break of positive feedback loops in Trojan States Vulnerable Circuits,” 2014 IEEE International Symposium on Circuits and Systems (ISCAS), Melbourne, VIC, Australia, 2014, pp. 289–292. [CrossRef]

- Y. Li and D. Chen, “Efficient analog verification against Trojan states using divide and contraction method,” 2014 IEEE International Symposium on Circuits and Systems (ISCAS), Melbourne, VIC, Australia, 2014, pp. 281–284. [CrossRef]

- Z. Liu, Y. Li, Y. Duan, R. L. Geiger and D. Chen, “Identification and break of positive feedback loops in Trojan States Vulnerable Circuits,” 2014 IEEE International Symposium on Circuits and Systems (ISCAS), Melbourne, VIC, Australia, 2014, pp. 289–292. [CrossRef]

- A. Catania, M. Cicalini, M. Dei, M. Piotto, P. Bruschi, “Performance Analysis and Design Optimization of Parallel-Type Slew-Rate Enhancers for Switched-Capacitor Applications,” in Electronics, 2020, vol. 9, no. 11, pp. 1949. [CrossRef]

- Q. Wang, R. L. Geiger and D. Chen, “Hardware Trojans embedded in the dynamic operation of analog and mixed-signal circuits,” 2015 National Aerospace and Electronics Conference (NAECON), Dayton, OH, USA, 2015, pp. 155–158. [CrossRef]

- Y. Jin, D. Maliuk, Y. Makris, “Hardware Trojan detection in analog/RF integrated circuits,” in Secure System Design and Trustable Computing, 2016, pp. 241–268. [CrossRef]

- Y. Li and D. Chen, “Efficient analog verification against Trojan states using divide and contraction method,” 2014 IEEE International Symposium on Circuits and Systems (ISCAS), Melbourne, VIC, Australia, 2014, pp. 281–284. [CrossRef]

- A. Antonopoulos, C. Kapatsori and Y. Makris, “Trusted Analog/Mixed- Signal/RF ICs: A Survey and a Perspective,” in IEEE Design & Test, vol. 34, no. 6, pp. 63–76, Dec. 2017. [CrossRef]

- M. M. Alam, S. Chowdhury, B. Park, D. Munzer, N. Maghari, M. Tehranipoor, D. Forte, “Challenges and opportunities in analog and mixed signal (AMS) integrated circuit (IC) security,” in Journal of Hardware and Systems Security, 2018, vol. 2, pp. 15–32. [CrossRef]

- Y. Cao, C. -H. Chang and S. Chen, “A Cluster-Based Distributed Active Current Sensing Circuit for Hardware Trojan Detection,” in IEEE Transactions on Information Forensics and Security, vol. 9, no. 12, pp. 2220–2231, Dec. 2014. [CrossRef]

- M. Onabajo, Y.-B. Kim, “Method to use on-chip temperature sensors for detection of Trojan circuits,” Patent US 10074580, Publicated: Sep. 11, 2018.

- A. Antonopoulos, C. Kapatsori, Y. Makris, “Hardware Trojans in analog, mixed-signal, and RF ICs,” The Hardware Trojan War, Springer, Cham, 2018, pp. 101–123. [CrossRef]

- A. Belous, V. Solodukha, “Main development trends, problems and threats of modern microelectronics,” in Components and Technologies, 2019, no. 10, pp. 6–14. (in Russian)

- E. Kuznetsov, A. Saurov, “Hardware Trojans. Part 1: New threats to cyber security,” in Nanoindustry, 2016, no. 7, pp. 16–25. (in Russian)

- E. Kuznetsov, A. Saurov, “Hardware Trojans. Part 2: Examples of implementation, methods of insertion and activation,” in Nanoindustry, 2016, no. 8 (70), pp. 12–20. (in Russian). [CrossRef]

- E. Kuznetsov, A. Saurov, “Hardware Trojans. Part 3: Methods for prevention and detection,” in Nanoindustry, 2017, no. 1 (71), pp. 30–40. (in Russian). [CrossRef]

- E. Kuznetsov, A. Saurov, “Hardware Trojans. Part 4: Software and hardware countermeasures,” in Nanoindustry, 2017, no. 2 (72), pp. 42–56. (in Russian). [CrossRef]

- N. N. Prokopenko, A. S. Budyakov, “Architecture and circuit design of high-speed operational amplifiers,” SRSUES Publishing House, Shakhty, 2006, 231 p. (in Russian)

- N. N. Prokopenko, “Nonlinear active correction in precision analog microcircuits,” Rostov-on-Don: Publishing house of the North Caucasus Scientific Center of Higher School, 2000, 224 p. (in Russian)

- V. I. Anisimov, M. V. Kapitonov, N. N. Prokopenko, Yu. M. Sokolov, “Operational amplifiers with direct coupling of cascades,” Leningrad, 1979, 148 p. (in Russian)

- R. J. Widlar, “Wide range operational amplifier input stage,” Рatent US 4797629, Publicated: Jan. 10, 1989.

- V.S. Rysin, V.A. Tkachenko, “Operational amplifier,” SU 970638, Publicated: Oct. 30, 1982.

- N. N. Prokopenko, A. S. Budyakov, N. V. Kovbasyuk, “Energy and current limitations for the input stages of operational amplifiers with maximum speed in large signal mode,” Problems of modern analog microcircuitry: materials of the V International Scientific and Practical Seminar, SRSUES Publishing House, Shakhty, 2006. pp. 48–52. (in Russian)

- N. N. Prokopenko, O. V. Dvornikov, V. E. Chumakov, A. V. Bugakova, “Circuit design of high-speed operational amplifiers: monograph,” SOLON-Press, Russia, Moscow, 2023, 248 p. (in Russian)

- C. H. Hung, Y. Zheng, J. Guo and K. N. Leung, “Bandwidth and Slew Rate Enhanced OTA With Sustainable Dynamic Bias,” in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 67, no. 4, pp. 635–639, April 2020. [CrossRef]

- A. J. Lopez-Martin, S. Baswa, Jaime Ramirez-Angulo and R. G. Carvajal, “Low-Voltage Super class AB CMOS OTA cells with very high slew rate and power efficiency,” in IEEE Journal of Solid-State Circuits, vol. 40, no. 5, pp. 1068–1077, May 2005. [CrossRef]

- J. Close, “High speed op amps: Performance, process and topologies,” 2012 IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM), Portland, OR, USA, 2012, pp. 1–8. [CrossRef]

- B. Huang and, D. Chen, “A simple slew rate enhancement technique with improved linearity and preserved small signal performance,” 2014 IEEE 57th International Midwest Symposium on Circuits and Systems (MWSCAS), College Station, TX, USA, 2014, pp. 270–273. [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).