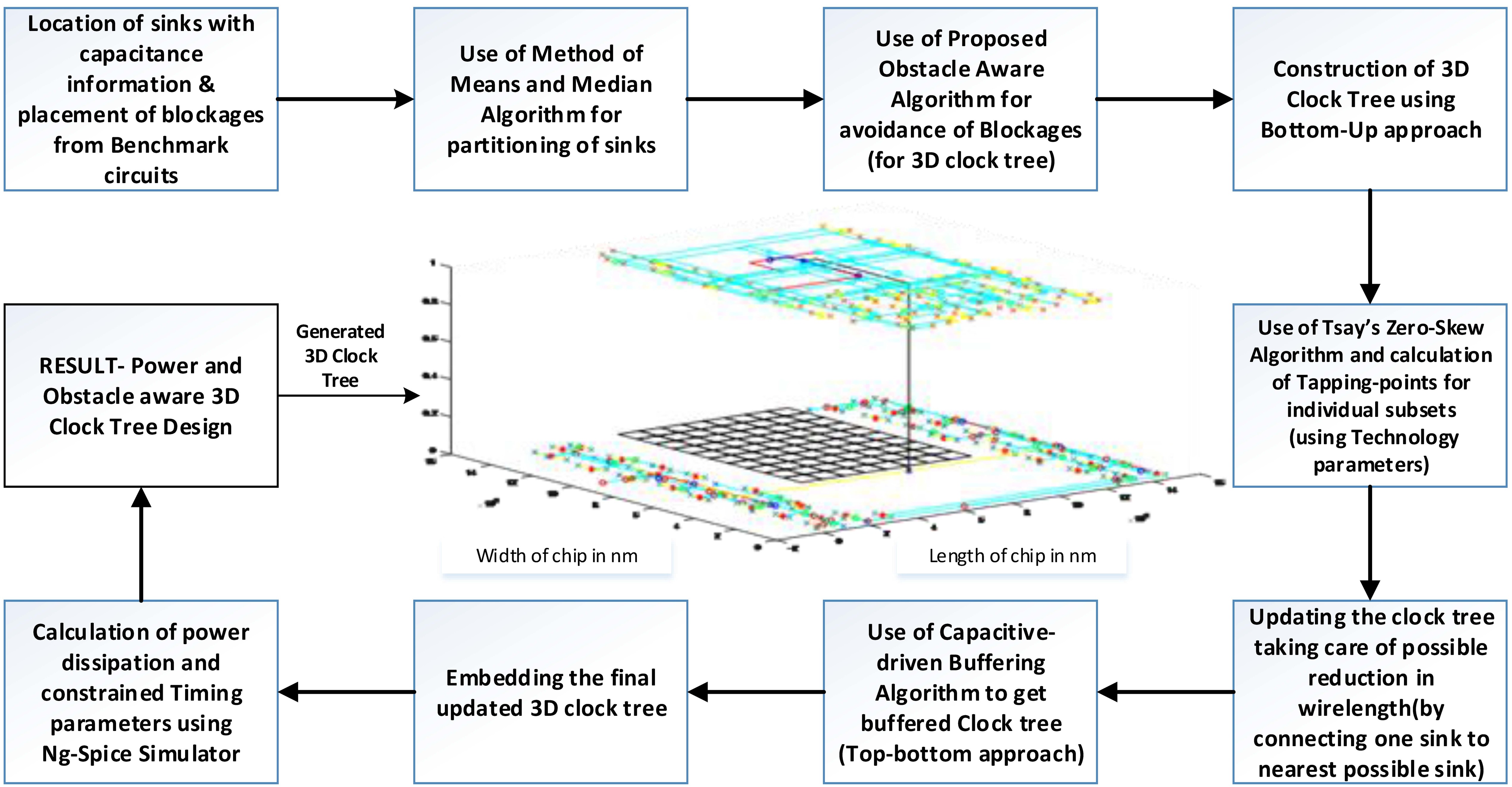

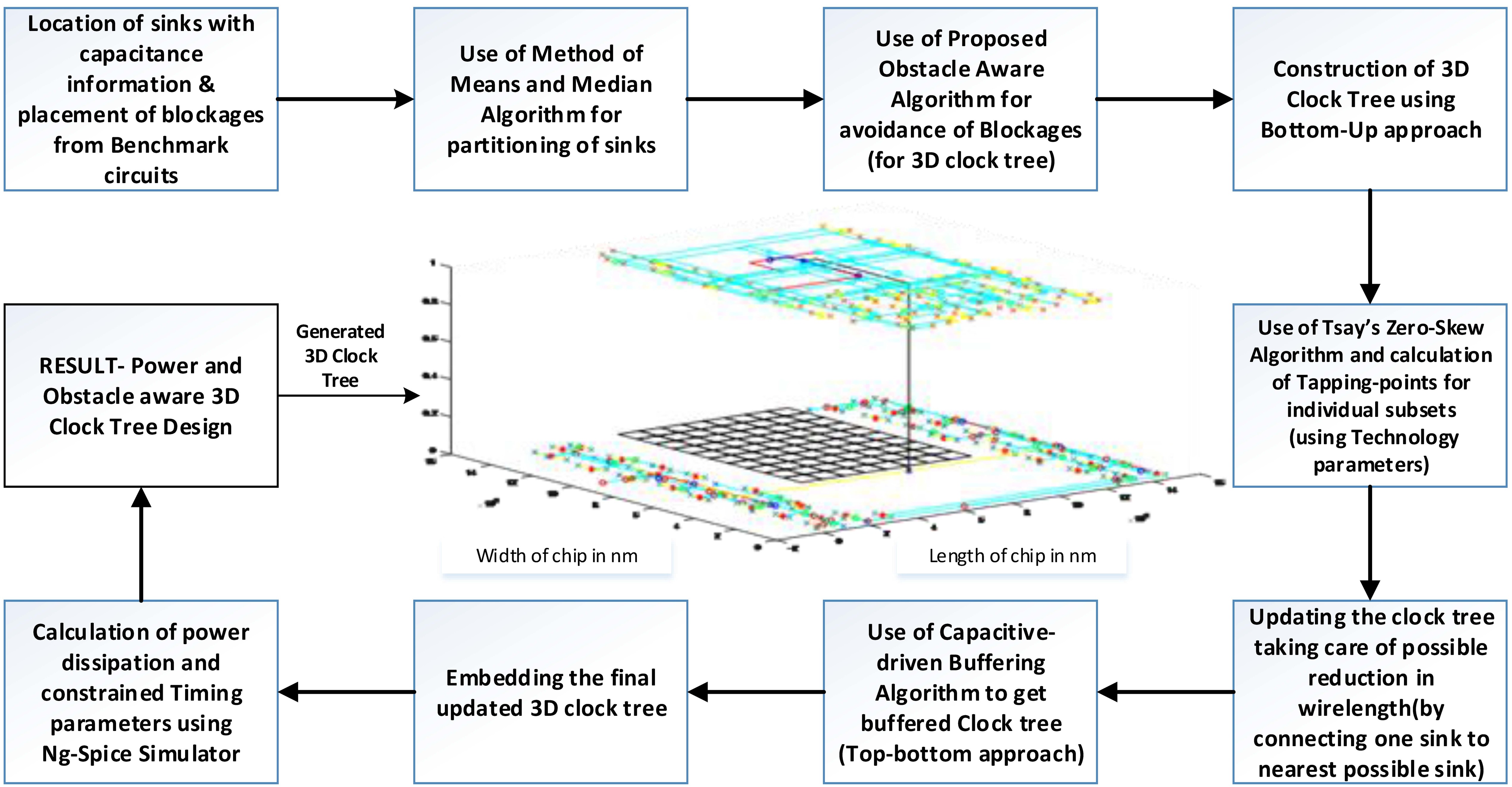

Clock Network Design (CDN) is a critical step while designing any Integrated-Circuits (ICs). It holds vital importance in the performance of entire circuit. Due to continuous scaling, 3D ICs stacked with TSV are gaining importance, with an objective to continue with the Moore's law. Through-Silicon-Via (TSV) provides the vertical interconnection between two die, which allows the electrical signal to flow through it. 3D ICs has many advantages over conventional 2D planar ICs like reduced power, area, cost, wire-length etc. The proposed work is mainly focused on power reduction and obstacle avoidance for 3D ICs. Various techniques have already been introduced for minimizing clock power within specified clock constraints of the 3D CND network. Proposed 3D Clock Tree Synthesis (CTS) is a combination of various algorithms with an objective to meet reduction in power as well as avoidance of obstacle or blockages while routing the clock signal from one sink to other sink. These blockages like RAM, ROM, PLL etc. are fixed during the placement process. The work is carried out mainly in three steps- first is Generation of 3D Clock tree avoiding the blockages, then Buffering and Embedding and finally validating the results by SPICE simulation. The experimental result shows that our CTS approach results in significant 9% reduction in power as compare to the existing work.