Augmented Assembly

The proposed augmentations of assembly language cover all language levels, starting from the lowest level, that of machine language, to levels with a high degree of abstraction. These augmentations provide a greater flexibility of assembly language in operating uniformly with different processor architectures through an easier correlation with lower-level languages (machine code, microcode, etc.) but especially with higher-level languages through similar or complementary augmentations with mid-level [

8] and high-level [

9] languages.

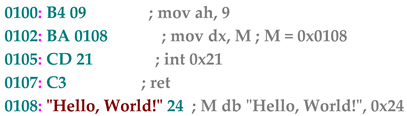

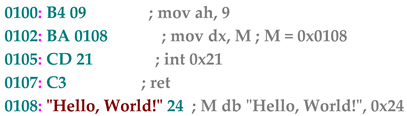

Low-level augmentations involve making machine language operations more flexible to cover the increasing variability of processor architectures through directly including extended machine-level code blocks in assembly language (similar to how the C language allows the inclusion of lower-level code through the asm directive), making machine-level representations a first-class concept. Thus, the machine language is augmented with the acceptance of big-endian descriptions, in addition to the usual little-endian descriptions at the hexadecimal byte level separated by spaces, other bases can also be used, including character/ASCII/256 base (which means a value from 0 to 255 that fits in one byte represented by a character within a string type description) as can be seen in the following example related to the x86 processor family (the simplest, complete and most compact possible code of a "Hello, World!" application written in machine language).

Beyond compatibility with the conventional disassembly outputs, the augmentations allow parameterization for different execution targets (classical CPUs, virtual machines, neural accelerators, quantum devices, etc.) so that “machine” language/code becomes a generalized, extensible notion rather than a processor-specific artifact. This flexibility allow emerging computational paradigms with weight-encoding or gate-encoding requirements to accommodated through the same directive infrastructure through a machine-agnostic facility, treating their "machine code" as specialized encoding domains rather than fundamentally different abstractions.

Data and code level augmentations related to memory space addressing and management through data / code and memory directives must describe memory regions, alignment constraints, symbolic address spaces, and relocation behavior in a processor-agnostic manner, enabling consistent reasoning about layout regardless of target architecture or assembly dialect. However, the different existing assembler dialects require reconcile syntactic variants to ease adoption and interoperability of some usual legacy directives (db, .byte, org, .org, etc.) and treated as syntactic aliases mapped onto a unified semantic core to ensure ecosystem compatibility.

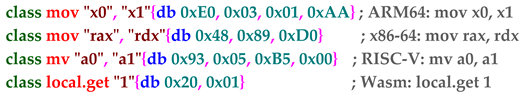

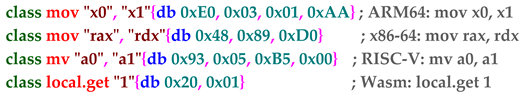

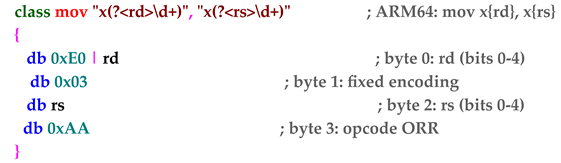

The augmentations at instructions level imply uniformization of common instructions (data movement, arithmetic, control flow, conditional operations, memory access, etc.) with explicitly architecture-independent declared semantics and virtualization or lowering rules for architecture-specific instructions, allowing the source to express intent at the instruction level while still generating correct, architecture-specific encodings. Thus, the generalized instruction representation provides canonical operation names with well-defined semantics while allowing architecture-specific instantiation. In this way, the system handles operand polymorphism (resolve the tension between architectures with explicit operand ordering as Intel vs. AT&T syntax for instance), implicit operands, and architectural variants through a unified descriptive framework. For example, a general move operation with explicit source/destination operand types can instantiate as x86 mov, ARM mov/ldr, RISC-V mv/lw, or WASM local.get, depending on operand characteristics and target architecture. The augmentation handles architectural asymmetries through explicit virtualization: architectures lacking certain instruction categories (e.g., RISC-V's absence of complex addressing modes and implicit flags,) trigger automatic expansion into equivalent sequences or alien to classic assembly (e.g. stack-based WASM instructions also managed as general equivalent register-based instructions). These flexibilities will enable a "write-once, tune-everywhere" workflow, bridges the gap between raw machine control and cross-platform portability.

The Abstract Instruction Set Architecture (A-ISA) represents a necessary unifying architectural level in which the augmentations at the instruction categories level are managed unitarily in a more general/abstract processor mode. Thus, these abstract processor elements such as registers and instructions are referenced through logical roles and indices rather than fixed architectural names. For example, a general-purpose register may be uniformly addressed as r0, whether it maps to r0/x0 on ARM, ax/eax/rax on x86, a0 on RISC-V, or a virtual register in WASM. This abstraction extends beyond registers to include flags, stack models, and calling conventions, enabling consistent expression of low-level logic while deferring architectural specialization to a later translation phase. This architectural level that capture architectural patterns abstractly allows the uniformization of different processor types in a portable way and also to write assembly code that adapts to different instantiations of similar architectural families (e.g., 32-bit versus 64-bit variants, different SIMD widths, etc.). This level truly achieves machine-language portability because it strictly abstracts existing ISA elements rather than replacing them with higher-level constructs, the present augmented assembly representing exactly a true portable assembly language. By contrast, C language eliminates fundamental machine concepts such as explicit conditional jumps and direct control over execution flow, replacing them with semantic abstractions, which is why C is not a truly portable assembly language, despite often being presented as one.

The metaprogramming level augmentations on assembly language consist on a series of parameterization, composition, and controlled expansion with well-defined compile-time text semantics [

6], expressive enough to manage architectural variability, feature selection, and code generation strategies, while remaining predictable and analyzable. These augmentations generalize the usual macros which are simple text substitutions to syntactic and semantic translations through a concept that unites macros, classes, and functions into a more general

class /

macro concept [

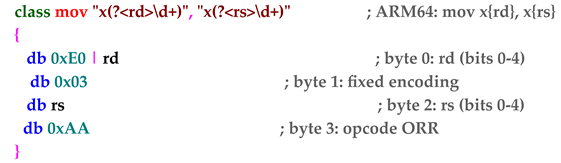

6] which allows explicit expansion rules, parameter evaluation, and conditional logic. These hyper-classes are actually much more flexible macros that can operate over abstract instructions, registers, and architectural features, within text macro-processing. Thus, these facilities will allow easy abstractions at any of the levels presented previously, as can be seen in the following examples of direct explicit definition of some instructions:

Along with the power of syntactic and semantic abstraction, metaprogramming augmentations will also allow compile-time (assembly-time) control constructs of the assembler to reason about target capabilities, select appropriate instruction forms, and generate consistent code paths without external processing or code generation tools.

High level augmentations include lexical, syntactic, and semantic analysis mechanisms, enabling it both to bootstrap its own compiler/assembler and also to process high-level structured code according to user-defined syntaxes specific to some high-level language (as for libraries implementations, etc.) as well as the management of natural language descriptions, AI routines directly related to hardware infrastructure, etc. Assembly language obtains in this way a controlled path to higher-level abstractions, without abandoning its low-level foundations, through: pattern matching, tokenization, parsing primitives, code generation, etc. Thus, RegExp (Regular Expressions) can be used in various areas, including in hyper-classes at the argument level to build instruction templates, as in the following example

where RegExp rules can be even more precise with

(\d|[

12]

\d|30) instead of

\d+ or can be supplemented by an assertion

and a message

"Register out of range", etc. Similarly, syntactic and semantic tools can be used within the language, thus facilitating representations that resemble high-level languages and providing a descriptive framework across computational paradigms by incorporate naturally at low-level (where are there major differences) non-traditional architectures, including neural, AI-based systems, quantum models, etc.

Although historically assembly language introduced the first level of abstraction over machine language, it has remained indispensable for the precise description of processor-level instructions in critical areas of programming instruments. Assembly language continues to be the point at which executable code debugging, reverse engineering and disassembly-based decompilation processes typically terminate, as up to assembly level translations to/from machine language can still be considered reversible. Assembly augmentations enable direct, powerful and concise abstractions that closely reflect the underlying execution model, allowing explicit control over registers, memory layout, instruction sequencing, and processor-specific features that are often inaccessible or deliberately hidden in high-level languages. This direct expressiveness makes assembly uniquely suited for defining a universal, architecture-aware intermediate representation, capable of faithfully modeling execution semantics while remaining close enough to hardware to expose optimization opportunities, non-standard instructions, and specialized execution patterns that cannot be reliably expressed elsewhere in higher level languages which have already become inefficient in integrating different architectures without implementation critical libraries in lower-level languages.

and a message "Register out of range", etc. Similarly, syntactic and semantic tools can be used within the language, thus facilitating representations that resemble high-level languages and providing a descriptive framework across computational paradigms by incorporate naturally at low-level (where are there major differences) non-traditional architectures, including neural, AI-based systems, quantum models, etc.

and a message "Register out of range", etc. Similarly, syntactic and semantic tools can be used within the language, thus facilitating representations that resemble high-level languages and providing a descriptive framework across computational paradigms by incorporate naturally at low-level (where are there major differences) non-traditional architectures, including neural, AI-based systems, quantum models, etc.