Submitted:

20 November 2025

Posted:

21 November 2025

You are already at the latest version

Abstract

Keywords:

1. Introduction

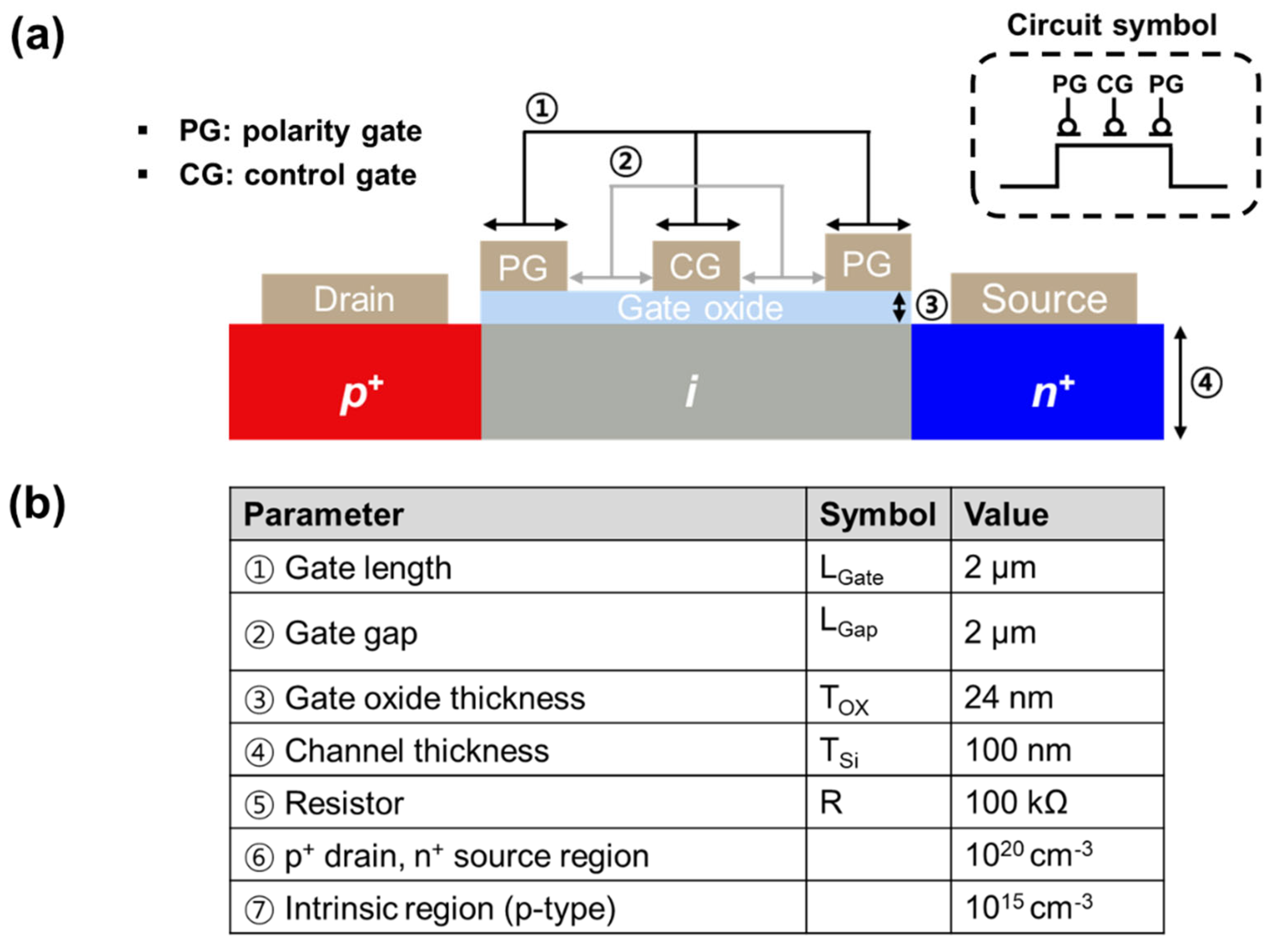

2. Materials and Methods

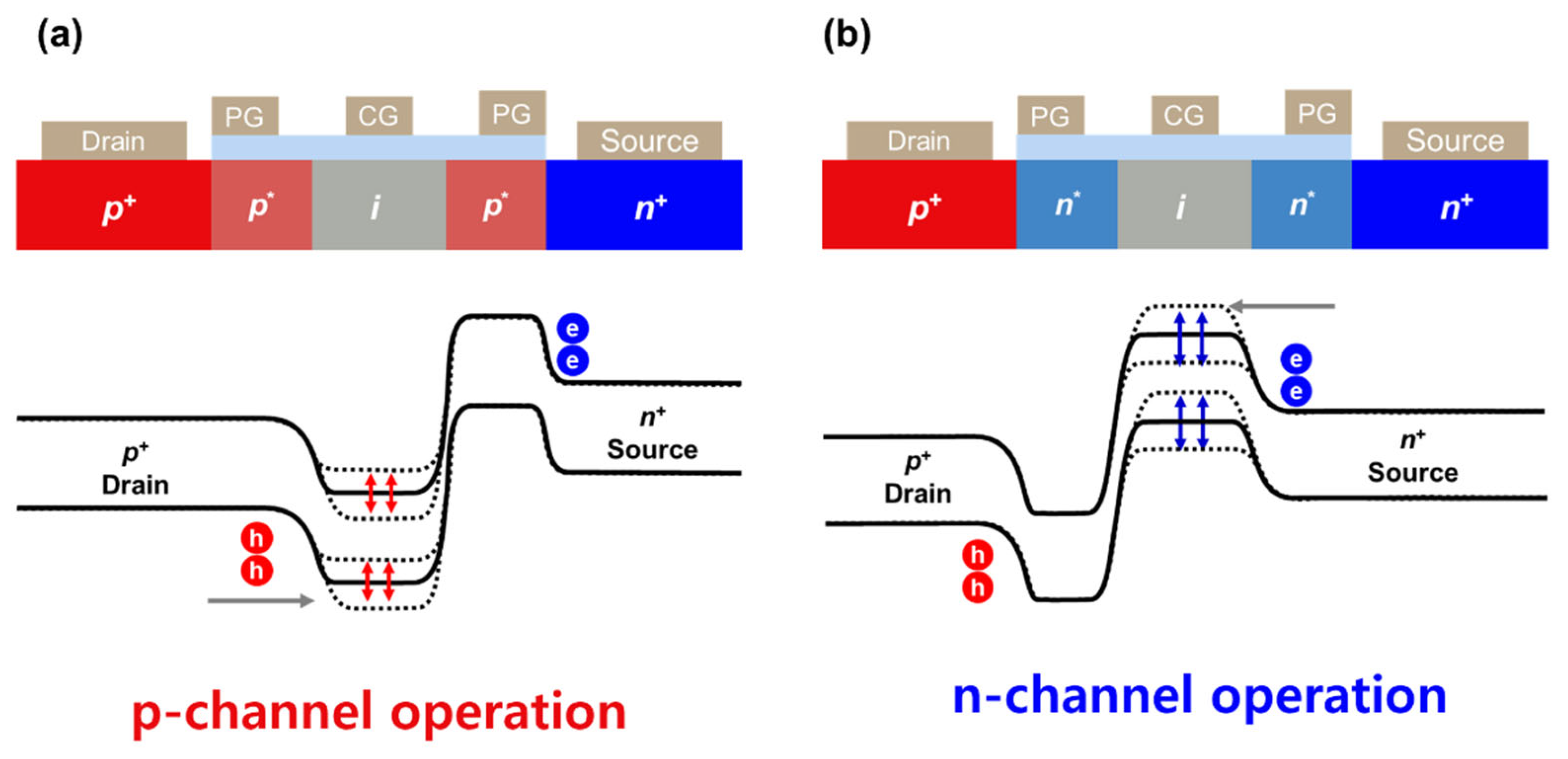

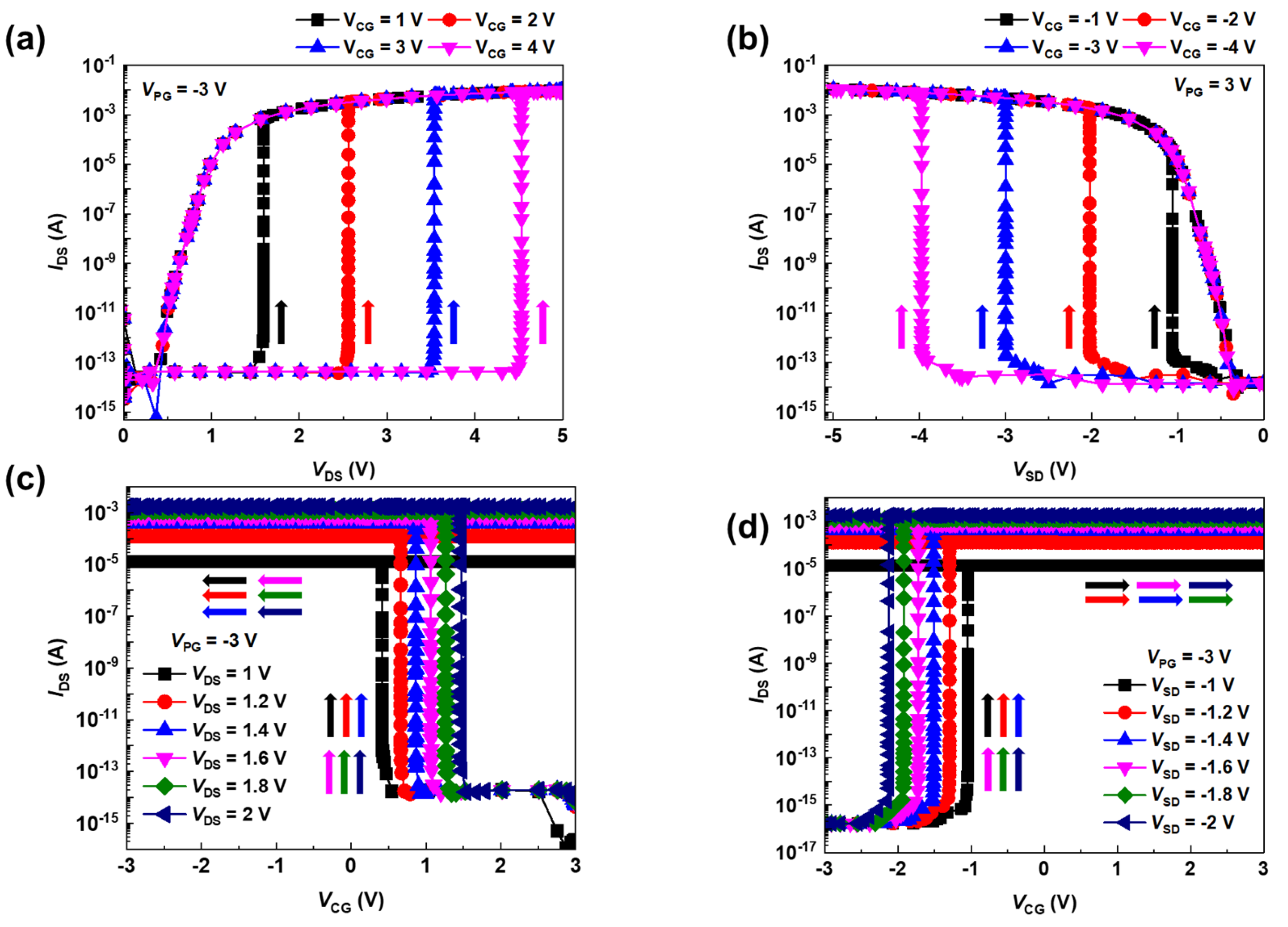

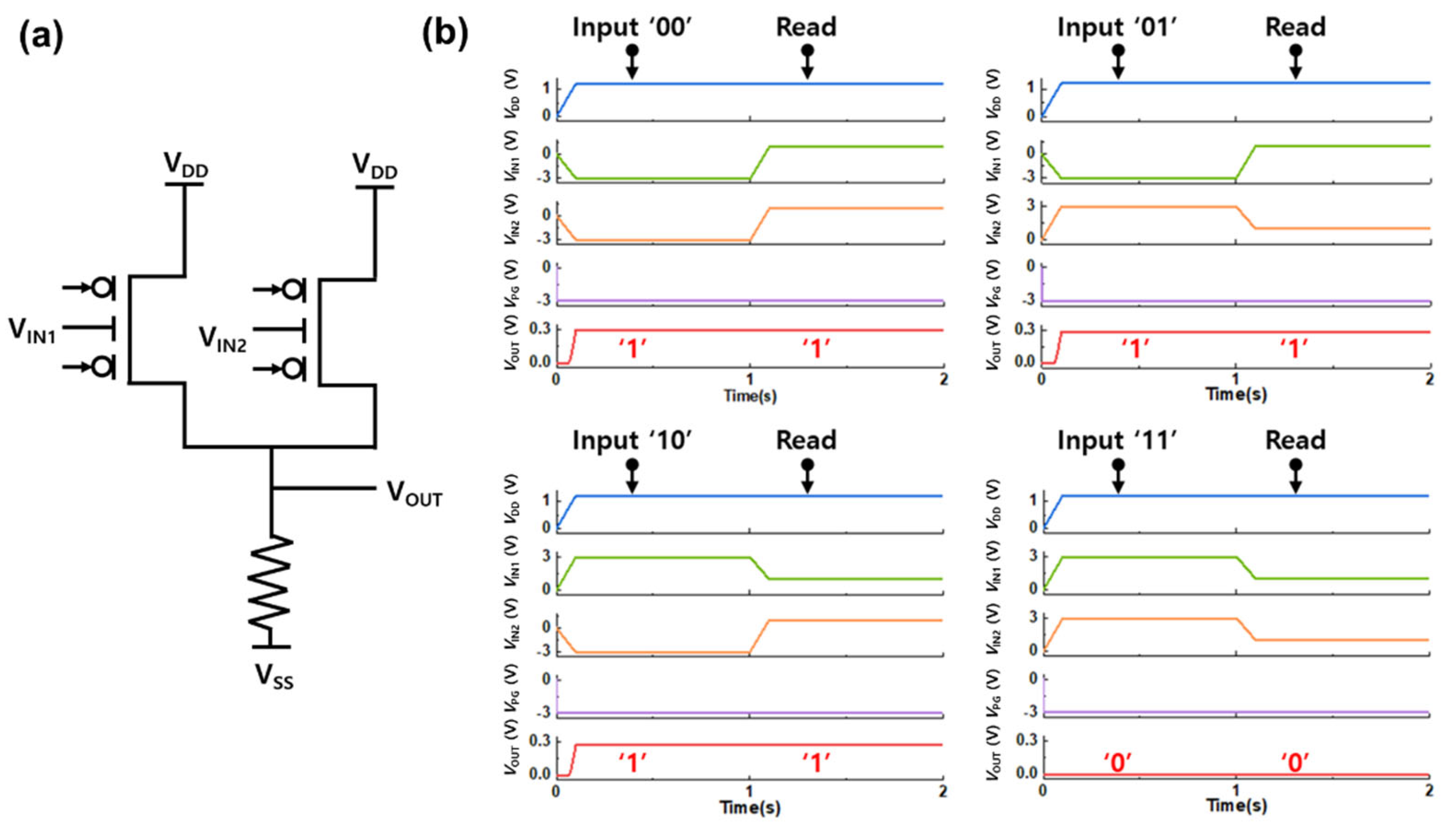

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| BGN | Bandgap narrowing |

| CG | Control gate |

| FBFET | Feedback field-effect transistor |

| LIM | Logic-in-memory |

| PG | Polarity gate |

| SS | Subthreshold swing |

| TCAD | Technology computer-aided design |

References

- Kudithipudi, D.; Schuman, C.; Vineyard, C.M.; Pandit, T.; Merkel, C.; Kubendran, R.; Aimone, J.B.; Orchard, G.; Mayr, C.; Benosman, R.; et al. Neuromorphic Computing at Scale. Nature 2025, 637, 801–812. [Google Scholar] [CrossRef] [PubMed]

- Ghose, S.; Boroumand, A.; Kim, J.S.; Gómez-Luna, J.; Mutlu, O. Processing-in-Memory: A Workload-Driven Perspective. IBM J. Res. Dev. 2019, 63, 3–1. [Google Scholar] [CrossRef]

- Asifuzzaman, K.; Miniskar, N.R.; Young, A.R.; Liu, F.; Vetter, J.S. A Survey on Processing-in-Memory Techniques: Advances and Challenges. Memories - Mater. Devices, Circuits Syst. 2023, 4, 100022. [Google Scholar] [CrossRef]

- Wang, C.; Shi, G.; Qiao, F.; Lin, R.; Wu, S.; Hu, Z. Research Progress in Architecture and Application of RRAM with Computing-in-Memory. Nanoscale Adv. 2023, 5, 1559–1573. [Google Scholar] [CrossRef] [PubMed]

- Zahoor, F.; Hussin, F.A.; Isyaku, U.B.; Gupta, S.; Khanday, F.A.; Chattopadhyay, A.; Abbas, H. Resistive Random Access Memory: Introduction to Device Mechanism, Materials and Application to Neuromorphic Computing. Discov. nano 2023, 18, 36. [Google Scholar] [CrossRef] [PubMed]

- Chen, J.; Zhao, W.; Wang, Y.; Shu, Y.; Jiang, W.; Ha, Y. A Reliable 8T SRAM for High-Speed Searching and Logic-in-Memory Operations. IEEE Trans. Very Large Scale Integr. Syst. 2022, 30, 769–780. [Google Scholar] [CrossRef]

- Lee, C.; Shin, C. Study on Various Device Structures for Steep-Switching Silicon-on-Insulator Feedback Field-Effect Transistors. IEEE Trans. Electron Devices 2020, 67, 1852–1858. [Google Scholar] [CrossRef]

- Katta, S.S.; Kumari, T.; Srinivas, P.S.T. .; Tiwari, P.K. Logic-in-Memory Application of Silicon Nanotube-Based FBFET with Core-Source Architecture. Microelectronics J. 2024, 146, 106133. [Google Scholar] [CrossRef]

- Lim, E.; Son, J.; Cho, K.; Kim, S. Logic and Memory Characteristics of an Inverter Comprising a Feedback FET and a MOSFET. Semicond. Sci. Technol. 2022, 37, 65025. [Google Scholar] [CrossRef]

- Lim, D.; Cho, K.; Kim, S. Single Silicon Neuron Device Enabling Neuronal Oscillation and Stochastic Dynamics. IEEE Electron Device Lett. 2021, 42, 649–652. [Google Scholar] [CrossRef]

- Lee, C.; Sung, J.; Shin, C. Understanding of Feedback Field-Effect Transistor and Its Applications. Appl. Sci. 3070. [CrossRef]

- Kim, Y.; Cho, J.; Lim, D.; Woo, S.; Cho, K.; Kim, S. Switchable-Memory Operation of Silicon Nanowire Transistor. Adv. Electron. Mater. 2018, 1800429, 1–7. [Google Scholar] [CrossRef]

- Lim, D.; Cho, K.; Kim, S. Reconfigurable Logic-in-Memory Using Silicon Transistors. Adv. Mater. Technol. 2022, 7, 2101504. [Google Scholar] [CrossRef]

- Lim, D.; Son, J.; Cho, K.; Kim, S. Quasi-nonvolatile Silicon Memory Device. Adv. Mater. Technol. 2020, 5, 2000915. [Google Scholar] [CrossRef]

- Lim, D.; Kim, S. Polarity Control of Carrier Injection for Nanowire Feedback Field-Effect Transistors. Nano Res. 2019, 12, 2509–2514. [Google Scholar] [CrossRef]

- Physics and Properties of Semiconductors—A Review. In Physics of Semiconductor Devices; 2006; pp. 5–75 ISBN 9780470068328.

- Lombardi, C.; Manzini, S.; Saporito, A.; Vanzi, M. A Physically Based Mobility Model for Numerical Simulation of Nonplanar Devices. IEEE Trans. Comput. Des. Integr. Circuits Syst. 1988, 7, 1164–1171. [Google Scholar] [CrossRef]

- Canali, C.; Majni, G.; Minder, R.; Ottaviani, G. Electron Drift Velocity in Silicon. Phys. Rev. B 1975, 12, 2265–2284. [Google Scholar] [CrossRef]

- Slotboom, J.W.; de Graaff, H.C. Measurements of Bandgap Narrowing in Si Bipolar Transistors. Solid. State. Electron. 1976, 19, 857–862. [Google Scholar] [CrossRef]

- Dziewior, J.; Schmid, W. Auger Coefficients for Highly Doped and Highly Excited Silicon. Appl. Phys. Lett. 1977, 31, 346–348. [Google Scholar] [CrossRef]

- Klaassen, D.B.M. A Unified Mobility Model for Device Simulation—Part I: Model Equations and Concentration Dependence. Solid. State. Electron. 1992, 35, 953–959. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).