Submitted:

12 November 2025

Posted:

17 November 2025

You are already at the latest version

Abstract

Keywords:

1. Introduction

- -

- voltage asymmetry in the collector–base bias conditions of the dominant transistor pair;

- -

- internal feedback factors in transistors caused by the Early effect;

- -

- base current gain coefficients (β) of bipolar transistors, which in many cases have relatively low values (β=50-200).

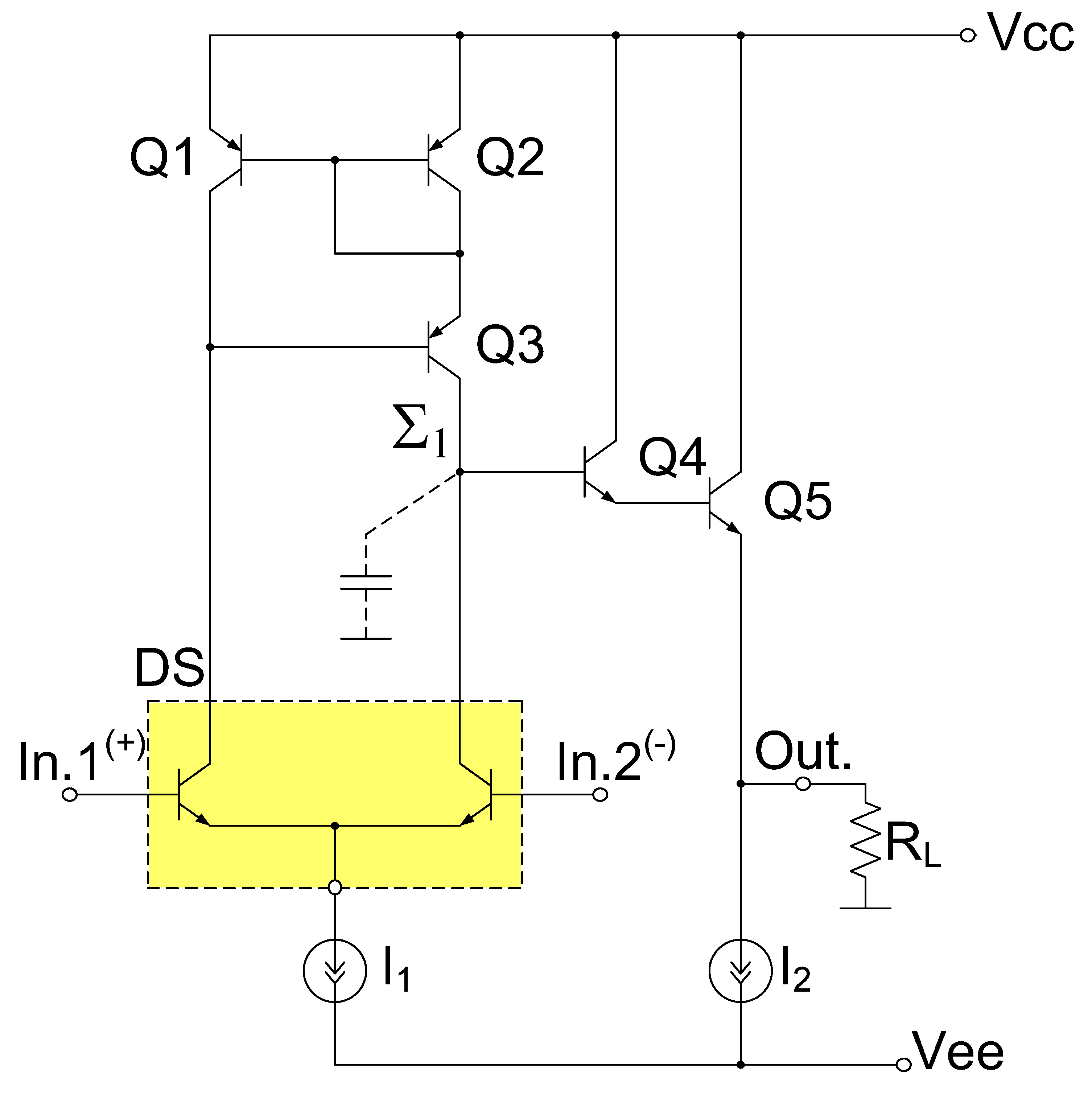

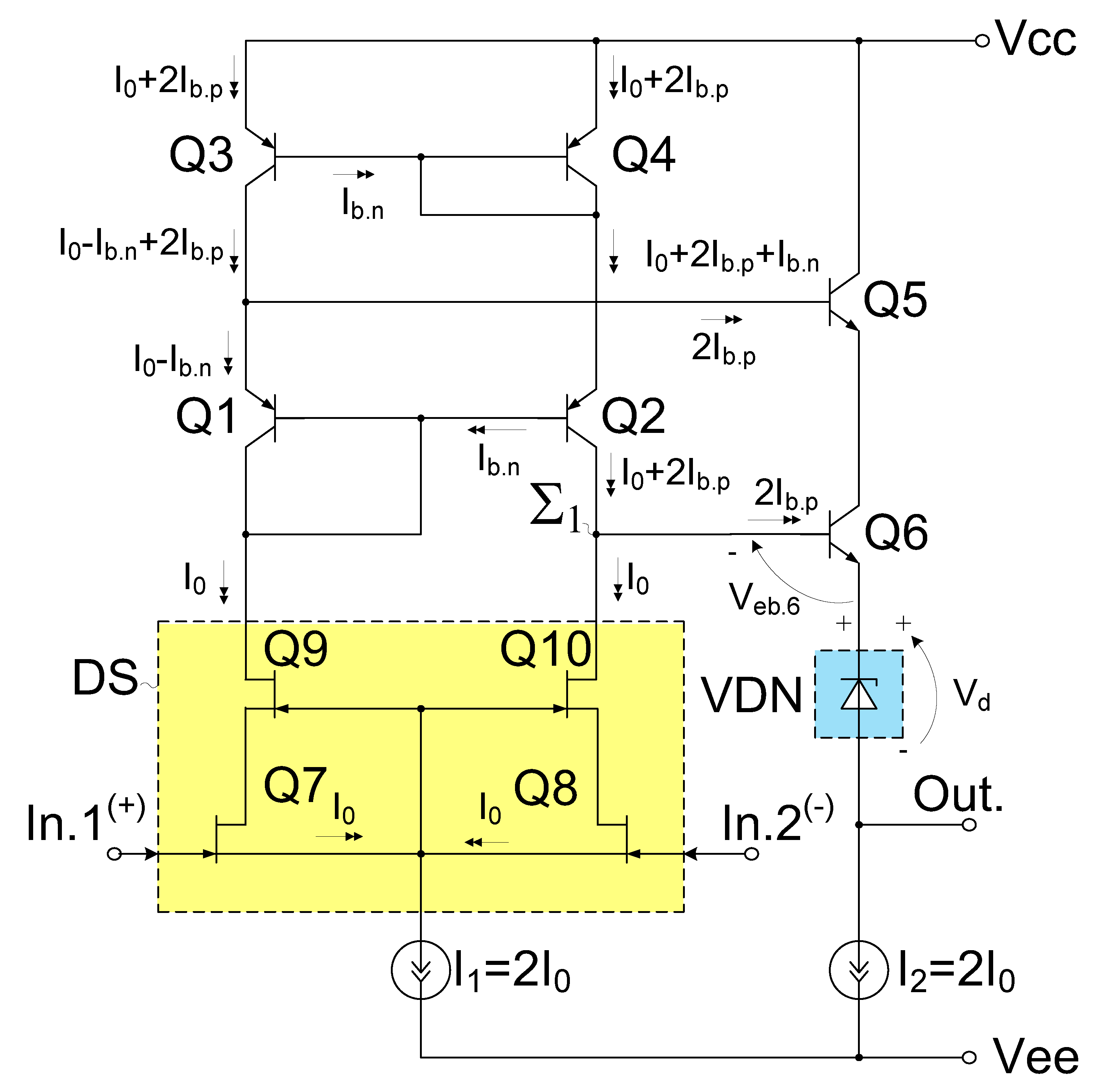

2. Analysis of the Basic Scheme of the Proposed Op Amp

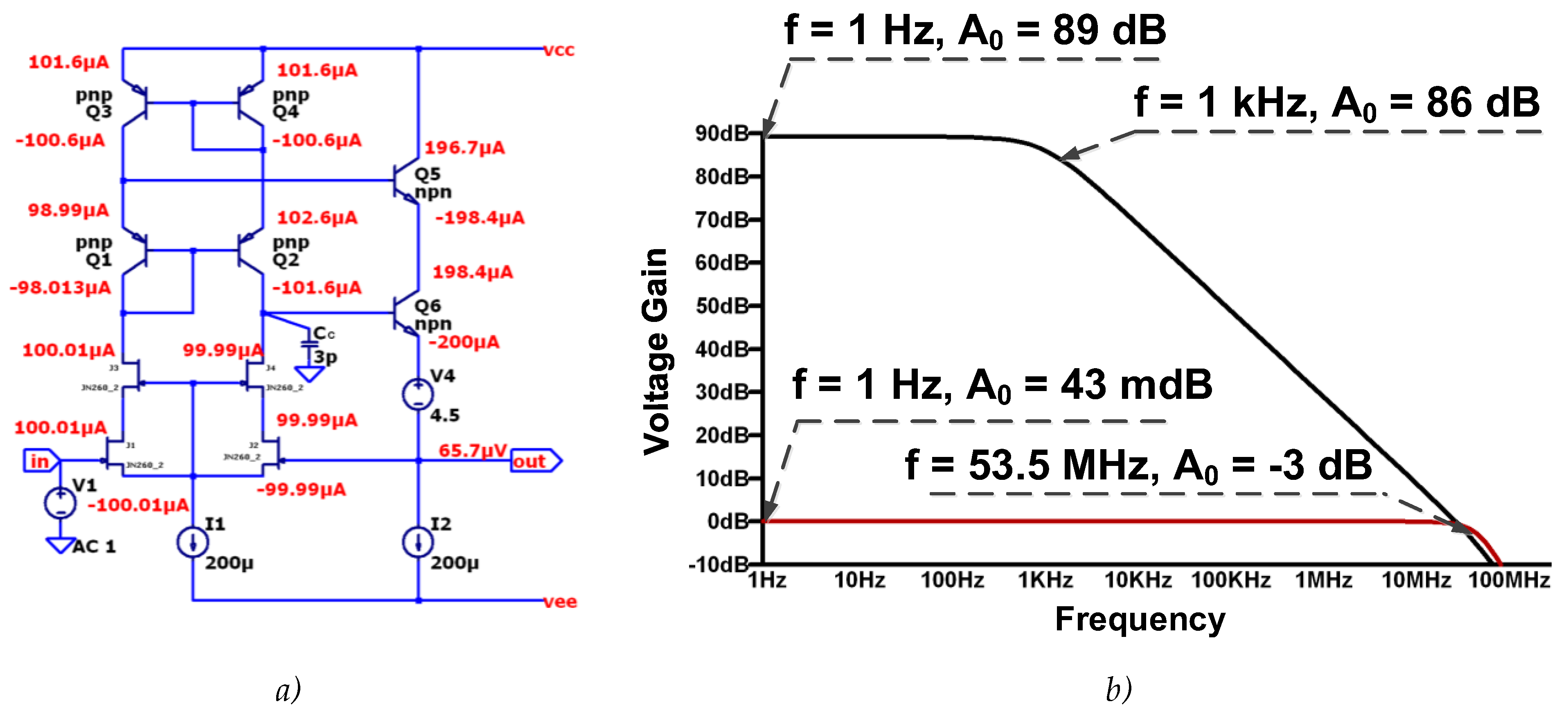

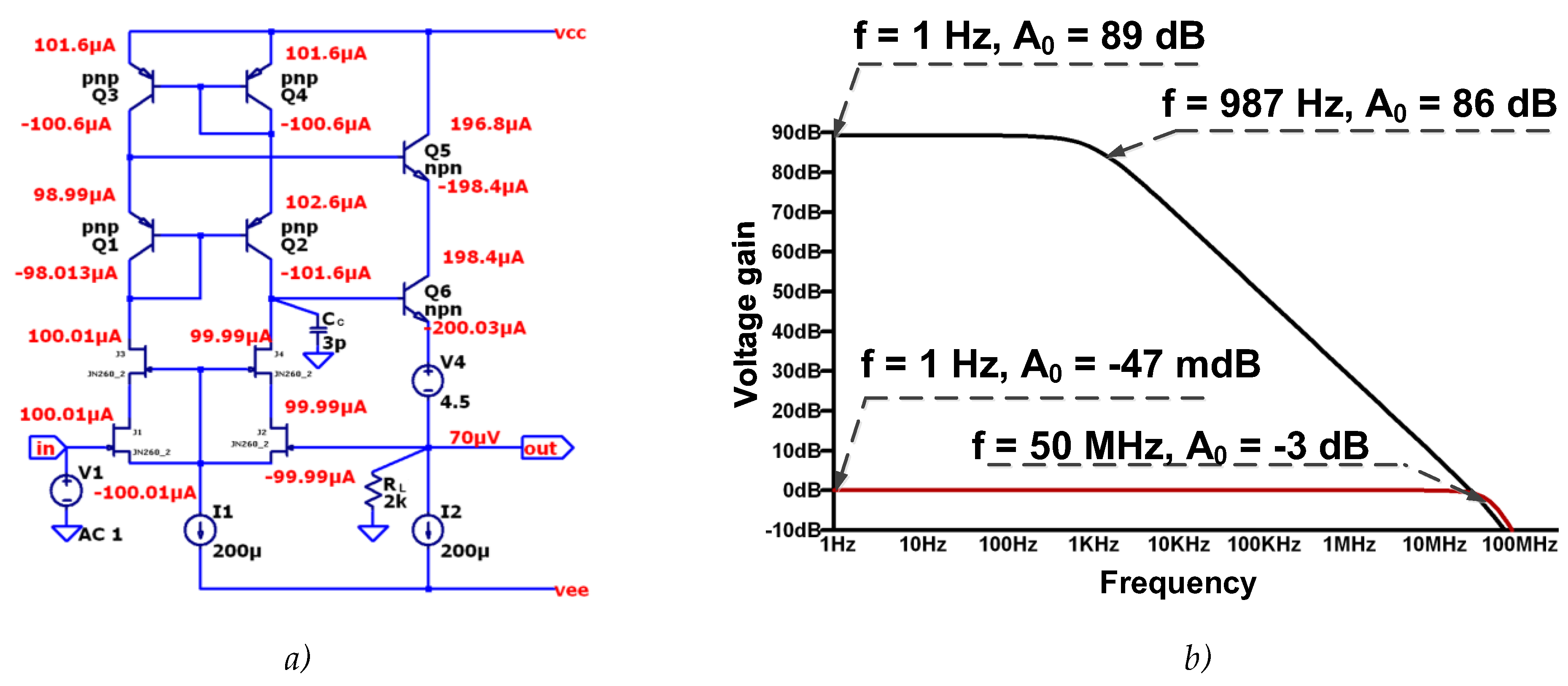

3. Results of Computer Simulation

4. Conclusion

References

- Carter, B., & Mancini, R. Op Amps for Everyone. Translated from English by A. N. Rabodzey. Moscow: Dodeka-XXI, 2011. 544 p. (Schematic Design Series). Includes English title page. ISBN 978-5-94120-242-3.

- Borkar; Shekhar Y. et al. Transistor group mismatch detection and reduction. US Patent 6272666, 2001-08-07.

- Hart; Michael L. et al. Method and apparatus for compensating for process variations. US Patent 7453311, 2008-11-18.

- Horowitz, P., & Hill, W. The Art of Electronics. 2nd ed. Translated from English. Moscow: BINOM Publishing, 2014. 704 p.

- Bugakova, A. V., Prokopenko, N. N., Dvornikov, O. V., & Drozdov, D. G. Differential Amplifier Based on Complementary Junction Field-Effect Transistors. Patent RF No. 2736412, Int. Cl. H03F 3/34, H03F 3/45; application No. 2020115040/08; filed April 29, 2020; published November 17, 2020, Bull. No. 32. Applicant: Don State Technical University (DSTU).

- Prokopenko, N. N., Dvornikov, O. V., & Pakhomov, I. V. Input Differential Stage Based on Complementary Junction Field-Effect Transistors for Low-Temperature Operation. Patent RF No. 2712416, Int. Cl. H03F 3/00; application No. 2019122270/08; filed July 16, 2019; published January 28, 2020, Bull. No. 4. Applicant: Don State Technical University (DSTU).

- Chumakov, V. E., Prokopenko, N. N., Kunts, A. V., & Bugakova, A. V. Differential Amplifier Based on Gallium Arsenide Field-Effect Transistors. Patent RF No. 2770912, Int. Cl. H03F 3/45; application No. 2021129177; filed October 6, 2021; published April 25, 2022, Bull. No. 12. Applicant: Don State Technical University (DSTU).

- Sergeenko, M. A., Chumakov, V. E., Dvornikov, O. V., & Prokopenko, N. N. Precision Gallium Arsenide Operational Amplifier with Low Systematic Input Offset Voltage and High Voltage Gain. Patent RF No. 2813370, Int. Cl. H03F 3/45; application No. 2023130248; filed November 21, 2023; published February 12, 2024, Bull. No. 5. Applicant: Don State Technical University (DSTU).

- Prokopenko, N. N., Dvornikov, O. V., Bugakova, A. V., & Pakhomov, I. V. Differential Operational Amplifier. Patent RF No. 2616573, Int. Cl. H03F 3/45; application No. 2015149078/08; filed November 16, 2015; published April 17, 2017, Bull. No. 11. Applicant: Don State Technical University (DSTU).

- Bugakova, A. V., Zhuk, A. A., & Prokopenko, N. N. Differential Amplifier Based on Complementary Junction Field-Effect Transistors. Patent RF No. 2688225, Int. Cl. H03F 3/34, H03F 3/45; application No. 2018126843/08; filed July 23, 2018; published May 21, 2019, Bull. No. 15. Applicant: Don State Technical University (DSTU).

- Prokopenko, N. N., Zhuk, A. A., Bugakova, A. V., & Pakhomov, I. V. Differential Stage Based on Complementary JFETs with Enhanced Common-Mode Input Signal Rejection. Patent RF No. 2710296, Int. Cl. H03F 1/00, H03F 3/34; application No. 2019131161/08; filed October 3, 2019; published December 25, 2019, Bull. No. 36. Applicant: Don State Technical University (DSTU).

- Prokopenko, N. N., Budyakov, P. S., & Pakhomov, I. V. Differential Amplifier Based on Complementary Field-Effect Transistors with Improved DC Operating Point Stability. Patent RF No. 2710930, Int. Cl. H03F 3/34, H03F 3/45; application No. 2019122165/08; filed July 15, 2019; published January 14, 2020, Bull. No. 2. Applicant: Don State Technical University (DSTU).

- Prokopenko, N. N., Drozdov, D. G., & Zhuk, A. A. Class AB Differential Stage Based on Complementary Junction Field-Effect Transistors for Low-Temperature Operation. Patent RF No. 2710847, Int. Cl. H03F 3/34; application No. 2019126326/08; filed August 21, 2019; published January 14, 2020, Bull. No. 2. Applicant: Don State Technical University (DSTU).

- Pakhomov, I. V., Titov, A. E., Chumakov, V. E., & Prokopenko, N. N. Precision Operational Amplifier Based on Complementary Bipolar and Input Junction Field-Effect Transistors. Russian Patent Application No. 2025128076, filed October 08, 2025.

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).