Submitted:

02 September 2025

Posted:

03 September 2025

Read the latest preprint version here

Abstract

Keywords:

1. Introduction

2. Fundamentals of Embedded Logging System Technology

3. Embedded Linux-Based Low-Power Persistent Logging System Design

3.1. Log Capture

3.2. Log Persistence Mechanism

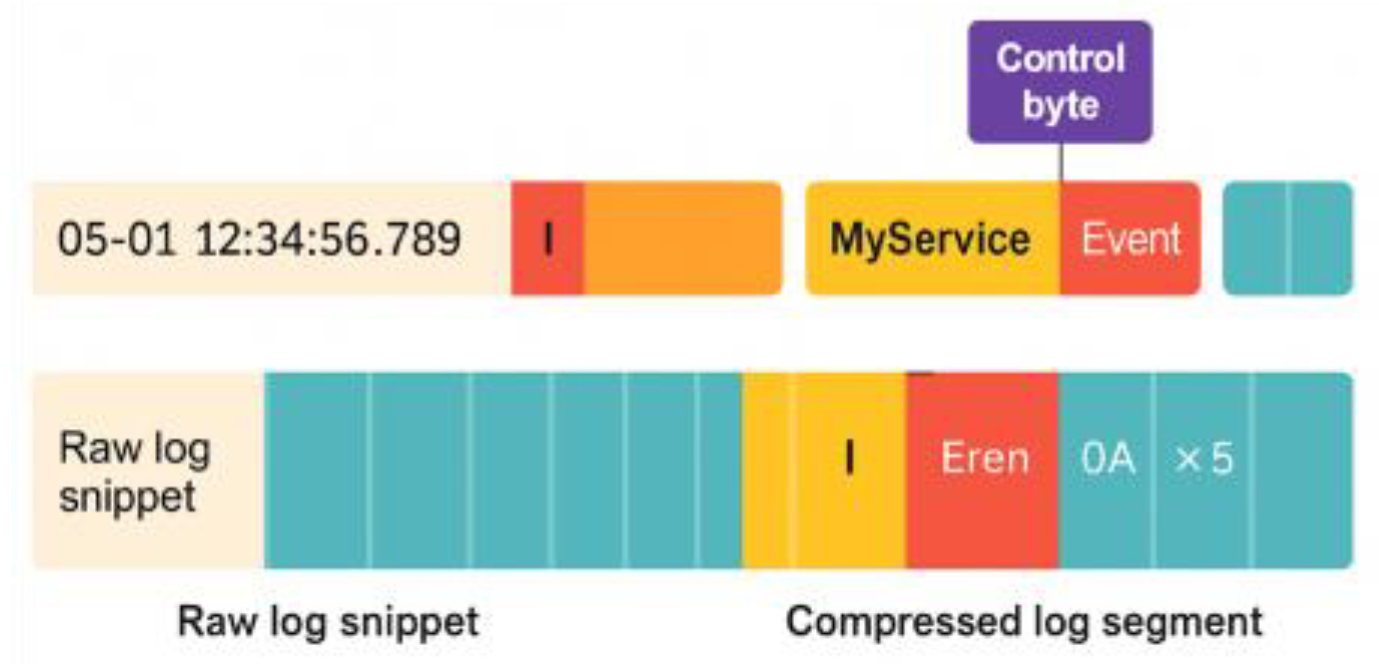

3.3. Log Compression and Storage

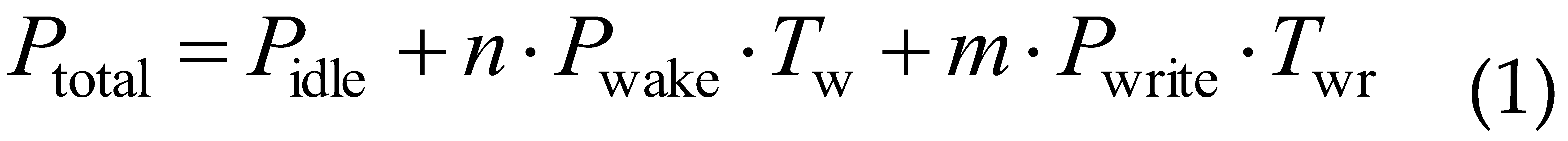

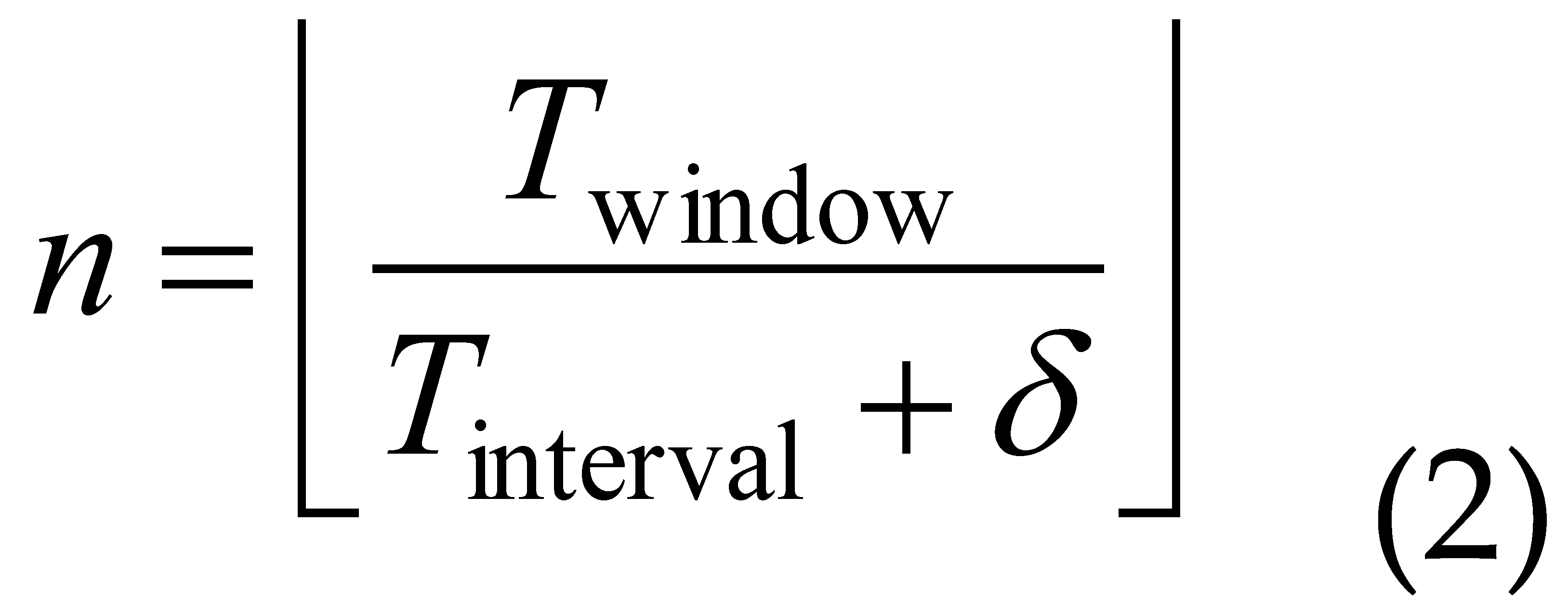

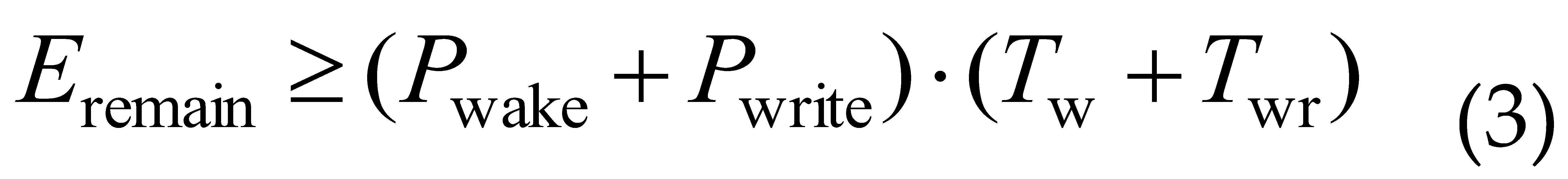

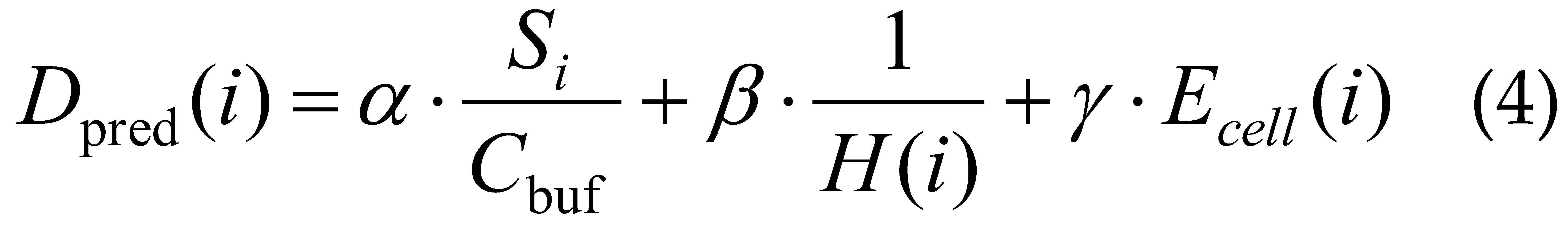

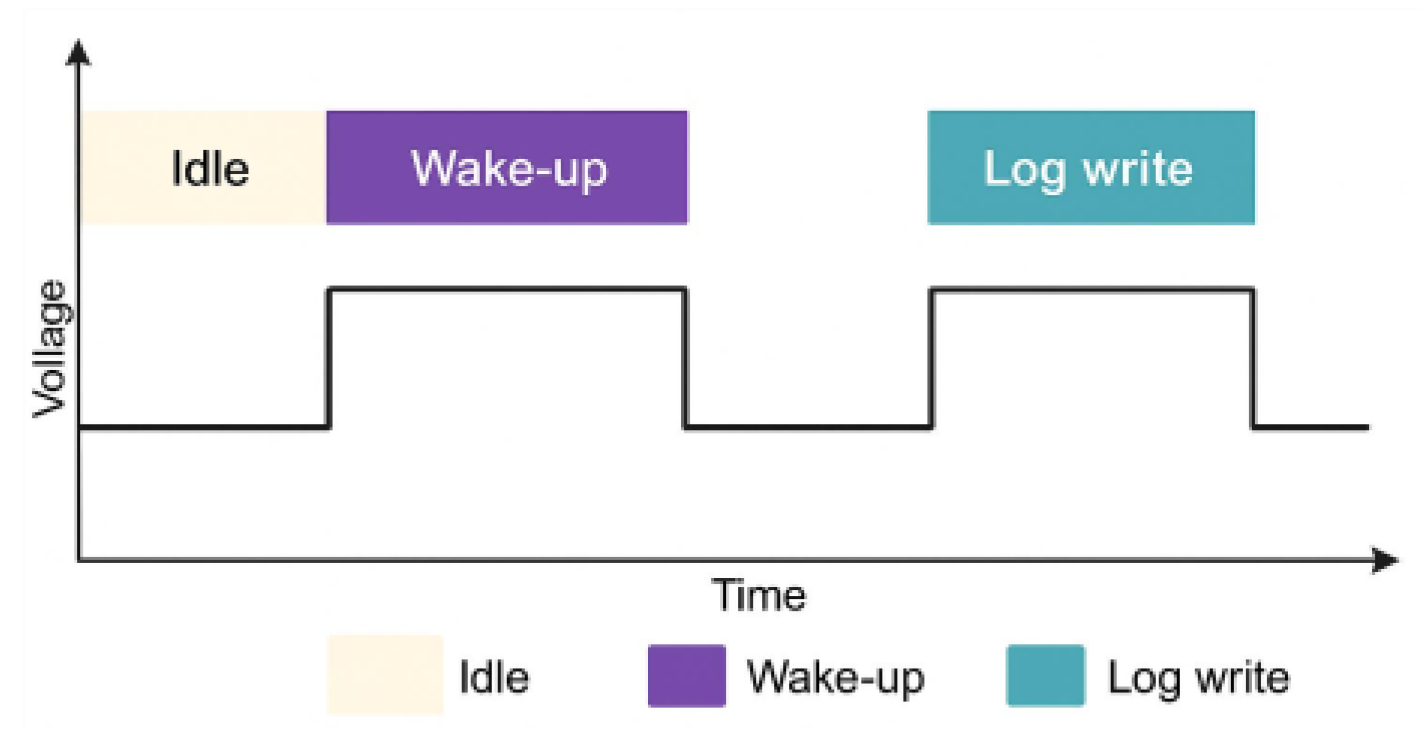

3.4. System Low Power Design

3.5. System Performance Optimization

4. System Experimental Results and Analysis

4.1. Experimental Environment and Test Program

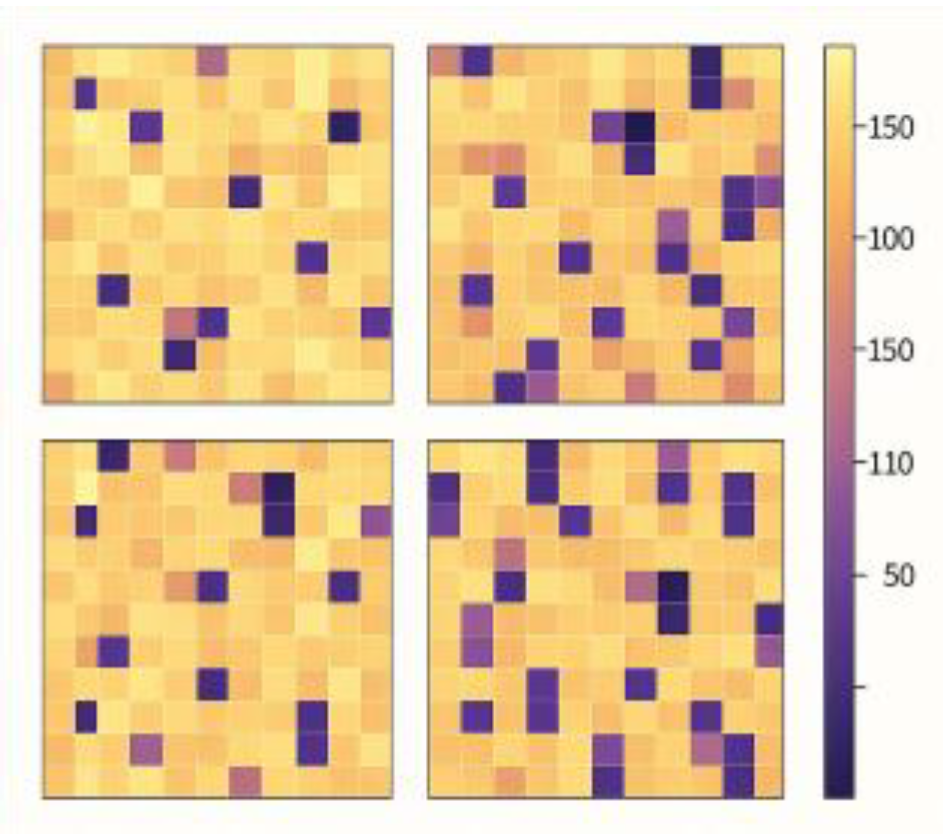

4.2. Power Consumption Test and Analysis

4.3. Storage Performance Test

4.4. Reliability and Data Integrity Validation

5. Conclusions

References

- Kok C L, Heng J B, Koh Y Y, et al. Energy-, Cost-, and Resource-Efficient IoT Hazard Detection System with Adaptive Monitoring[J]. Sensors, 2025, 25(6): 1761.

- Shankar, V. Machine Learning for Linux Kernel Optimization: Current Trends and Future Directions[J]. International Journal of Computer Sciences and Engineering, 2025, 13(3): 56-64.

- Pires L M, Figueiredo J, Martins R, et al. Design and Development of a Low-Power IoT System for Continuous Temperature Monitoring[J]. Designs, 2025, 9(3): 73.

- Zhang Z, Bai E, Joy K, et al. Smart glasses for supporting distributed care work: systematic review[J]. JMIR Medical Informatics, 2023, 11(1): e44161.

- Busaeed S, Mehmood R, Katib I, et al. LidSonic for visually impaired: Green machine learning-based assistive smart glasses with smart app and Arduino[J]. Electronics, 2022, 11(7): 1076.

- Mills K A, Brown A. Smart glasses for 3D multimodal composition[J]. Learning, Media and Technology, 2025, 50(2): 156-177.

- Huang Y J, Lin J C, Lee S S, et al. Reading and walking with smart glasses: Effects of display and control modes on safety[J]. International Journal of Human–Computer Interaction, 2024, 40(23): 7875-7891.

- Li K, Agarwal D, Zhang R, et al. SonicID: User Identification on Smart Glasses with Acoustic Sensing[J]. Proceedings of the ACM on Interactive, Mobile, Wearable and Ubiquitous Technologies, 2024, 8(4): 1-27.

- Kim S K, Lee Y, Hwang H R, et al. Wearable smart glasses for first-person video analysis to evaluate nursing skills: A pilot study with a mixed method design[J]. Journal of Computer Assisted Learning, 2025, 41(1): e13080.

- Hu, L. (2025). Hybrid Edge-AI Framework for Intelligent Mobile Applications: Leveraging Large Language Models for On-device Contextual Assistance and Code-Aware Automation. Journal of Industrial Engineering and Applied Science, 3(3), 10-22.

| Configuration item | Parameter value or status |

| Master Chip Model | Qualcomm QCS603 |

| Kernel Version | Android 11 AOSP Custom |

| Log process operation mode | Userland daemon (daemon level) |

| Log path | /dev/logd-persist |

| Initial size of cache pool | 1MB |

| File rotation period | Every 5 minutes |

| Total Test Duration | 60 minutes |

| Log Trigger Type | Static Standby / High Frequency Burst / Low Frequency Normal |

| Log Write Frequency (Analog) | 15 entries/s ~ 80 entries/s (different stages) |

| Current Sampling Accuracy | 0.01mA |

| Disable Module | OTA update, background synchronization service |

| Test Stage | CPU Power (mW) | Memory Power (mW) | Flash Power (mW) | Bus I/F Power (mW) | Total (mW) | CPU % | Mem % | Flash % | Bus % |

| Static Standby | 5.4 | 2.1 | 1.3 | 0.9 | 9.7 | 55.70% | 21.60% | 13.40% | 9.30% |

| High Freq. Burst Write | 26.8 | 11.7 | 14.2 | 5.1 | 57.8 | 46.40% | 20.20% | 24.60% | 8.80% |

| Low Freq. Normal Write | 14.1 | 6.3 | 5.8 | 2.2 | 28.4 | 49.60% | 22.20% | 20.40% | 7.80% |

| Cache Refresh Window | 19.6 | 8.2 | 9.4 | 3 | 40.2 | 48.80% | 20.40% | 23.40% | 7.50% |

| Cache Size | Compression level | Average write latency (ms) | Maximum write latency (ms) | Average throughput rate(KB/s) | Single Rotation Time(ms) |

| 128KB | LZ4 Fast | 3.21 | 9.72 | 176.4 | 176.4 |

| 256KB | LZ4 Fast | 2.54 | 7.63 | 202.7 | 2.5 |

| 256KB | LZ4 HC | 2.87 | 8.44 | 191.2 | 112 |

| 1MB | LZ4 HC | 2.12 | 6.81 | 223.5 | 107 |

| Fault Type | Recovery Time (ms) | Lost Entries | CRC Failures | Segment Reorg Success | Misplaced Indexes |

| Sudden Power Failure | 412 | 0 | 1 | 100% | 0 |

| Kernel Crash Reboot | 385 | 2 | 2 | 100% | 0 |

| Write Interrupt | 367 | 0 | 0 | 100% | 1 |

| Compression Failure Injection | 398 | 1 | 3 | 98.60% | 2 |

| Batch Power-Off (20x) | 467 | 0 | 4 | 100% | 0 |

| Flush-Incomplete Power Loss | 492 | 1 | 5 | 96.20% | 3 |

| Flash Exhaust + Forced Write | 478 | 2 | 3 | 97.80% | 1 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).