Submitted:

02 June 2025

Posted:

03 June 2025

You are already at the latest version

Abstract

Keywords:

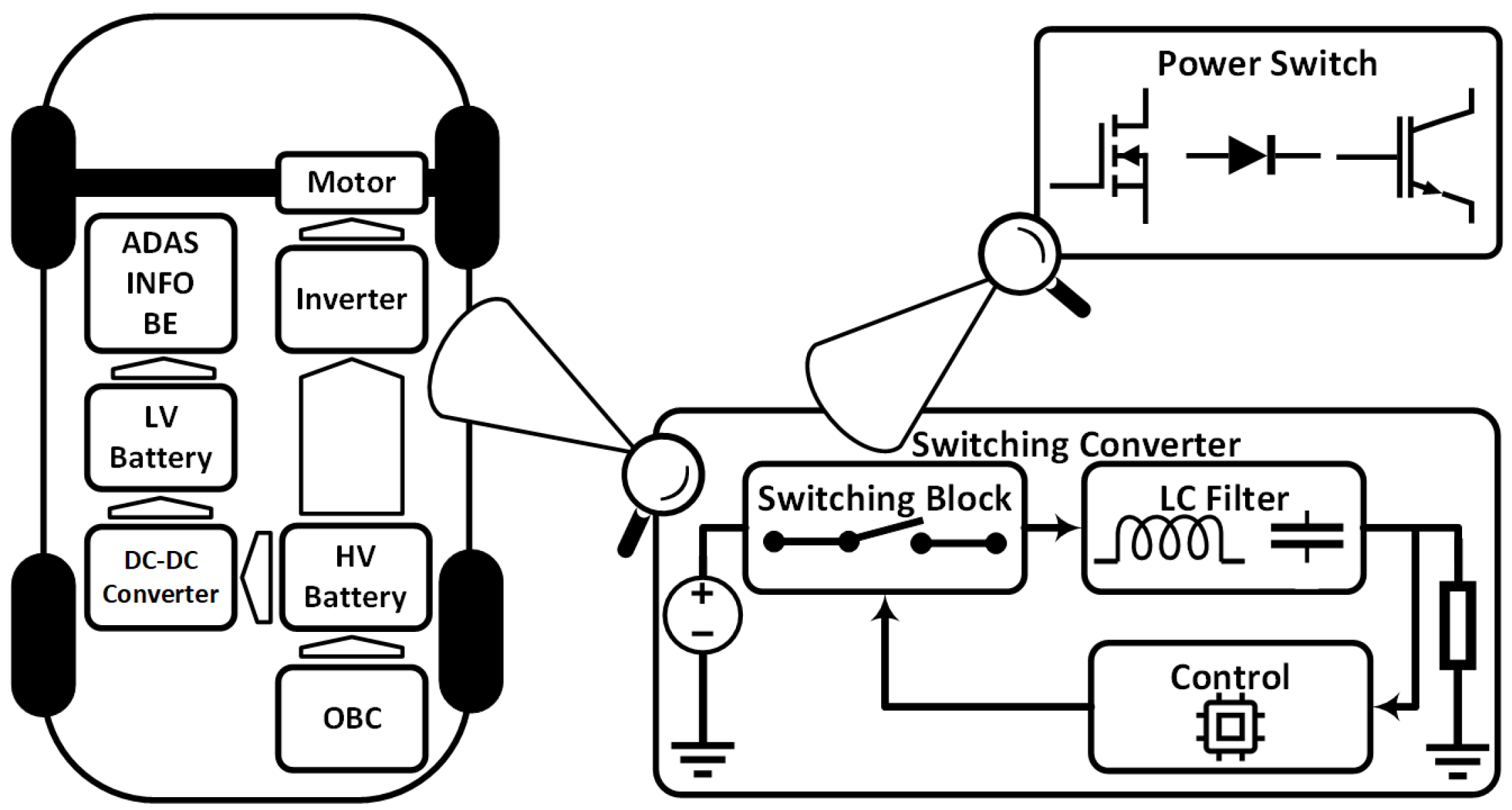

1. Introduction

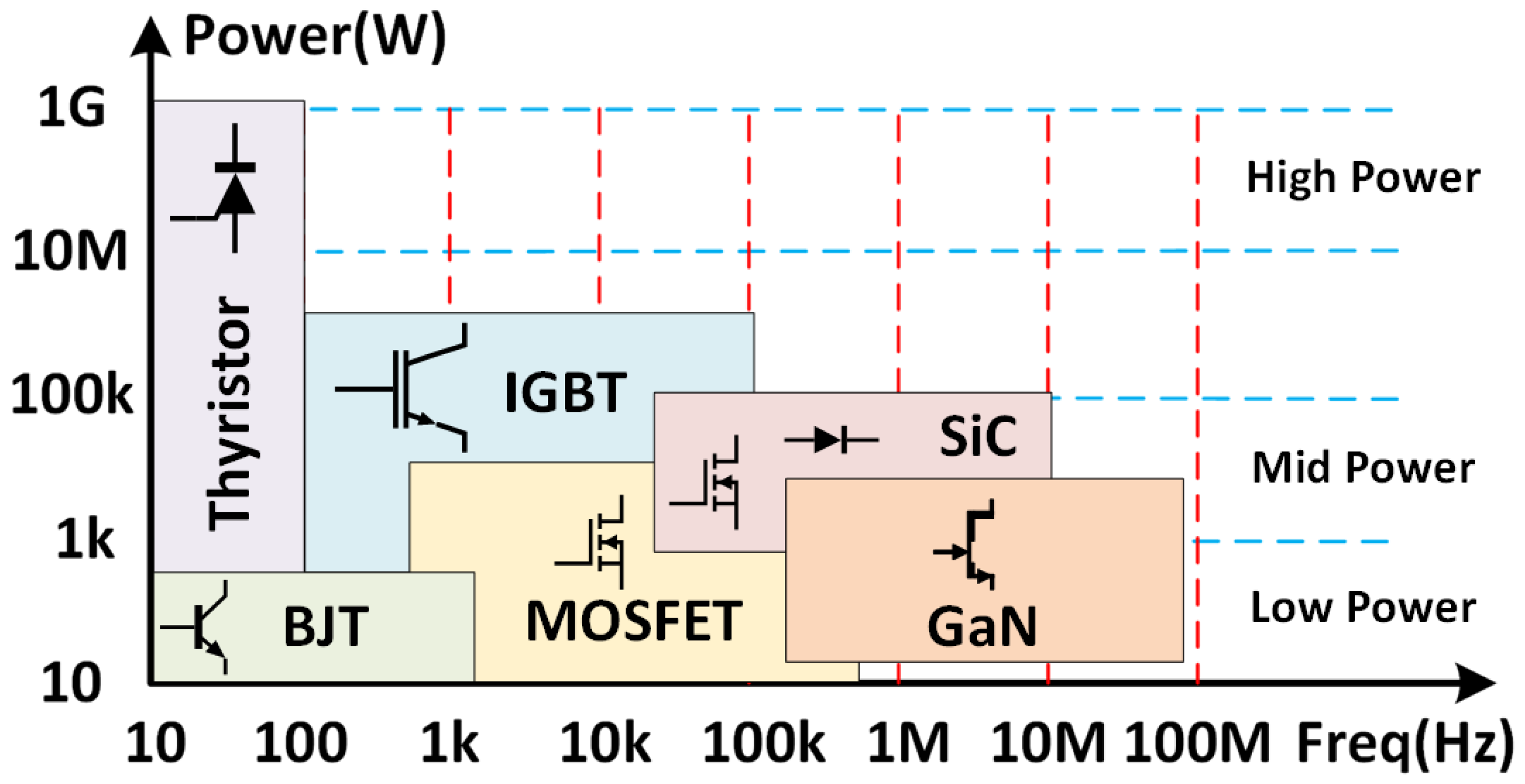

2. Semiconductor Technologies for Power Conversion Applications

3. GaN Technology

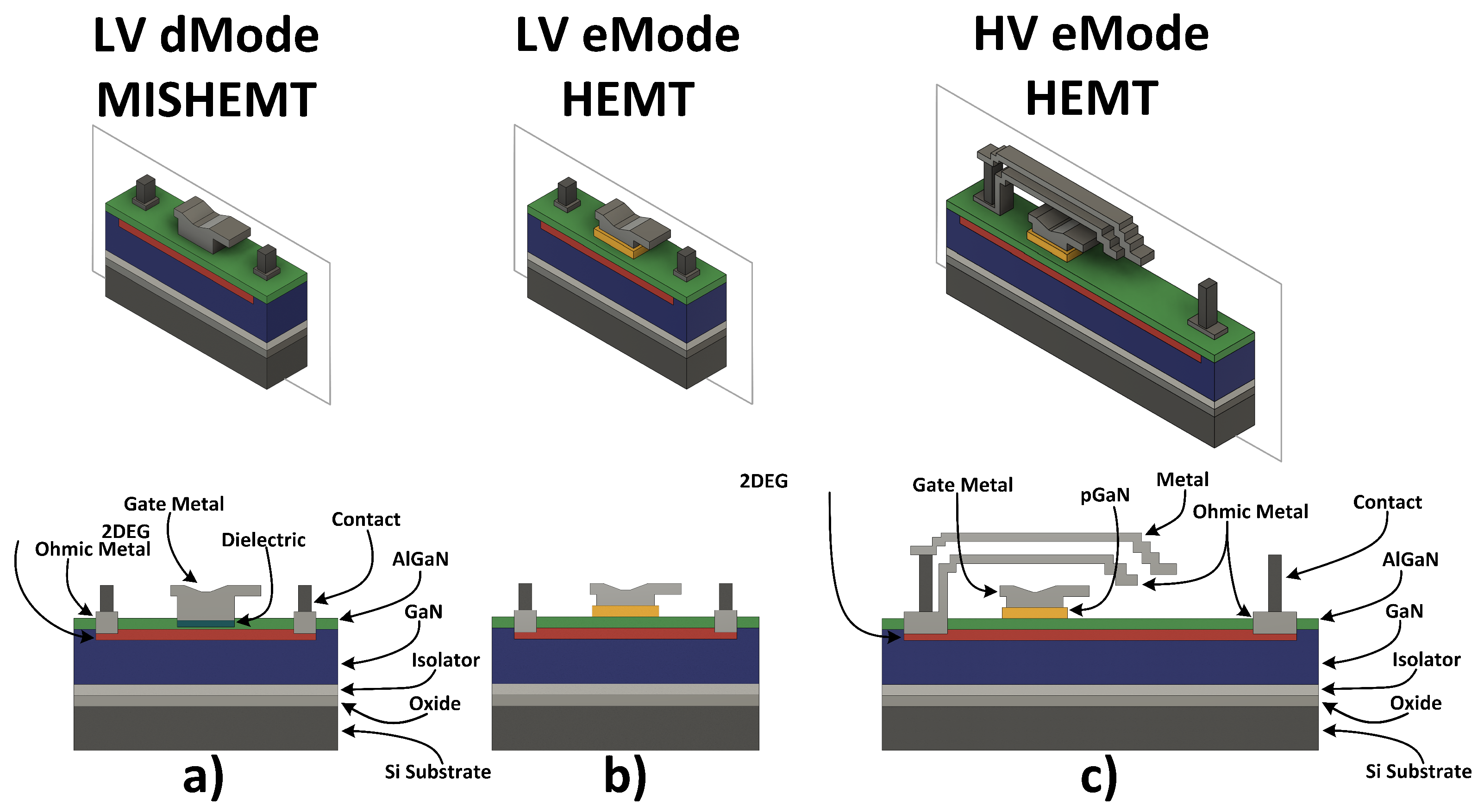

3.1. GaN Devices

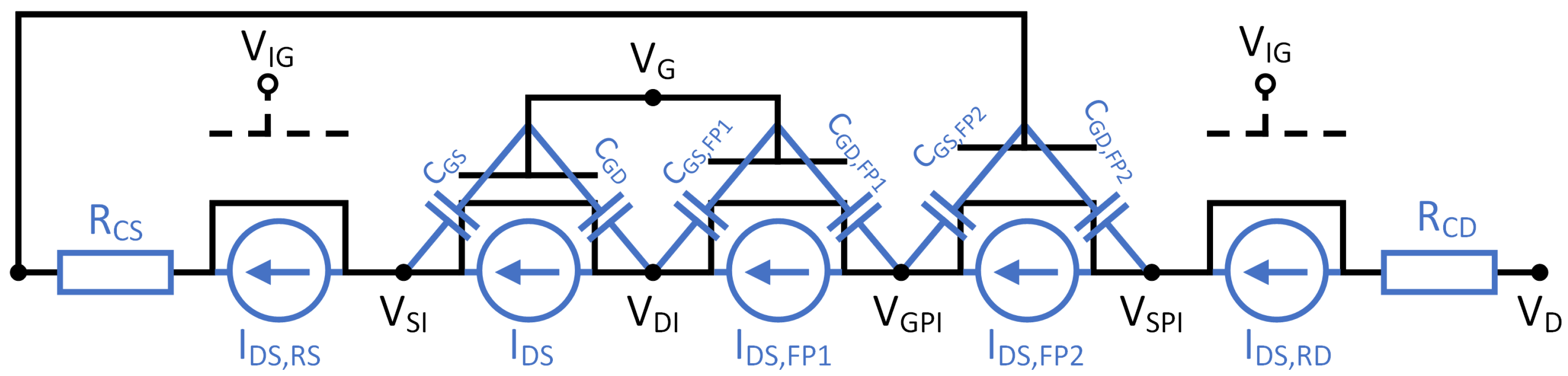

3.2. GaN HEMT Model

3.3. GaN Packaging

4. GaN Monolithic Integrated Circuits

4.1. Digital Design

4.2. Analog Design

4.3. Power Circuits

5. GaN Power Converters Evaluation

6. Conclusion

Funding

Abbreviations

| ADAS | Advanced Driver Assistance Systems |

| AlN | Aluminum Nitride |

| BDS | Bidirectional Switch |

| BE | Body Electronics |

| BS | Bootstrapped |

| BV | Breakdown Voltage |

| CAVET | Current Aperture Vertical Electron Transistor |

| CCM | Continuous Conduction Mode |

| COT | Constant-On-Time |

| CS | Chip-scale |

| DCFL | Direct-Coupled FET Logic |

| GaAs | Gallium Arsenide |

| GaN | Gallium Nitride |

| HEMTs | High Electron Mobility Transistors |

| HV | High Voltage |

| IC | Integrated Circuit |

| IGBT | Insulated Gate Bipolar Transistor |

| INFO | Infotainement |

| LV | Low Voltage |

| MIS-HEMT | Metal-Insulator-Semiconductor HEMT |

| MVSG | MIT Virtual Source GaN-HEMT |

| OBC | Onboard Battery Charger |

| PCB | Printed Circuit Board |

| PCFL | Pseudo-Complementary FET Logic |

| PCS | Power Conversion System |

| PD | Pull-Down |

| PE | Power electronics |

| POL | Point-Of-Load |

| PS | Power Switch |

| PU | Pull-Up |

| RTL | Resistor-Transistor Logic |

| RF | Radio Frequency |

| SC | Switching Converter |

| SB | Switching Block |

| Si | Silicone |

| SiC | Silicone Carbide |

| SiP | System in Package |

| UWBG | Ultra Wide Bandgap |

| WBG | Wide Bandgap |

| ZVD | Zero Voltage Detector |

References

- Krein, P.T. Data center challenges and their power electronics. CPSS Transactions on Power Electronics and Applications 2017, 2, 39–46.

- Chan, C.; Chau, K. An overview of power electronics in electric vehicles. IEEE Transactions on Industrial Electronics 1997, 44, 3–13. [CrossRef]

- Panigrahi, S.; Thakur, A. Current trends in power electronics for wind and solar energy conversion systems. In Proceedings of the ICPEDC, 2017, pp. 242–247.

- Devices, A. LTC7821, 2018. Datasheet. Accessed: May 17, 2025. [Online].

- van Wyk, J.D.; Lee, F.C. On a Future for Power Electronics. IEEE Journal of Emerging and Selected Topics in Power Electronics 2013, 1, 59–72.

- Erickson, R.W.; Maksimovic, D., Fundamentals of Power Electronics, 3rd ed.; Springer Cham, 2020.

- Gaudenzio Meneghesso, M.M.; Zanoni, E., Gallium Nitride-enabled High Frequency and High efficiency Power Conversion, 1st ed.; Springer Cham, 2018.

- intersil. HIGH FREQUENCY POWER CONVERTERS. https://www.analog.com/media/en/technical-documentation/tech-articles/an9208.pdf, 1994. Application Note Accessed: Dec. 21, 2024. [Online].

- Medinceanu, P.C.; Enachescu, M. An Overview of GaN Technology for Power Conversion Applications. In Proceedings of the ISETC, 2024, pp. 1–4.

- Chen, K.J.; Häberlen, O.; Lidow, A.; Tsai, C.l.; Ueda, T.; Uemoto, Y.; Wu, Y. GaN-on-Si Power Technology: Devices and Applications. IEEE Transactions on Electron Devices 2017, 64, 779–795. [CrossRef]

- Ellis, et al., N.M. Gallium Nitride-based 48V-to-1V Point-of-Load (PoL) Converter for Aerospace Telecommunications and Computing Applications. In Proceedings of the IEEE APEC, 2024, pp. 1384–1388.

- Park, J.M. Novel Power Devices for Smart Power Applications, 2004. Dissertation.

- Slawinski, M.; Heer, D.; Villbusch, T.; Buschkuehle, M. System study of SiC MOSFET and Si IGBT power module performance using a bidirectional buck-boost converter as evaluation platform. In Proceedings of the EPE’16 ECCE Europe, 2016, pp. 1–8.

- Palmer, P.; Zhang, X.; Shelton, E.; Zhang, T.; Zhang, J. An experimental comparison of GaN, SiC and Si switching power devices. In Proceedings of the IECON, 2017, pp. 780–785.

- Wort, C.J.; Balmer, R.S. Diamond as an electronic material. Materials Today 2008, 11, 22–28.

- Masataka Higashiwaki, Kohei Sasaki, A.K.T.M.; Yamakoshi, S. Development of gallium oxide power devices. PSS Applications and materials science 2014, 211, 21–26.

- Jinqiao Xie, Seiji Mia1, R.D.R.C.A.R.J.T.; Sitar, Z. Ni/Au Schottky diodes on AlxGa1-xN (0.7<x<1) grown on AlN single crystal substrates. PSS Current topics in solid state physics 2011, 8, 2407–2409.

- Tsao, J.Y.; Hollis, M.A.; Kaplar, R.J. Ultrawide-Bandgap Semiconductors: Research Opportunities and Challenges. Advanced Electronic Materials 2018, 4. [CrossRef]

- Li, J. The Emerging Adoption and Future Trends of SiC and GaN in EVs. https://www.idtechex.com/en/research-article/the-emerging-adoption-and-future-trends-of-sic-and-gan-in-evs/31201, 2024. Accessed: May 17, 2025. [Online].

- Zorpette, G. The Next Powerhouse Transistor For controlling high voltages, aluminum nitride will be hard to beat, 2024. Accessed: Dec. 21, 2024. [Online].

- Instruments, T. LMG341xR050, 2018. Datasheet. Accessed: May 17, 2025. [Online].

- Döring, P.; Driad, R.; Reiner, R.; Waltereit, P.; Leone, S.; Mikulla, M.; Ambacher, O. Technology of GaN-Based Large Area CAVETs With Co-Integrated HEMTs. IEEE Transactions on Electron Devices 2021, 68, 5547–5552. [CrossRef]

- Zhang, Y.; Sun, M.; Piedra, D.; Hu, J.; Liu, Z.; Lin, Y.; Gao, X.; Shepard, K.; Palacios, T. 1200 V GaN vertical fin power field-effect transistors. In Proceedings of the IEEE IEDM, 2017, pp. 9.2.1–9.2.4. [CrossRef]

- Baratella, G.; Chatterjee, U.; Syshchyk, O.; Borga, M.; Fabris, E.; Cosnier, T.; Bakeroot, B.; Decoutere, S. Monolithic 650-V Dual-Gate p-GaN Bidirectional Switch. IEEE Transactions on Electron Devices 2024, 71, 6904–6909. [CrossRef]

- Infineon. Infineon announces CoolGaN™ bidirectional switch and CoolGaN Smart Sense for higher performance and more cost-effective power systems, 2024.

- Infineon. Infineon pioneers world’s first 300 mm power gallium nitride (GaN) technology – an industry game-changer. https://www.infineon.com/cms/en/about-infineon/press/press-releases/2024/INFXX202409-142.html, 2024. Accessed: May 16, 2025. [Online].

- Chu, R.; Corrion, A.; Chen, M.; Li, R.; Wong, D.; Zehnder, D.; Hughes, B.; Boutros, K. 1.2 kV Normally Off GaN-on-Si FET With Low Dynamic on Resistance. IEEE Electron Device Letters 2011, 32, 632–634.

- Hilt, O.; Brunner, F.; Cho, E.; Knauer, A.; Bahat-Treidel, E.; Würfl, J. Normally-off high-voltage p-GaN gate GaN HFET with carbon-doped buffer. In Proceedings of the IEEE ISPSD, 2011, pp. 239–242. [CrossRef]

- Imada, T.; Kanamura, M.; Kikkawa, T. Enhancement-mode GaN MIS-HEMTs for power supplies. In Proceedings of the ECCE ASIA, 2010, pp. 1027–1033.

- Radhakrishna, U.; Antoniadis, D. MIT Virtual Source GaN HEMT-High Voltage (MVSG-HV) compact model. https://nanohub.org/publications/73/1, 2015. Accessed: May 17, 2025. [Online].

- Radhakrishna, U.; Choi, P.; Antoniadis, D.A. Facilitation of GaN-Based RF- and HV-Circuit Designs Using MVS-GaN HEMT Compact Model. IEEE Transactions on Electron Devices 2019, 66, 95–105. [CrossRef]

- Alaei, M.; Borga, M.; Fabris, E.; Decoutere, S.; Lauwaert, J.; Bakeroot, B. Extending Electrostatic Modeling for Schottky p-GaN Gate HEMTs: Uniform and Engineered p-GaN Doping. IEEE Transactions on Electron Devices 2024, 71, 5949–5955. [CrossRef]

- Lidow, A. Six Reasons to Rethink Power Semiconductor Packaging. https://epc-co.com/epc/about-epc/gan-talk-blog/post/13424/six-reasons-to-rethink-power-semiconductor-packaging, 2016. Accessed: May 17, 2025. [Online].

- Reusch, D.; Strydom, J.; Lidow, A. Thermal Evaluation of Chip-Scale Packaged Gallium Nitride Transistors. IEEE Journal of Emerging and Selected Topics in Power Electronics 2016, 4, 738–746.

- Kaufmann, M.; Seidel, A.; Wicht, B. Long, Short, Monolithic - The Gate Loop Challenge for GaN Drivers: Invited Paper. In Proceedings of the IEEE CICC), 2020, pp. 1–5.

- Ain, K.N.; Zhang, G.Q.; Rodrigues, A.; Hasan, M.N.; Holzmann, D.; Geens, K.; Chatterjee, U.; Roshanghias, A. An Introduction to Wire-Bondless Discrete GaN Power Packages With Top-Side Cu Sinterconnects®. In Proceedings of the IEEE ESTC, 2024, pp. 1–5.

- Moench, S.; Reiner, R.; Waltereit, P.; Benkhelifa, F.; Hückelheim, J.; Meder, D.; Zink, M.; Kaden, T.; Noll, S.; Mansfeld, S.; et al. PCB-Embedded GaN-on-Si Half-Bridge and Driver ICs With On-Package Gate and DC-Link Capacitors. IEEE Transactions on Power Electronics 2021, 36, 83–86.

- Kaufmann, M.; Wicht, B. Monolithic Integration in E-Mode GaN Technology, 1st ed.; Springer Cham, 2022.

- Li, X.; Amirifar, N.; Geens, K.; Zhao, M.; Guo, W.; Liang, H.; You, S.; Posthuma, N.; Jaeger, B.D.; Stoffels, S.; et al. GaN-on-SOI: Monolithically Integrated All-GaN ICs for Power Conversion. In Proceedings of the IEDM, 2019, pp. 4.4.1–4.4.4.

- Zhu, et al., M. Monolithic integration of GaN-based NMOS digital logic gate circuits with E-mode power GaN MOSHEMTs. In Proceedings of the IEEE ISPSD, 2018, pp. 236–239.

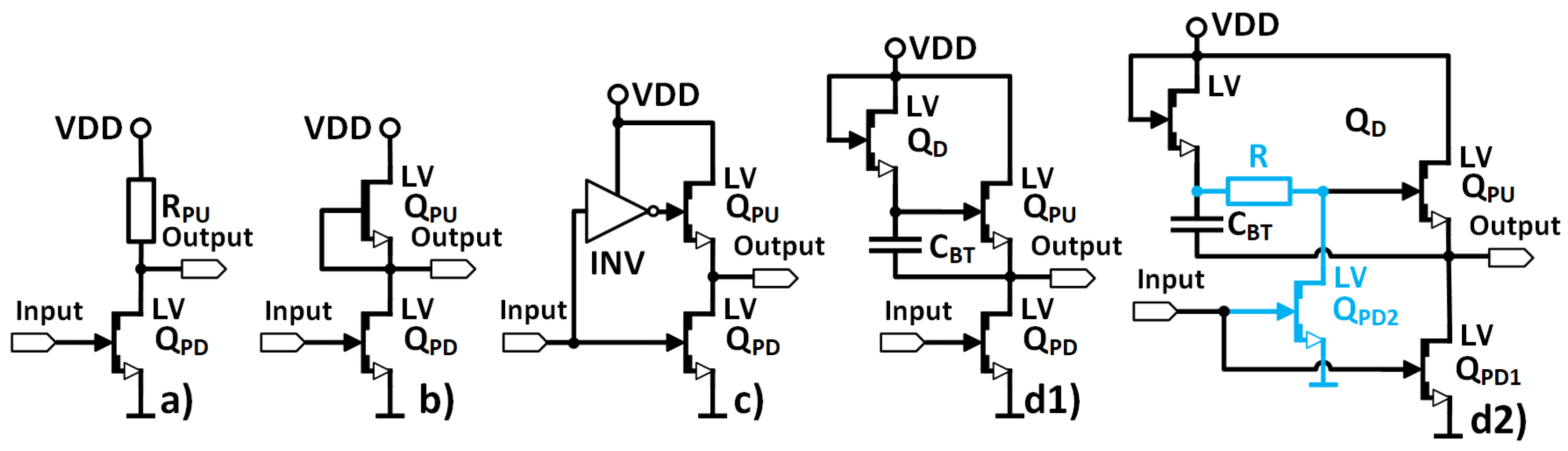

- Basler, M.; Moench, S.; Reiner, R.; Waltereit, P.; Quay, R.; Kallfass, I.; Ambacher, O. A Pseudo-Complementary GaN-Based Gate Driver with Reduced Static Losses. In Proceedings of the IEEE WiPDA, 2019, pp. 93–98.

- Medinceanu, P.C.; Enachescu, M. Analysis of the Bootstrapped GaN Logic Gate Family. In Proceedings of the IEEE CAS, 2024, pp. 229–232.

- Daniel M. Kinzer, Santosh Sharma, J.J.Z. GaN CIRCUIT DRIVERS FOR GaN CIRCUIT LOADS, US20160079854A1.

- Ma, S.; Jiang, Q.; Huang, S.; Wang, X.; Liu, X. A GaN-Based Hybrid Logic Circuitry With Low Power Consumption and Enhanced Fan-Out Capability. IEEE Transactions on Electron Devices 2025, 72, 618–624.

- Kaufmann, M.; Lueders, M.; Kaya, C.; Wicht, B. 18.2 A Monolithic E-Mode GaN 15W 400V Offline Self-Supplied Hysteretic Buck Converter with 95.6% Efficiency. In Proceedings of the IEEE ISSCC, 2020, pp. 288–290.

- Wu, S.; Ran, Z.; Tong, Z.; Liu, T.; Lu, Y. A Monolithic Integrated E-Mode GaN 48V-to-1V DC-DC Buck Converter with PWM Control. In Proceedings of the IEEE ICTA, 2023, pp. 130–131.

- Grobe, J.; Weihs, L.; Hanhart, M.; Wunderlich, R.; Heinen, S. Monolithic Integration of a 400V GaN Half-Bridge Converter With Output Voltage Regulation. IEEE Transactions on Circuits and Systems II: Express Briefs 2024, 71, 4591–4595. [CrossRef]

- Pennisi, S.; Pulvirenti, F.; Samperi, K. Frequency Compensation Scheme for a Full GaN OpAmp driving 1-nF load. In Proceedings of the IEEE ISCAS, 2022, pp. 2042–2046.

- Deneke, N.; Wicht, B. A 500-V, 6.25-MHz GaN-IC With Gate Driver and Level Shifter for Off-Line Power Supplies. IEEE Solid-State Circuits Letters 2024, 7, 207–210. [CrossRef]

- Grobe, J.; Zoche, J.; Wunderlich, R.; Heinen, S. An Auto-Zero Comparator for Monolithic GaN Power Integration. In Proceedings of the PRIME, 2024, pp. 1–4.

- EPC. EPC2152, 2021. Datasheet. Accessed: May 17, 2025. [Online].

- Systems, M.P. MP8040, 2011. Datasheet. Accessed: May 17, 2025. [Online].

- Instruments, T. LMG2100R044, 2023. Datasheet. Accessed: May 17, 2025. [Online].

- Lai, R.; Zhou, Z.; Wu, J.; Dai, Y.; Liu, X.; Zhang, B.; Shi, Y.; Li, S.; Qin, Z. A Monolithic GaN Power Stage With Common-Mode Transient Immunity and Negative Voltage Operation Design for High-Frequency Power Converters. IEEE Transactions on Power Electronics 2024, 39, 8129–8145. [CrossRef]

- Jiang, W.L.; Kadee Murray, S.; Zaman, M.S.; De Vleeschouwer, H.; Roig, J.; Moens, P.; Trescases, O. Monolithic Integration of a 5-MHz GaN Half-Bridge in a 200-V GaN-on-SOI Process: Programmable dv/dt Control and Floating High-Voltage Level-Shifter. In Proceedings of the IEEE APEC, 2021, pp. 728–734.

- Yamashita, Y.; Stoffels, S.; Posthuma, N.; Decoutere, S.; Kobayashi, K. Monolithically Integrated E-mode GaN-on-SOI Gate Driver with Power GaN-HEMT for MHz-Switching. In Proceedings of the IEEE WiPDA, 2018, pp. 231–236.

- Deneke, N.; Wicht, B. 31.10 A Fully integrated 500V, 6.25MHz GaN-IC for Totem-Pole PFC Off-Line Power Conversion. In Proceedings of the IEEE ISSCC, 2024, Vol. 67, pp. 514–516.

- Pallo, N.; Foulkes, T.; Modeer, T.; Coday, S.; Pilawa-Podgurski, R. Power-dense multilevel inverter module using interleaved GaN-based phases for electric aircraft propulsion. In Proceedings of the IEEE APEC, 2018, pp. 1656–1661.

- Navitas. Dell Adopts Navitas GaNFast Technology for Laptop Fast Charger. https://navitassemi.com/dell-adopts-navitas-ganfast-technology-for-laptop-fast-charger/, 2020. Accessed: May 17, 2025. [Online].

- Navitas. Navitas Goes Global in Xiaomi’s Mi 11 Fast Charger. https://navitassemi.com/navitas-goes-global-in-xiaomis-mi-11-fast-charger/, 2021. Accessed: May 17, 2025. [Online].

- Then, H.W.; Radosavljevic, M.; Bader, S.; Zubair, A.; Vora, H.; Nair, N.; Koirala, P.; Beumer, M.; Nordeen, P.; Vyatskikh, A.; et al. DrGaN: an Integrated CMOS Driver-GaN Power Switch Technology on 300mm GaN-on-Si with E-mode GaN MOSHEMT and 3D Monolithic Si PMOS. In Proceedings of the IEDM, 2023, pp. 1–4.

- Reiner, R.; Gerrer, T.; Weiss, B.; Waltereit, P.; Moench, S.; Meder, D.; Sinnwell, M.; Dammann, M.; Quay, R.; Ambacher, O. Si-Substrate Removal for AlGaN/GaN Devices on PCB Carriers. In Proceedings of the ISPSD, 2020, pp. 286–289.

| Material | k | |||||

| Si | 1.12 | 11.7 | 1350 | 0.3 | 1.5 | |

| GaAs | 1.42 | 12.9 | 8500 | 0.4 | 0.5 | |

| 4H-SiC | 3.23 | 9.66 | 900 | 2.5 | 4.9 | |

| GaN | 3.39 | 8.9 | 1265* | 3.75 | 1.3 | |

| 4.9 | 10 | 300 | 8 | 0.23** | ||

| Diamond | 5.47 | 5.7 | 4500 | 10 | 24 | |

| AlN | 6.1 | 8.5 | 500 | 15.9 | 3.21 | |

| Notes: *1265 in bulk, 2000 in 2DEG | ||||||

| **0.23 for [010] and 0.13 for [100] | ||||||

| Work | [23](V) | [22](V) | [27](L) | [28](L) | [29](L) | |

|---|---|---|---|---|---|---|

| Param. | ||||||

| Fin | CAVET | HEMT | HEMT | MIS-HEMT | ||

| GaN | GaN | Si | SiC | SiC | ||

| 1 | -2.8 | 0.64 | 1.8 | 3 | ||

| 0.2 | 16.2 | 9 | 0.62 | 0.8 | ||

| 1200 | 201 | 1200 | 1000 | 420 | ||

| 25 | 1.08 | 0.18 | 0.35 | 0.86 | ||

| Notes: L-Lateral, V-Vertical,* for V, for L | ||||||

| Work | [54] | [55] | [56] | [49,57] | [51] | [52] | [53] | |

|---|---|---|---|---|---|---|---|---|

| Param. | ||||||||

| 5 | 12(1) | 6 | 6(2) | 12 | 24(4) | 5 | ||

| 25 | 5 | 10 | 6.25 | 3 | 1.2 | 10 | ||

| 2 | - | 4.75 | 6.6 | 10.2 | - | - | ||

| BS | RTL | RTL | RTL, PCFL | BS | CMOS | CMOS | ||

| 30 | 80 | - | 500 | 14.5(3) | 100 | 4.4 | ||

| 30 | 80 | 67 | 500 | 14.5(3) | 100 | 4.4 | ||

| 1.5 | 3 | 10 | - | 15 | 9 | 35 | ||

| 25 | 200 | 100 | 650 | 60 | 28 | 90 | ||

| 100 | - | - | - | 21 | 60(5) | 22.5 | ||

| ≈200@25 | - | 2070@10 | 132@30 | 40@3 | - | 75@0.5 | ||

| Notes: | ||||||||

| (1) is 6.8V and is 12V. (2) is 6V and is 11V. | ||||||||

| (3) In the previous datasheet version the value was 8.5. | ||||||||

| (4) The voltage gets internally regulated down to 5V. | ||||||||

| (5) The type of power consumption isn’t specified. Static power is assumed. | ||||||||

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).