Submitted:

27 May 2025

Posted:

29 May 2025

You are already at the latest version

Abstract

Keywords:

1. Introduction

2. Modeling of Thermal Characteristics of SiC Power Semiconductors

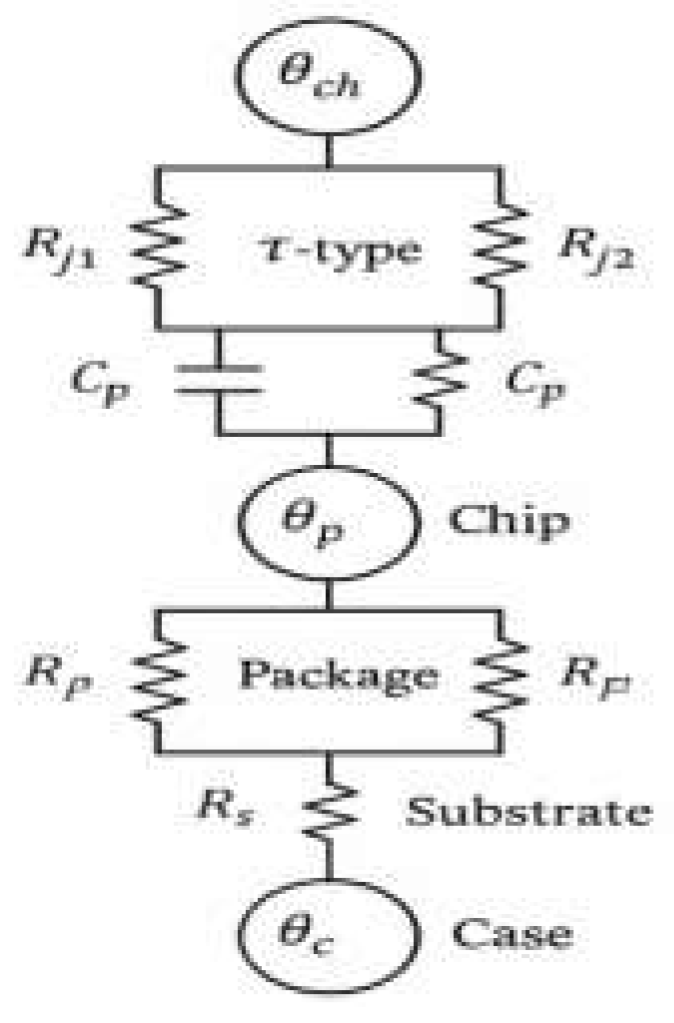

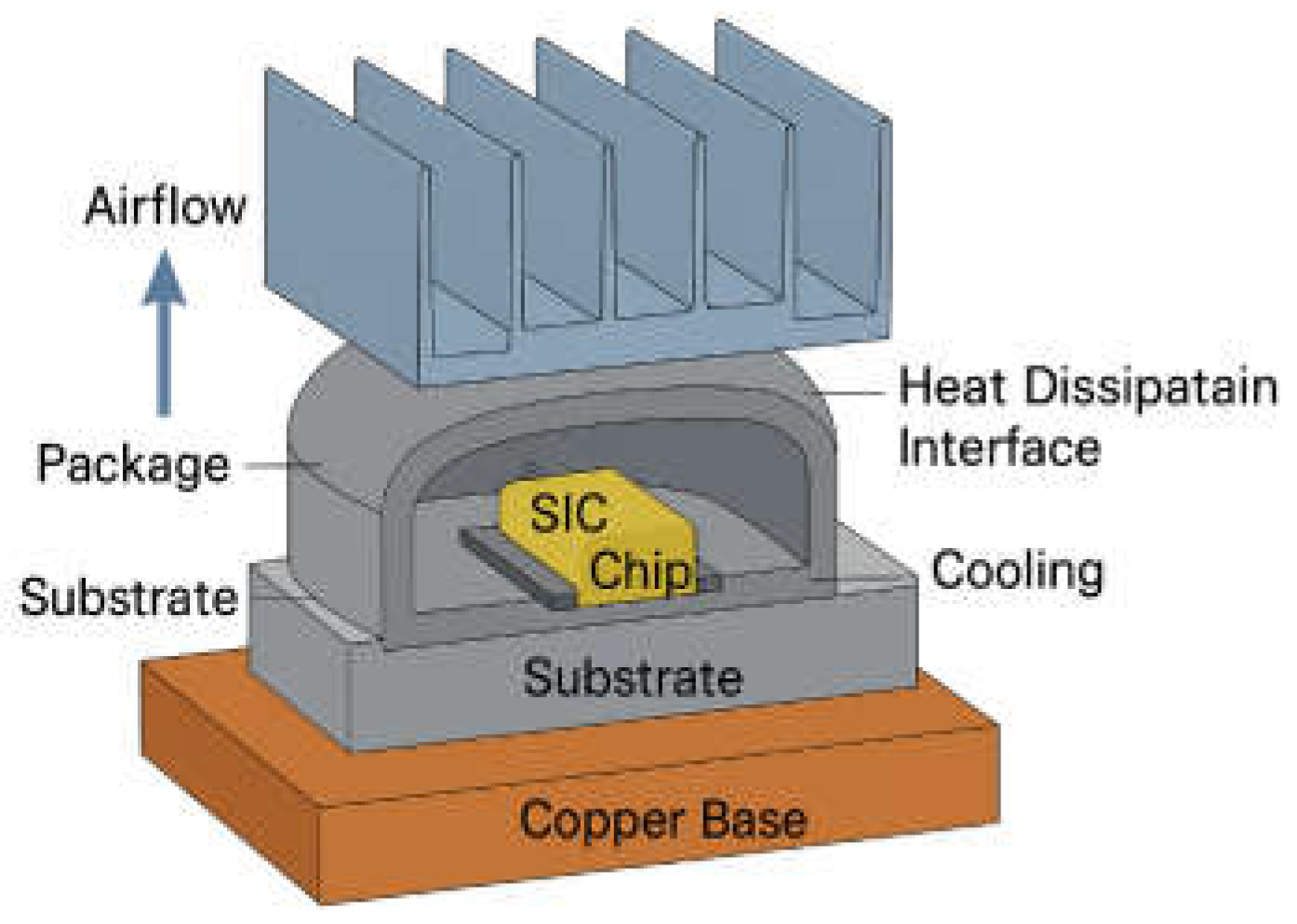

2.1. Thermal Network Topology Construction

2.2. Mathematical Model Derivation

2.3. Model Simplification and Parameter Extraction

3. Improved Genetic Algorithm Design

3.1. Question Coding Design

3.2. Adaptation Function Construction

3.3. Genetic Operator Improvement

4. Co-Optimization of Thermal Management Systems

4.1. Optimization Objective Analysis

4.2. Optimization of Thermal Structure Parameters

4.3. Optimization of Cooling System Parameters

4.4. Multi-Parameter Co-Optimization Strategy

5. Experimental Validation and Result Analysis

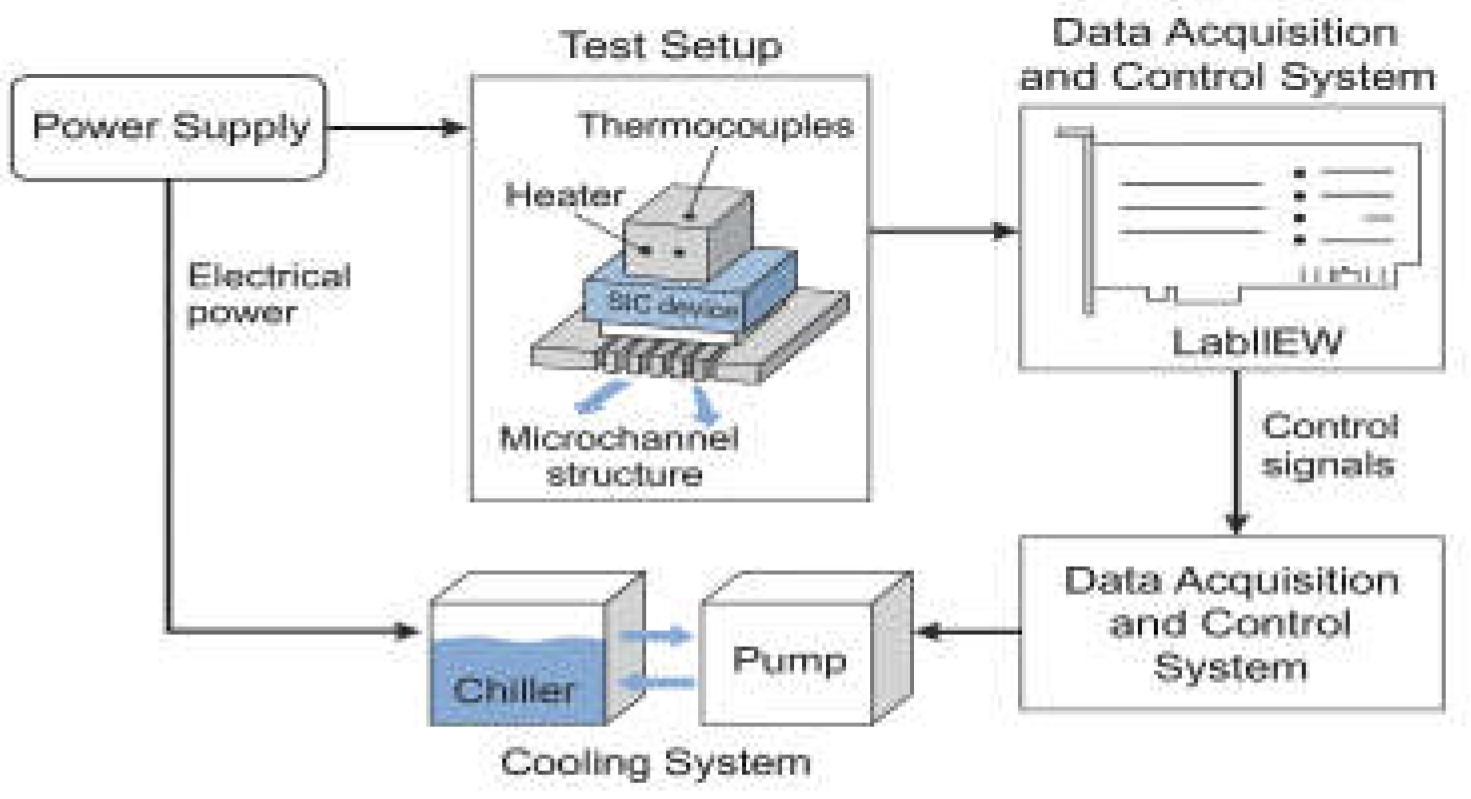

5.1. Experimental Platform Construction

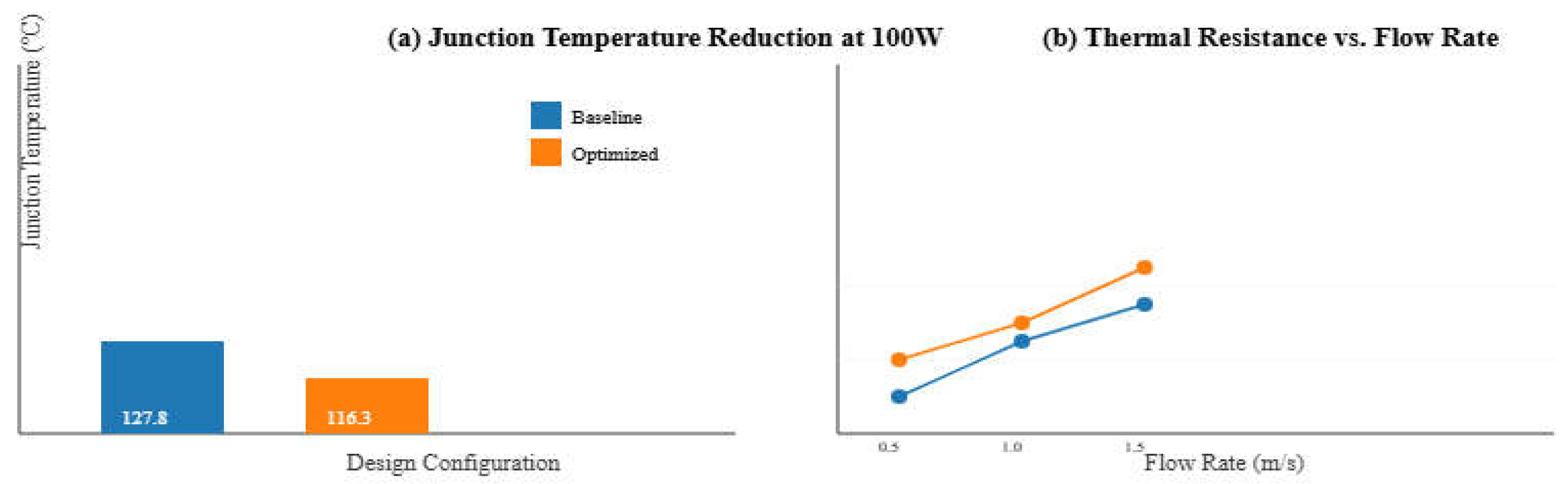

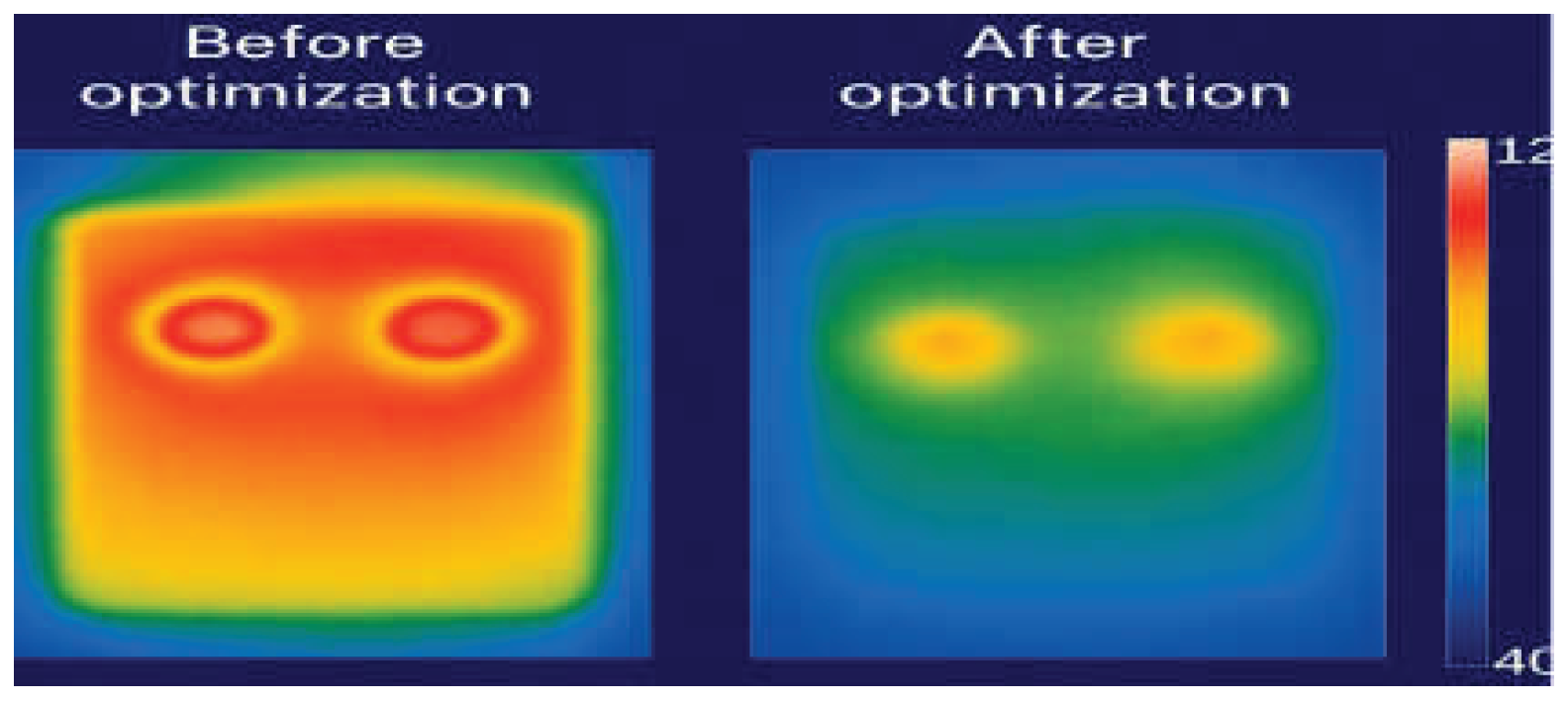

5.2. Optimization Effect Analysis

6. Conclusions

References

- Pourfattah, F.; Sabzpooshani, M. On the thermal management of a power electronics system: Optimization of the cooling system using genetic algorithm and response surface method[J]. Energy 2021, 232, 120951. [Google Scholar] [CrossRef]

- Rafin, S.M.S.H.; Ahmed, R.; Haque, M.A.; et al. Power electronics revolutionized: A comprehensive analysis of emerging wide and ultrawide bandgap devices[J]. Micromachines 2023, 14, 2045. [Google Scholar] [CrossRef] [PubMed]

- Elqady, H.I.; El-Shazly, A.H.; Elkady, M.F. Parametric study for optimizing double-layer microchannel heat sink for solar panel thermal management[J]. Scientific Reports 2022, 12, 18278. [Google Scholar] [CrossRef] [PubMed]

- Kelly, B.J. DIGITAL CODESIGN OF A POWER MODULE WITH INTEGRATED THERMAL MANAGEMENT[D]. Georgia Institute of Technology, 2022.

- Hinov, N. Smart Energy Systems Based on Next-Generation Power Electronic Devices[J]. Technologies 2024, 12, 78. [Google Scholar] [CrossRef]

- Rajamony, R.; Wang, S.; Calderon-Lopez, G.; et al. Artificial neural networks-based multi-objective design methodology for wide-bandgap power electronics converters[J]. IEEE Open Journal of Power Electronics 2022, 3, 599–610. [Google Scholar] [CrossRef]

- Sun, L.; Qiao, M.; Xia, Y.; et al. Review of Voltage Balancing Techniques for Series-Connected SiC Metal–Oxide–Semiconductor Field-Effect Transistors[J]. Energies 2024, 17, 5846. [Google Scholar] [CrossRef]

- Tirupati Rao, V.; Raja Sekhar, Y. Hybrid photovoltaic/thermal (PVT) collector systems with different absorber configurations for thermal management–a review[J]. Energy & Environment 2023, 34, 690–735. [Google Scholar]

- Aouichak, I.; Jacques, S.; Bissey, S.; et al. A bidirectional grid-connected DC–AC converter for autonomous and intelligent electricity storage in the residential sector[J]. Energies 2022, 15, 1194. [Google Scholar] [CrossRef]

- Popescu, M.; Bitoleanu, A.; Suru, C.V.; et al. Shunt active power filters in three-phase, three-wire systems: A topical review[J]. Energies 2024, 17, 2867. [Google Scholar] [CrossRef]

| structural layer | makings | Thermal conductivity λ(W/m-K) | Density ρ (kg/m³) | Specific heat capacity cp(J/kg-K) | Thickness L(mm) | Cross-sectional area A (mm²) |

| Chip (SiC) | SiC | 370 | 3210 | 690 | 0.15 | 1.5 × 1.5 = 2.25 |

| solder layer | SnAgCu | 50 | 7400 | 230 | 0.10 | 2.25 |

| DBC Ceramic Layer | AlN | 180 | 3300 | 740 | 0.38 | 2.25 |

| Copper Substrate (Heat Dissipation) | Cu | 390 | 8960 | 385 | 1.00 | 10.0 × 10.0 = 100.00 |

| TIM Thermally Conductive Interface Material | silicone grease | 5.5 | 2200 | 1300 | 0.20 | 100.00 |

| Radiator base plate | aluminum (chemistry) | 205 | 2700 | 900 | 5.00 | 100.00 |

| Flow Rate (m/s) | State | Tj,max (°C) | Rth,eq (K/W) | τ90% (s) |

| 0.5 | Baseline | 127.8 | 0.336 | 3.82 |

| 0.5 | Optimized | 116.3 | 0.282 | 2.97 |

| 1.0 | Baseline | 121.4 | 0.298 | 3.12 |

| 1.0 | Optimized | 108.7 | 0.233 | 2.26 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).