Submitted:

27 November 2024

Posted:

29 November 2024

You are already at the latest version

Abstract

Keywords:

1. Introduction

2. Core Innovations

2.1. Dynamic BeamSNARKS Generation Optimization Mechanism

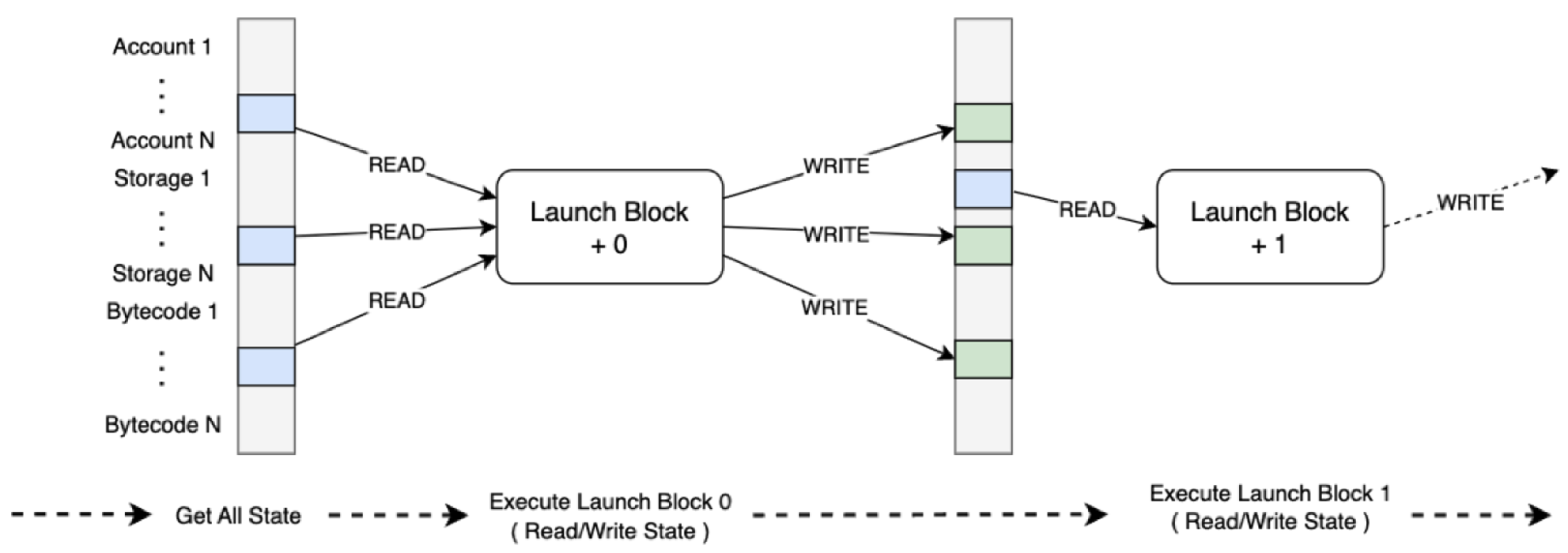

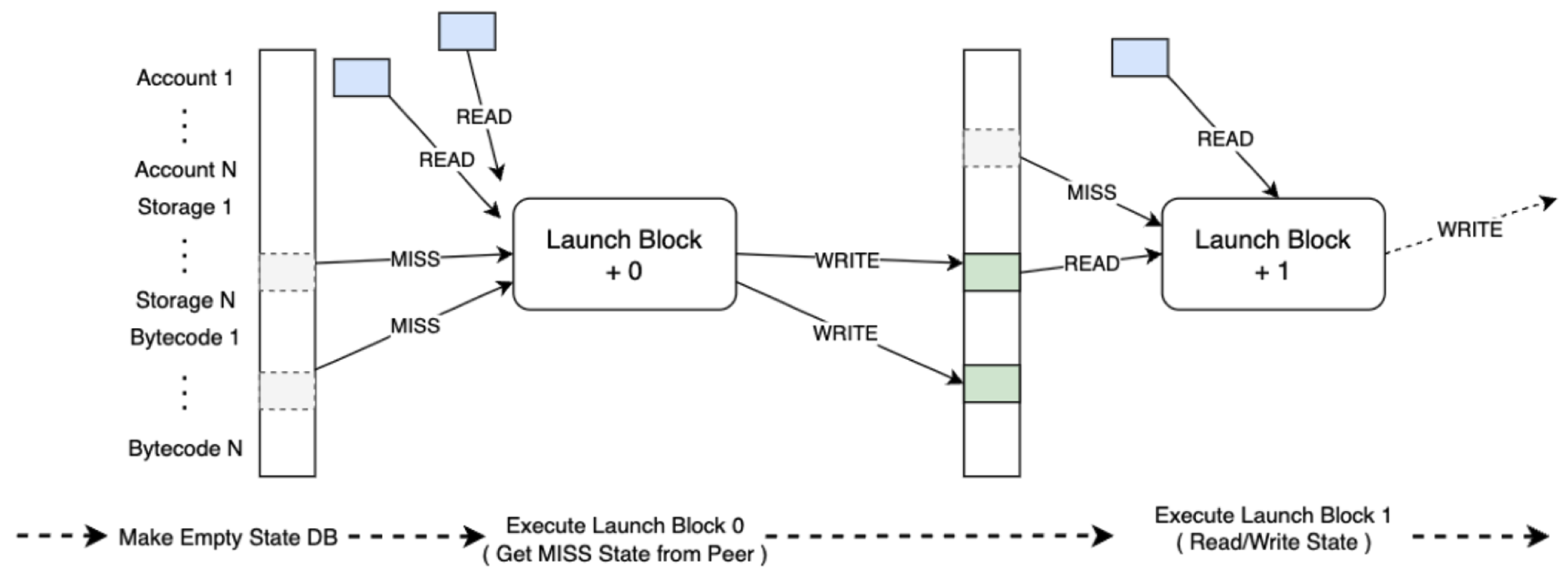

2.1.1. On-Demand State Synchronization

2.1.2. Incremental Proof Generation

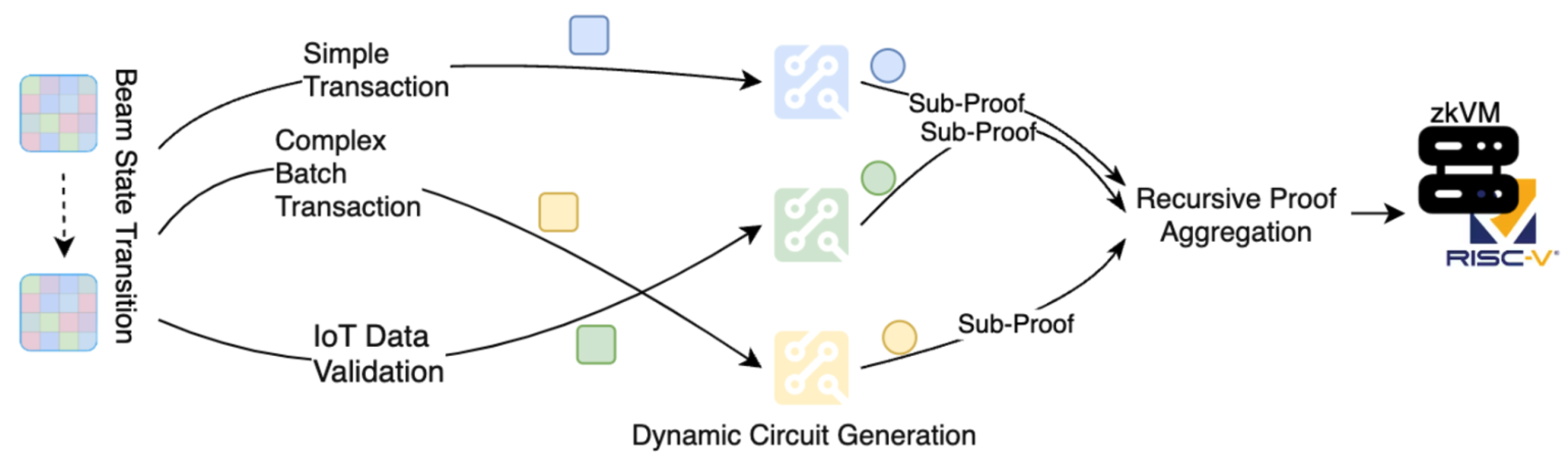

2.2. Dynamic SNARKification

3. Experiments

3.1. Performance Evaluation of Chain SNARKification

| Batch Size | Technique | Generation Time (ms) ± SD | Verification Time (ms) ± SD | CPU Usage (%) ± SD | Memory Usage (GB) ± SD |

|---|---|---|---|---|---|

| 1,000 Transactions | FCD | 502.3 ± 18.4 | 51.7 ± 3.2 | 30.5 ± 1.8 | 4.1 ± 0.3 |

| DS | 298.7 ± 14.6 | 29.4 ± 2.1 | 19.7 ± 1.3 | 3.2 ± 0.2 | |

| 10,000 Transactions | FCD | 5,027.6 ± 95.3 | 203.4 ± 10.7 | 61.2 ± 3.5 | 16.4 ± 0.8 |

| DS | 2,489.2 ± 81.7 | 101.8 ± 7.2 | 40.6 ± 2.4 | 12.3 ± 0.6 | |

| 50,000 Transactions | FCD | 30,127.5 ± 480.3 | 1,014.8 ± 50.1 | 90.7 ± 4.6 | 64.5 ± 1.7 |

| DS | 14,856.9 ± 340.2 | 608.3 ± 25.4 | 70.3 ± 3.2 | 48.2 ± 1.1 |

3.2. Performance Analysis of zkVM Proof Generation

4. Conclusions

References

- Ethereum Beam Chain: FAQ to Unpack the Big DevCon Announcement — polygon.technology. Available online: https://polygon.technology/blog/ethereum-beam-chain-faq-to-unpack-the-big-devcon-announcement (accessed on 27 November 2024).

- The 1.x Files: The State of Stateless Ethereum | Ethereum Foundation Blog — blog.ethereum.org. Available online: https://blog.ethereum.org/2019/12/30/eth1x-files-state-of-stateless-ethereum (accessed on 27 November 2024).

- Pustišek, M.; Umek, A.; Kos, A. Approaching the communication constraints of ethereum-based decentralized applications. Sensors 2019, 19, 2647. [Google Scholar] [CrossRef] [PubMed]

- Luong, D.A.; Park, J.H. Privacy-preserving blockchain-based healthcare system for iot devices using zk-snark. IEEE Access 2022, 10, 55739–55752. [Google Scholar] [CrossRef]

- Shang, X.; Tan, L.; Yu, K.; Zhang, J.; Kaur, K.; Hassan, M.M. Newton-interpolation-based zk-snark for artificial internet of things. Ad Hoc Networks 2021, 123, 102656. [Google Scholar] [CrossRef]

- Cui, E.; Li, T.; Wei, Q. Risc-v instruction set architecture extensions: A survey. IEEE Access 2023, 11, 24696–24711. [Google Scholar] [CrossRef]

| Transaction Type | Load (TPS) | Proof Generation Time (ms) ± SD | Throughput (TPS) ± SD | CPU Usage (%) ± SD | Memory Usage (GB) ± SD |

|---|---|---|---|---|---|

| Simple | 100 | 52.3 ± 3.1 | 998.4 ± 12.7 | 21.2 ± 1.5 | 5.2 ± 0.3 |

| 500 | 72.8 ± 4.6 | 502.6 ± 9.8 | 41.8 ± 2.1 | 10.3 ± 0.6 | |

| Moderate Complexity | 100 | 153.7 ± 5.8 | 498.2 ± 10.1 | 31.7 ± 1.8 | 8.5 ± 0.4 |

| 500 | 201.4 ± 7.2 | 305.4 ± 11.3 | 52.9 ± 2.5 | 12.1 ± 0.7 | |

| Complex | 100 | 497.5 ± 15.4 | 102.3 ± 6.9 | 62.4 ± 3.3 | 12.4 ± 0.8 |

| 500 | 812.6 ± 18.7 | 82.1 ± 5.4 | 82.7 ± 4.1 | 18.6 ± 1.2 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).