Submitted:

27 May 2024

Posted:

28 May 2024

You are already at the latest version

Abstract

Keywords:

1. Introduction

2. Preeliminars

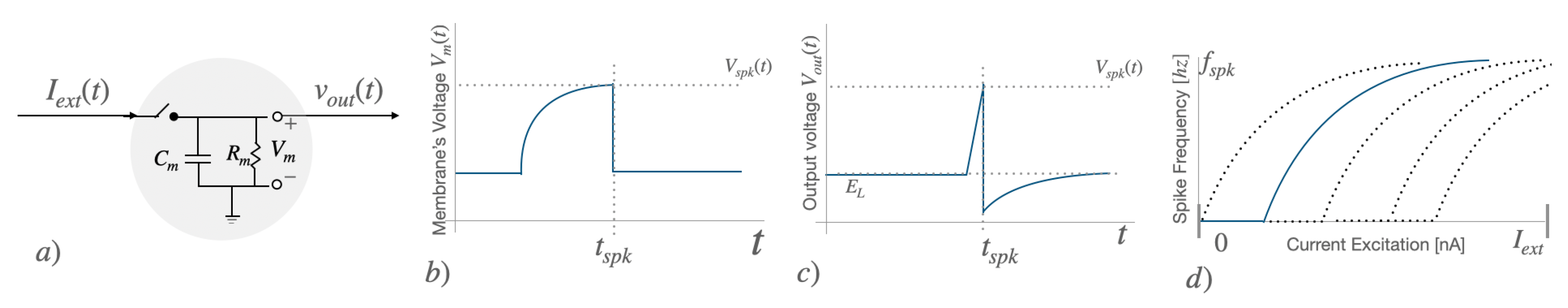

2.1. Spiking Neural Networks

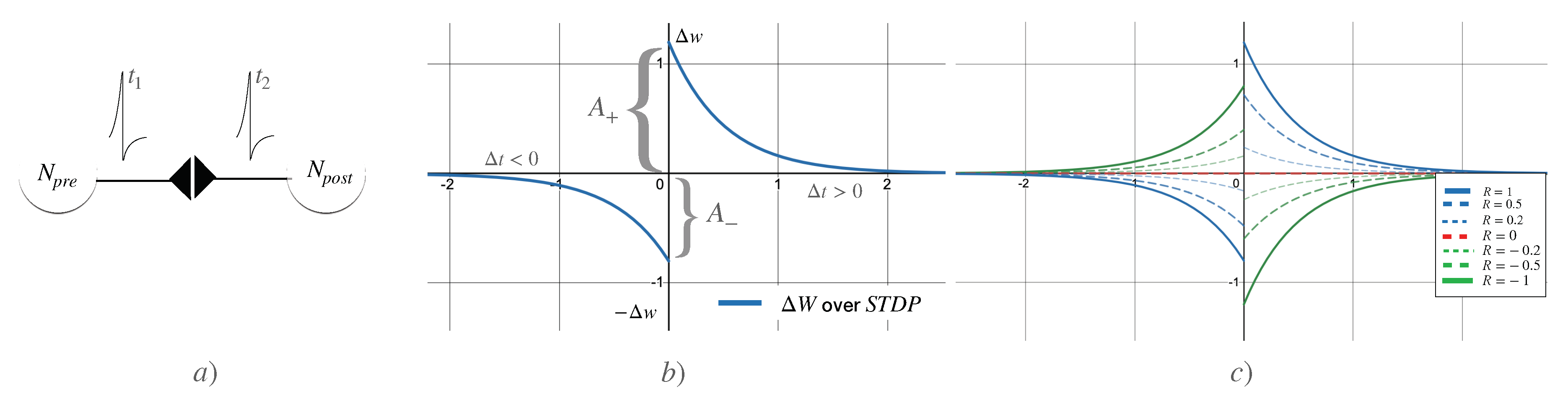

2.2. R-STDP Learning Rule

3. Materials and Methods

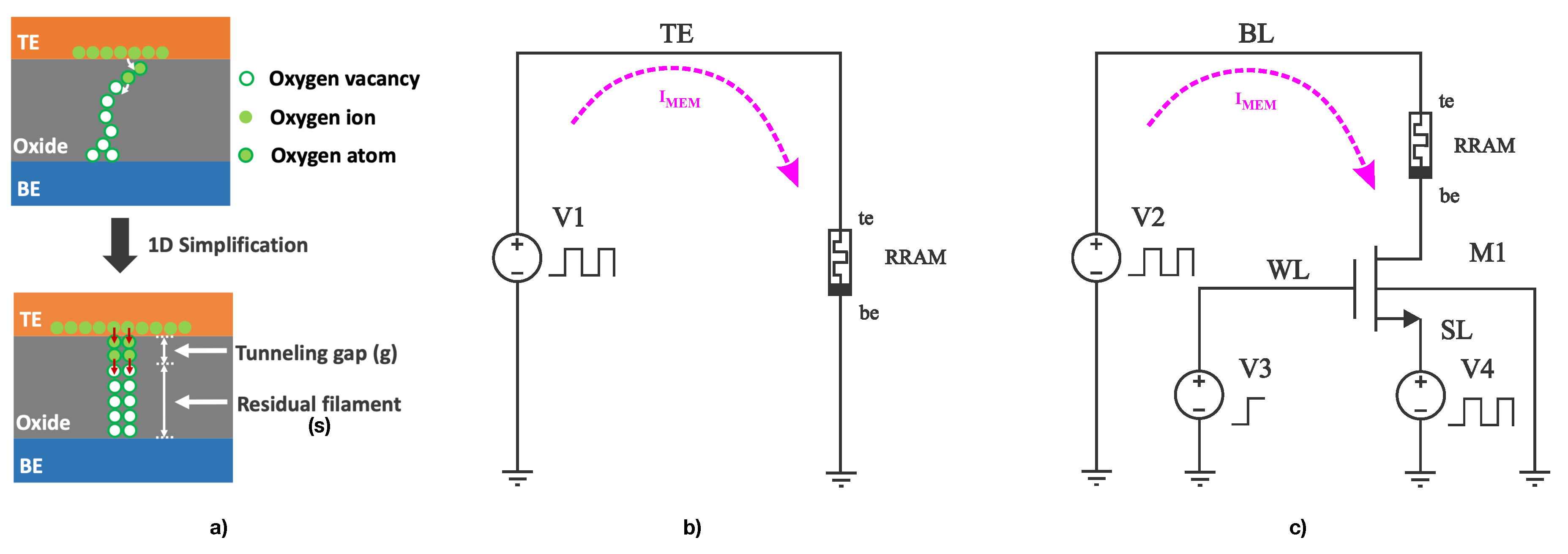

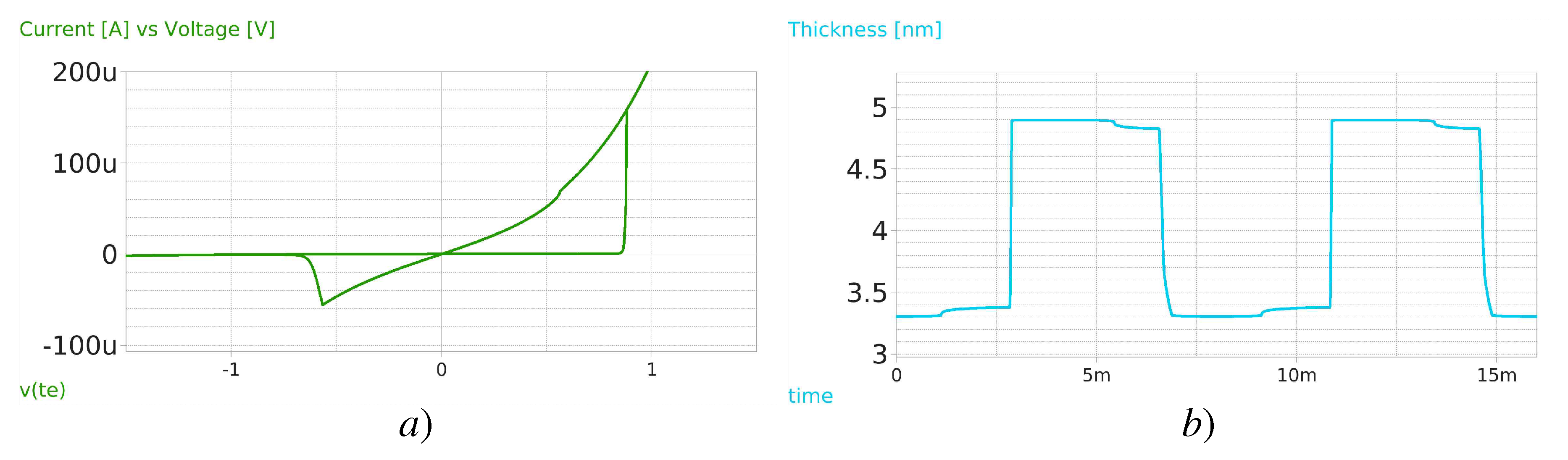

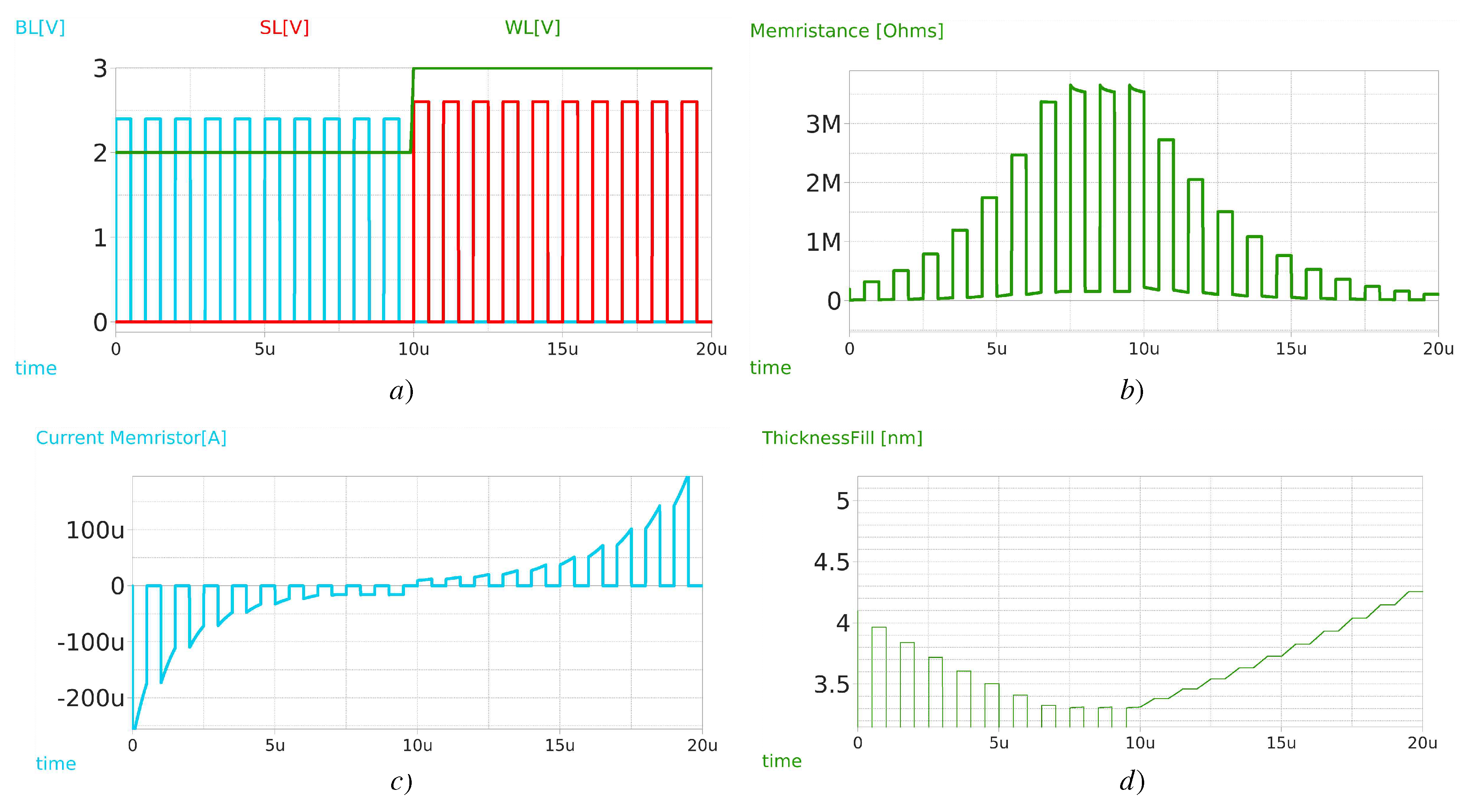

3.1. Memristor Device

- Defining TE, BE and the tip of the filament (i.e., g) as electric nodes in Verilog-A. As each node in an electrical circuit possesses properties (Voltage, Currents, Magnetic Flow, and charge), the compiler knows how to compute the current from the tip of the filament to , by using

- Providing alternative functions implementations for exp(), sinh(), to limit the maximum slope these can reach between the past and the next timestep. Several simulator engines use dynamic timestep selection for faster simulation periods and convergence issues. Of course, this limits the minimum timestep a simulator can use but avoids convergence issues or extended execution periods.

- Avoiding the usage of if-then-else statements to set the boundaries for the thickness of the filament. Instead, use a smooth, differentiable version of the unit step function.

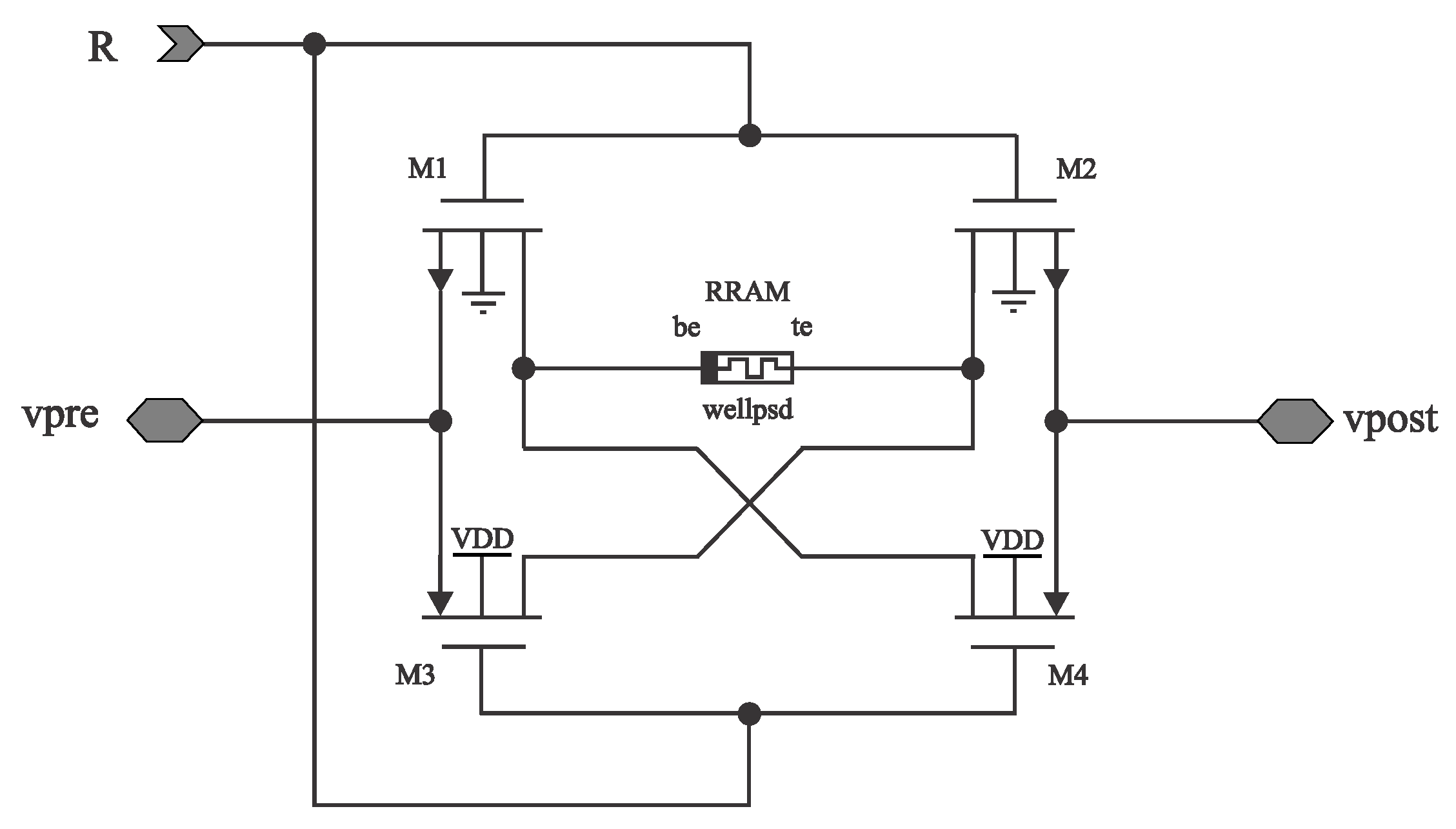

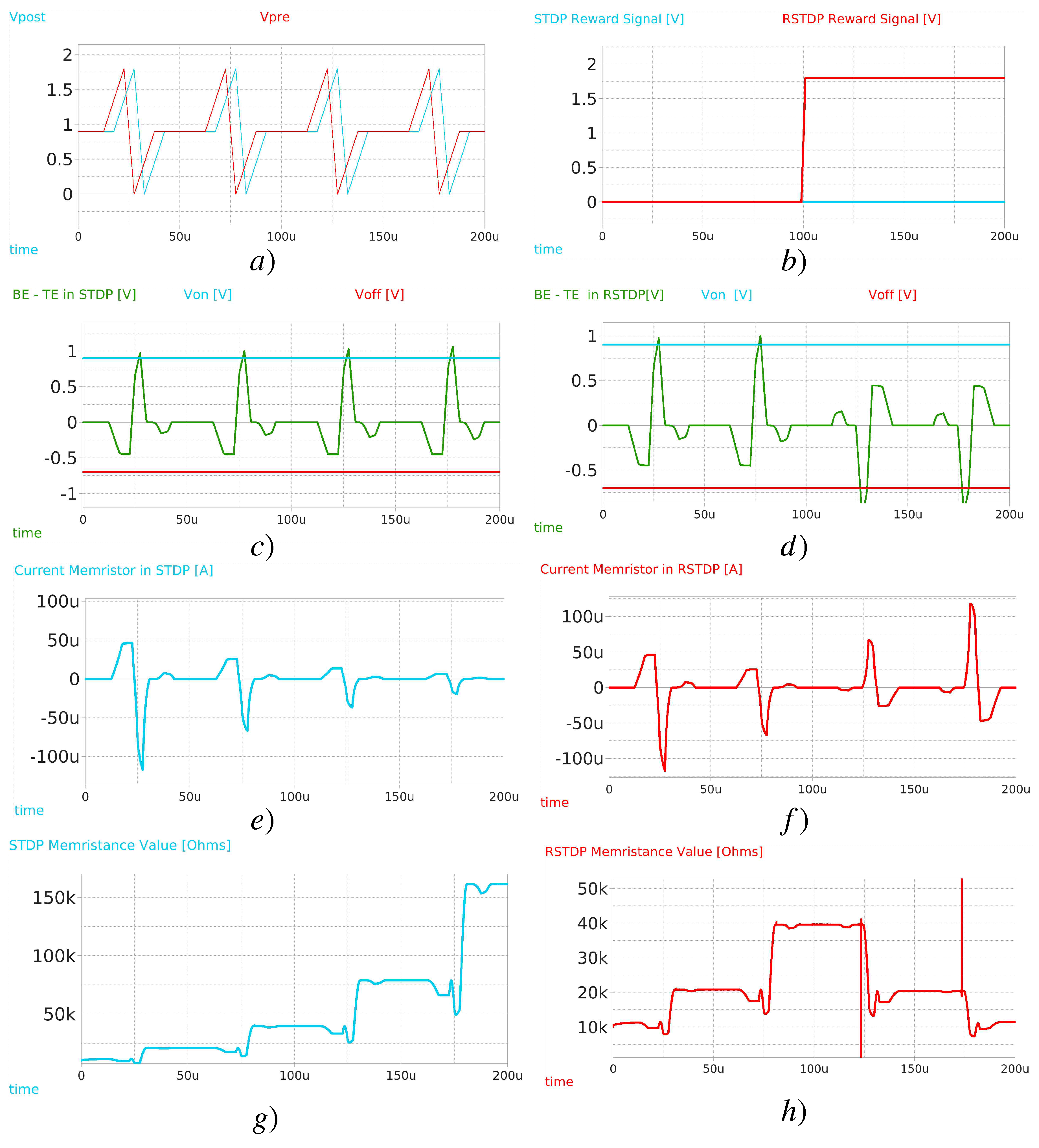

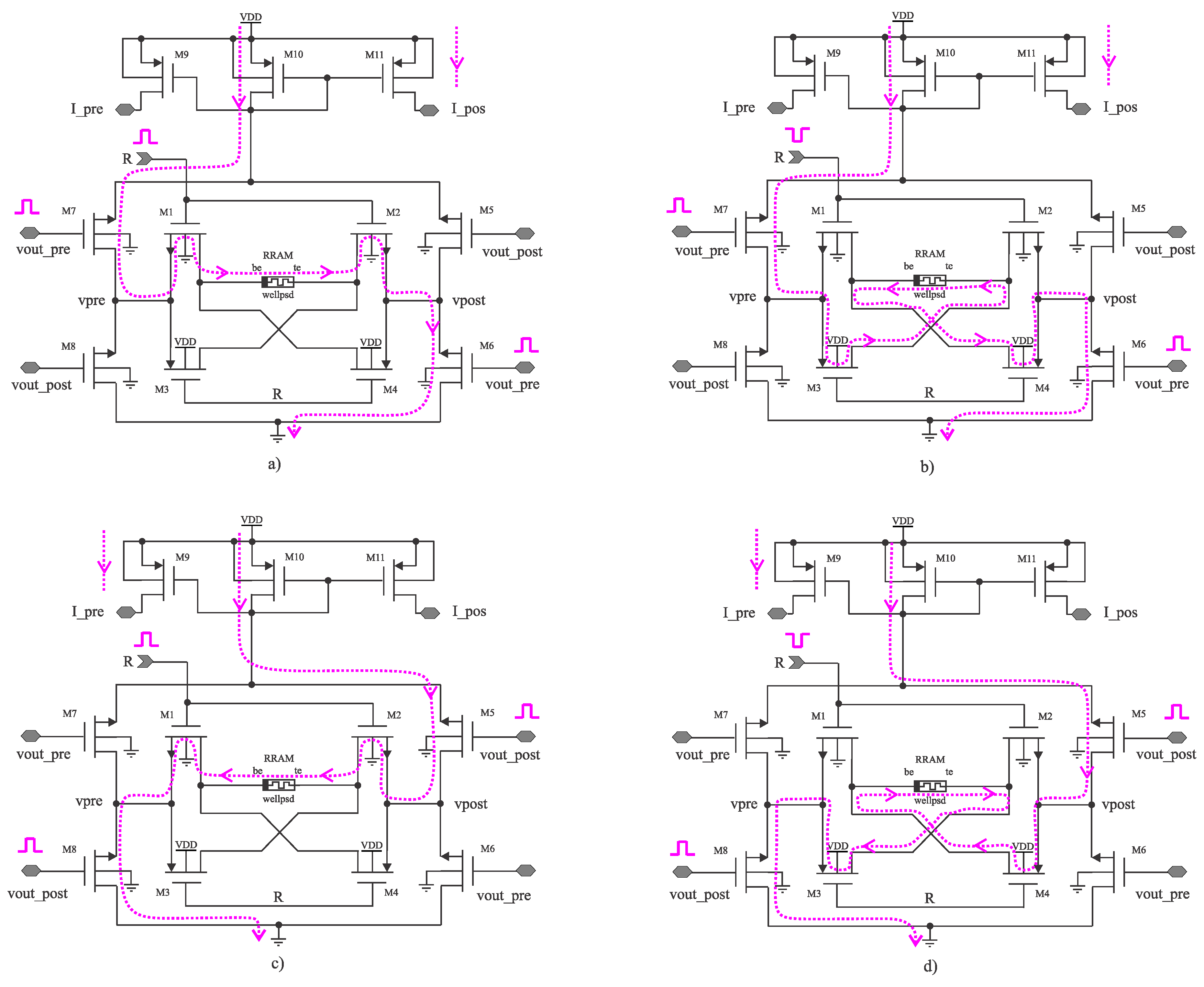

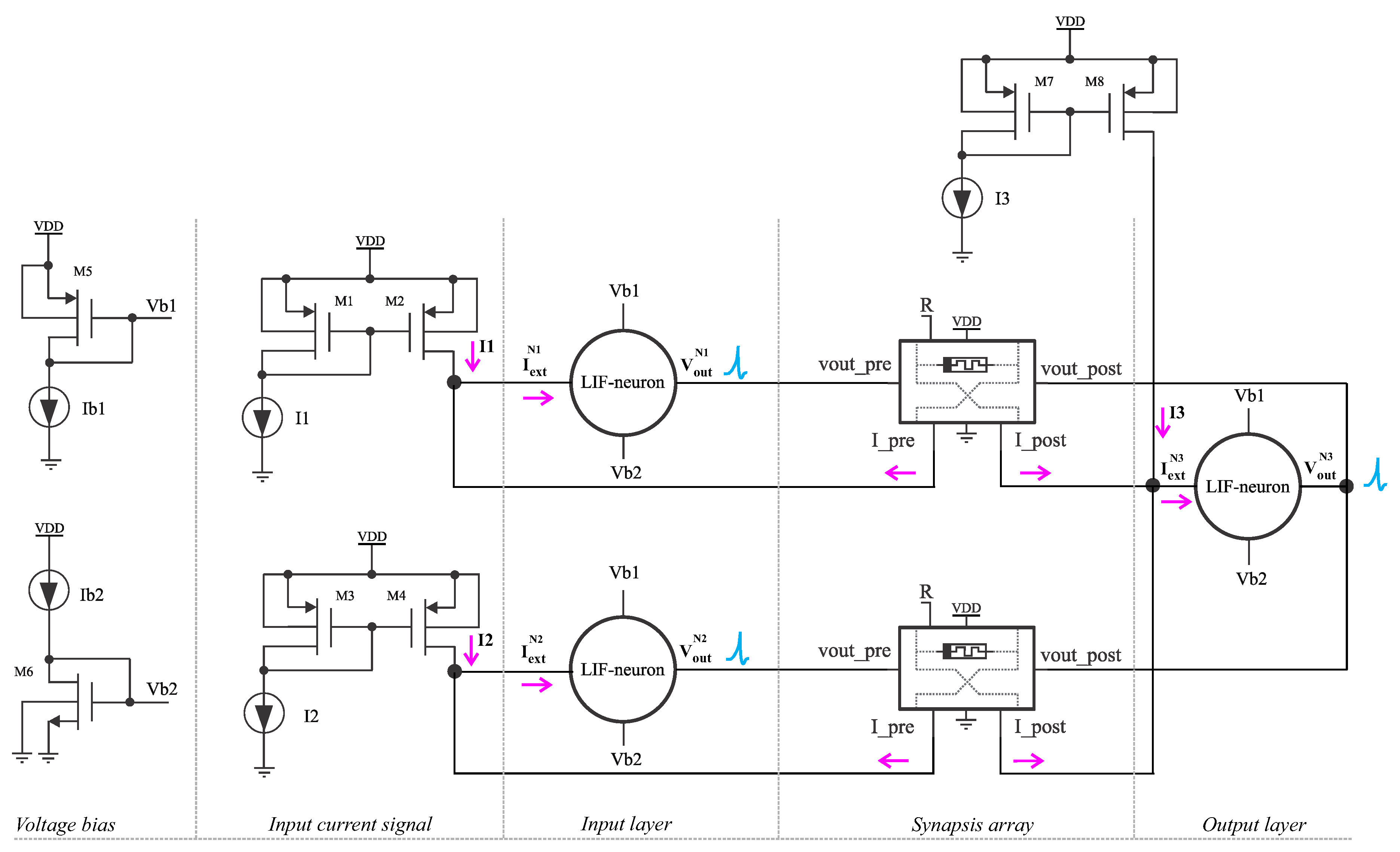

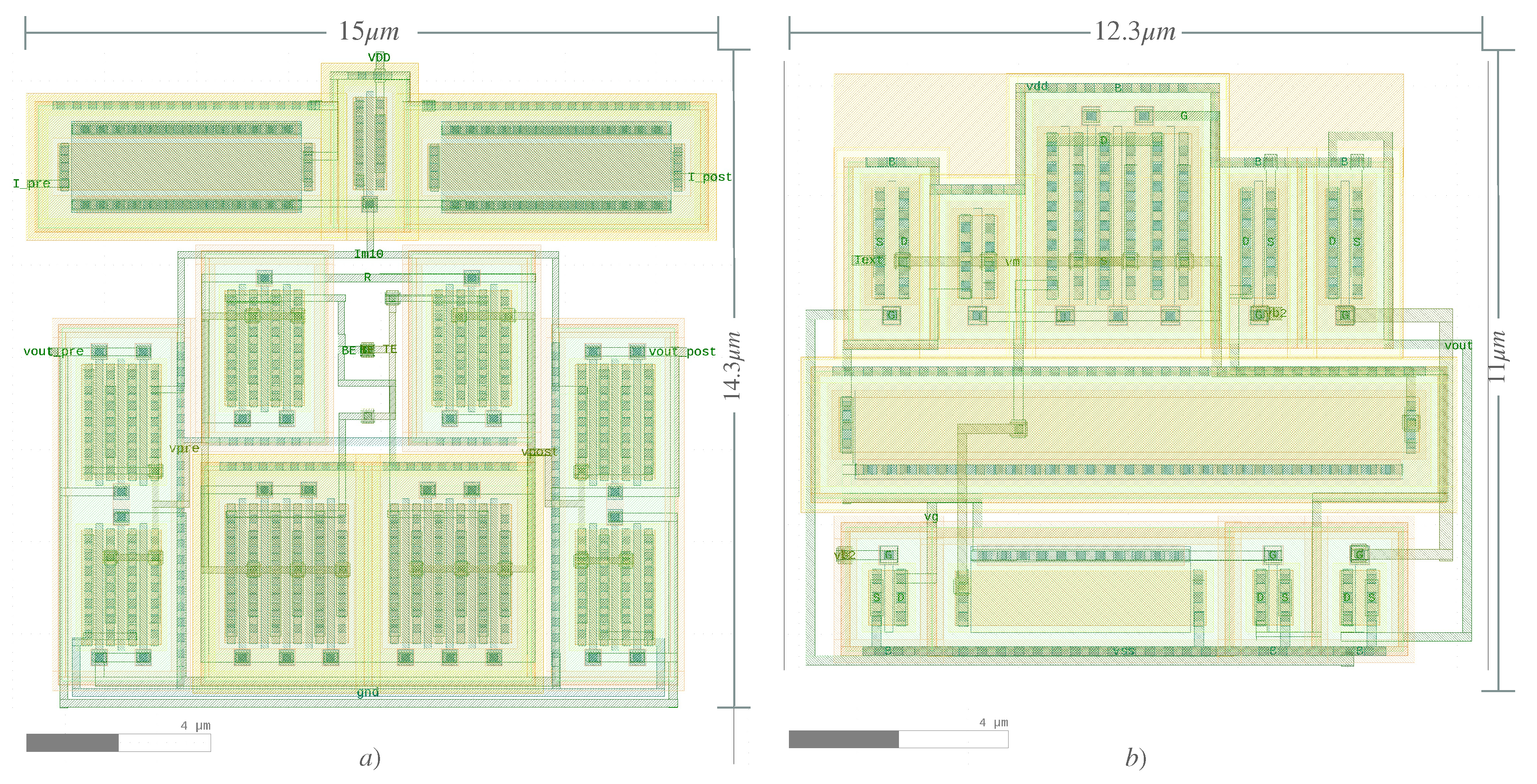

3.2. R-STDP Circuit Implementation

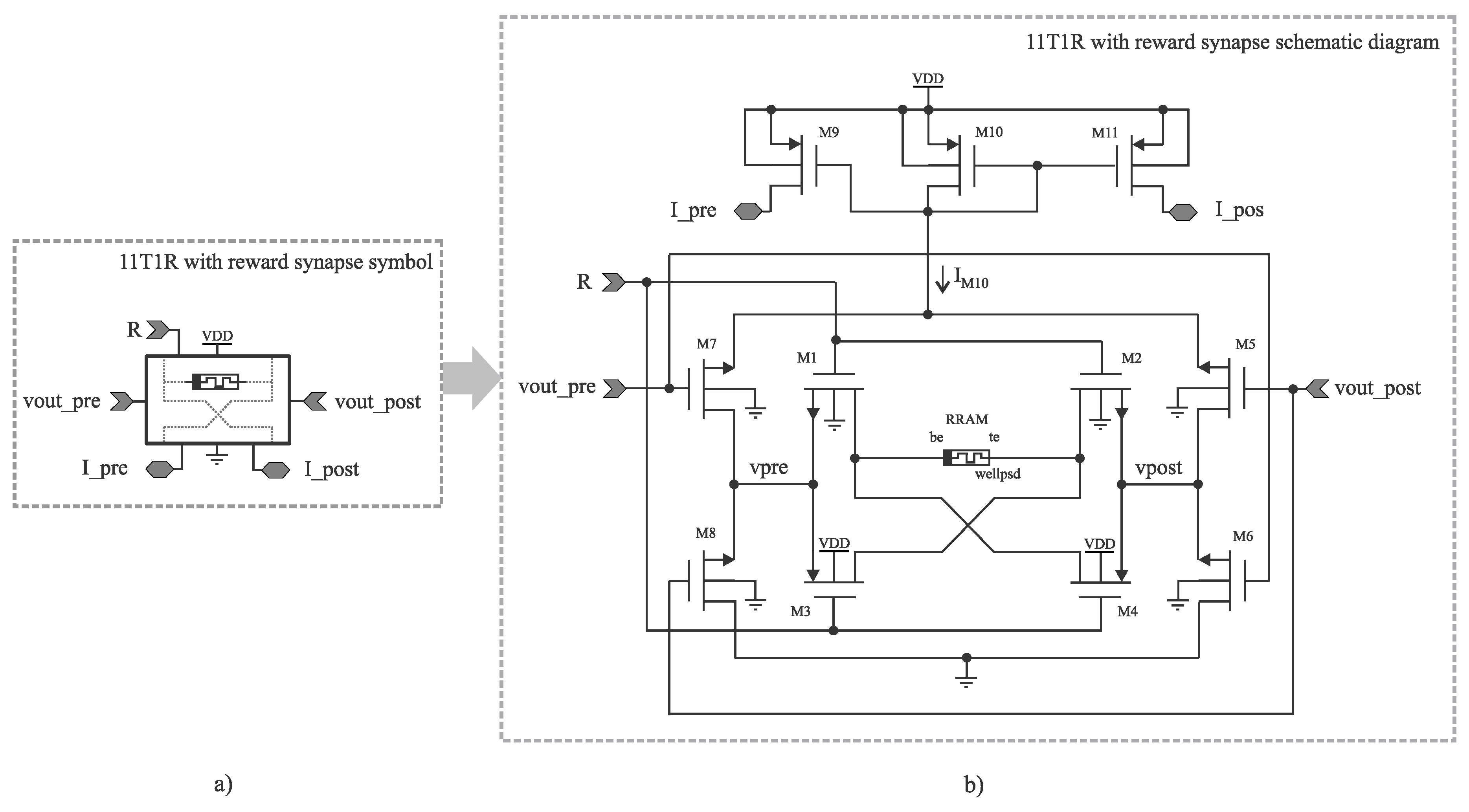

3.3. Adding Spike Reconformation and Current Decoupling to the Synapse

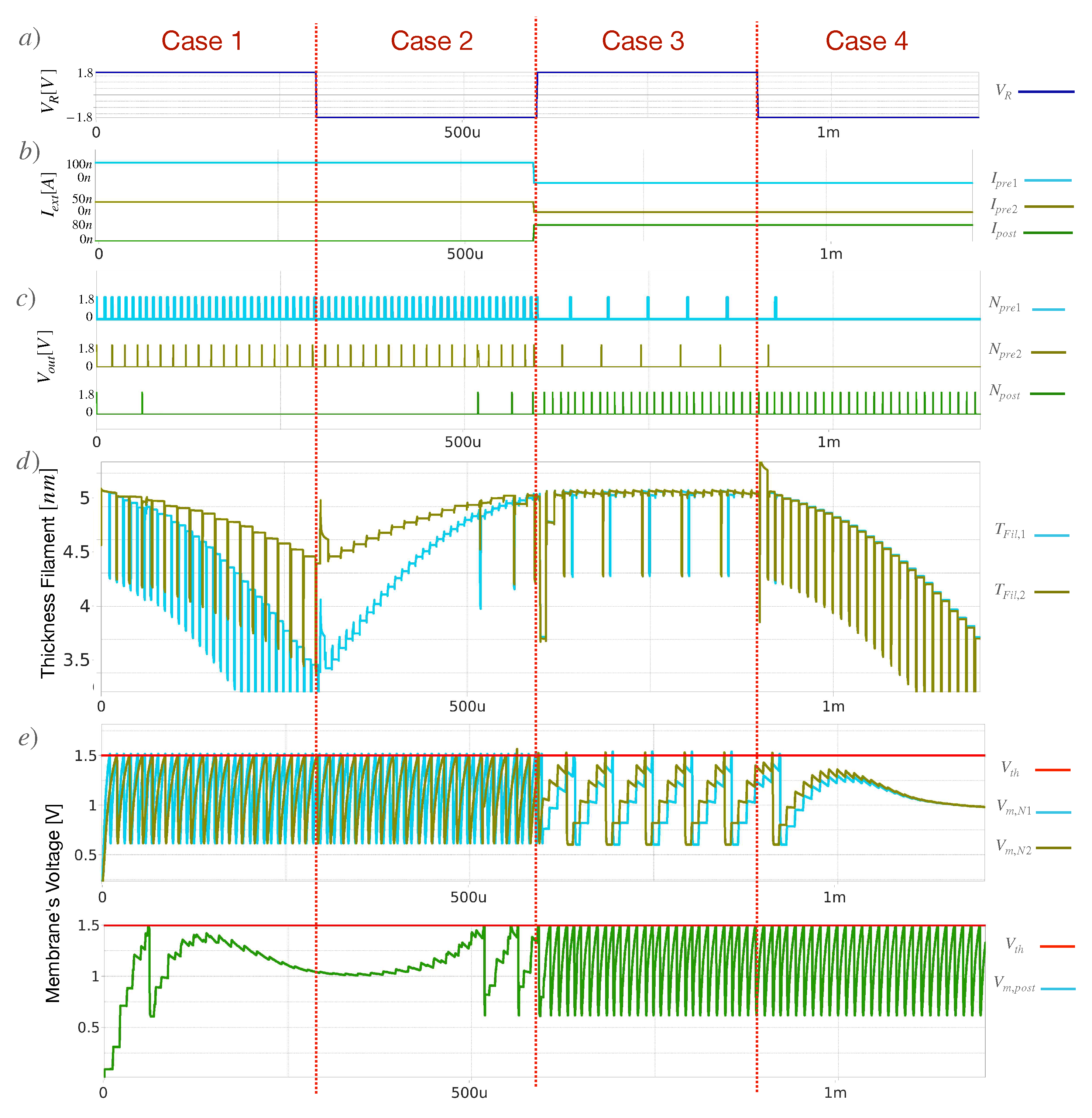

- . When a presynaptic spike arrives and the reward signal is on. This routes the current from BE to TE in the memristor, yielding to LTD;

- . Due to the reward signal being negative, the same spike train that should produce LTD now produces LTP, as the current flows from TE to BE;

- . Postsynaptic spikes with reward signal on, the current flows from TE to BE, producing LTP;

- . Postsynaptic spikes with a reward signal off, the current flows from BE to TE, producing LTD;

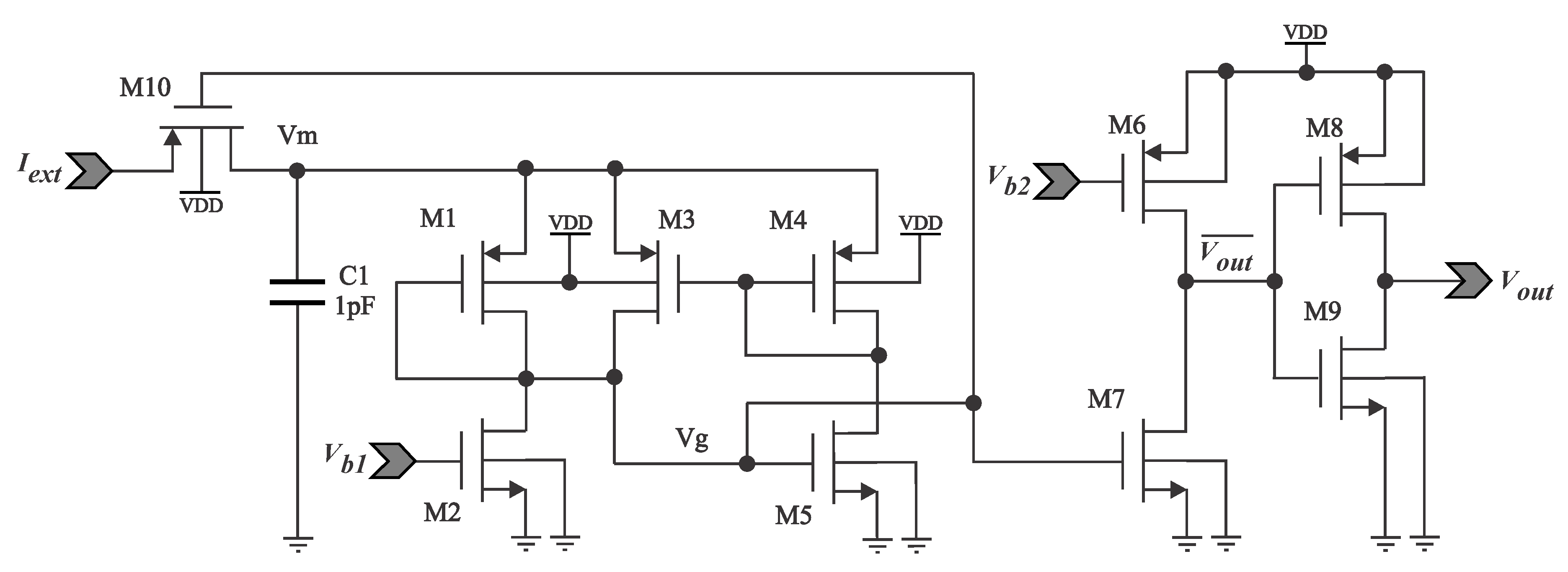

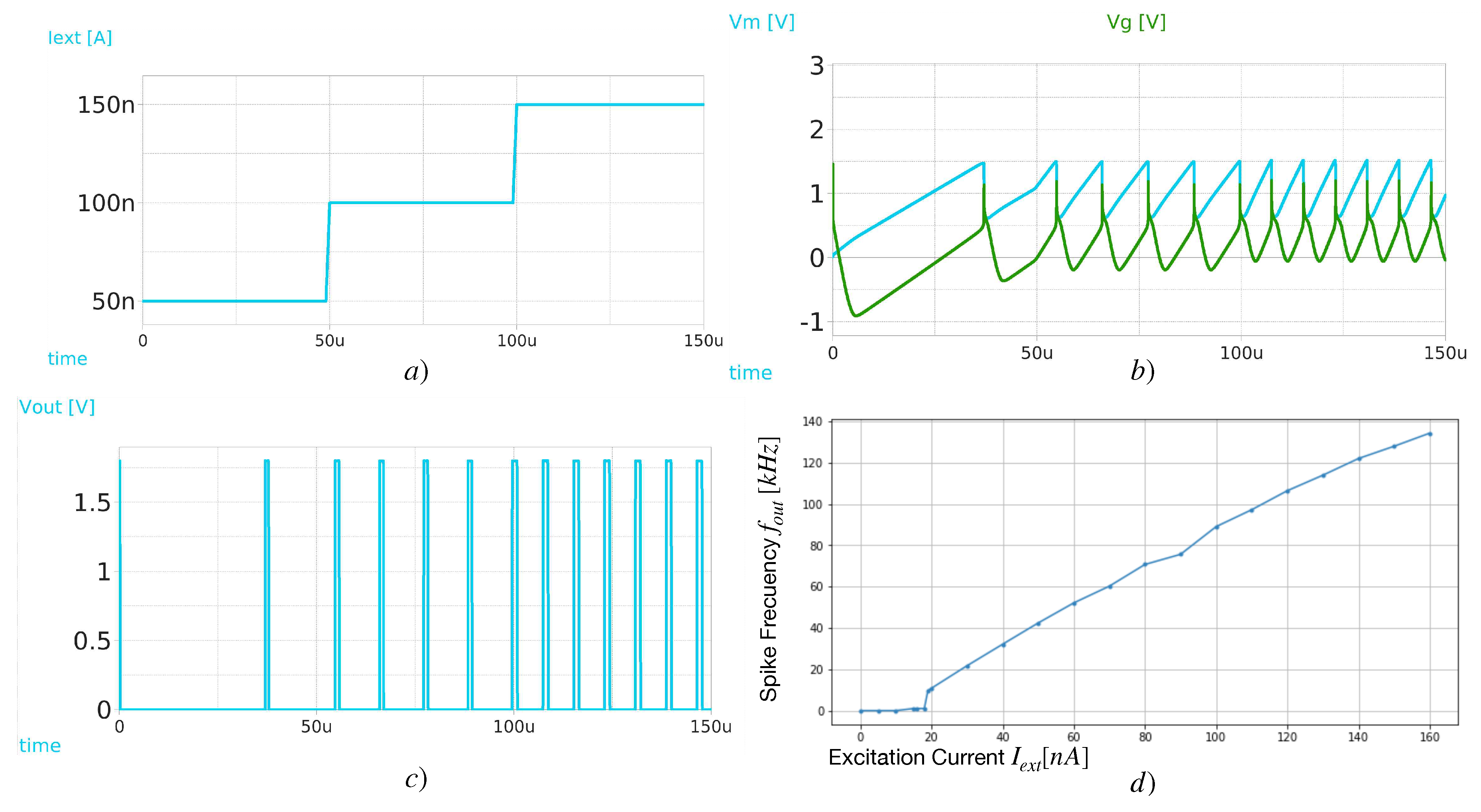

3.4. Neuron circuit

- An external input current excitation arrives through (PMOS), enabled at start. is set as a diode.

- charges for each incoming spike, increasing the voltage at node .

- A leaky current is flowing thourgh at all times. If no further incoming electrical impulses are received, the neuron will lose all of its electrical charge. defines .

- When , , which is the threshold voltage for the NMOS device, enabling the charge to flow through and .

- also turns on, enabling current to flow and making voltage at drops. At the same time, , turning off transistor , disabling current integration for the neuron.

- As drops, rises, as works as an inverter. controls the current of the transistor , and conforming the width of the spike. The node provides the final output spike, which can be fed to subsequent synapses.

- acts as a controlled diode, blocking any current from when the neuron is spiking.

4. Results

5. Discussion

5.1. Regarding the synapse circutry

5.2. Future Work towards Tailor-Made Neuromorphic Computing

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Abbreviations

| ADC | Analog to Digital Converter |

| BE | Bottom Electrode |

| CMOS | Complementary Metal Oxide Semiconductor |

| CPU | Central Processing Unit |

| DAC | Digital to Analog Converter |

| DDPG | Deep Deterministic Policy Gradient |

| FPGA | Field Programmable Gate Array |

| GAN | Generative Adversarial Network |

| GDS | Graphic Database System |

| GPU | Graphic Processing Unit |

| HRS | High Resistance State |

| IBM | International Business Machines |

| LIF | Leaky Integrate and Fire |

| LRS | Low Resistance State |

| LTD | Long Term Depreciation |

| LTP | Long Term Potentiation |

| MIM | Metal Insulator Metal |

| NMOS | Negative Metal Oxide Semiconductor |

| PCELL | Parametric Cell |

| PMOS | Positive Metal Oxide Semiconductor |

| RL | Reinforcement Learning |

| RRAM | Resistive Random Access Memory |

| RSTDP | Reward-Modulated Spike Time Dependant Plasticity |

| SNN | Spiking Neural Networks |

| SPICE | Simulation Program with Integrated Circuit Emphasis |

| STDP | Spike Time Dependant Plasticity |

| TAB | Trainable Analog Block |

| TCL | Tool Command Language |

| TD3 | Twin Delayed Deep Deterministic Policy Gradient |

| TE | Top Electrode |

| VTEAM | Voltage Threshold Adaptive Memristor |

References

- Akl, M.; Sandamirskaya, Y.; Walter, F.; Knoll, A. Porting Deep Spiking Q-Networks to Neuromorphic Chip Loihi. International Conference on Neuromorphic Systems 2021; Association for Computing Machinery: New York, NY, USA, 2021; ICONS 2021. [Google Scholar] [CrossRef]

- Matos, J.B.P.; de Lima Filho, E.B.; Bessa, I.; Manino, E.; Song, X.; Cordeiro, L.C. Counterexample Guided Neural Network Quantization Refinement. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 2024, 43, 1121–1134. [Google Scholar] [CrossRef]

- Gewaltig, M.O.; Diesmann, M. NEST (NEural Simulation Tool). Scholarpedia 2007, 2, 1430. [Accessed 20-05-2024]. [Google Scholar] [CrossRef]

- Eshraghian, J.K.; Ward, M.; Neftci, E.; Wang, X.; Lenz, G.; Dwivedi, G.; Bennamoun, M.; Jeong, D.S.; Lu, W.D. Training spiking neural networks using lessons from deep learning. Proceedings of the IEEE 2023, 111, 1016–1054. [Google Scholar] [CrossRef]

- Bekolay, T.; Bergstra, J.; Hunsberger, E.; DeWolf, T.; Stewart, T.; Rasmussen, D.; Choo, X.; Voelker, A.; Eliasmith, C. Nengo: a Python tool for building large-scale functional brain models. Frontiers in Neuroinformatics 2014, 7, 1–13. [Accessed 20-05-2024]. [Google Scholar] [CrossRef] [PubMed]

- Khan, S.Q.; Ghani, A.; Khurram, M. Population coding for neuromorphic hardware. Neurocomputing 2017, 239, 153–164. [Google Scholar] [CrossRef]

- Thakur, C.S.; Hamilton, T.J.; Wang, R.; Tapson, J.; van Schaik, A. A neuromorphic hardware framework based on population coding. 2015 International Joint Conference on Neural Networks (IJCNN), 2015, pp. 1–8. [CrossRef]

- Schöfmann, C.M.; Fasli, M.; Barros, M.T. Investigating Biologically Plausible Neural Networks for Reservoir Computing Solutions. IEEE Access 2024, 12, 50698–50709. [Google Scholar] [CrossRef]

- Juárez-Lora, A.; García-Sebastián, L.M.; Ponce-Ponce, V.H.; Rubio-Espino, E.; Molina-Lozano, H.; Sossa, H. Implementation of Kalman Filtering with Spiking Neural Networks. Sensors 2022, 22. [Google Scholar] [CrossRef] [PubMed]

- Li, X.; Sun, J.; Sun, Y.; Wang, C.; Hong, Q.; Du, S.; Zhang, J. Design of Artificial Neurons of Memristive Neuromorphic Networks Based on Biological Neural Dynamics and Structures. IEEE Transactions on Circuits and Systems I: Regular Papers 2024, 71, 2320–2333. [Google Scholar] [CrossRef]

- Shi, C.; Lu, J.; Wang, Y.; Li, P.; Tian, M. Exploiting Memristors for Neuromorphic Reinforcement Learning. 2021 IEEE 3rd International Conference on Artificial Intelligence Circuits and Systems (AICAS), 2021, pp. 1–4. [CrossRef]

- Akl, M.; Ergene, D.; Walter, F.; Knoll, A. Toward robust and scalable deep spiking reinforcement learning. Frontiers in Neurorobotics 2023, 16. [Google Scholar] [CrossRef] [PubMed]

- Hsieh, E.; Zheng, X.; Nelson, M.; Le, B.; Wong, H.S.; Mitra, S.; Wong, S.; Giordano, M.; Hodson, B.; Levy, A.; Osekowsky, S.; Radway, R.; Shih, Y.; Wan, W.; Wu, T.F. High-Density Multiple Bits-per-Cell 1T4R RRAM Array with Gradual SET/RESET and its Effectiveness for Deep Learning. 2019 IEEE International Electron Devices Meeting (IEDM). IEEE, 2019. [CrossRef]

- Wang, T.; Roychowdhury, J. Well-Posed Models of Memristive Devices 2016.

- Jiang, Z.; Yu, S.; Wu, Y.; Engel, J.H.; Guan, X.; Wong, H.S.P. Verilog-A compact model for oxide-based resistive random access memory (RRAM). 2014 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), 2014, pp. 41–44. [CrossRef]

- Alshaya, A.; Han, Q.; Papavassiliou, C. RRAM, Device, Model and Memory. 2022 International Conference on Microelectronics (ICM). IEEE, 2022. [CrossRef]

- Alshaya, A.; Malik, A.; Mifsud, A.; Papavassiliou, C. Comparison of 1T1R and 1C1R ReRAM Arrays. Journal of Physics: Conference Series 2023, 2613, 012010. [Google Scholar] [CrossRef]

- Alshaya, A.; Han, Q.; Papavassiliou, C. Passive Selectorless Memristive Structure with One Capacitor-One Memristor. 2022 International Conference on Microelectronics (ICM), 2022, pp. 121–124. [CrossRef]

- Skywater. User Guide 2014; SkyWater SKY130PDK 0.0.0-22-g72df095 documentation. https://sky130-fd-pr-reram.readthedocs.io/en/latest/user_guide.html, 2019. [Accessed 25-04-2024].

- Xyce(™) Parallel Electronic Simulator. [Computer Software] https://doi.org/10.11578/dc.20171025.1421, 2013. [CrossRef]

- Juarez-Lora, A. GitHub - AlejandroJuarezLora. SNN-IPN, MICROSE-IPN. https://github.com/AlejandroJuarezLora/SNN_IPN, 2024. [Accessed 25-04-2024].

- Kuthe, P.; Muller, M.; Schroter, M. VerilogAE: An Open Source Verilog-A Compiler for Compact Model Parameter Extraction. IEEE Journal of the Electron Devices Society 2020, 8, 1416–1423. [Google Scholar] [CrossRef]

- Vogt, H. Ngspice, the open source Spice circuit simulator - Intro — ngspice.sourceforge.io. https://ngspice.sourceforge.io/index.html, 2024. [Accessed 25-04-2024].

- Tian, M.; Lu, J.; Gao, H.; Wang, H.; Yu, J.; Shi, C. A Lightweight Spiking GAN Model for Memristor-centric Silicon Circuit with On-chip Reinforcement Adversarial Learning. 2022 IEEE International Symposium on Circuits and Systems (ISCAS), 2022, pp. 3388–3392. [CrossRef]

- Stoliar, P.; Akita, I.; Schneegans, O.; Hioki, M.; Rozenberg, M.J. A spiking neuron implemented in VLSI. Journal of Physics Communications 2022, 6, 021001. [Google Scholar] [CrossRef]

- Kvatinsky, S.; Ramadan, M.; Friedman, E.G.; Kolodny, A. VTEAM: A General Model for Voltage-Controlled Memristors. IEEE Transactions on Circuits and Systems II: Express Briefs 2015, 62, 786–790. [Google Scholar] [CrossRef]

- Edwards, T. Magic User Guide, 2024.

| 4T1M structure | 11T1M | Neuron | testbench |

|---|---|---|---|

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).