Submitted:

07 May 2024

Posted:

07 May 2024

You are already at the latest version

Abstract

Keywords:

1. Introduction

2. Preparation, Measurements Fitting Algorithm

2.1. Preparation and Measurement of NFinFET

2.2. Fitting IDS-VDS and IDS-VGS

2.3. Fitting Algoritm

3. Results

4. Analysis and Discussion

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Appendix A

| Yes | Can be improved | Must be improved | Not applicable | |

| Does the introduction provide sufficient background and include all relevant references? | ( ) | ( ) | (x) | ( ) |

| Are all the cited references relevant to the research? | ( ) | ( ) | (x) | ( ) |

| Is the research design appropriate? | ( ) | ( ) | (x) | ( ) |

| Are the methods adequately described? | ( ) | ( ) | (x) | ( ) |

| Are the results clearly presented? | ( ) | ( ) | (x) | ( ) |

| Are the conclusions supported by the results? | ( ) | ( ) | (x) | ( ) |

where α is a viscosity coefficient, m is the mass of carriers, and E is the electrical force coming from the applied bias across the channel. Before electrons reach the maximum speed,

where α is a viscosity coefficient, m is the mass of carriers, and E is the electrical force coming from the applied bias across the channel. Before electrons reach the maximum speed, where l is the traverse distance length that the electron travels as E is applied. So,

where l is the traverse distance length that the electron travels as E is applied. So, where

where

and

and

which gives the information that the mobility in the conventional ID(VD, VG) formula in Equation (2) is constant only when N=1 at certain fixed gate bios.

which gives the information that the mobility in the conventional ID(VD, VG) formula in Equation (2) is constant only when N=1 at certain fixed gate bios.| Yes | Can be improved | Must be improved | Not applicable | |

| Does the introduction provide sufficient background and include all relevant references? | ( ) | ( ) | ( ) | (x) |

| Are all the cited references relevant to the research? | ( ) | ( ) | (x) | ( ) |

| Is the research design appropriate? | ( ) | ( ) | ( ) | (x) |

| Are the methods adequately described? | ( ) | ( ) | ( ) | (x) |

| Are the results clearly presented? | ( ) | ( ) | (x) | ( ) |

| Are the conclusions supported by the results? | ( ) | ( ) | (x) | ( ) |

References

- Diab, A.; Torres Sevilla, G.-A.; Christoloveanu, S.; and Hussain, M.-M. Room to high temperature measurements of flexible SOI FinFETs with sub-20-nm fins. IEEE Trans. Electron. Devices 2014, 61, 3978. [Google Scholar] [CrossRef]

- Wang, F.; Xie, Y.; Bernstein, K.; Luo, Y. Dependability analysis of nano-scale FinFET circuits. In Proceedings of the IEEE Computer Society Annual Symposium on Emerging VLSI Technologies and Architectures (ISVLSI'06), Karlsruhe, Germany, 2–3 March 2006; pp 6, 399.

- Huang, X.; Lee, W.-C.; Kuo, C.; Hisamoto, D.; Chang, L.; Kedzierski, J.; Anderson, E.; Takeuchi, H.; Choi, Y.-K.; Asano, K.; et al. Sub-50 nm P-channel FinFET. IEEE Trans. Electron. Devices 2001, 48, 880. [Google Scholar] [CrossRef]

- Rudenko, T. , Kilchytska, V., Arshad, M.K.M., Raskin, J.-P., Nazarov, A. and Flandre, D. On the MOSFET Threshold Voltage Extraction by Transconductance and Transconductance-to-Current Ratio Change Methods: Part II-Effect of Drain Voltage. IEEE Trans. Electron. Devices, 2011; 58, 4180–4188. [Google Scholar]

- Takahashi, T.; Beppu, N.; Chen, K.; Oda, S.; Uchida, K. Self-heating effects and analog performance optimization of Fin-type field-effect transistors. Jpn. J. Appl. Phys. 2013, 52, 04CC03. [Google Scholar] [CrossRef]

- Saitoh, M.; Yasutake, N.; Nakabayashi, Y.; Uchida, K.; Numata, T. Understanding of strain effects on high-field carrier velocity in (100) and (110) CMOSFETs under quasi-ballistic transport. 2009 IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, USA, 07-09 December; pp. 1-4.

- Chen, C.W.; Wang, S.J.; Hsieh, W.C.; Chen, J.M.; Jong, T.; Lan, W.H.; Wang, M.C. Q-factor Performance of 28 nm-node High-k Gate Dielectric under DPN Treatment at Different Annealing Temperatures. Electronics 2020, 9, 2086. [Google Scholar] [CrossRef]

- Lu, P.; Yang, C.; Li, Y.; Li, B.; Han, Z. Three-Dimensional TID Hardening Design for 14 nm Node SOI FinFETs. Eng 2021, 2, 620–631. [Google Scholar] [CrossRef]

- Song, Y.S.; Tayal, S.; Rahi, S.B.; Kim, J.H.; Upadhyay, A.K.; Park, B.-G. Thermal-Aware IC Chip Design by Combining High Thermal Conductivity Materials and GAA MOSFET. In Proceedings of the 2022 5th International Conference on Circuits, Systems and Simulation (ICCSS), Nanjing, China, 13-15 May 2022; pp. 135–140. [Google Scholar]

- Crupi, G.; Schreurs, D.M.M.-P.; Caddemi, A.; Angelov, I.; Homayouni, M.; Raffo, A.; Vannini, G.; Parvais, B. Purely analytical extraction of an improved nonlinear FinFET model including non-quasi-static effects. Microelectron. Eng. 2009, 86, 2283–2289. [Google Scholar] [CrossRef]

- Li, Y.; Zhao, F.; Cheng, X.; Liu, H.; Zan, Y.; Li, J.; Zhang, Q.; Wu, Z.; Luo, J.; Wang, W. Four-Period Vertically Stacked SiGe/Si Channel FinFET Fabrication and Its Electrical Characteristics. Nanomaterials 2021, 11, 1689. [Google Scholar] [CrossRef] [PubMed]

- Zhao, E.; Zhang, J.; Salman, A.; Subba, N.; Chan, J.; Marathe, A.; Beebe, S.; Taylor, K. Reliability challenges of high performance PD SOI CMOS with ultra-thin gate dielectrics. Solid State Electron. 2004, 48, 1703–1708. [Google Scholar] [CrossRef]

- Zhao, Z.Q.; Li, Y.; Zan, Y.; Li, Y.L.; Li, J.J.; Cheng, X.H.; Wang, G.L.; Liu, H.Y.; Wang, H.X.; Zhang, Q.Z.; et al. Fabrication technique of the Si0.5Ge0.5 Fin for the high mobility channel FinFET device. Semicond. Sci. Technol. 2020, 35, 045015. [Google Scholar] [CrossRef]

- Lee, J.; Park, T.; Ahn, H.; Kwak, J.; Moon, T.; Shin, C. Prediction Model for Random Variation in FinFET Induced by Line-Edge-Roughness (LER). Electronics 2021, 10, 455. [Google Scholar] [CrossRef]

- B. Van Zeghbroeck, Priciples of Semiconductor Devices, Chapter 7.6 Advanced MOSFET issues. http: //ece-www. colorado. edu/~bart/ book/book/title.htm [2/28/2002 5:26:12 PM].

- Yang, H.-C.; Chi, S.-C. Process Corresponding Implications Associated with a Conclusive Model-Fit Current-Voltage Characteristic Curves. Appl. Sci. 2022, 12, 462. [Google Scholar] [CrossRef]

- Yang, H.-C.; Chi, S.-C.; Liao, W.S. Comparison of Fitting Current–Voltage Characteristics Curves of FinFET Transistors with Various Fixed Parameter. Appl. Sci. 2022, 12, 10519. [Google Scholar] [CrossRef]

- Ryder, L. H. The sine-Gordon kink, In Quantum Field Theory, the Press Syndicate of the University of Cambridge, Cambridge , UK, 1985, pp402.

- D. Lacroix, I. Traore, S. Fumwron, and G. Jeandel. Phonon transport in silicon, influence of the dispersion properties choice on the description of the anharmonics resistive mechanisms. Eur. Phys. J. B 2009, 67, 15–25.

- Kang, S.-M.; Leblebici, Y. CMOS Digital Integrated Circuits: analysis and design, Chapter 4 Modeling of MOS Transistors Using SPICE, p111, Published by McGRAW-Hill International Editions, ISBN 0-07-114423-4.

- Yang, H.-C.; Chi, S.-C. Conclusive Model-Fit Current Voltage Characteristic Curves with Kink Effects. Appl. Sci. 2023, 13, 12379. [Google Scholar] [CrossRef]

- Yang, H.-C. , Jui-Ming Tsai, Tsin-Yuan Chang, Wen-Shiang Liao, Sung-Ching Chi; The Effects of Thickness of Source/Drain Fin on P-Channel FinFET Devices and the Corresponding Quantum Effects, p165-169, Nano-science Nanotechnology Lett. 2014, Vol 6, No 2.

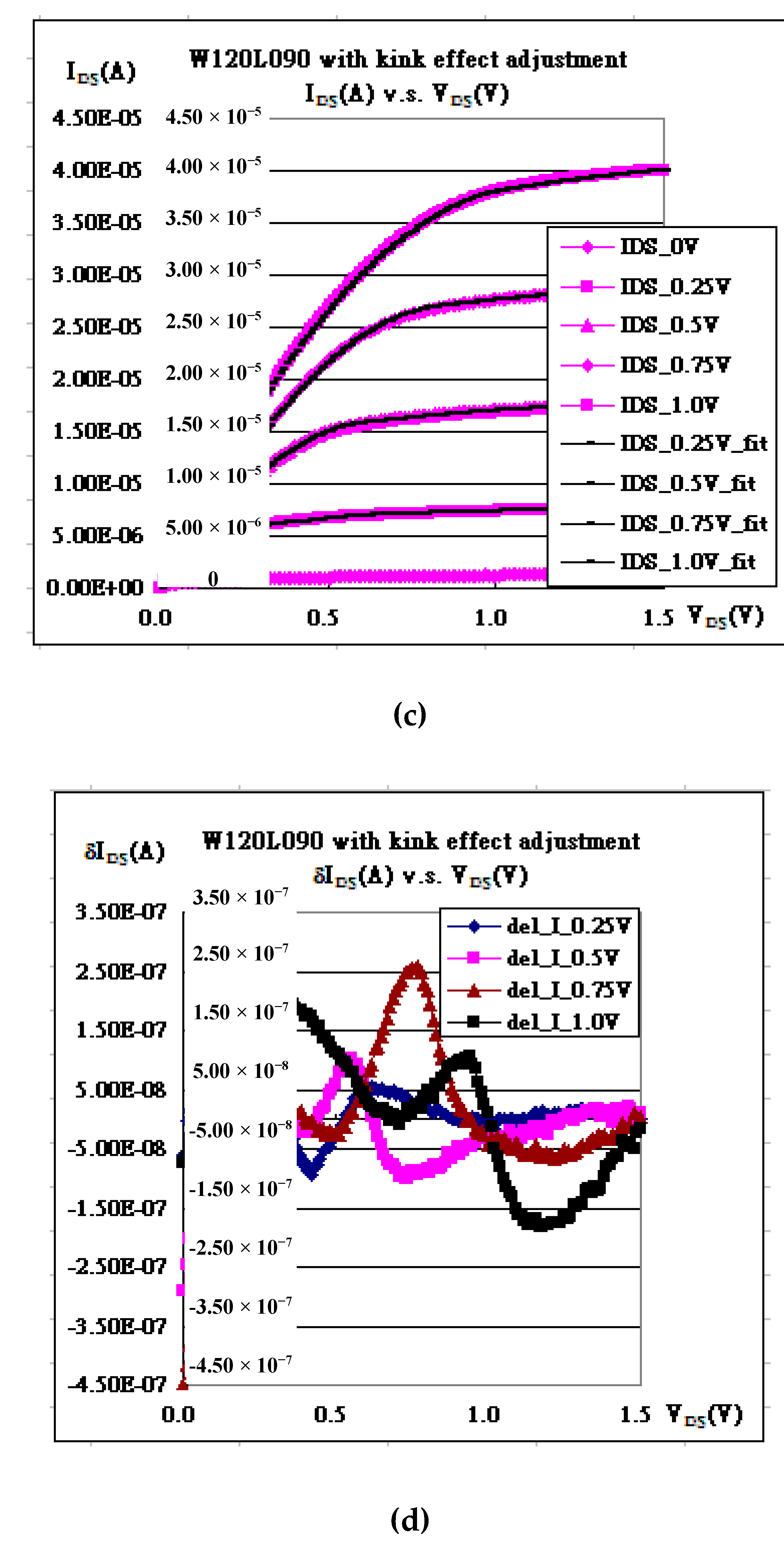

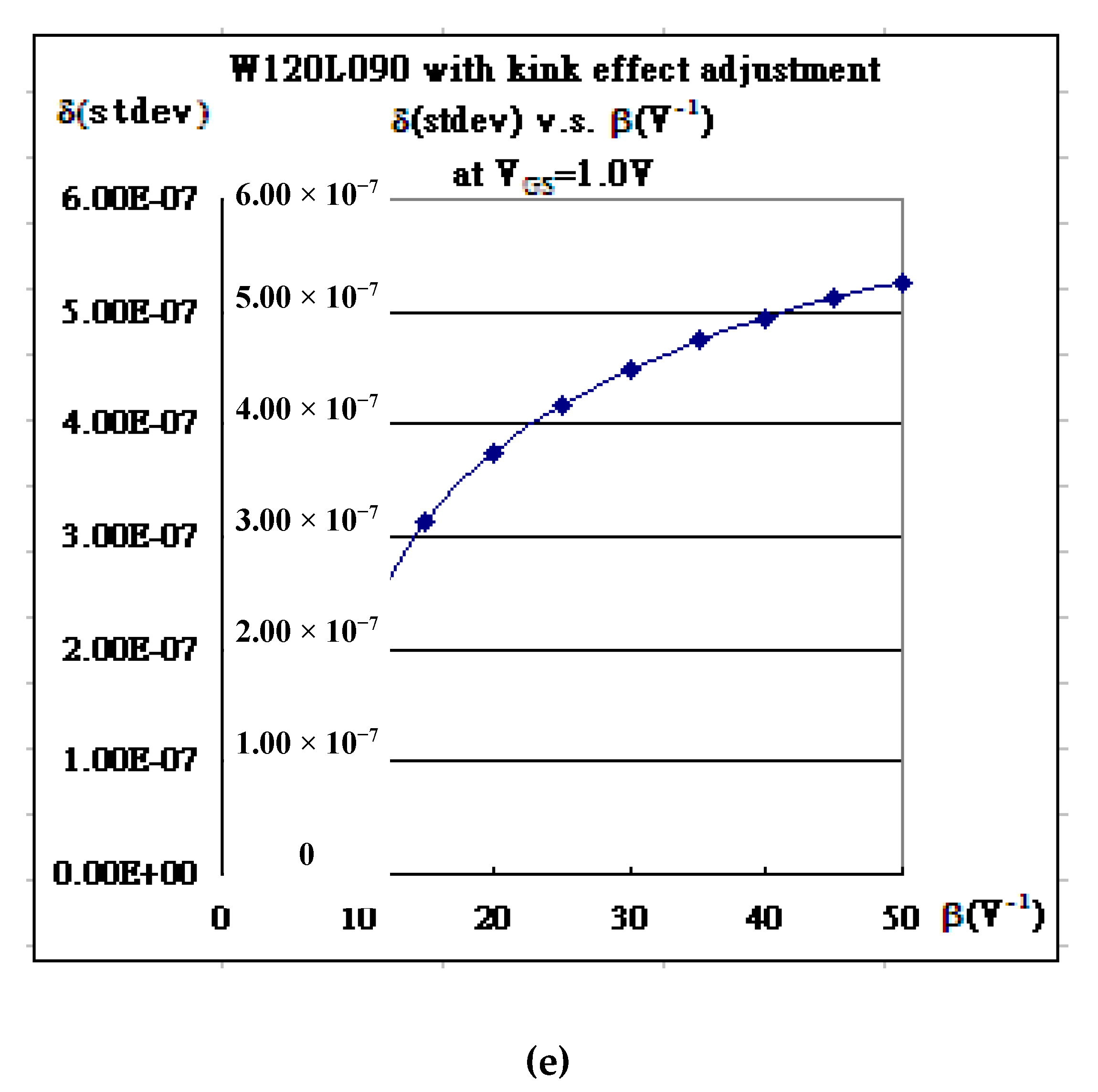

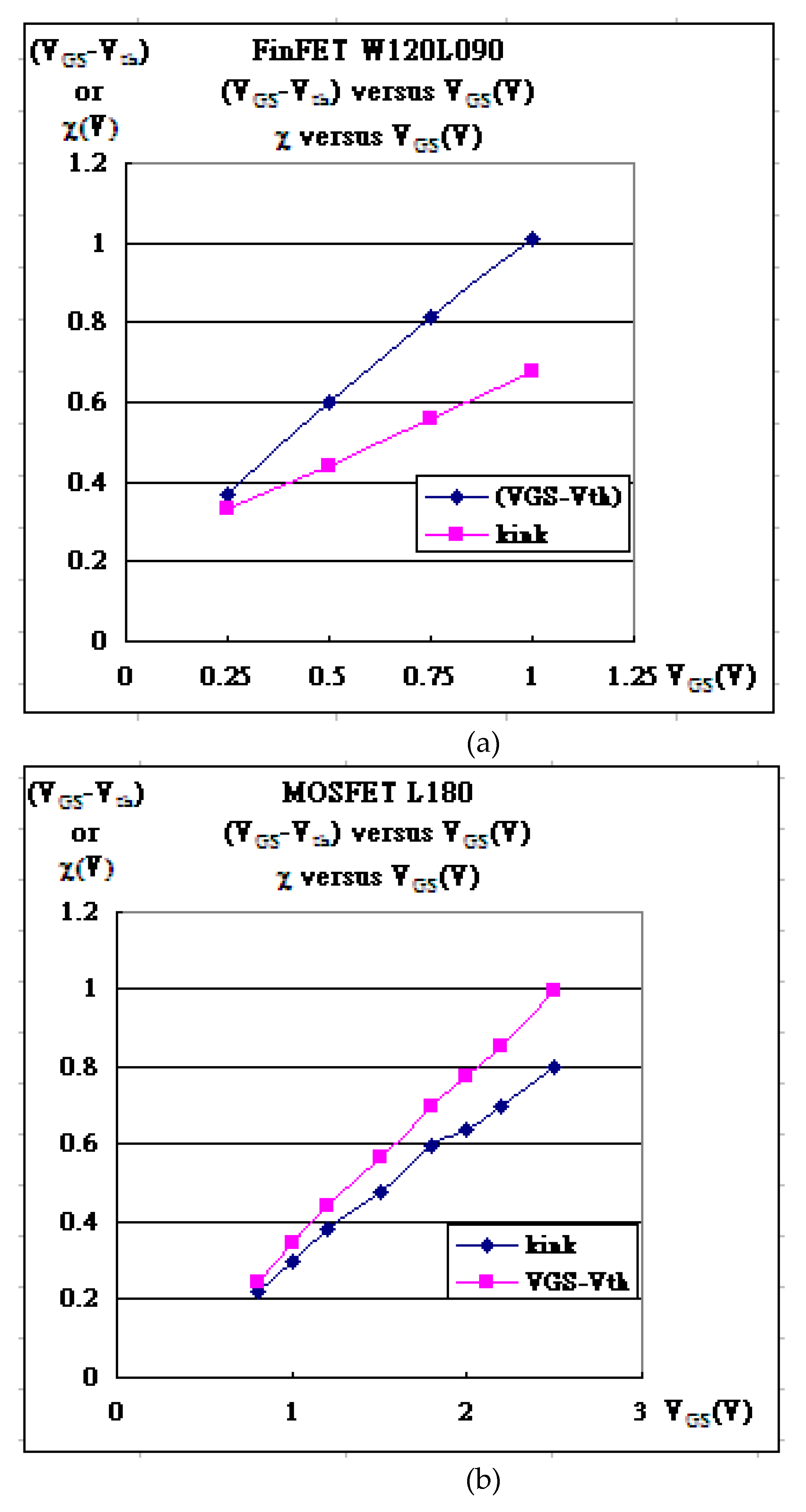

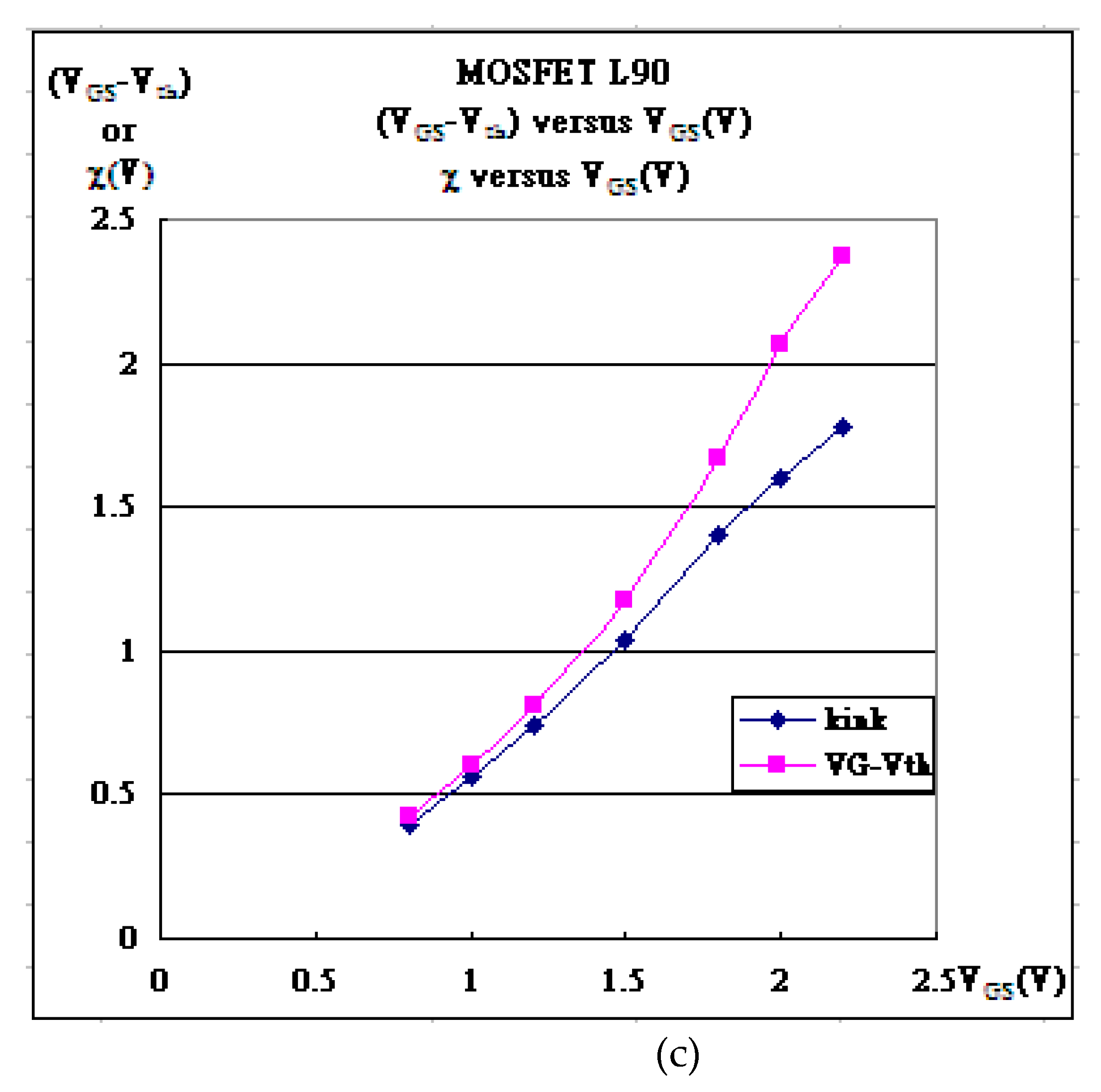

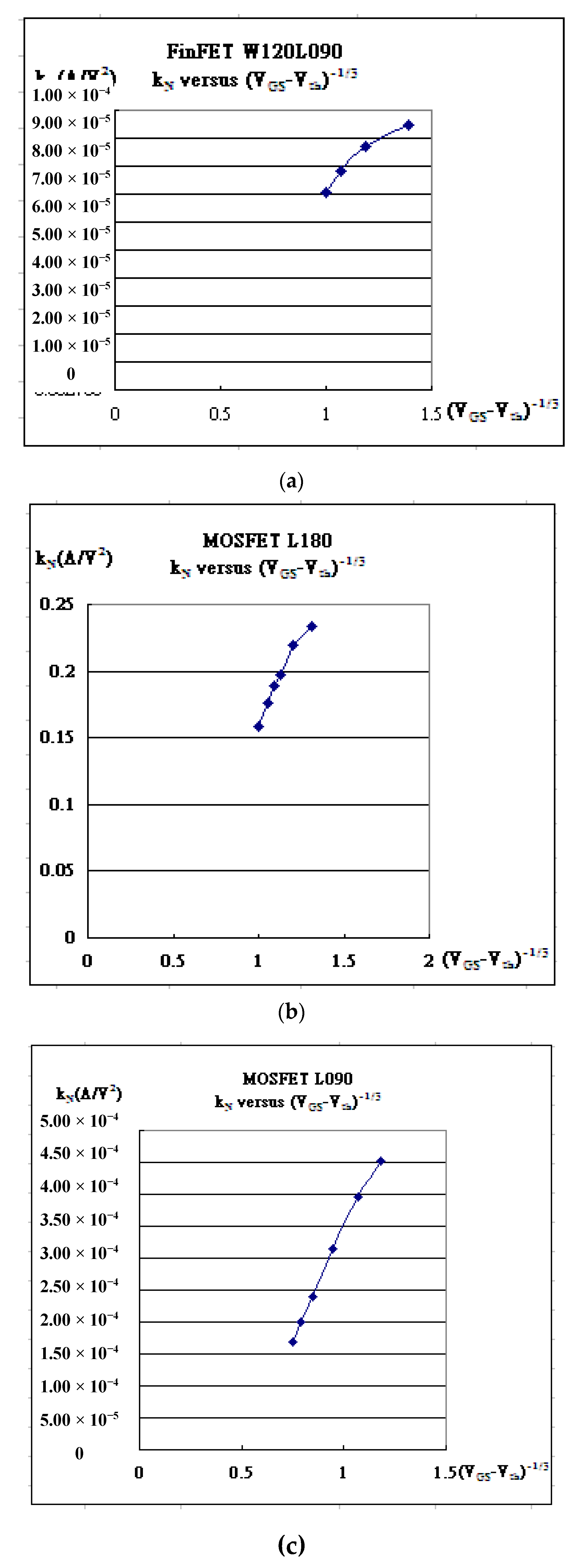

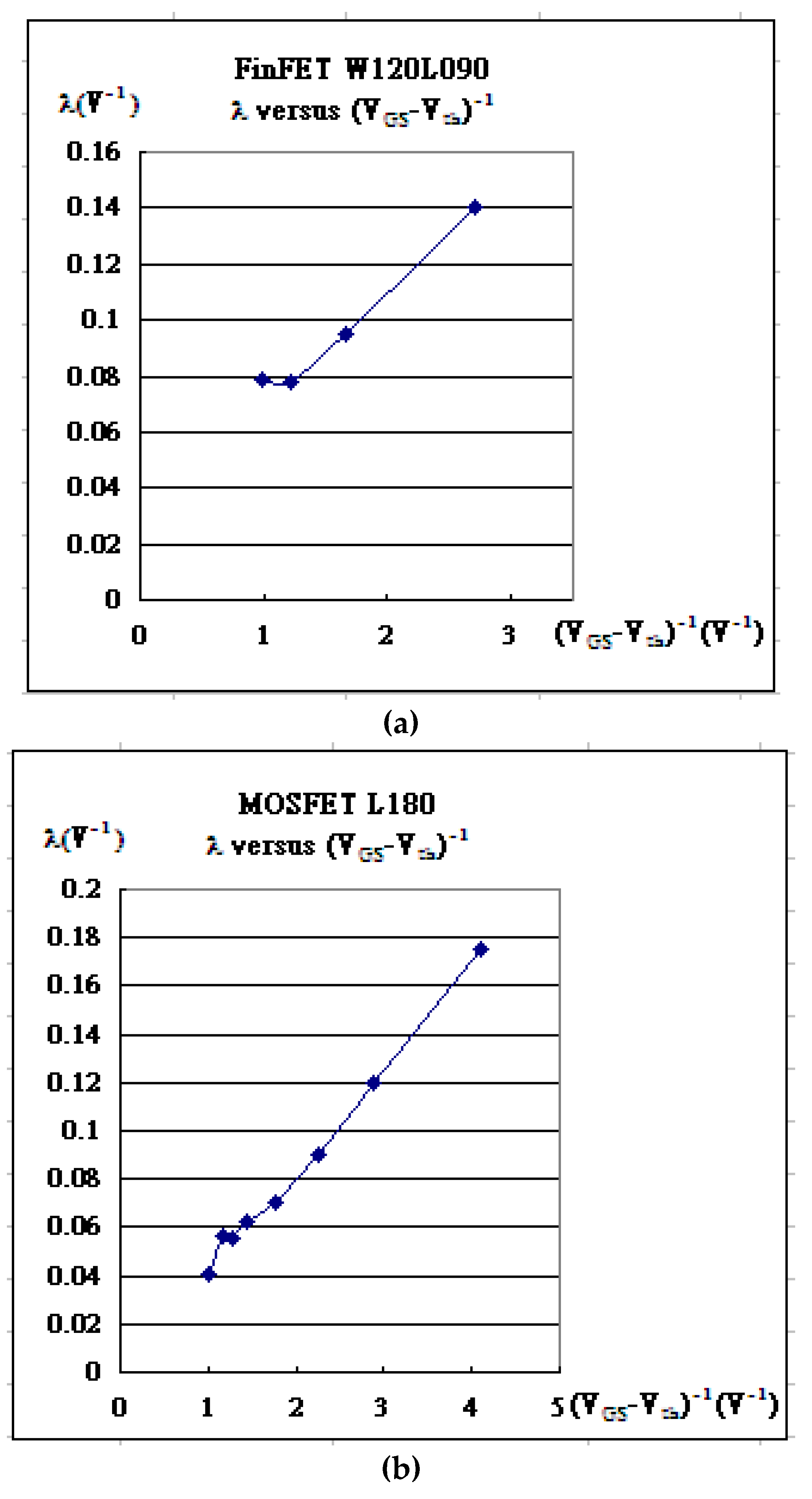

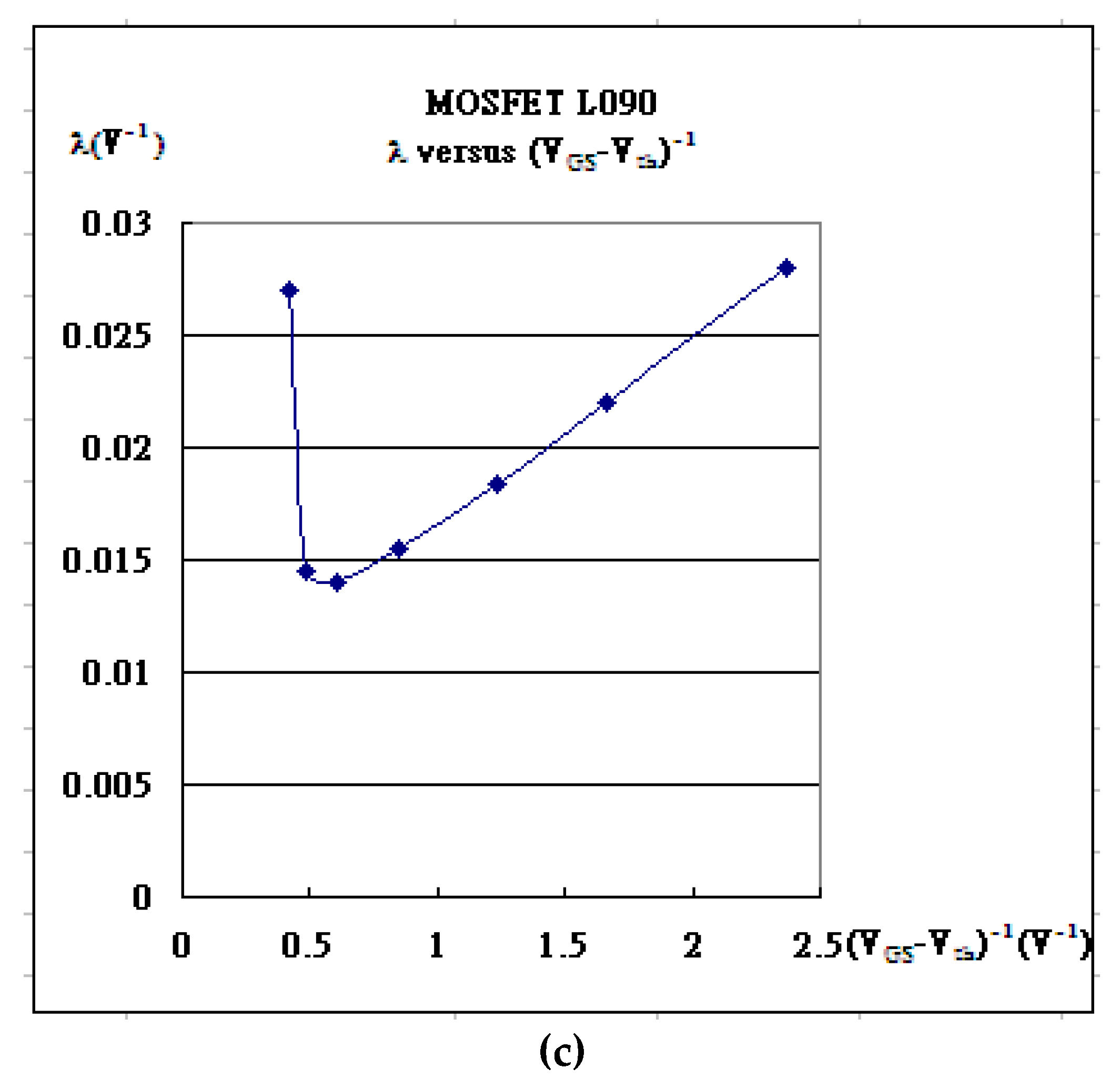

| Gate Bias | kN | Vth | λ | Kink (χ) | α |

|---|---|---|---|---|---|

| VGS = 0.25V | 9.50×10-5 | -0.1197 | 0.140 | 0.33 | 5.95×10-7 |

| VGS = 0.50V | 8.73×10-5 | -0.0981 | 0.095 | 0.44 | 8.9×10-7 |

| VGS = 0.75V | 7.78×10-5 | -0.065 | 0.078 | 0.56 | 1.09×10-6 |

| VGS = 1.00V | 7.07×10-5 | -0.007 | 0.079 | 0.68 | 1.22×10-6 |

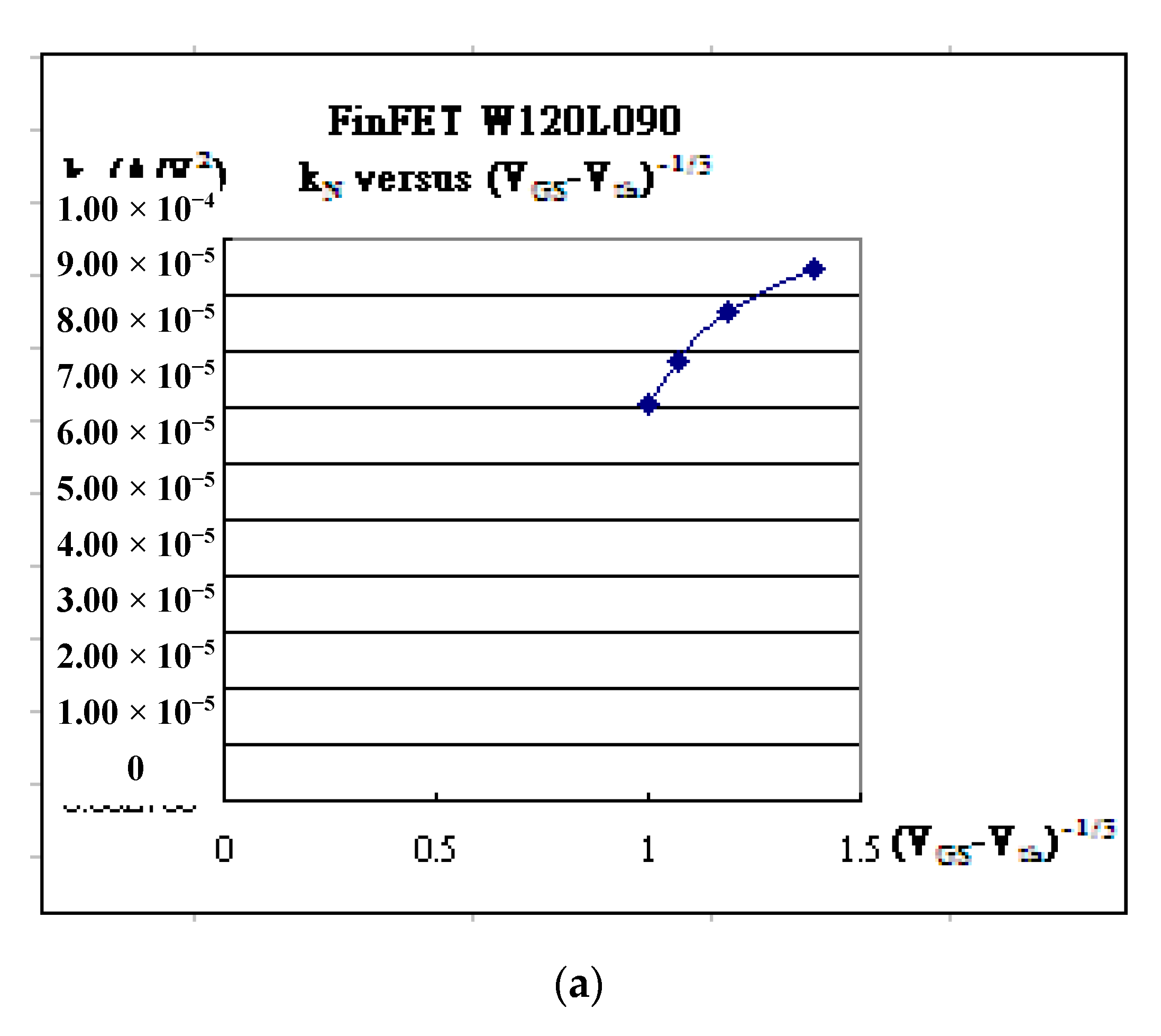

| Gate Bias | kN | Vth | λ | Kink (χ) | α |

|---|---|---|---|---|---|

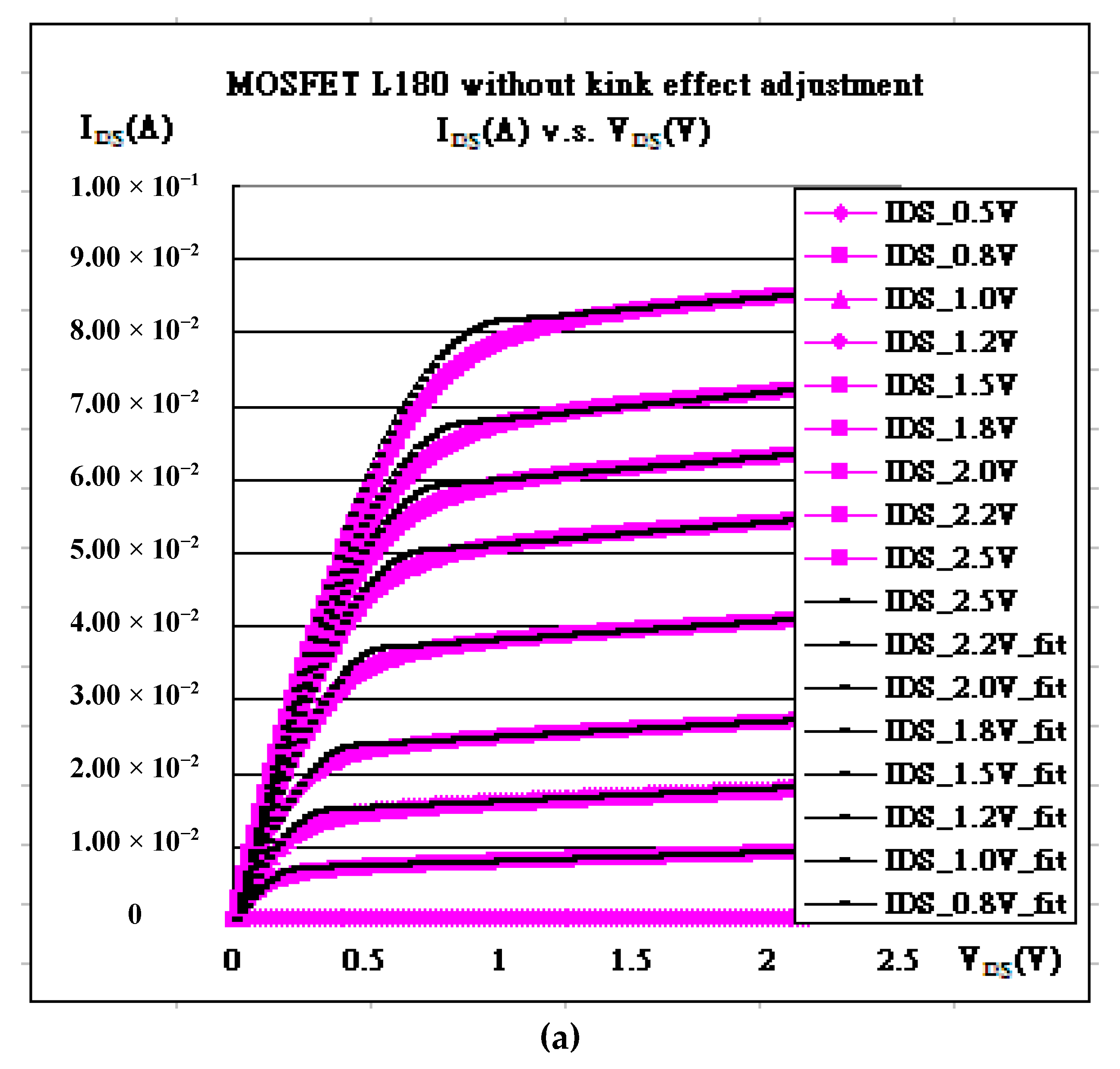

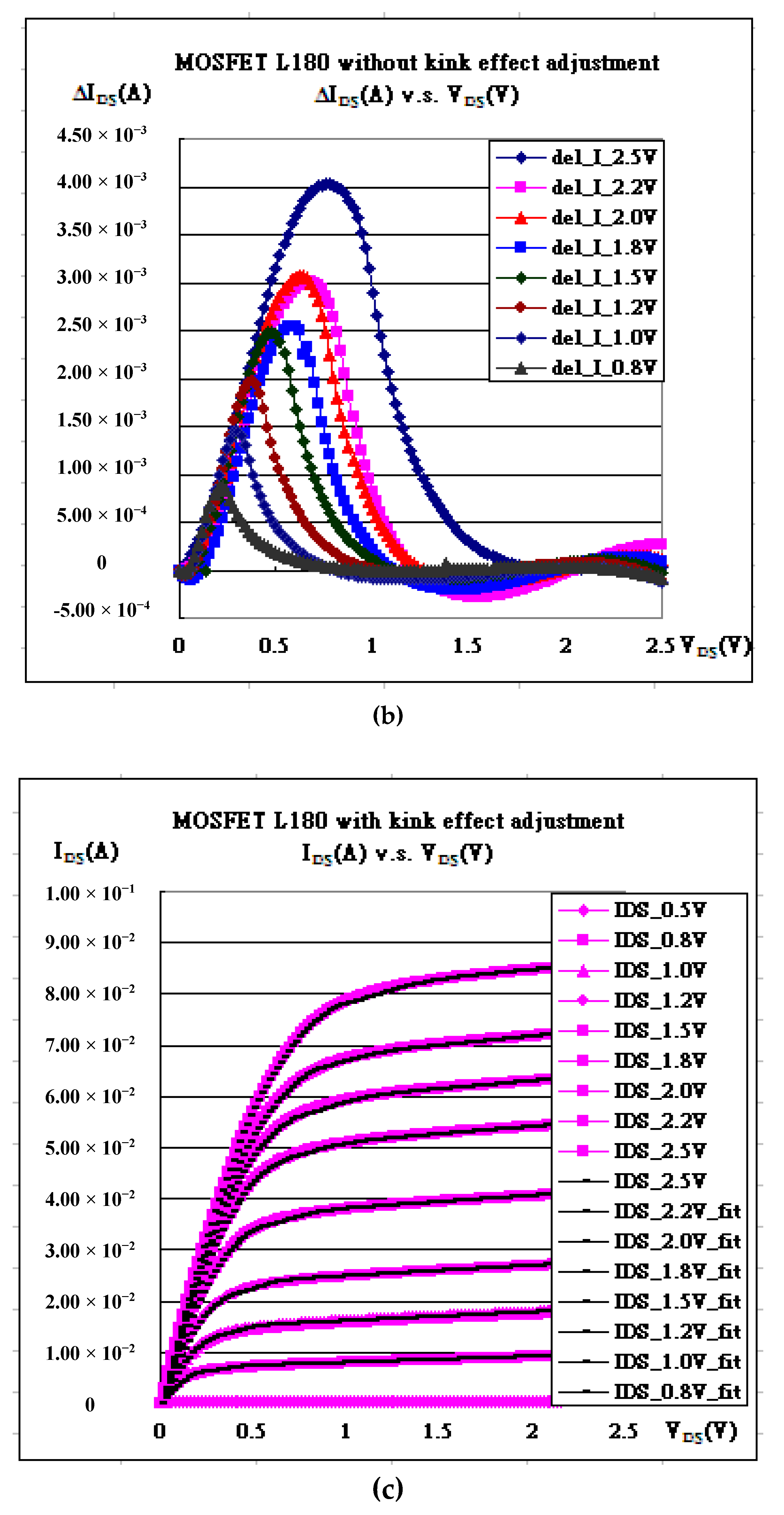

| VGS = 0.80V | 0.228 | 0.556 | 0.17 | 0.22 | 7.7781×10-4 |

| VGS = 1.00V | 0.24 | 0.654 | 0.12 | 0.3 | 1.4426×10-3 |

| VGS = 1.20V | 0.234 | 0.7585 | 0.09 | 0.38 | 1.9528×10-3 |

| VGS =1.50V | 0.22 | 0.931 | 0.07 | 0.48 | 2.4542×10-3 |

| VGS = 1.80 V | 0.197 | 1.101 | 0.062 | 0.6 | 2.5051×10-3 |

| VGS = 2.00V | 0.189 | 1.225 | 0.055 | 0.64 | 3.1098×10-3 |

| VGS = 2.20V | 0.1765 | 1.345 | 0.056 | 0.7 | 3.006×10-3 |

| VGS = 2.50 V | 0.155 | 1.505 | 0.051 | 0.8 | 4.016×10-3 |

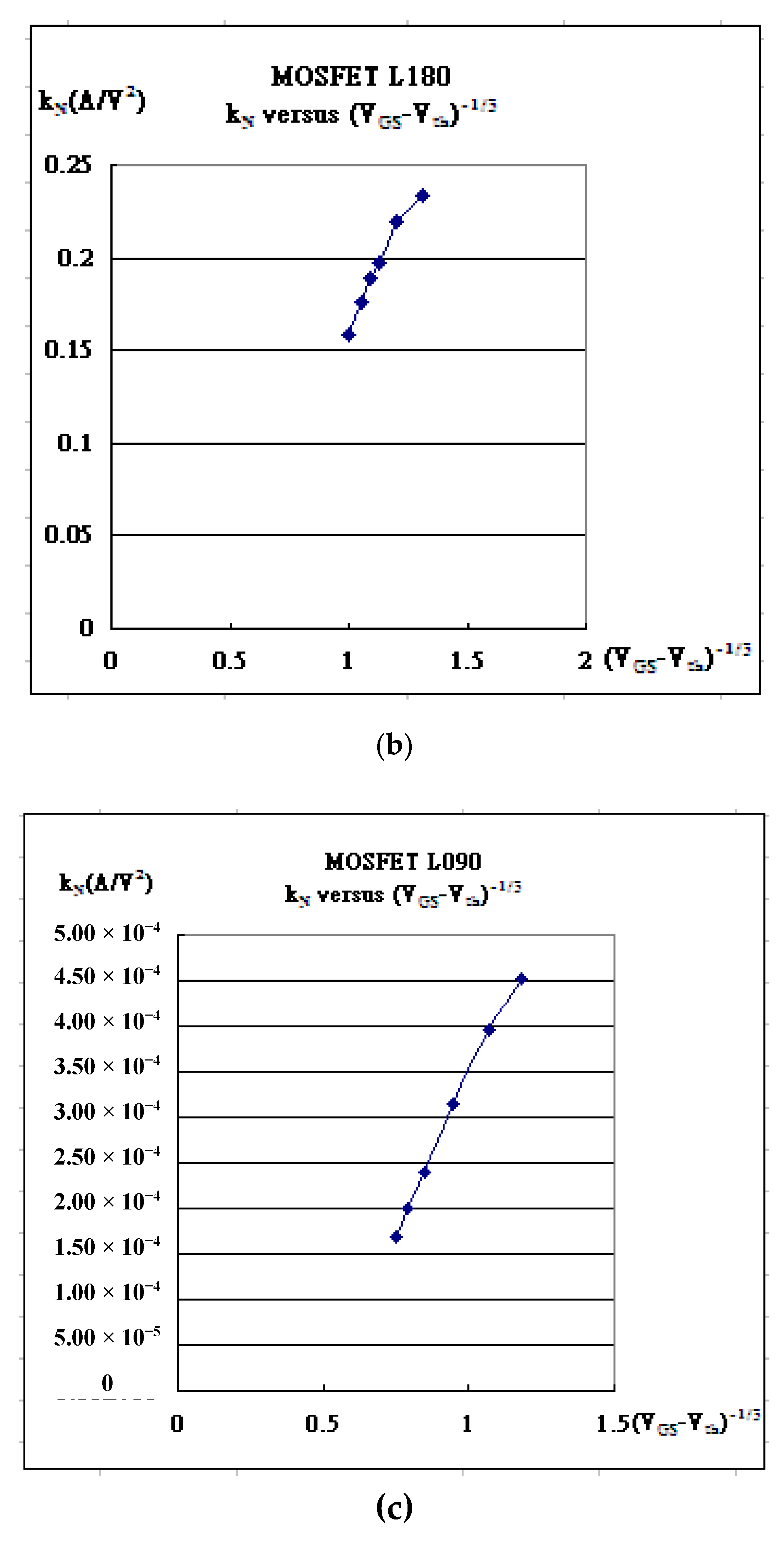

| Gate Bias | kN | Vth | λ | Kink (χ) | I_Kink (α) |

|---|---|---|---|---|---|

| VGS = 0.80V | 5.000×10-4 | 0.3772 | 0.028 | 0.40 | 2.3966×10-6 |

| VGS = 1.00V | 4.530×10-4 | 0.398 | 0.022 | 0.56 | 3.2207×10-6 |

| VGS = 1.20V | 3.950×10-4 | 0.3905 | 0.0184 | 0.74 | 3.8950×10-6 |

| VGS =1.50V | 3.150×10-4 | 0.3215 | 0.0155 | 1.04 | 5.1265×10-6 |

| VGS = 1.80 V | 2.400×10-4 | 0.1345 | 0.014 | 1.4 | 6.5264×10-6 |

| VGS = 2.00V | 2.000×10-4 | -0.063 | 0.0145 | 1.6 | 8.7565×10-6 |

| VGS = 2.20V | 1.680×10-4 | -0.17 | 0.027 | 1.78 | 1.1965×10-5 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).