Submitted:

18 April 2024

Posted:

22 April 2024

You are already at the latest version

Abstract

Keywords:

1. Introduction

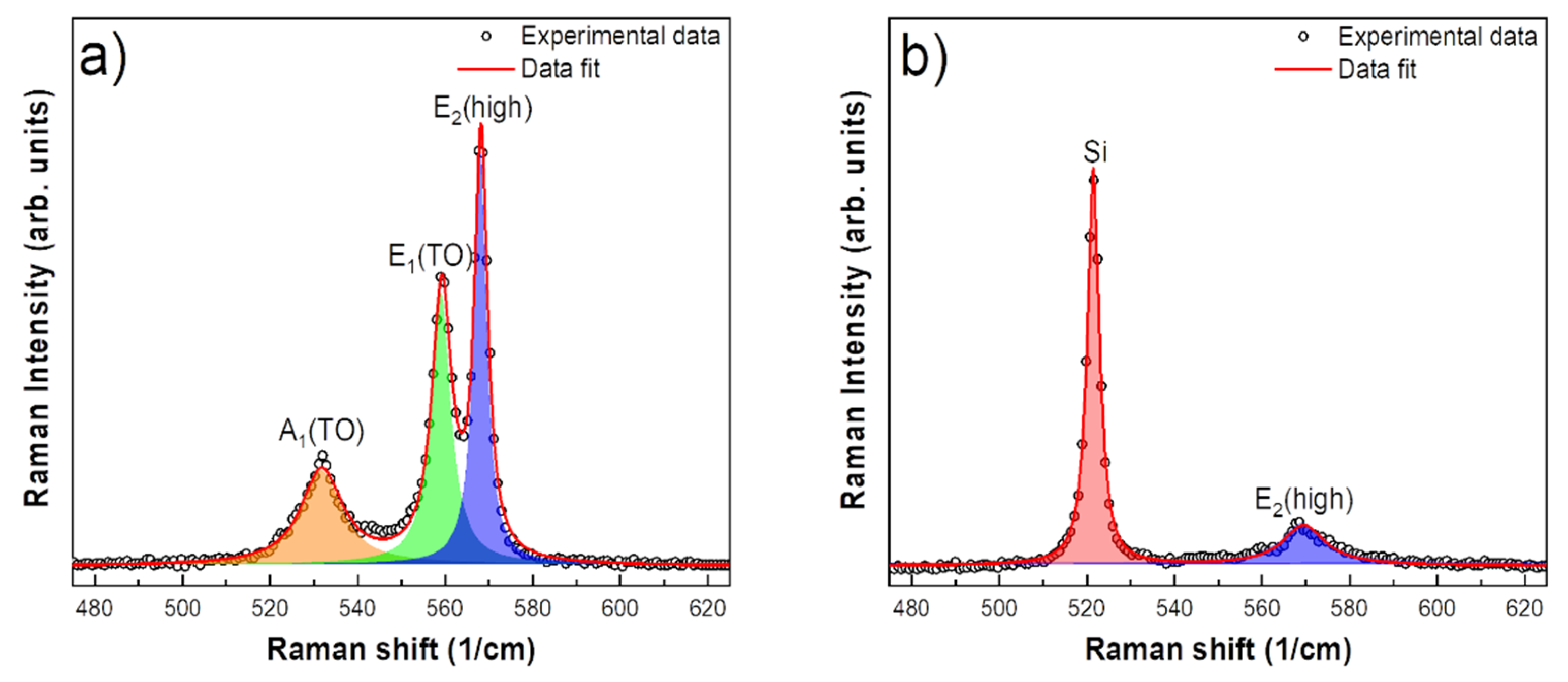

2. Materials and Methods

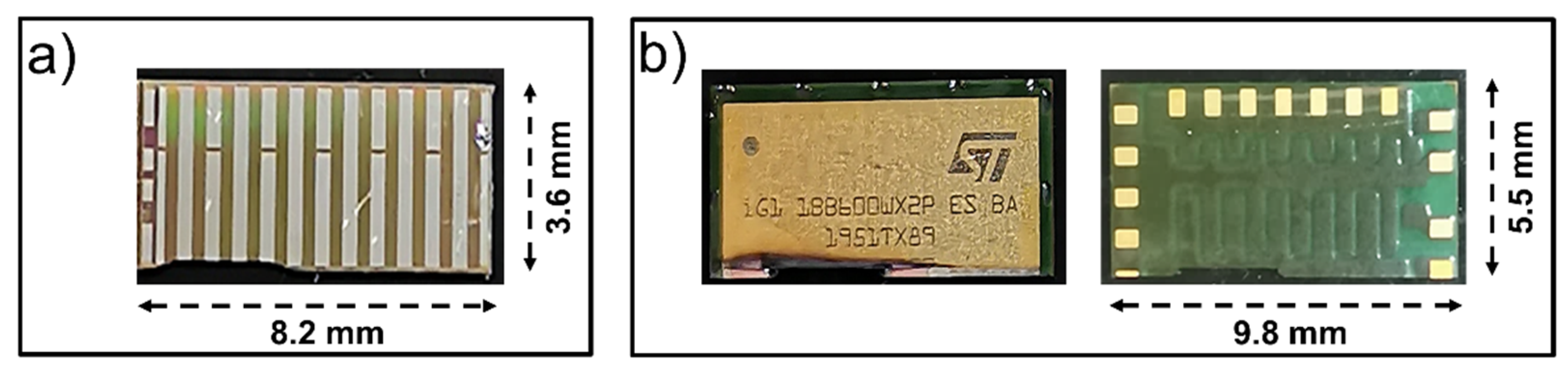

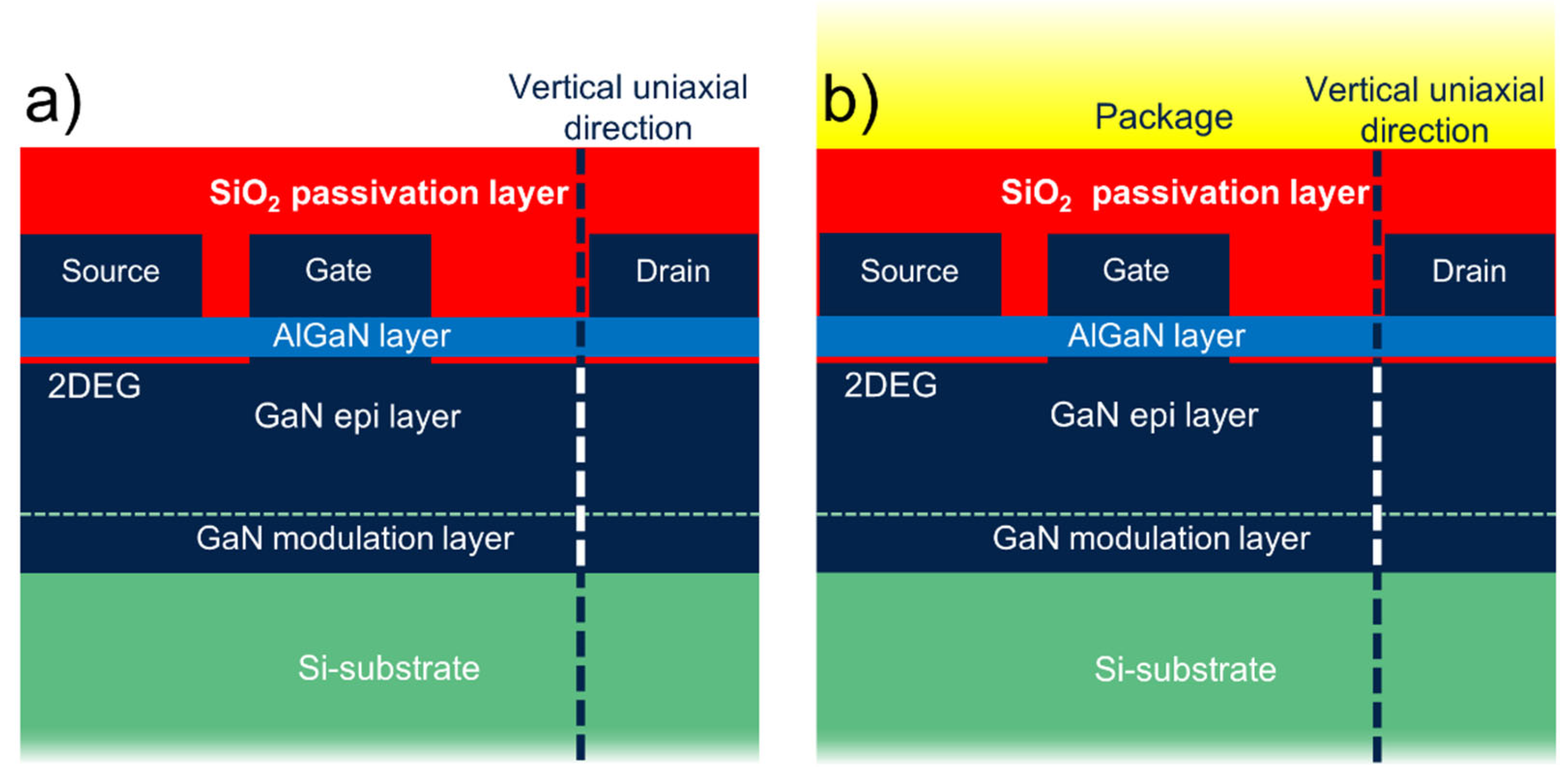

2.1. Material

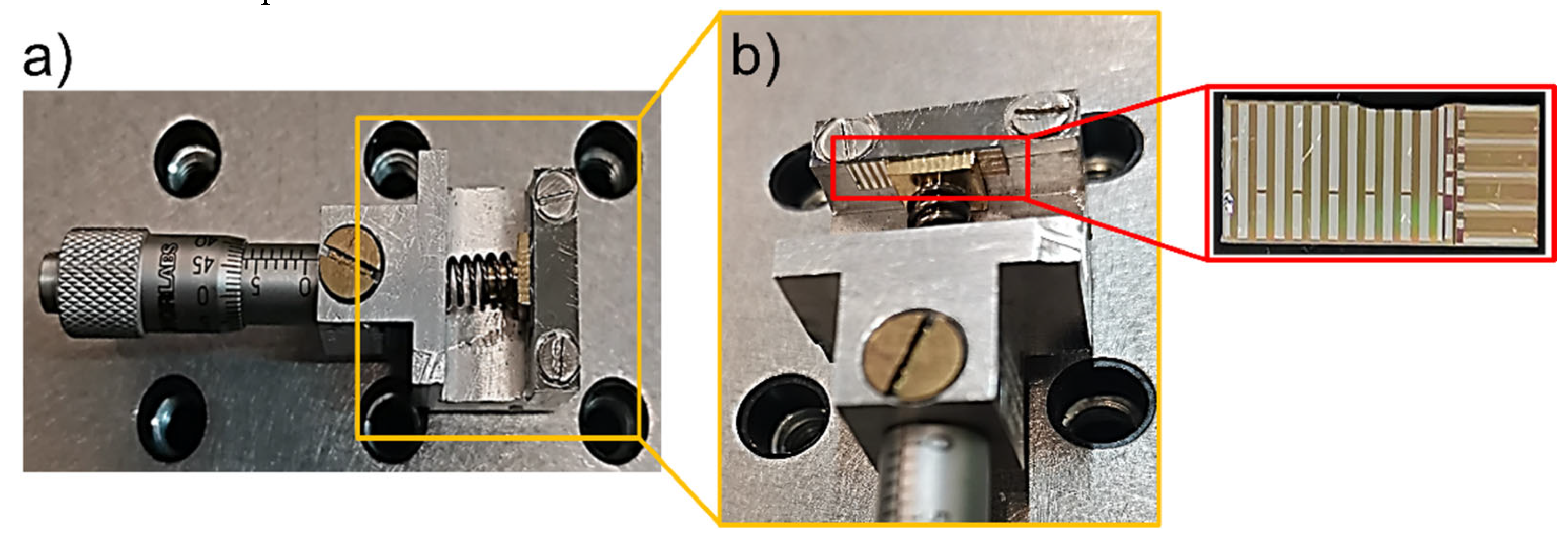

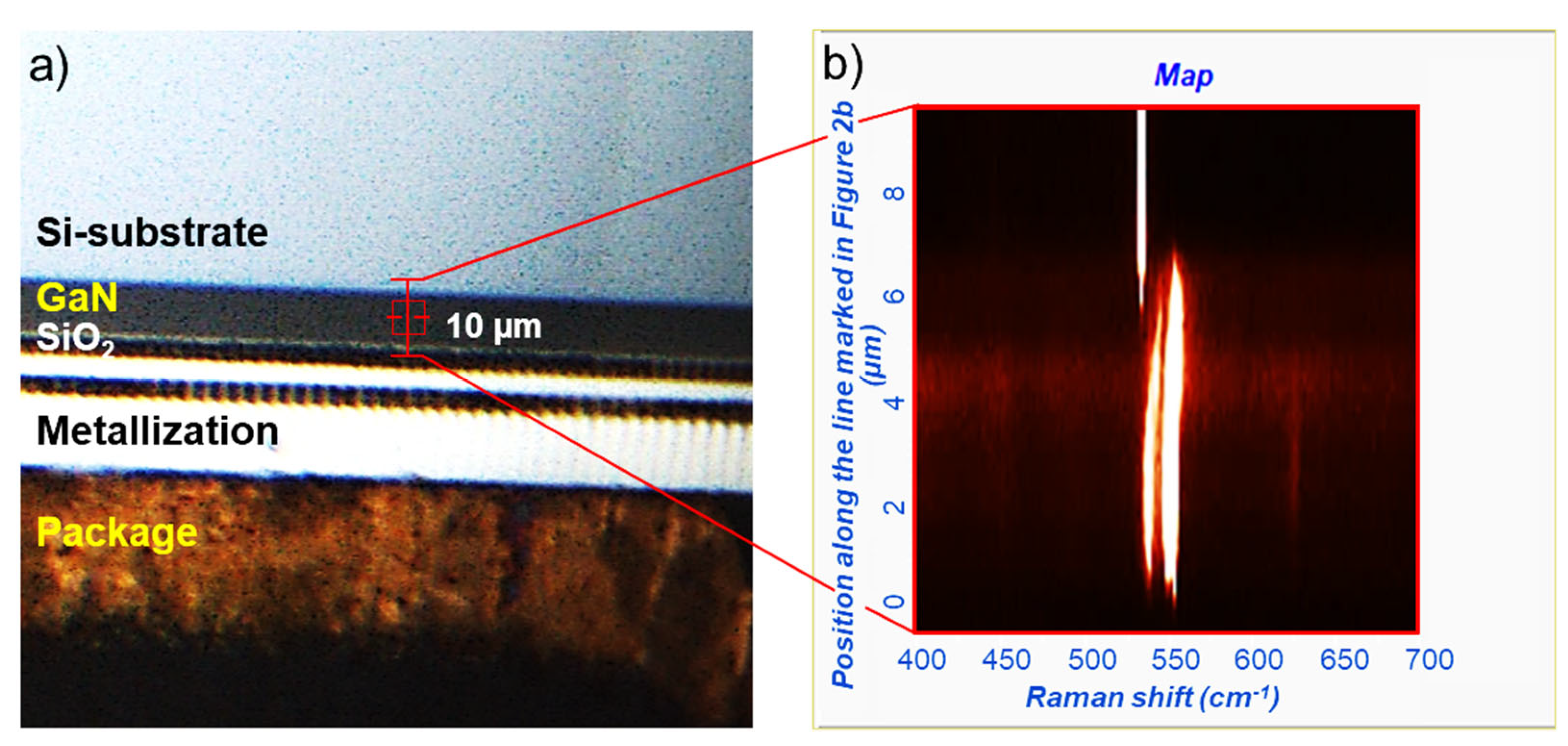

2.2. Method

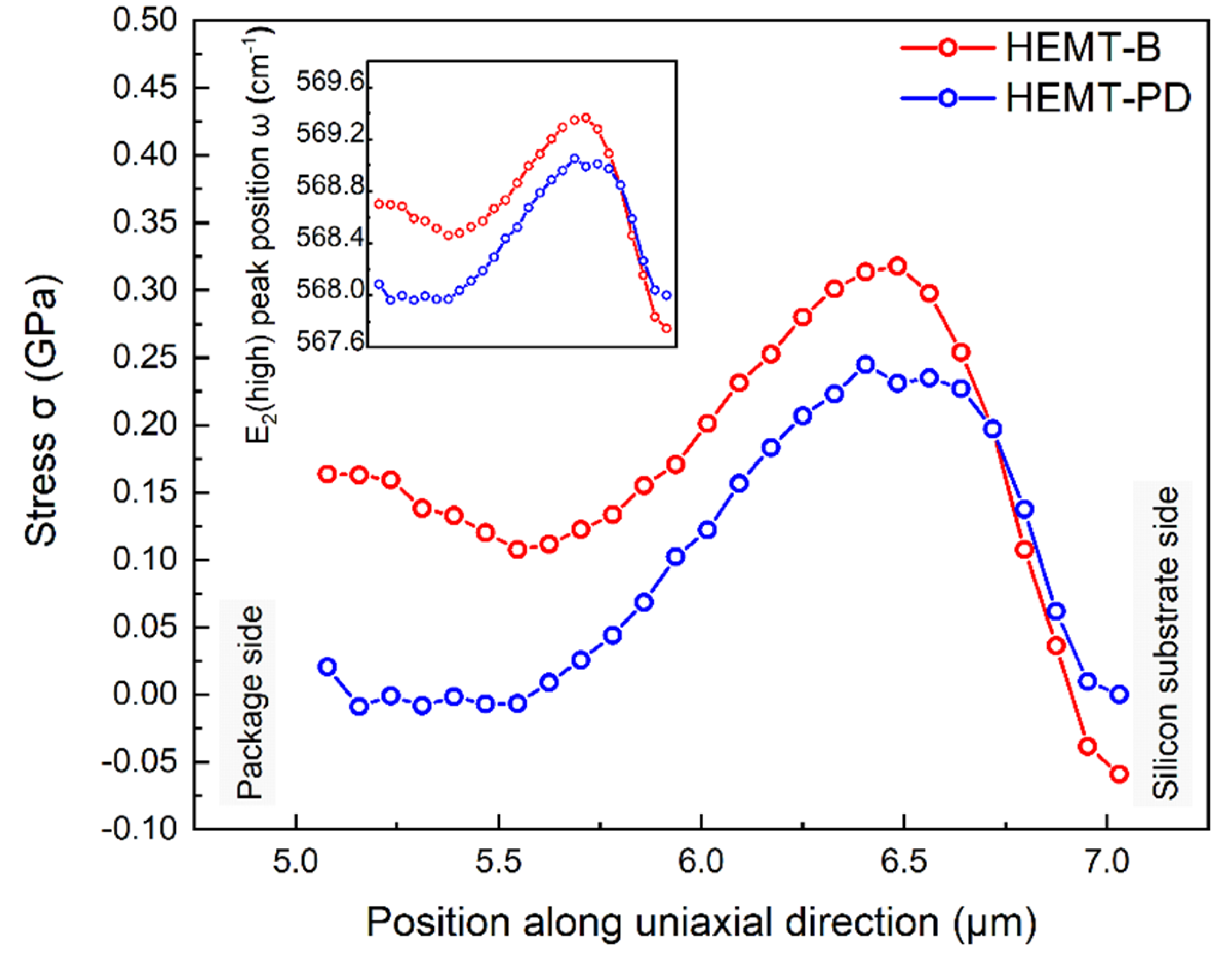

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Zhao, D.G.; Xu, S.J.; Xie, M.H.; Tong, S.Y.; Yang, H. Stress and Its Effect on Optical Properties of GaN Epilayers Grown on Si(111), 6H-SiC(0001), and c -Plane Sapphire. Appl Phys Lett 2003, 83, 677–679. [Google Scholar] [CrossRef]

- Ishida, T. GaN HEMT Technologies for Space and Radio Applications. Microw J (Int Ed) 2011, 54, 56–66. [Google Scholar]

- Trew, R.J.; Bilbro, G.L.; Kuang, W.; Liu, Y.; Yin, H. Microwave AlGaN/GaN HFETs. IEEE Microw Mag 2005, 6, 56–66. [Google Scholar] [CrossRef]

- Mishra, U.K.; Parikh, P. ; Yi-Feng Wu AlGaN/GaN HEMTs-an Overview of Device Operation and Applications. Proceedings of the IEEE 2002, 90, 1022–1031. [Google Scholar] [CrossRef]

- Islam, N.; Mohamed, M.F.P.; Khan, M.F.A.J.; Falina, S.; Kawarada, H.; Syamsul, M. Reliability, Applications and Challenges of GaN HEMT Technology for Modern Power Devices: A Review. Crystals (Basel) 2022, 12, 1581. [Google Scholar] [CrossRef]

- Cho, J.; Li, Z.; Asheghi, M.; Goodson, K.E. NEAR-JUNCTION THERMAL MANAGEMENT: THERMAL CONDUCTION IN GALLIUM NITRIDE COMPOSITE SUBSTRATES. Annual Review of Heat Transfer 2015, 18, 7–45. [Google Scholar] [CrossRef]

- Liu, L.; Edgar, J.H. Substrates for Gallium Nitride Epitaxy. Materials Science and Engineering: R: Reports 2002, 37, 61–127. [Google Scholar] [CrossRef]

- Schuster, M.; Wachowiak, A.; Szabo, N.; Jahn, A.; Merkel, U.; Ruf, A.; Mikolajick, T.; Murad, S.; Hu, C.; Groh, L.; et al. HEMT Test Structure Technology for Fast On-Wafer Characterization of Epitaxial GaN-on-Si Material. In Proceedings of the 2013 International Semiconductor Conference Dresden - Grenoble (ISCDG); IEEE, September 2013; pp. 1–3. [Google Scholar]

- Ma, L.; Qiu, W.; Fan, X. Stress/Strain Characterization in Electronic Packaging by Micro-Raman Spectroscopy: A Review. Microelectronics Reliability 2021, 118, 114045. [Google Scholar] [CrossRef]

- Bayerer, R. Advanced Packaging Yields Higher Performance and Reliability in Power Electronics. Microelectronics Reliability 2010, 50, 1715–1719. [Google Scholar] [CrossRef]

- Panarello, S.; Garesci, F.; Triolo, C.; Patane, S.; Patti, D.; Russo, S. Reliability Model Application for Power Devices Using Mechanical Strain Real Time Mapping. In Proceedings of the 2016 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD); IEEE, June 2016; pp. 127–130.

- Kim, Y.; Subramanya, S.G.; Siegle, H.; Krüger, J.; Perlin, P.; Weber, E.R.; Ruvimov, S.; Liliental-Weber, Z. GaN Thin Films by Growth on Ga-Rich GaN Buffer Layers. J Appl Phys 2000, 88, 6032–6036. [Google Scholar] [CrossRef]

- Ahmad, I.; Holtz, M.; Faleev, N.N.; Temkin, H. Dependence of the Stress–Temperature Coefficient on Dislocation Density in Epitaxial GaN Grown on α-Al2O3 and 6H–SiC Substrates. J Appl Phys 2004, 95, 1692–1697. [Google Scholar] [CrossRef]

- Xu, Z.; He, Z.; Song, Y.; Fu, X.; Rommel, M.; Luo, X.; Hartmaier, A.; Zhang, J.; Fang, F. Topic Review: Application of Raman Spectroscopy Characterization in Micro/Nano-Machining. Micromachines (Basel) 2018, 9, 361. [Google Scholar] [CrossRef]

- Choi, S.; Heller, E.; Dorsey, D.; Vetury, R.; Graham, S. Analysis of the Residual Stress Distribution in AlGaN/GaN High Electron Mobility Transistors. J Appl Phys 2013, 113. [Google Scholar] [CrossRef]

- Kamarudzaman, A.; Abu Bakar, A.S. Bin; Azman, A.; Omar, A.-Z.; Supangat, A.; Talik, N.A. Positioning of Periodic AlN/GaN Multilayers: Effect on Crystalline Quality of a-Plane GaN. Mater Sci Semicond Process 2020, 105, 104700. [Google Scholar] [CrossRef]

- Maize, K.; Pavlidis, G.; Heller, E.; Yates, L.; Kendig, D.; Graham, S.; Shakouri, A. High Resolution Thermal Characterization and Simulation of Power AlGaN/GaN HEMTs Using Micro-Raman Thermography and 800 Picosecond Transient Thermoreflectance Imaging. In Proceedings of the 2014 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS); IEEE, October 2014; pp. 1–8.

- Rieger, W.; Metzger, T.; Angerer, H.; Dimitrov, R.; Ambacher, O.; Stutzmann, M. Influence of Substrate-Induced Biaxial Compressive Stress on the Optical Properties of Thin GaN Films. Appl Phys Lett 1996, 68, 970–972. [Google Scholar] [CrossRef]

- Kisielowski, C.; Krüger, J.; Ruvimov, S.; Suski, T.; Ager, J.W.; Jones, E.; Liliental-Weber, Z.; Rubin, M.; Weber, E.R.; Bremser, M.D.; et al. Strain-Related Phenomena in GaN Thin Films. Phys Rev B 1996, 54, 17745–17753. [Google Scholar] [CrossRef]

- Greco, G.; Iucolano, F.; Roccaforte, F. Review of Technology for Normally-off HEMTs with p-GaN Gate. Mater Sci Semicond Process 2018, 78, 96–106. [Google Scholar] [CrossRef]

- Beechem, T.; Christensen, A.; Green, D.S.; Graham, S. Assessment of Stress Contributions in GaN High Electron Mobility Transistors of Differing Substrates Using Raman Spectroscopy. J Appl Phys 2009, 106. [Google Scholar] [CrossRef]

- Choi, S.; Heller, E.R.; Dorsey, D.; Vetury, R.; Graham, S. Thermometry of AlGaN/GaN HEMTs Using Multispectral Raman Features. IEEE Trans Electron Devices 2013, 60, 1898–1904. [Google Scholar] [CrossRef]

- Beechem, T.E.I. METROLOGY OF GaN ELECTRONICS USING MICRO‐RAMAN SPECTROSCOPY; 2008.

- Sugie, R.; Uchida, T. Determination of Stress Components in 4H-SiC Power Devices via Raman Spectroscopy. J Appl Phys 2017, 122. [Google Scholar] [CrossRef]

- Tripathy, S.; Chua, S.J.; Chen, P.; Miao, Z.L. Micro-Raman Investigation of Strain in GaN and AlxGa1−xN/GaN Heterostructures Grown on Si(111). J Appl Phys 2002, 92, 3503–3510. [Google Scholar] [CrossRef]

- Harima, H. Properties of GaN and Related Compounds Studied by Means of Raman Scattering. Journal of Physics: Condensed Matter 2002, 14, R967–R993. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).