Submitted:

24 January 2024

Posted:

24 January 2024

You are already at the latest version

Abstract

Keywords:

1. Introduction

2. Related Work

3. Background

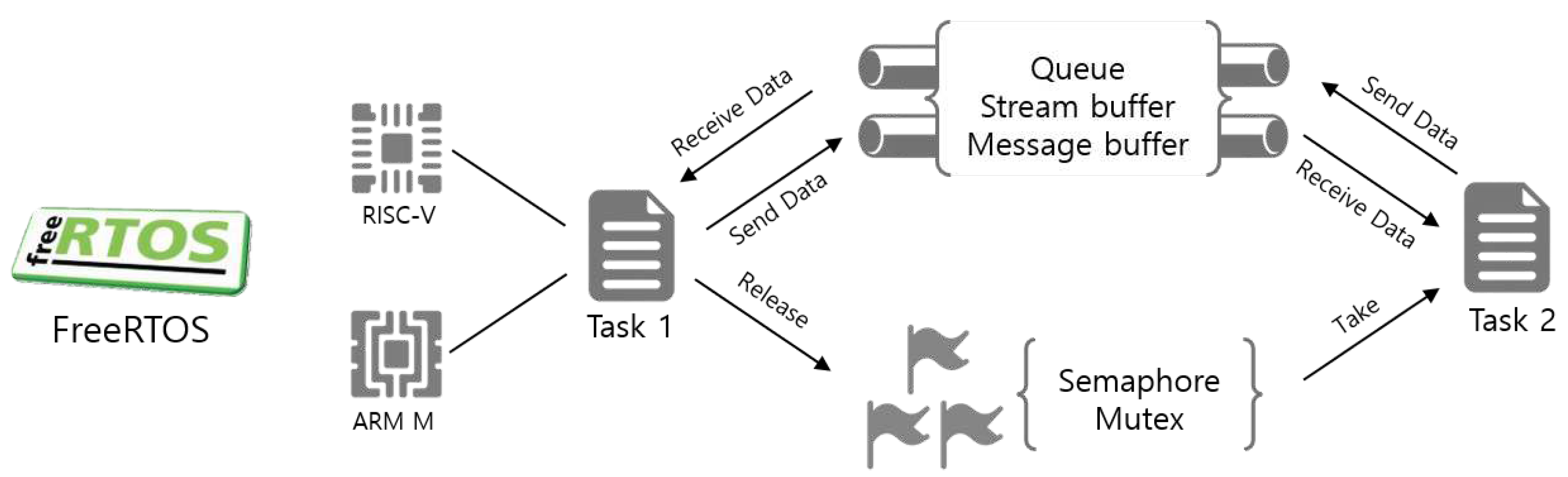

3.1. FreeRTOS

3.2. Preempt-RT

3.3. Inter-task communication

- Queue: This mechanism is for message transfers between tasks, operating on a first-in, first-out (FIFO) basis. Users can define the message size and the queue’s capacity. In many types of RTOS, if a task attempts to retrieve a message from an empty queue, it will wait until another task places a message in the queue.

- Semaphore: Semaphores are used to manage access to task resources. Operating systems typically categorize them into binary semaphores, with a count limit of one, and counting semaphores, with a higher count limit. Unlike mutexes, semaphores do not prioritize tasks, making them suitable for synchronizing operations between tasks.

- Mutex: A mutex, short for mutual exclusion, limits access to a resource to one task at a time, ensuring that the task holding the mutex can operate without interference from others. While similar to a binary semaphore in restricting access to a single resource, a mutex is unique in that it is assigned to the task with the highest priority.

4. Real-time Performance measurement on FreeRTOS

4.1. Inter Task Communication of FreeRTOS

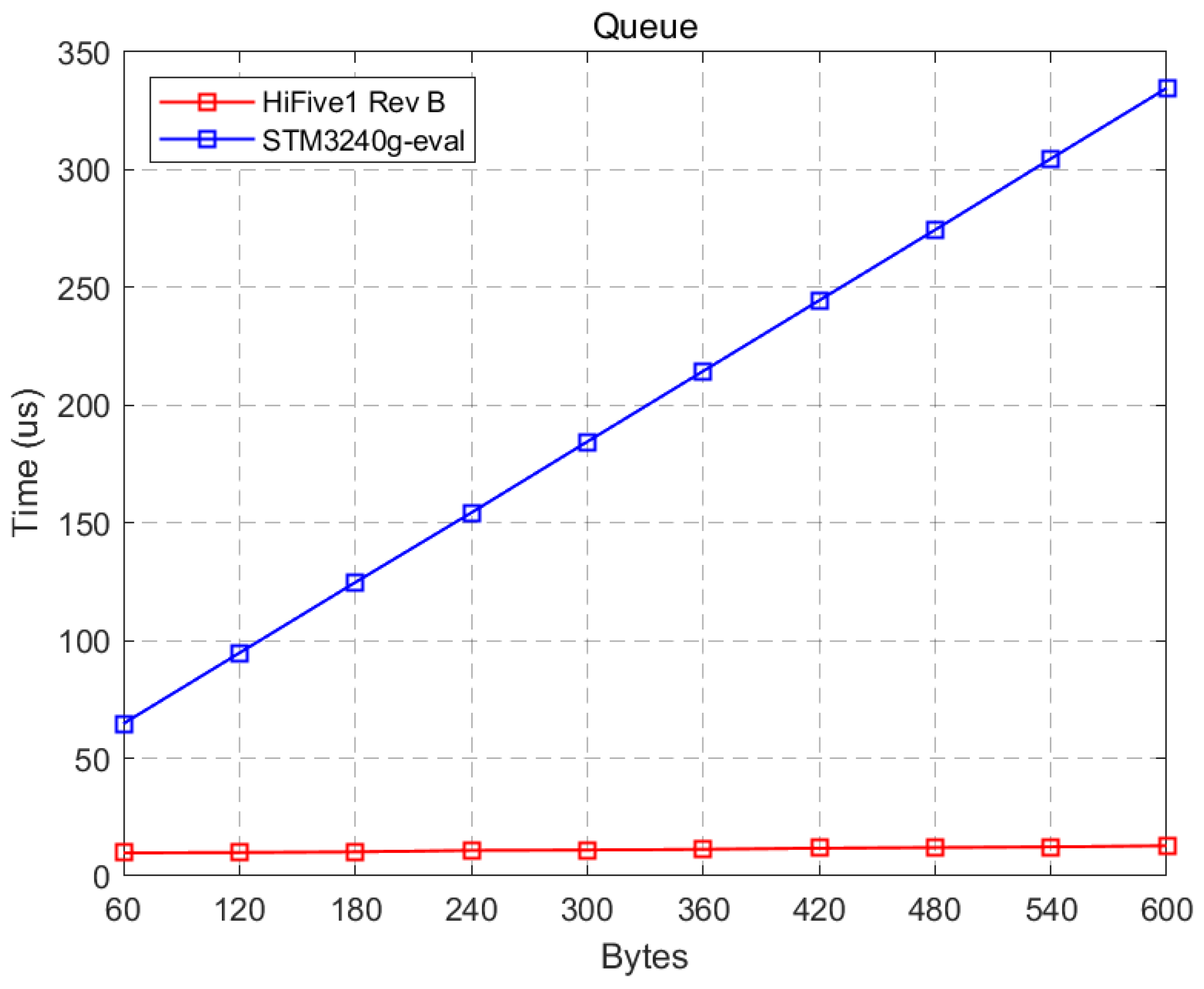

4.1.1. Queue

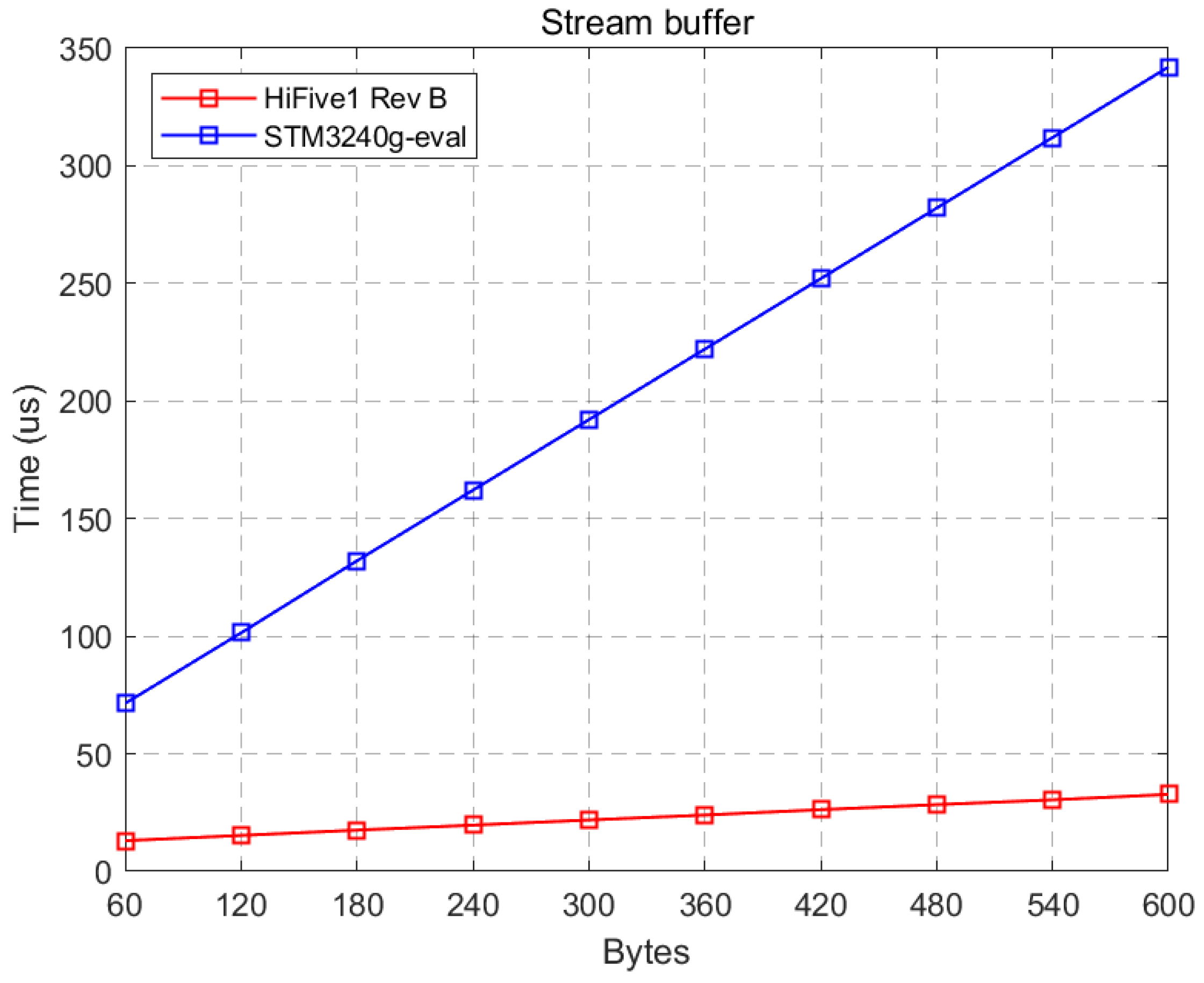

4.1.2. Stream Buffer

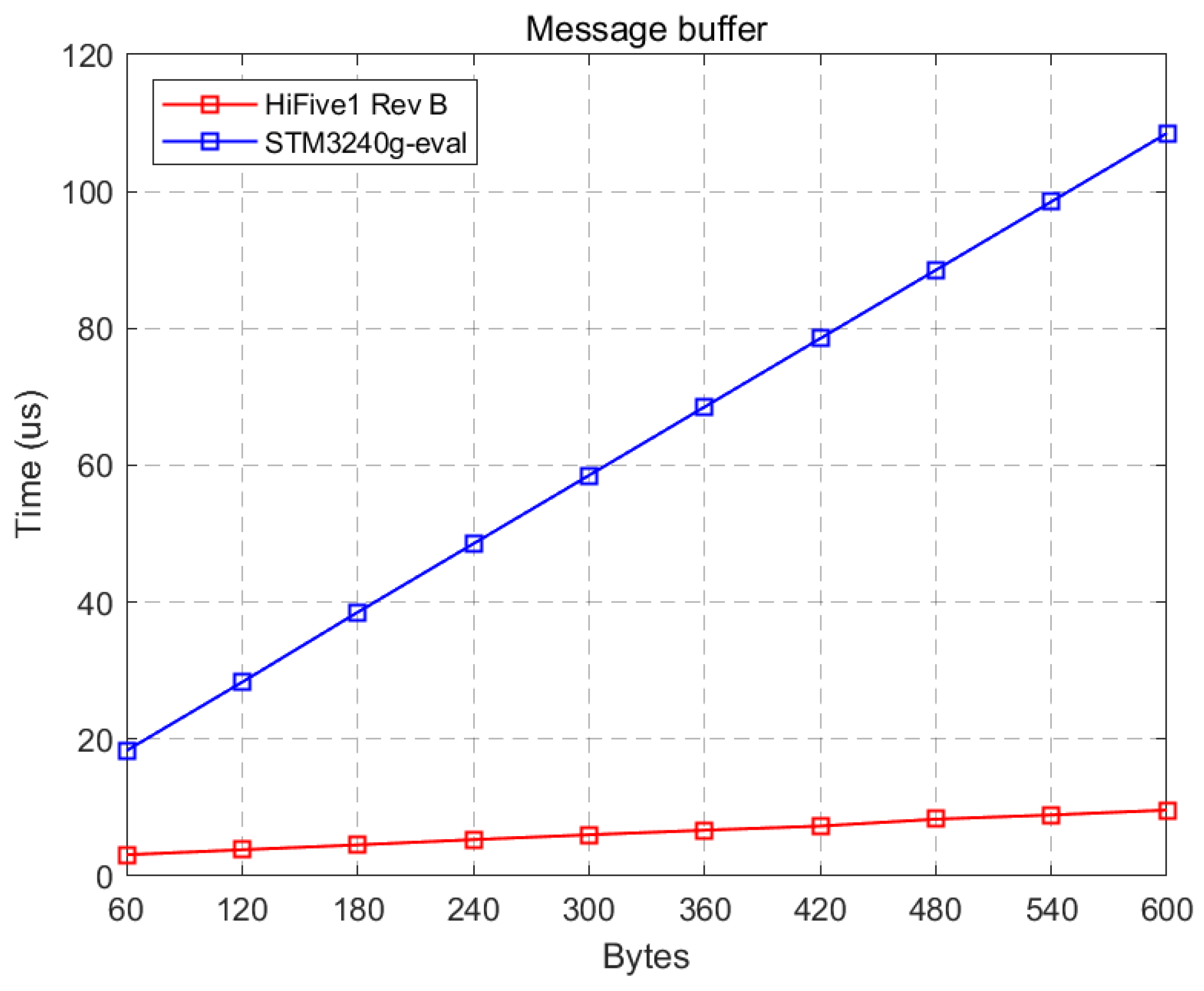

4.1.3. Message Buffer

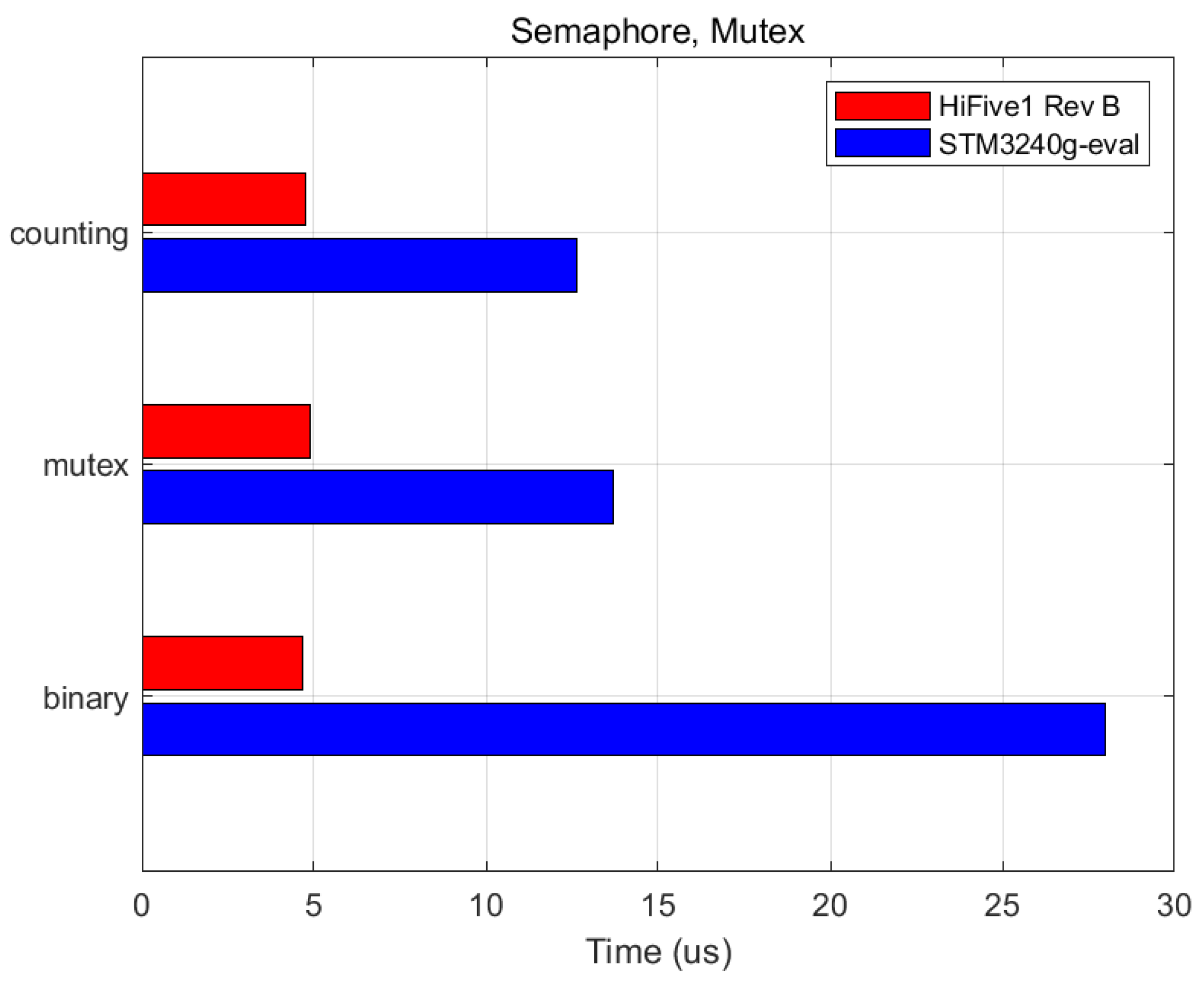

4.1.4. Semaphore and Mutex

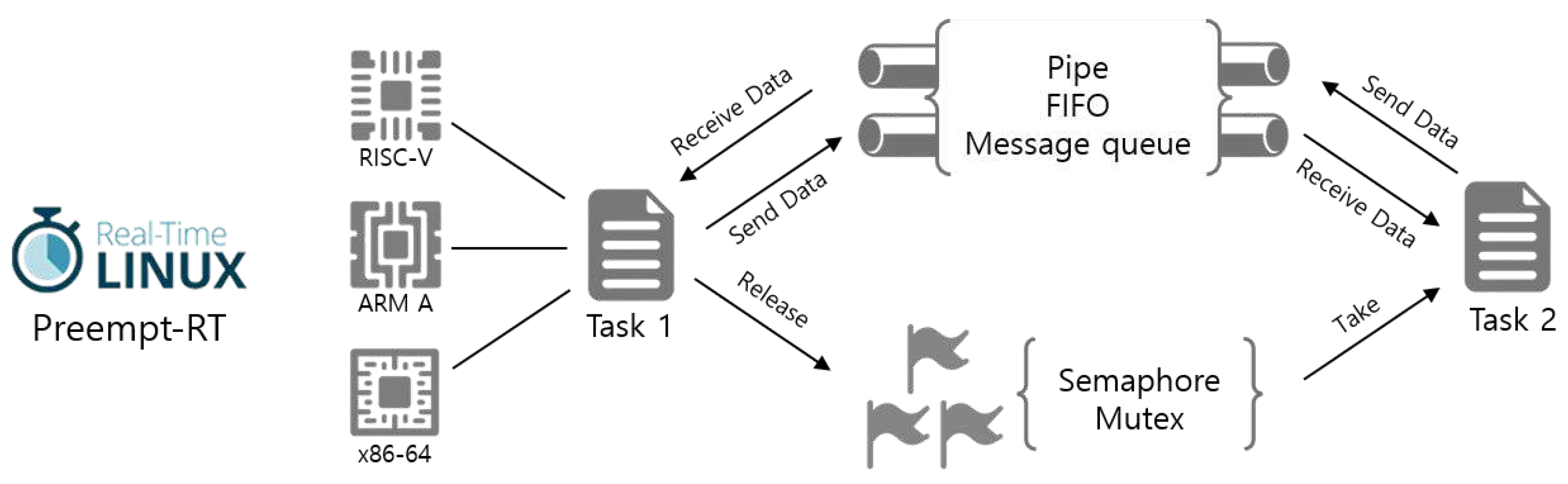

5. Real-time Performance measurement on Preempt-RT

5.1. Inter Task Communication of Preempt-RT

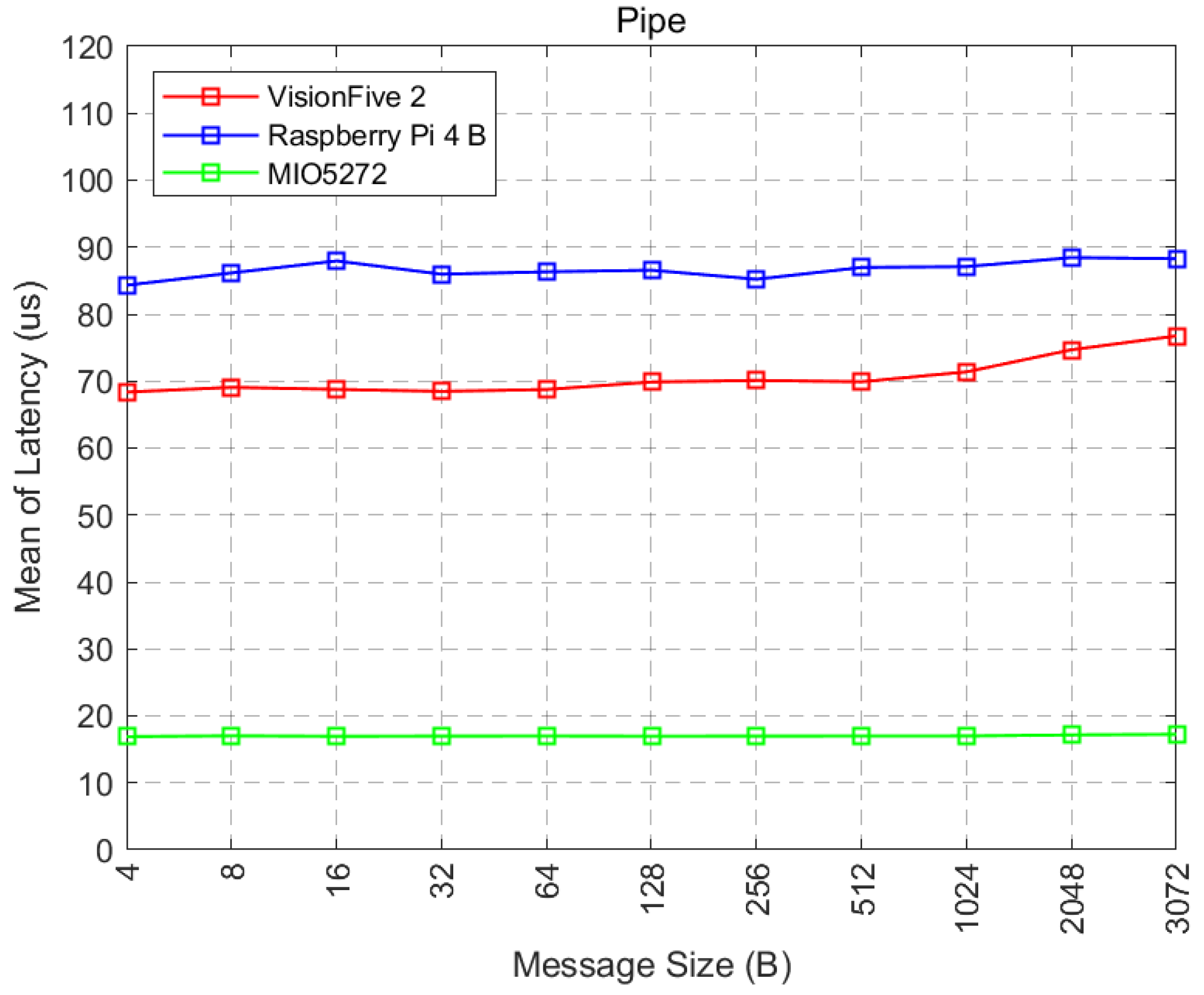

5.1.1. Pipe

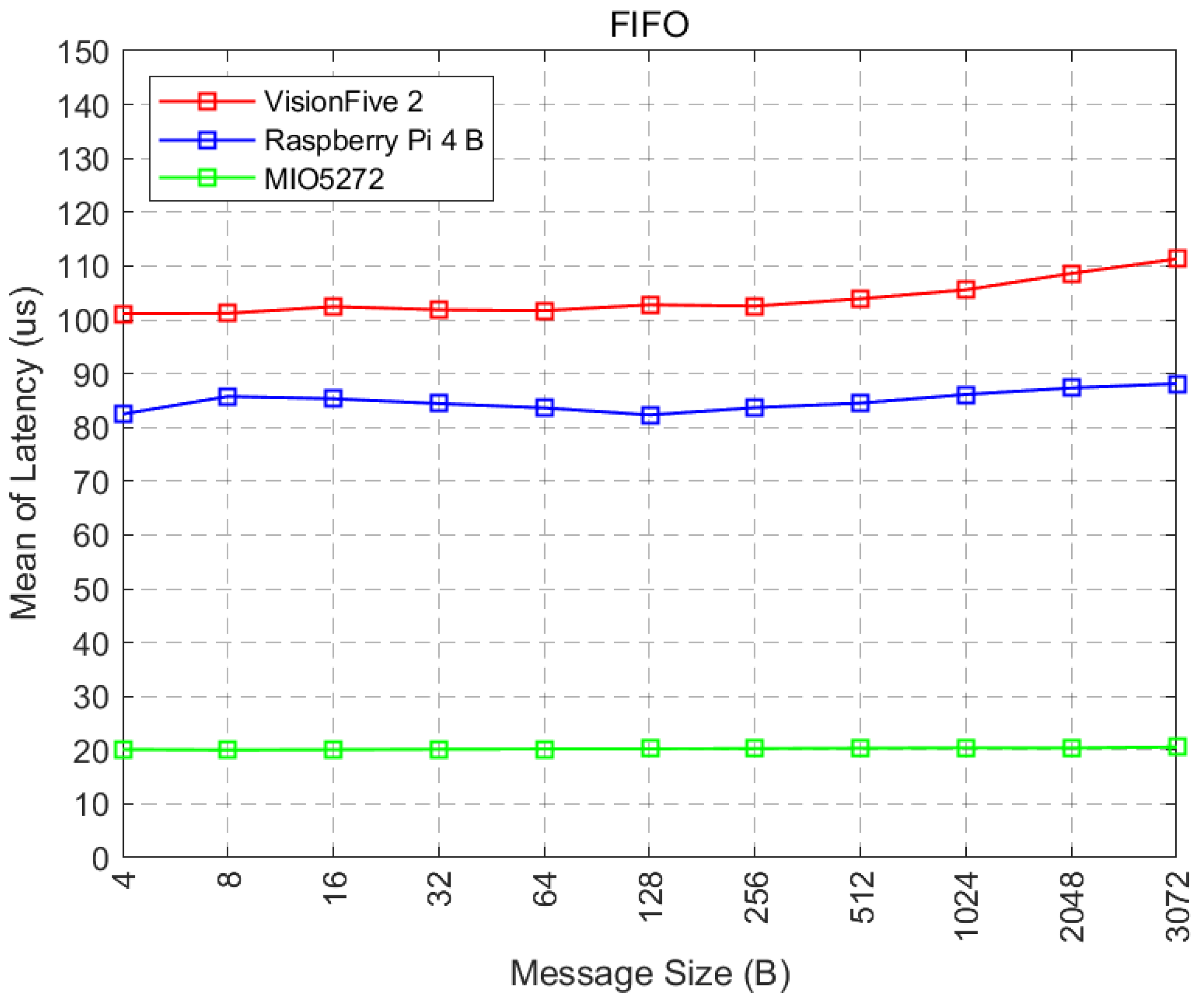

5.1.2. FIFO

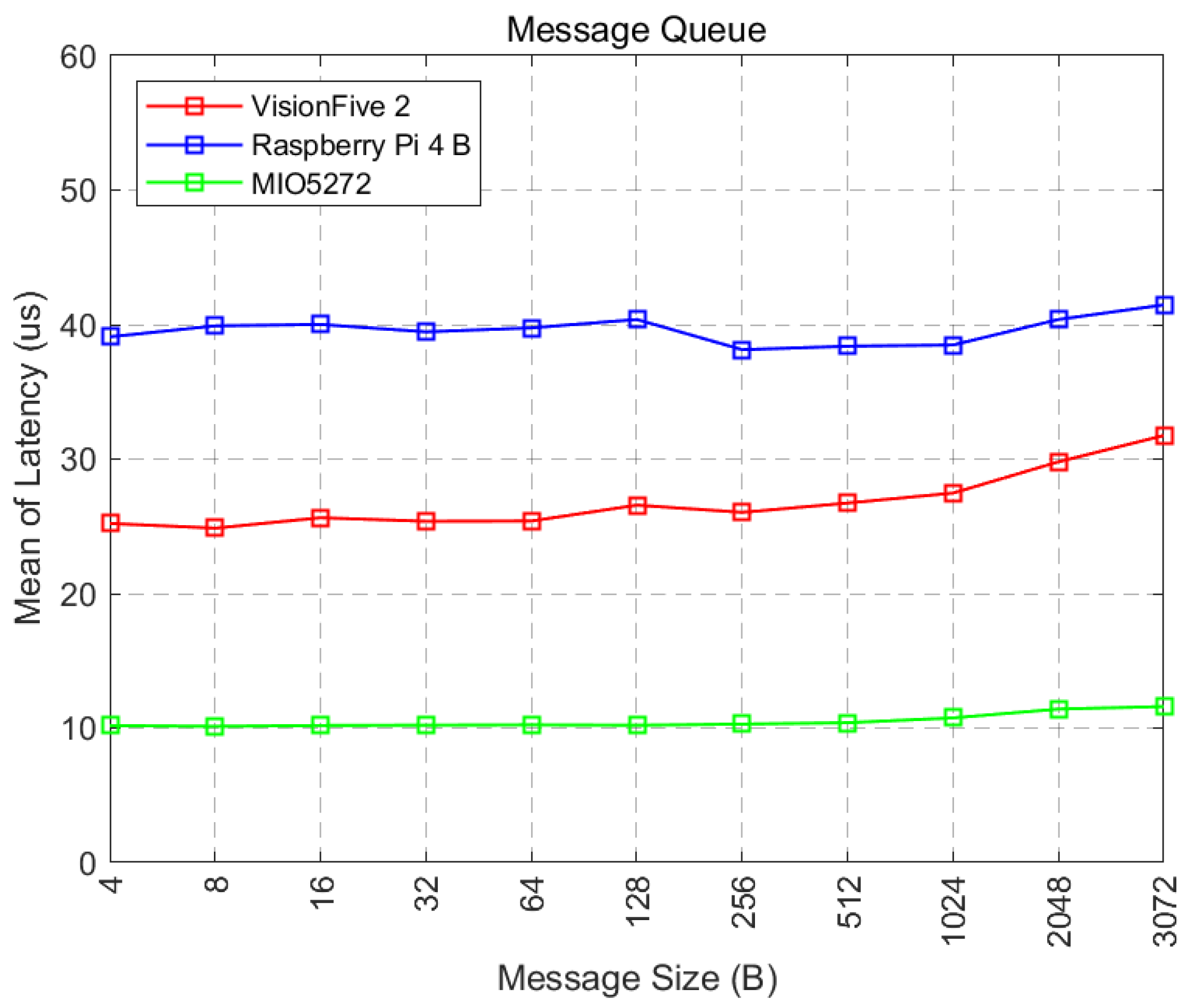

5.1.3. Message Queue

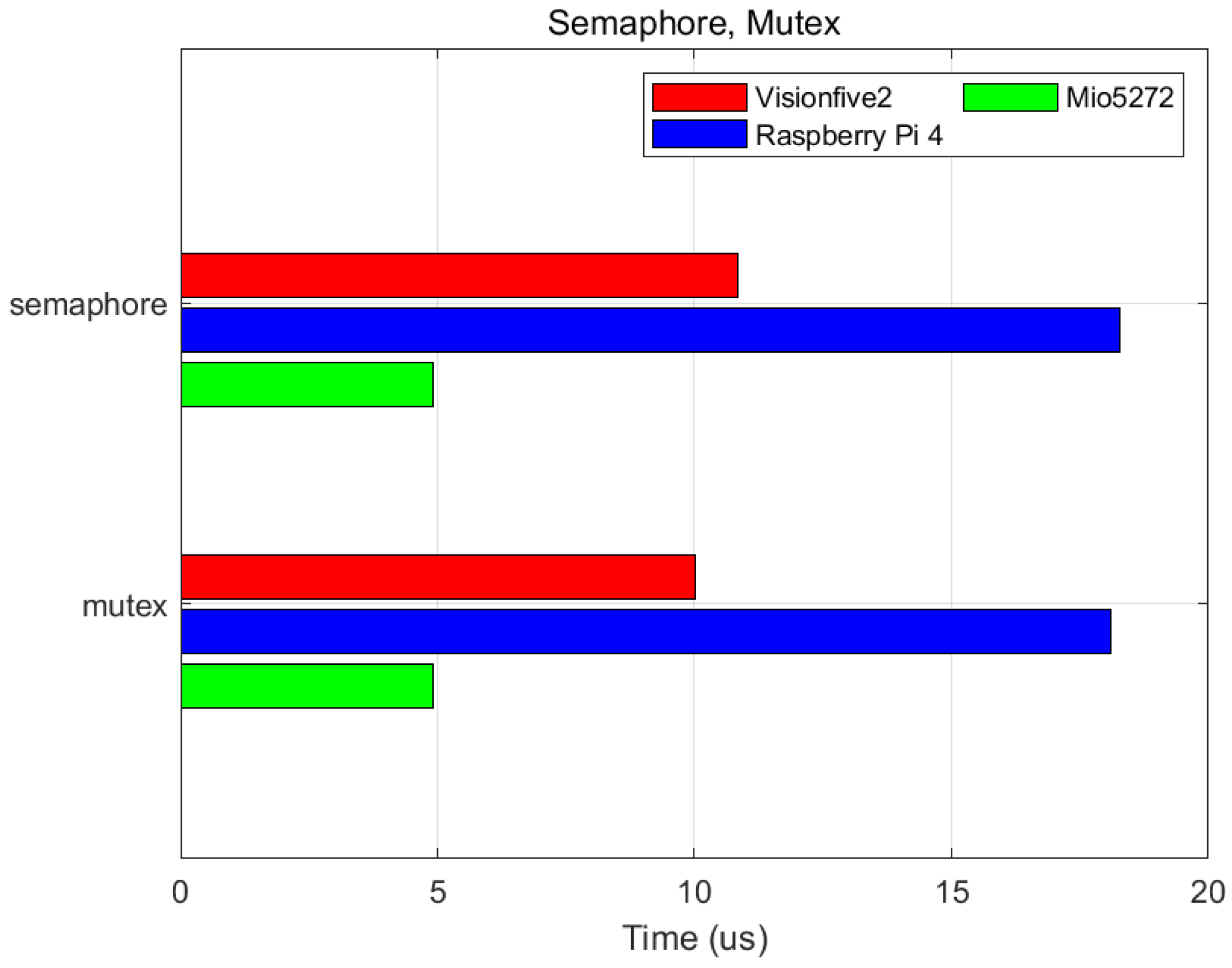

5.1.4. Semaphore and Mutex

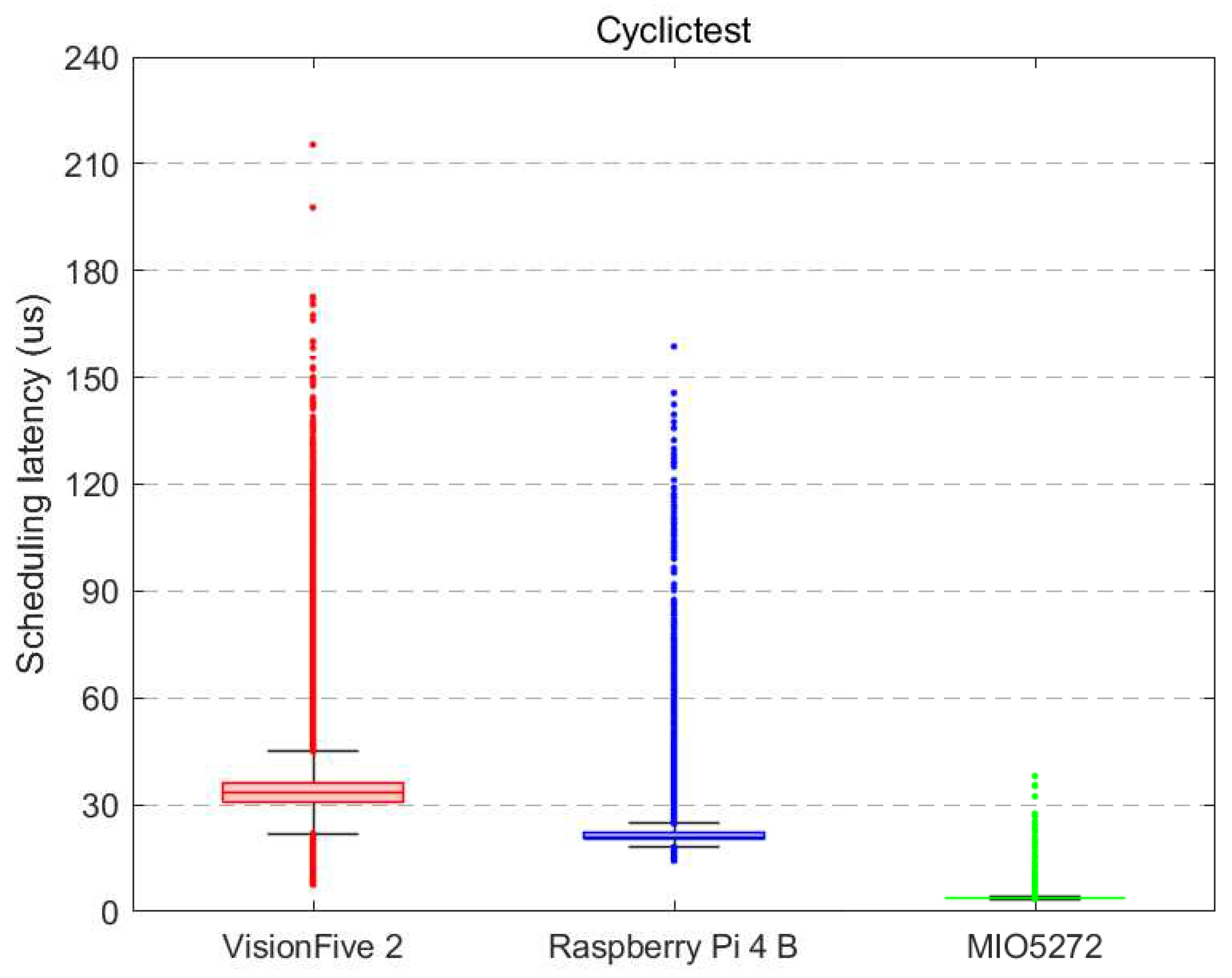

5.2. Scheduling Latency

| Hardware | Mean (us) | Min (us) | Max (us) | Sdev (us) |

|---|---|---|---|---|

| VisionFive 2 | 32.690 | 7.662 | 202.984 | 7.023 |

| Raspberry Pi 4 B | 21.472 | 14.311 | 158.704 | 1.440 |

| MIO-5272 | 3.919 | 3.489 | 38.051 | 0.202 |

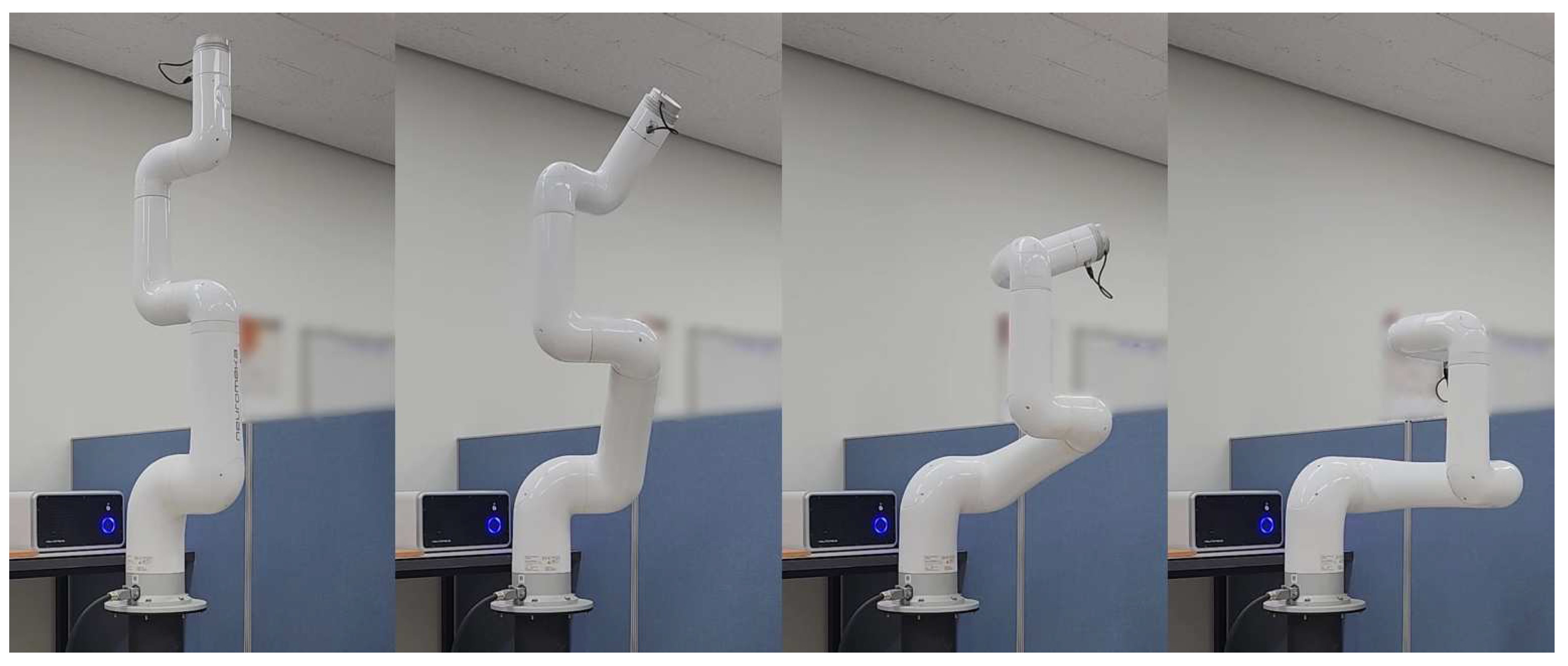

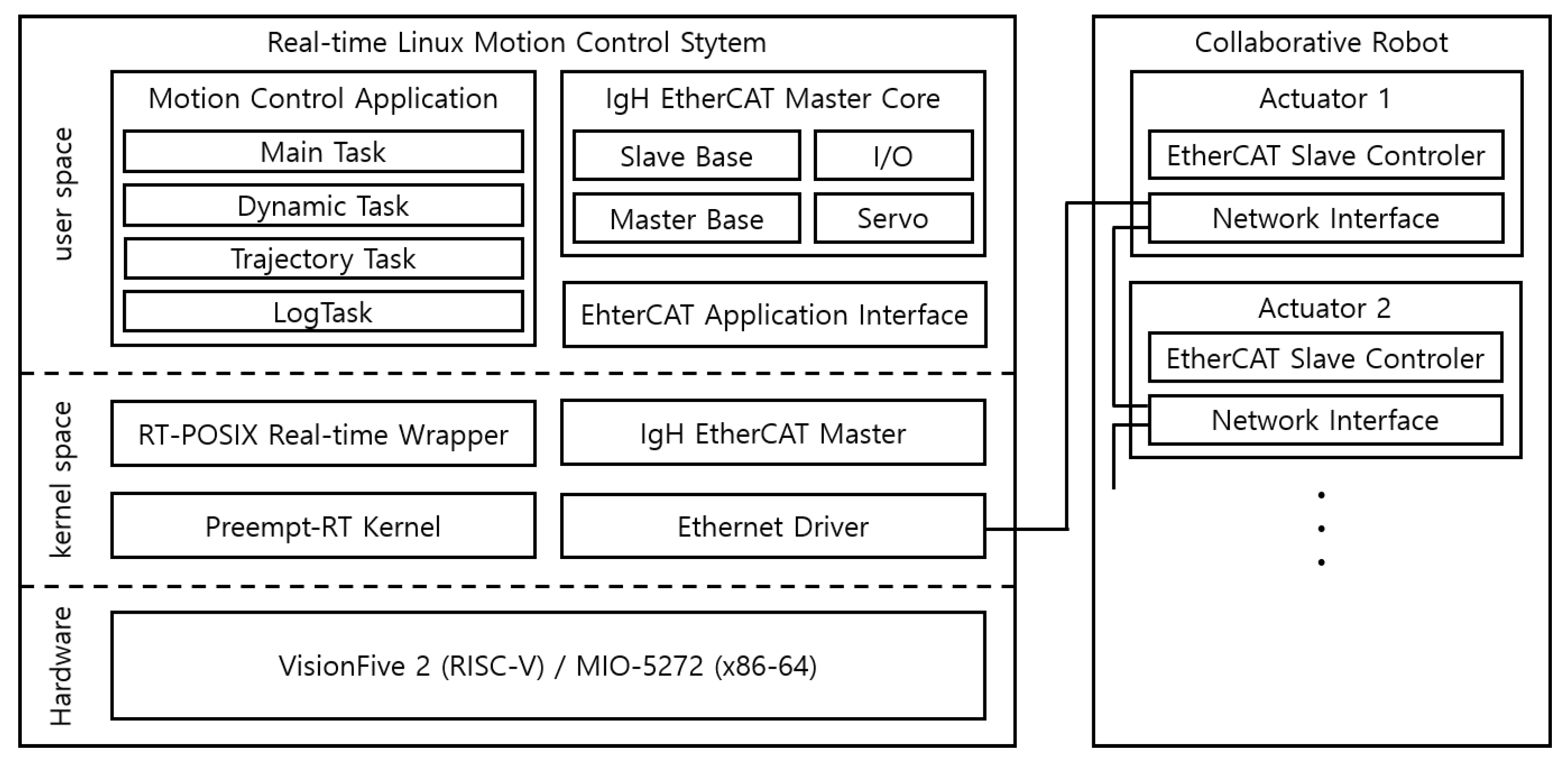

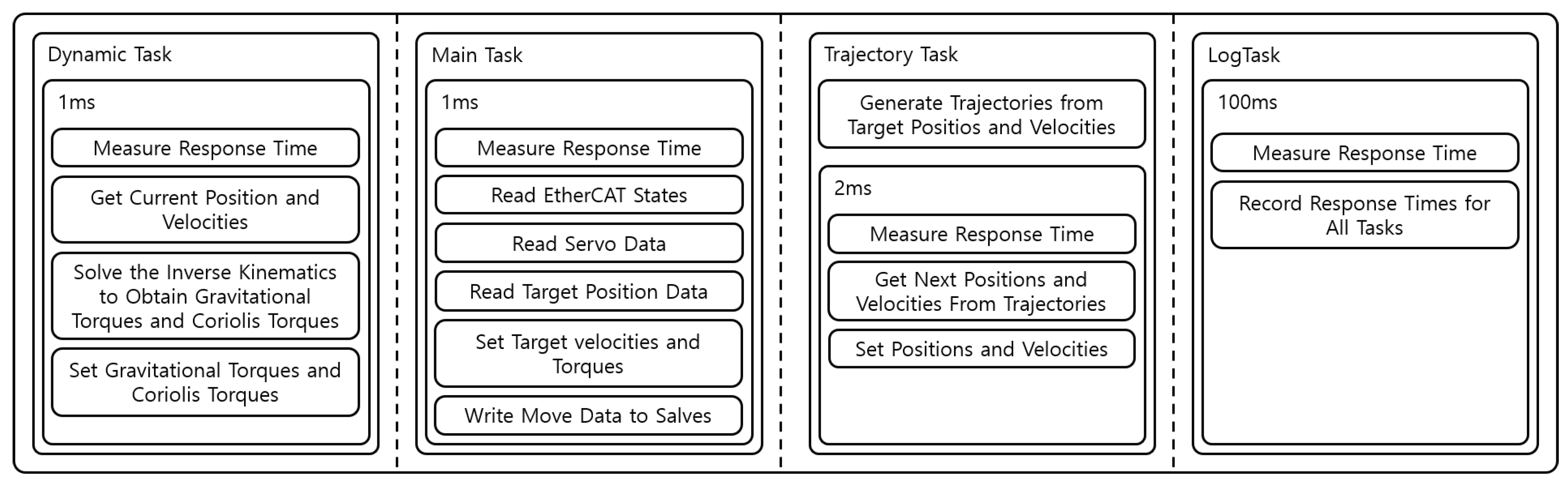

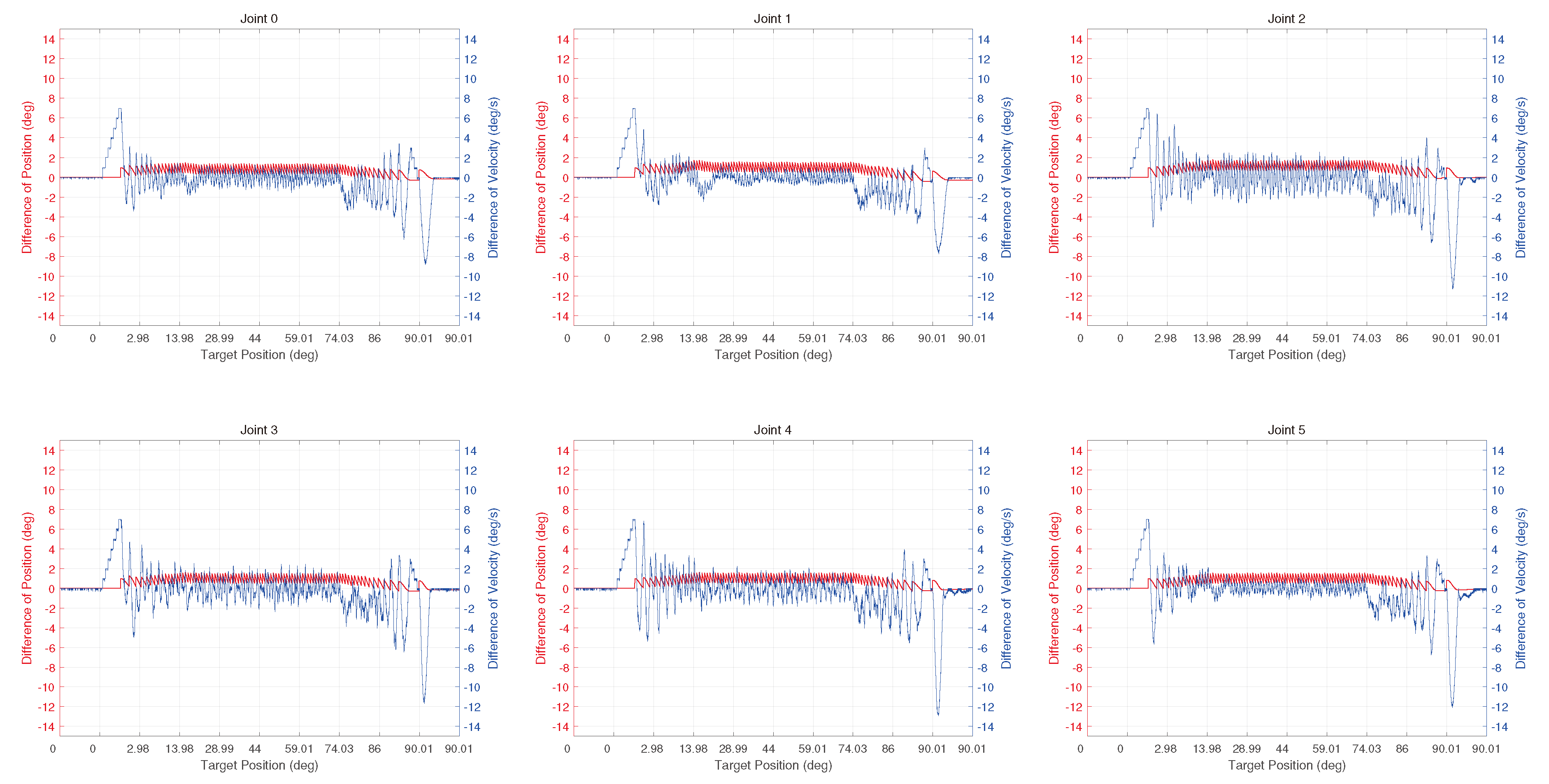

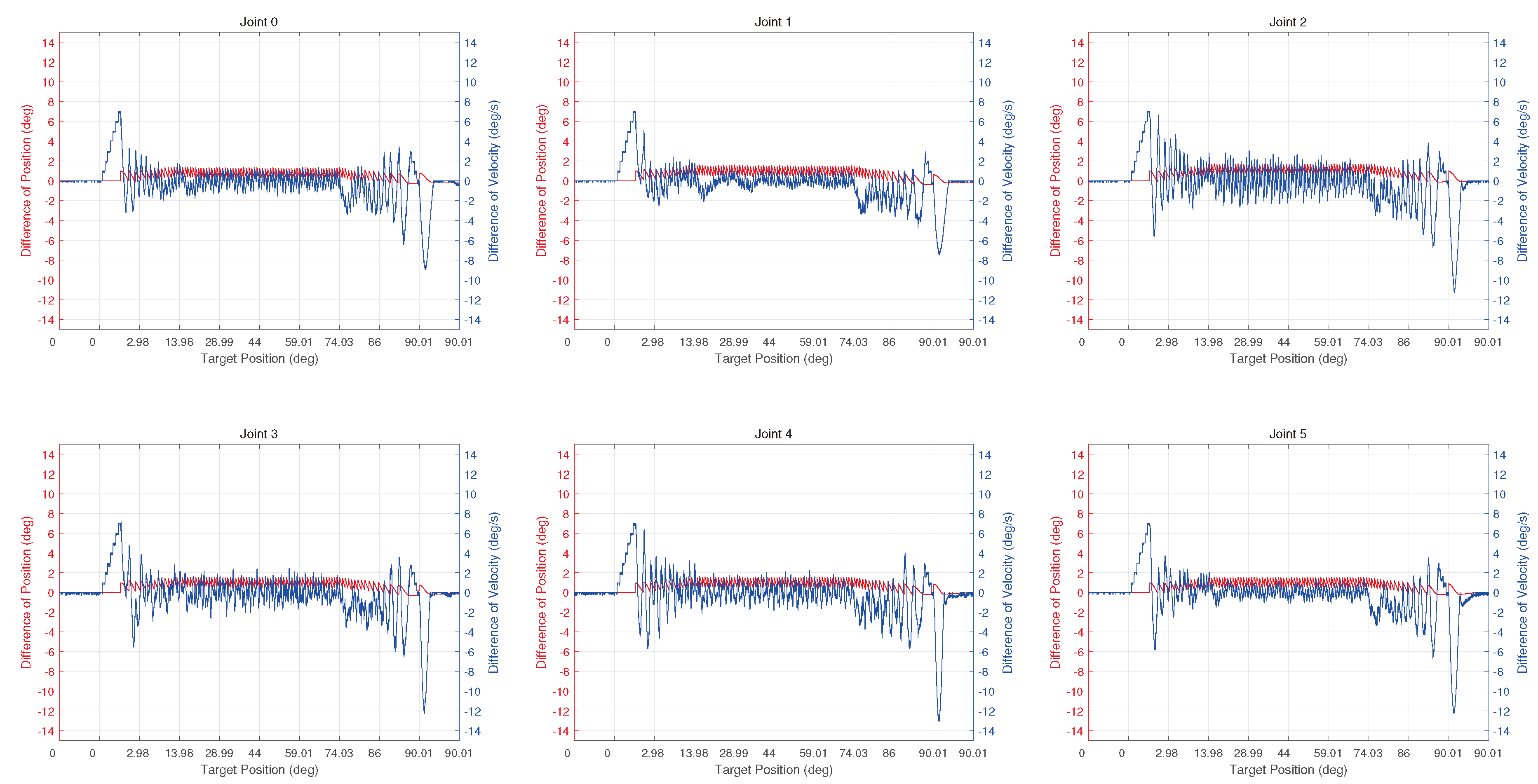

6. Real-time Performance Experiment on Collaborative Robot

6.1. Motion Control of a Collaborative Robot

7. Conclusion

References

- Davis, R.I.; Burns, A. A survey of hard real-time scheduling for multiprocessor systems. ACM computing surveys (CSUR) 2011, 43, 1–44. [Google Scholar] [CrossRef]

- Stankovic, J.A. Strategic directions in real-time and embedded systems. ACM Computing Surveys (CSUR) 1996, 28, 751–763. [Google Scholar] [CrossRef]

- Akesson, B.; Nasri, M.; Nelissen, G.; Altmeyer, S.; Davis, R.I. An empirical survey-based study into industry practice in real-time systems. In Proceedings of the 2020 IEEE Real-Time Systems Symposium (RTSS). IEEE; 2020; pp. 3–11. [Google Scholar]

- de Matos Pedro, A.; Pereira, D.; Pinho, L.M.; Pinto, J.S. Logic-based schedulability analysis for compositional hard real-time embedded systems. ACM SIGBED Review 2015, 12, 56–64. [Google Scholar] [CrossRef]

- Liu, D.; Hu, X.S.; Lemmon, M.D.; Ling, Q. Firm real-time system scheduling based on a novel QoS constraint. IEEE Transactions on Computers 2006, 55, 320–333. [Google Scholar] [CrossRef]

- Song, I.; Kim, S.; Karray, F. A real-time scheduler design for a class of embedded systems. IEEE/ASME Transactions on Mechatronics 2008, 13, 36–45. [Google Scholar] [CrossRef]

- Asanović, K.; Patterson, D.A. Instruction sets should be free: The case for risc-v. EECS Department, University of California, Berkeley, Tech. Rep. UCB/EECS-2014-146 2014. [Google Scholar]

- Patterson, D. Reduced instruction set computers then and now. Computer 2017, 50, 10–12. [Google Scholar] [CrossRef]

- Torres-Sánchez, E.; Alastruey-Benedé, J.; Torres-Moreno, E. Developing an AI IoT application with open software on a RISC-V SoC. In Proceedings of the 2020 XXXV Conference on Design of Circuits and Integrated Systems (DCIS). IEEE; 2020; pp. 1–6. [Google Scholar]

- Patterson, D.; Waterman, A. The RISC-V Reader: an open architecture Atlas. Strawberry Canyon, 2017. [Google Scholar]

- Ince, M.N.; Ledet, J.; Gunay, M. Building an open source Linux computing system on RISC-V. In Proceedings of the 2019 1st International Informatics and Software Engineering Conference (UBMYK). IEEE; 2019; pp. 1–4. [Google Scholar]

- Cannizzaro, M.J.; Gretok, E.W.; George, A.D. Risc-v benchmarking for onboard sensor processing. In Proceedings of the 2021 IEEE Space Computing Conference (SCC). IEEE; 2021; pp. 46–59. [Google Scholar]

- Abraham, V.; Ranpariya, D.; Parikh, P.; Gajjar, S.; Shah, D. Exploration of FreeRTOS on a RISC-V Architecture. In ICT Systems and Sustainability: Proceedings of ICT4SD 2022; Springer, 2022; pp. 1–11. [Google Scholar]

- Hambarde, P.; Varma, R.; Jha, S. The survey of real time operating system: RTOS. In Proceedings of the 2014 International Conference on Electronic Systems, Signal Processing and Computing Technologies. IEEE; 2014; pp. 34–39. [Google Scholar]

- Qian, K.; Wang, J.; Gopaul, N.S.; Hu, B. Low cost multisensor kinematic positioning and navigation system with Linux/RTAI. Journal of Sensor and Actuator Networks 2012, 1, 166–182. [Google Scholar] [CrossRef]

- Cifuentes-Cuadros, A.A.; Romero, E.; Caballa, S.; Vega-Centeno, D.; Elias, D.A. The LIBRA NeuroLimb: Hybrid Real-Time Control and Mechatronic Design for Affordable Prosthetics in Developing Regions. Sensors 2023, 24, 70. [Google Scholar] [CrossRef]

- Melot, N. Study of an operating system: FreeRTOS, 2009.

- Reghenzani, F.; Massari, G.; Fornaciari, W. The real-time linux kernel: A survey on preempt_rt. ACM Computing Surveys (CSUR) 2019, 52, 1–36. [Google Scholar] [CrossRef]

- de Oliveira, D.B.; Casini, D.; de Oliveira, R.S.; Cucinotta, T. Demystifying the real-time linux scheduling latency. In Proceedings of the 32nd Euromicro Conference on Real-Time Systems (ECRTS 2020). Schloss Dagstuhl-Leibniz-Zentrum für Informatik; 2020. [Google Scholar]

- Anh, T.N.B.; Tan, S.L. Real-time operating systems for small microcontrollers. IEEE micro 2009, 29, 30–45. [Google Scholar] [CrossRef]

- Peng, L.; Guan, F.; Perneel, L.; Timmerman, M. Behaviour and performance comparison between FreeRTOS and μC/OS-III. International Journal of Embedded Systems 2016, 8, 300–312. [Google Scholar] [CrossRef]

- Raymundo Belleza, R.; de Freitas Pignaton, E. Performance study of real-time operating systems for internet of things devices. IET Software 2018, 12, 176–182. [Google Scholar] [CrossRef]

- Yang, C.F.; Shinjo, Y. Obtaining hard real-time performance and rich Linux features in a compounded real-time operating system by a partitioning hypervisor. In Proceedings of the Proceedings of the 16th ACM SIGPLAN/SIGOPS International Conference on Virtual Execution Environments, 2020; pp. 59–72.

- Adam, G.K.; Petrellis, N.; Doulos, L.T. Performance assessment of linux kernels with PREEMPT_RT on ARM-based embedded devices. Electronics 2021, 10, 1331. [Google Scholar] [CrossRef]

- Jämbäck, M. Evaluation of Real-Time Linux on RISC-V processor architecture. Master’s thesis, 2022.

- Neuhard, Y. A Comparison of Real-time Operating Systems for Embedded Computing.

- Qutqut, M.H.; Al-Sakran, A.; Almasalha, F.; Hassanein, H.S. Comprehensive survey of the IoT open-source OSs. IET Wireless Sensor Systems 2018, 8, 323–339. [Google Scholar] [CrossRef]

- Shammar, E.A.; Zahary, A.T. The Internet of Things (IoT): a survey of techniques, operating systems, and trends. Library Hi Tech 2020, 38, 5–66. [Google Scholar] [CrossRef]

- Abbott, D. Linux for embedded and real-time applications. Elsevier, 2011. [Google Scholar]

- Litayem, N.; Saoud, S.B. Impact of the Linux real-time enhancements on the system performances for multi-core intel architectures. International Journal of Computer Applications 2011, 17, 17–23. [Google Scholar] [CrossRef]

- Delgado, R.; Choi, B.W. New insights into the real-time performance of a multicore processor. IEEE Access 2020, 8, 186199–186211. [Google Scholar] [CrossRef]

- Venkataraman, A.; Jagadeesha, K.K. Evaluation of inter-process communication mechanisms. Architecture 2015, 86, 64. [Google Scholar]

- Alagalla, A.; Rajapaksha, U.S. Techniques of Enhancing Synchronization Efficiency of Distributed Real Time Operating Systems. In Proceedings of the 2022 2nd International Conference on Advanced Research in Computing (ICARC). IEEE; 2022; pp. 308–313. [Google Scholar]

- Silva, M.; Cerdeira, D.; Pinto, S.; Gomes, T. Operating systems for Internet of Things low-end devices: Analysis and benchmarking. IEEE Internet of Things Journal 2019, 6, 10375–10383. [Google Scholar] [CrossRef]

- Kerrisk, M. The Linux programming interface: a Linux and UNIX system programming handbook; No Starch Press, 2010.

- Alonso, S.; Lázaro, J.; Jiménez, J.; Bidarte, U.; Muguira, L. Evaluating latency in multiprocessing embedded systems for the smart grid. Energies 2021, 14, 3322. [Google Scholar] [CrossRef]

- Delgado, R.; Choi, B.W.; Song, H. Application of etherCAT in microgrid communication network: a case study. In Proceedings of the 2018 International Conference on Platform Technology and Service (PlatCon). IEEE; 2018; pp. 1–6. [Google Scholar]

- Delgado, R.; Hong, C.H.; Shin, W.C.; Choi, B.W. Implementation and performance analysis of an EtherCAT Master on the latest real-time embedded Linux. International Journal of Applied Engineering Research 2015, 10, 44603–44609. [Google Scholar]

- Cho, S.Y.; Delgado, R.; Choi, B.W. Feasibility Study for a Python-Based Embedded Real-Time Control System. Electronics 2023, 12, 1426. [Google Scholar] [CrossRef]

- Tadese, M.; Pico, N.; Seo, S.; Moon, H. A Two-Step Method for Dynamic Parameter Identification of Indy7 Collaborative Robot Manipulator. Sensors 2022, 22, 9708. [Google Scholar] [CrossRef] [PubMed]

| Hardware | Microcontroller Unit | Architecture | RTOS | kernel version |

|---|---|---|---|---|

| HiFive1 Rev B | SiFive FE310-G002 32-bit | RISC-V RV32IMAC | FreeRTOS | 10.2.0 |

| STM3240G-EVAL | STM32F407IGH6 with ARM Cortex-M4F 32-bit | ARMv7-M | FreeRTOS | 10.2.0 |

| Hardware | Microporcessor Unit | Architecture | Real Time Kernel | kernel version |

|---|---|---|---|---|

| VisionFive 2 | JH7110 64-bit quad-core | RISC-V U74-MC | Preempt-RT | 5.15.0-rt17+ |

| Raspberry Pi 4 B | Broadcom BCM2711 ARM Cortex-A72 64-bit quad-core | ARMv8-A | Preempt-RT | 5.15.92-rt57-v8+ |

| MIO-5272 | Intel Core I7 6600U | x86-64 | Preempt-RT | 5.15.79-rt54 |

| HiFive1 Rev B (10.2.0) | STM3240G-EVAL (10.2.0) | STM3240G-EVAL (10.4.4) | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ITC | Mean (us) | Min (us) | Max (us) | Sdev (us) | Mean (us) | Min (us) | Max (us) | Sdev (us) | Mean (us) | Min (us) | Max (us) | Sdev (us) |

| Counting Semaphore | 4.74 | 4.73 | 4.74 | 0.004 | 12.64 | 12.63 | 12.64 | 0.003 | 12.39 | 12.39 | 12.40 | 0.002 |

| Mutex | 4.90 | 4.73 | 4.95 | 0.037 | 13.68 | 13.12 | 13.73 | 0.1 | 13.51 | 13.50 | 13.52 | 0.004 |

| Binary Semaphore | 4.68 | 4.65 | 4.73 | 0.019 | 27.97 | 0.07 | 334.71 | 68.8 | 12.50 | 12.50 | 12.51 | 0.002 |

| VisionFive 2 | Raspberry Pi 4 B | MIO-5272 | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ITC | Mean (us) | Min (us) | Max (us) | Sdev (us) | Mean (us) | Min (us) | Max (us) | Sdev (us) | Mean (us) | Min (us) | Max (us) | Sdev (us) |

| Semaphore | 10.84 | 10.5 | 63.3 | 0.47 | 18.29 | 17.19 | 82.85 | 1.94 | 4.92 | 3.82 | 83.52 | 0.24 |

| Mutex | 10.01 | 9.75 | 47.00 | 0.43 | 18.11 | 16.76 | 259.74 | 1.98 | 4.90 | 3.75 | 712.10 | 1.69 |

| Task | Response time (us) | Period (ms) | Priority | |

|---|---|---|---|---|

| VisionFive 2 | MIO-5272 | |||

| Dynamic Task | 112.71 | 95.89 | 1 | 95 |

| Main Task | 292.14 | 152.99 | 1 | 90 |

| Trajectory Task | 319.04 | 159.97 | 2 | 85 |

| Log Task | 329.50 | 164.08 | 100 | 70 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).