Submitted:

09 January 2023

Posted:

10 January 2023

You are already at the latest version

Abstract

Keywords:

Introduction:

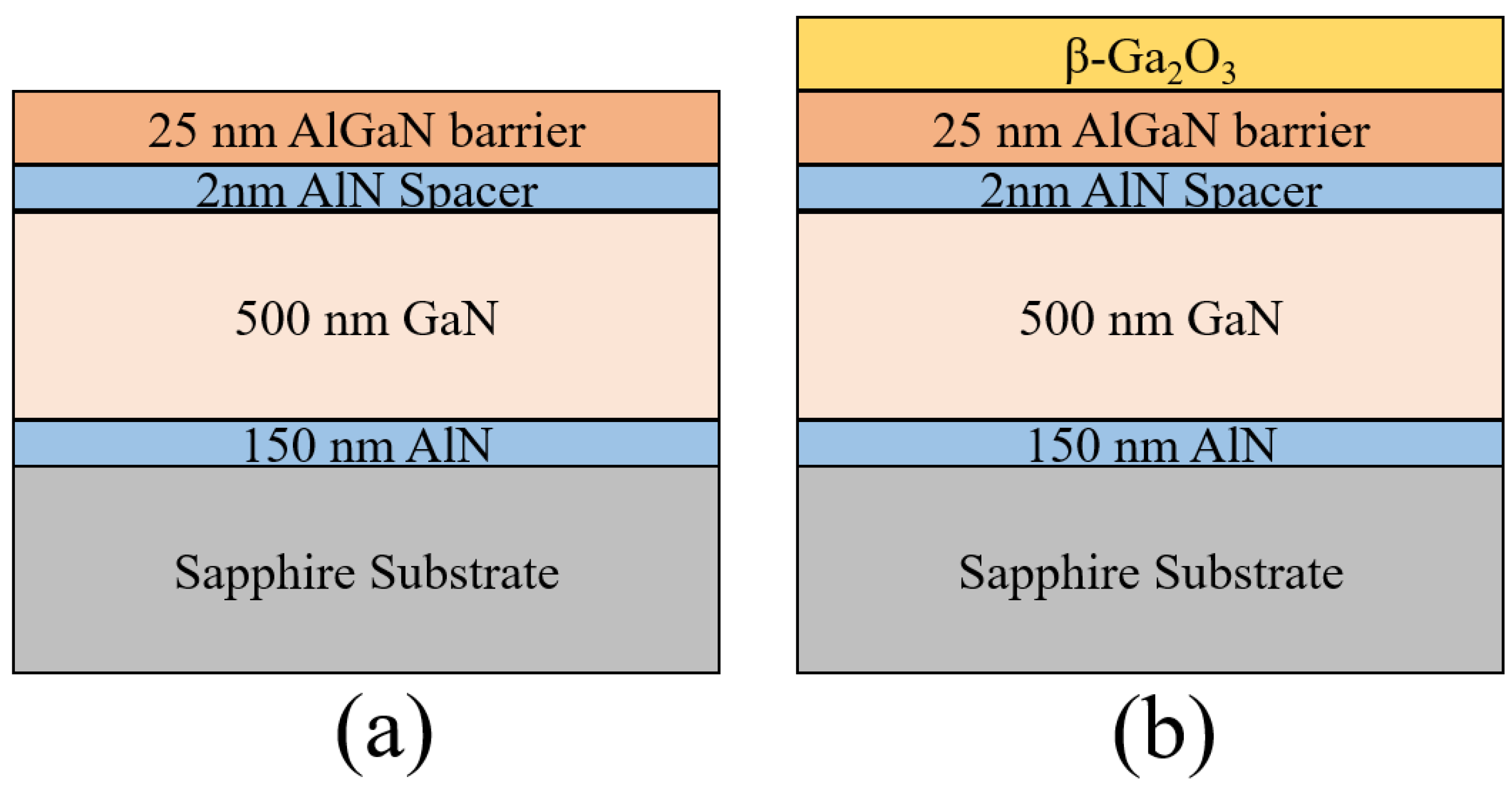

Experimental Methods:

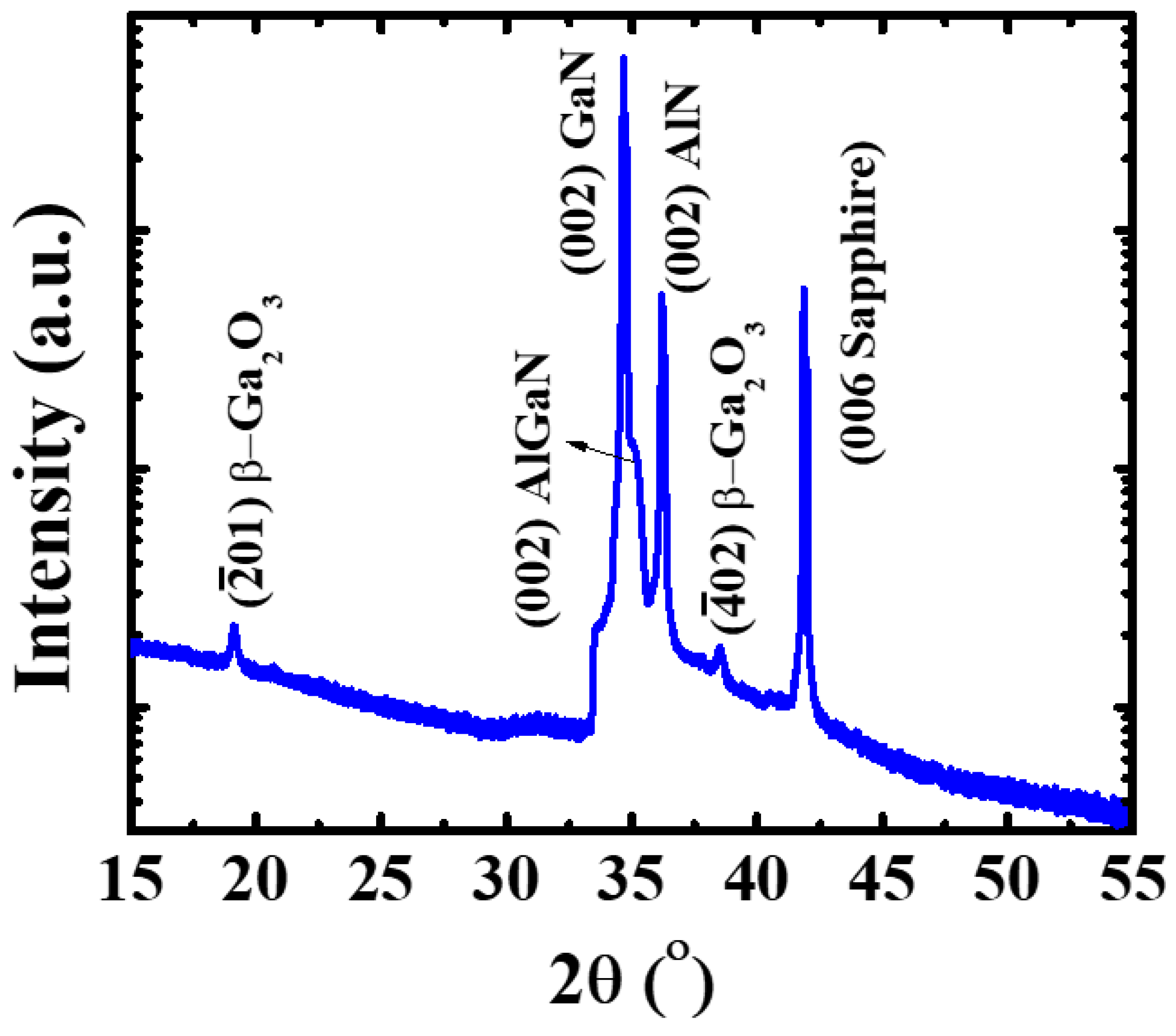

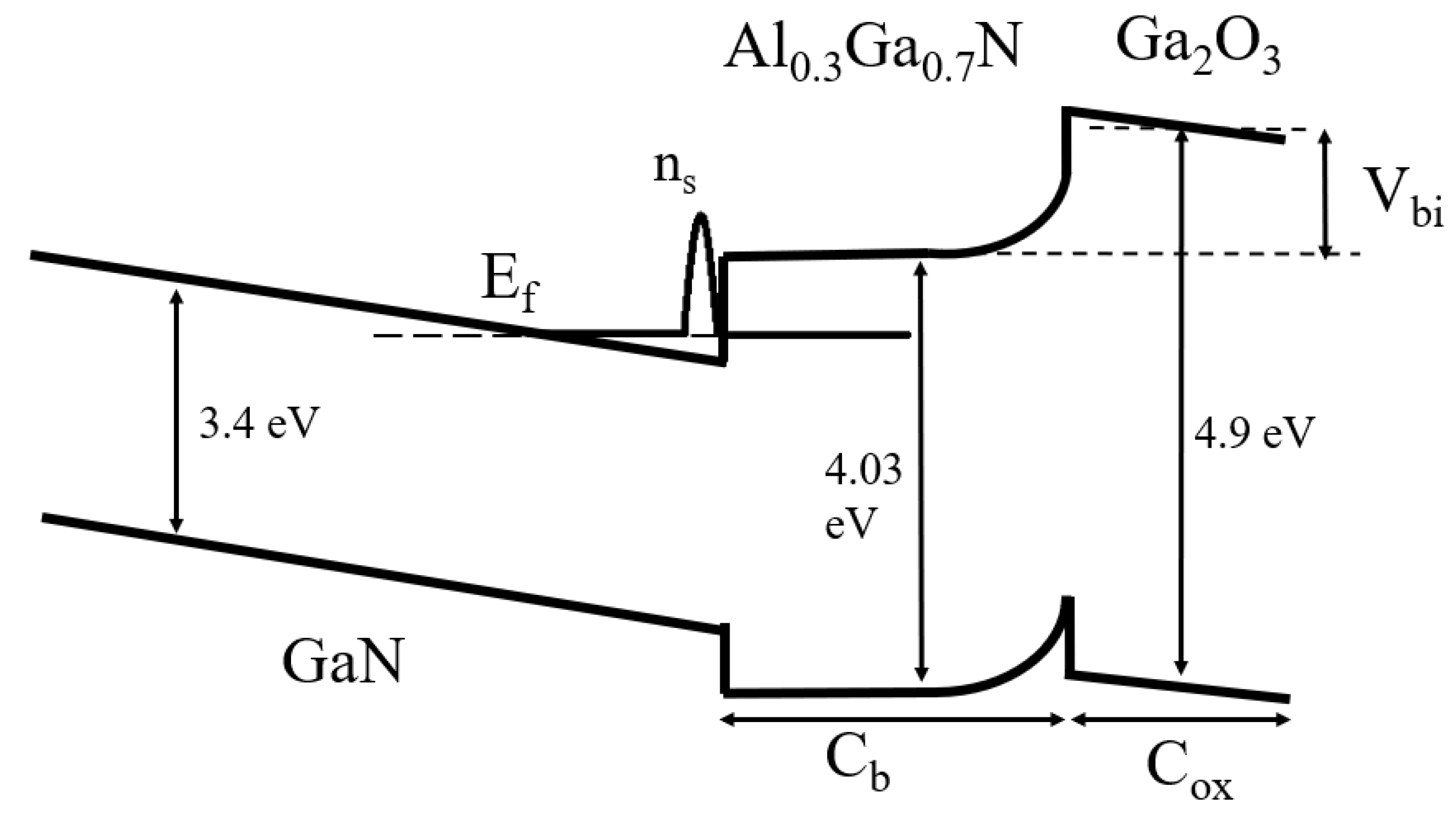

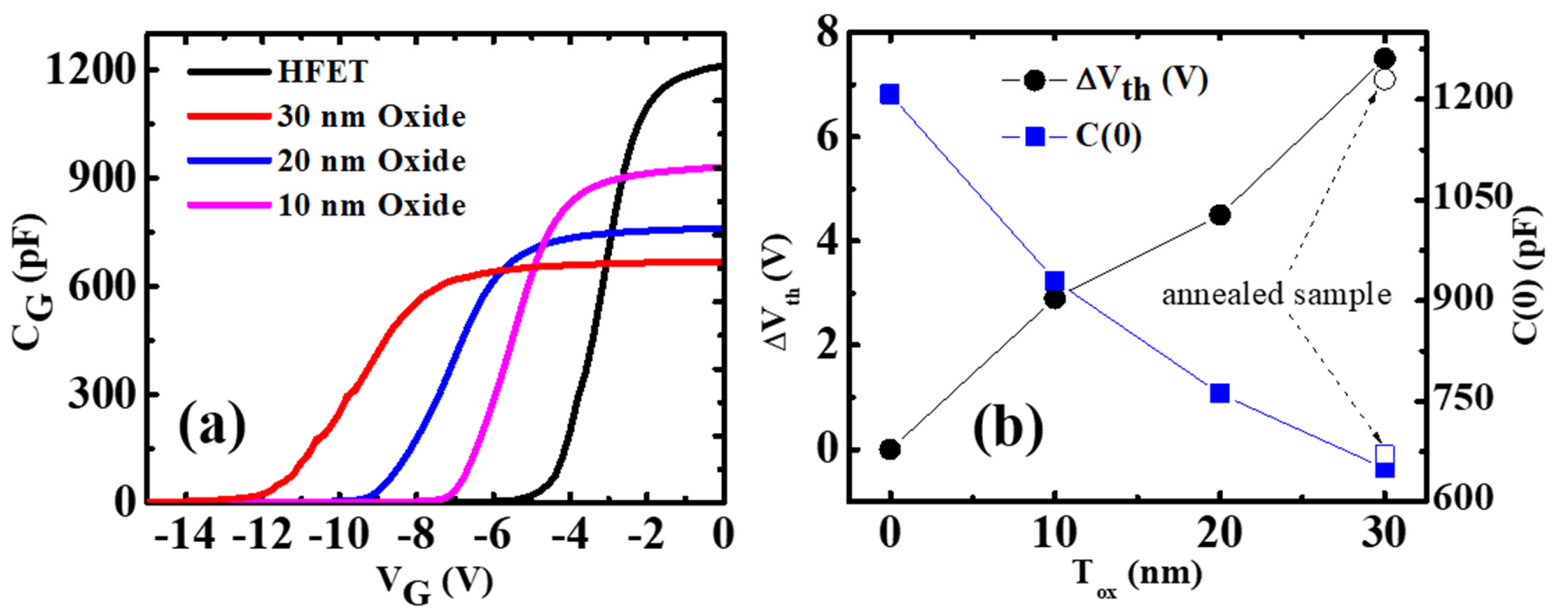

Results and Discussions:

| Vth (V) |

µ (cm2V-1 s-1) (Hall) |

Rsh (Ωcm-2) (Hall) |

Nd (cm-3) (Hall) |

ns (cm-2) (C-V) |

ns (cm-2) (Hall) |

Qox (Ccm-2) (C-V) |

Dit (cm-2eV-1) (C-V) |

|

|---|---|---|---|---|---|---|---|---|

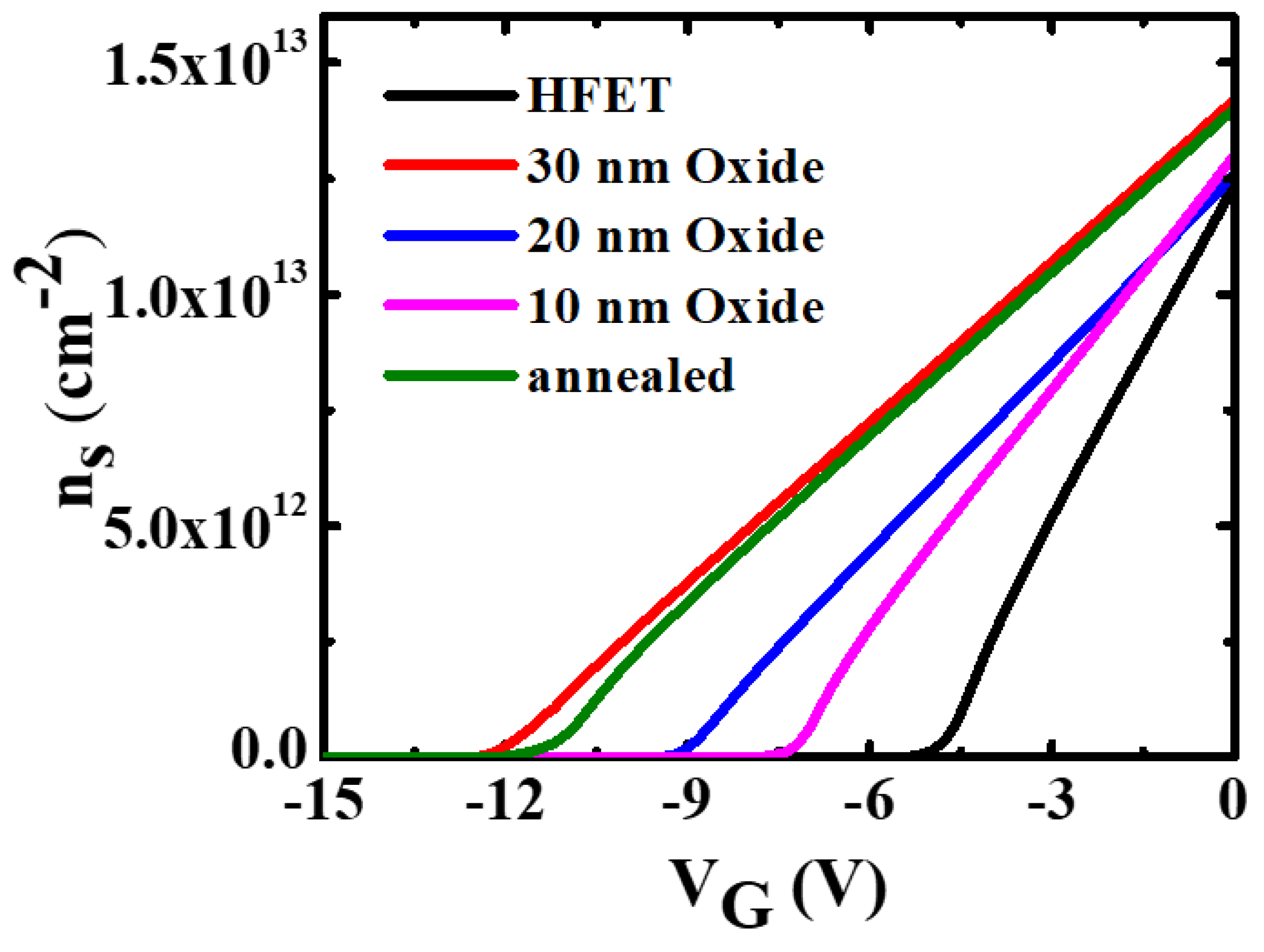

| HFET | -5 | 750 | 537 | 6.8×1018 | 1.25×1013 | 1.55×1013 | None | None |

| 10 nm | -7.9 | 772 | 630 | 5.0×1018 | 1.28×1013 | 1.4×1013 | -6.68×1012 | 7.47×1012 |

| 20 nm | -9.5 | 770 | 650 | 4.2×1018 | 1.24×1013 | 1.42×1013 | -1.64×1013 | 7.57×1012 |

| 30 nm | -12.5 | 776 | 685 | 4.4×1018 | 1.4×1013 | 1.4×1013 | -2×1013 | 4.98×1012 |

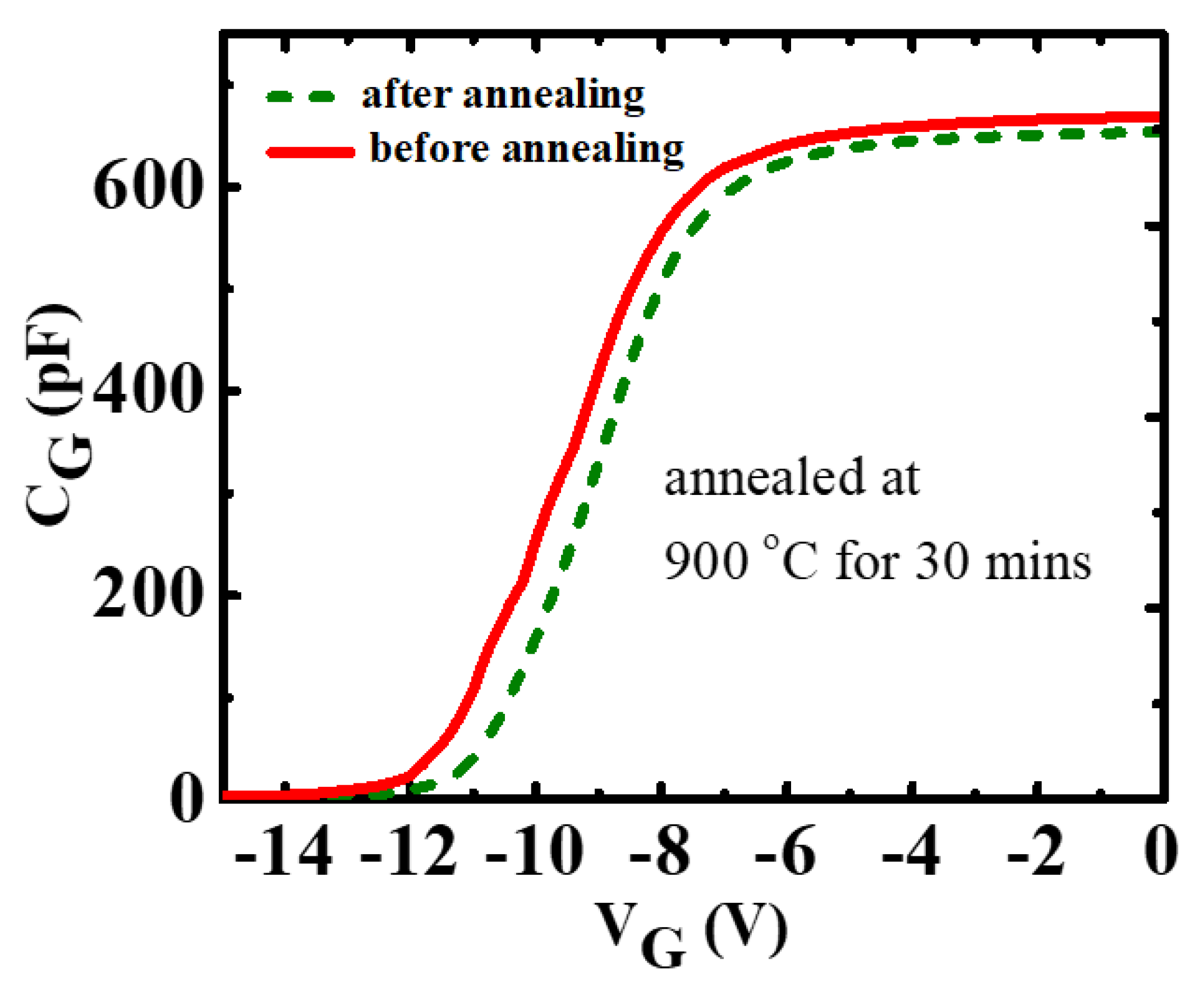

| annealed | -12.1 | 760 | 680 | 4.5×1018 | 1.4×1013 | 1.4×1013 | -3.06×1012 | 3×1012 |

Conclusions:

Supplementary Materials

Author Contributions

Acknowledgments

Data availability

Conflicts of Interest

References

- Morkoç, H. Handbook of Nitride Semiconductors and Devices, Materials Properties, Physics and Growth; 2009; Wiley-VCH GmbH, Weinhem, Germany. ISBN 9783527408375.

- Mohammad SN, Salvador AA, Morkoc H. Emerging gallium nitride-based devices. Proceedings of the IEEE. 1995; 83(10):1306-55. [CrossRef]

- Morkoç, H. Nitride Semiconductors and Devices; 1999, Springer-Verlag, Berlin Heidelberg, New York, ISBN 3-540-64038.

- Zeng, F.; An, J.X.; Zhou, G.; Li, W.; Wang, H.; Duan, T.; Jiang, L.; Yu, H. A Comprehensive Review of Recent Progress on GaN High Electron Mobility Transistors: Devices, Fabrication and Reliability. Electronics 2018, Vol. 7, Page 377 2018, 7, 377, doi:10.3390/ELECTRONICS7120377. [CrossRef]

- Islam, N.; Mohamed, M.F.P.; Khan, M.F.A.J.; Falina, S.; Kawarada, H.; Syamsul, M. Reliability, Applications and Challenges of GaN HEMT Technology for Modern Power Devices: A Review. Crystals (Basel) 2022, 12, 1581, doi:10.3390/cryst12111581. [CrossRef]

- Kim, H.; Lee, J.; Liu, D.; Lu, W. Gate Current Leakage and Breakdown Mechanism in Unpassivated AlGaNGaN High Electron Mobility Transistors by Post-Gate Annealing. Appl Phys Lett 2005, 86, 1–3, doi:10.1063/1.1899255. [CrossRef]

- Leach, J.H.; Morkoç, H. Status of Reliability of GaN-Based Heterojunction Field Effect Transistors. In Proceedings of the IEEE; Institute of Electrical and Electronics Engineers Inc., 2010; Vol. 98, pp. 1127–1139. [CrossRef]

- Purnachandra Rao, G.; Singh, R.; Lenka, T.R. Performance Analysis of AlGaN/GaN HEMT for RF and Microwave Nanoelectronics Applications. 2023, 139–153, doi:10.1007/978-981-19-2165-0_11. [CrossRef]

- Trew RJ. Wide bandgap semiconductor transistors for microwave power amplifiers. IEEE Microwave magazine. 2000 ;1(1):46-54. [CrossRef]

- Brar B, Boutros K, DeWarnes RE, Tilak V, Shealy R, Eastman L. Impact ionization in high performance AlGaN/GaN HEMTs. In Proceedings. IEEE Lester Eastman Conference on High Performance Devices 2002 (pp. 487-491).

- Trew RJ, Green DS, Shealy JB. AlGaN/GaN HFET reliability. IEEE Microwave magazine. 2009;10(4):116-27. [CrossRef]

- Zhou, H.; Lou, X.; Sutherlin, K.; Summers, J.; Kim, S.B.; Chabak, K.D.; Gordon, R.G.; Ye, P.D. DC and RF Performance of AlGaN/GaN/SiC MOSHEMTs with Deep Sub-Micron T-Gates and Atomic Layer Epitaxy MgCaO as Gate Dielectric. IEEE Electron Device Letters 2017, 38, 1409–1412. [CrossRef]

- Liu C, Chor EF, Tan LS. Investigations of Hf O 2∕ Al Ga N∕ Ga N metal-oxide-semiconductor high electron mobility transistors. Applied physics letters. 2006; 88(17):173504. [CrossRef]

- Asubar JT, Yatabe Z, Gregusova D, Hashizume T. Controlling surface/interface states in GaN-based transistors: Surface model, insulated gate, and surface passivation. Journal of Applied Physics. 2021; 129(12):121102. [CrossRef]

- Lee BH, Kang L, Nieh R, Qi WJ, Lee JC. Thermal stability and electrical characteristics of ultrathin hafnium oxide gate dielectric reoxidized with rapid thermal annealing. Applied Physics Letters. 2000; 76(14):1926-8. [CrossRef]

- Gusev EP, Copel M, Cartier E, Baumvol IJ, Krug C, Gribelyuk MA. High-resolution depth profiling in ultrathin Al 2 O 3 films on Si. Applied Physics Letters. 2000; 76(2):176-8. [CrossRef]

- Lee BH, Kang L, Nieh R, Qi WJ, Lee JC. Thermal stability and electrical characteristics of ultrathin hafnium oxide gate dielectric reoxidized with rapid thermal annealing. Applied Physics Letters. 2000; 76(14):1926-8. [CrossRef]

- Copel M, Gribelyuk M, Gusev E. Structure and stability of ultrathin zirconium oxide layers on Si (001). Applied Physics Letters. 2000; 76(4):436-8. [CrossRef]

- Husna, F.; Lachab, M.; Sultana, M.; Adivarahan, V.; Fareed, Q.; Khan, A. High-Temperature Performance of AlGaN/GaN MOSHEMT with SiO2 Gate Insulator Fabricated on Si (111) Substrate. IEEE Trans Electron Devices 2012, 59, 2424–2429, doi:10.1109/TED.2012.2204888. [CrossRef]

- Balakrishnan G, Babu RV, Shin KS, Song JI. Growth of highly oriented γ-and α-Al2O3 thin films by pulsed laser deposition. Optics & Laser Technology. 2014; 56:317-21. [CrossRef]

- Passlack M, Schubert EF, Hobson WS, Hong M, Moriya N, Chu SN, Konstadinidis K, Mannaerts JP, Schnoes ML, Zydzik GJ. Ga2O3 films for electronic and optoelectronic applications. Journal of applied physics. 1995; 77(2):686-93. [CrossRef]

- Green, A.J.; Speck, J.; Xing, G.; Moens, P.; Allerstam, F.; Gumaelius, K.; Neyer, T.; Arias-Purdue, A.; Mehrotra, V.; Kuramata, A.; et al. β-Gallium Oxide Power Electronics. APL Mater 2022, 10, doi:10.1063/5.0060327. [CrossRef]

- Choi DW, Chung KB, Park JS. Low temperature Ga2O3 atomic layer deposition using gallium tri-isopropoxide and water. Thin Solid Films. 2013; 546:31-4. [CrossRef]

- Donmez I, Ozgit-Akgun C, Biyikli N. Low temperature deposition of Ga2O3 thin films using trimethylgallium and oxygen plasma. Journal of Vacuum Science & Technology A: Vacuum, Surfaces, and Films. 2013; 31(1):01A110. [CrossRef]

- Hashizume, T.; Nishiguchi, K.; Kaneki, S.; Kuzmik, J.; Yatabe, Z. State of the Art on Gate Insulation and Surface Passivation for GaN-Based Power HEMTs. Mater Sci Semicond Process 2018, 78, 85–95. [CrossRef]

- Hasan, S.; Mamun, A.; Hussain, K.; Gaevski, M.; Ahmad, I.; Khan, A. Growth Evolution of High-Quality MOCVD Aluminum Nitride Using Nitrogen as Carrier Gas on the Sapphire Substrate. J Mater Res 2021, 36, 4360–4369, doi:10.1557/s43578-021-00387-z. [CrossRef]

- Hasan, S.; Mamun, A.; Hussain, K.; Patel, D.; Gaevski, M.; Ahmad, I.; Khan, A. Investigation of MOCVD Grown Crack-Free 4 Μm Thick Aluminum Nitride Using Nitrogen as a Carrier Gas. MRS Adv 2021, 6, 456–460, doi:10.1557/s43580-021-00071-8. [CrossRef]

- Shrestha, N.; Shrestha, N.M.; Wang, Y.Y.; Li, Y.; Chang, E.Y. Effect of AlN Spacer Layer on AlGaN/GaN HEMTs; 2013; ISBN 978-3-901578-26-7.

- Hubáček, T.; Hospodková, A.; Kuldová, K.; Slavická Zíková, M.; Pangrác, J.; Čížek, J.; Liedke, M.O.; Butterilng, M.; Wagner, A.; Hubík, P.; et al. Improvement of Luminescence Properties of N-GaN Using TEGa Precursor. J Cryst Growth 2020, 531, 125383, doi:10.1016/j.jcrysgro.2019.125383. [CrossRef]

- Roy, P.; Jawanpuria, S.; Vismita; Prasad, S.; Islam, A. Characterization of AlGaN and GaN Based HEMT with AlN Interfacial Spacer. In Proceedings of the Proceedings - 2015 5th International Conference on Communication Systems and Network Technologies, CSNT 2015; Institute of Electrical and Electronics Engineers Inc., 2015; pp. 786–788.

- Jewel, MU, Hasan, S., Crittenden, S., Avrutin V, Özgür Ü, Morkoç H., Ahmad, I., Growth of Thick Phase-Pure β-Ga2O3 on a c-Plane Sapphire Substrate Using MOCVD. Submitted Manuscript 2022.

- Ghose, S.; Rahman, S.; Hong, L.; Rojas-Ramirez, J.S.; Jin, H.; Park, K.; Klie, R.; Droopad, R. Growth and Characterization of β-Ga2O3 Thin Films by Molecular Beam Epitaxy for Deep-UV Photodetectors. J Appl Phys 2017, 122, doi:10.1063/1.4985855. [CrossRef]

- Moram MA, Vickers ME. X-ray diffraction of III-nitrides. Reports on progress in physics. 2009 Feb 20;72(3):036502. [CrossRef]

- George, S.M. Atomic Layer Deposition: An Overview. Chem Rev 2010, 110, 111–131, doi:10.1021/CR900056B. [CrossRef]

- M Grundmann, BandEng. 2005. http://my.ece.ucsb.edu/mgrundmann/.

- Langer JM, Heinrich H. Deep-level impurities: A possible guide to prediction of band-edge discontinuities in semiconductor heterojunctions. Physical review letters. 1985; 55(13):1414. [CrossRef]

- Jena, D. Polarization Induced Electron Populations in III-V Nitride Semiconductors Transport, Growth, and Device Applications; 2003, Doctoral Dissertation, University of California Santa Barbara.

- Langer JM, Delerue C, Lannoo M, Heinrich H. Transition-metal impurities in semiconductors and heterojunction band lineups. Physical Review B. 1988; 38(11):7723. [CrossRef]

- Rai S, Adivarahan V, Tipirneni N, Koudymov A, Yang J, Simin G, Khan MA. Low threshold-14 W/mm ZrO2/AlGaN/GaN metal–oxide–semiconductor heterostructure field effect transistors. Japanese journal of applied physics. 2006;45(6R):4985. [CrossRef]

- Shih, H.Y.; Chu, F.C.; Das, A.; Lee, C.Y.; Chen, M.J.; Lin, R.M. Atomic Layer Deposition of Gallium Oxide Films as Gate Dielectrics in AlGaN/GaN Metal–Oxide–Semiconductor High-Electron-Mobility Transistors. Nanoscale Res Lett 2016, 11, doi:10.1186/S11671-016-1448-Z. [CrossRef]

- Sze, S.; Li, Y.; Ng, K. Physics of Semiconductor Devices; John Wiley & Sons, Inc., 2021.

- Mollah S, Hussain K, Mamun A, Alam MD, Chandrashekhar MV, Simin G, Khan A. Threshold voltage control with high-temperature gate-oxide annealing in ultrawide bandgap AlGaN-channel MOSHFETs. Applied Physics Express. 2022;15(10):104001. [CrossRef]

- Schroder, D.K. Frontmatter. In Semiconductor Material and Device Characterization; John Wiley & Sons, Inc., 2005.

- Remesh, N.; Kumar, S.; Guiney, I.; Humphreys, C.J.; Raghavan, S.; Muralidharan, R.; Nath, D.N. A Novel Technique to Investigate the Role of Traps in the Off-State Performance of AlGaN/GaN High Electron Mobility Transistor on Si Using Substrate Bias. Physica Status Solidi (A) Applications and Materials Science 2020, 217, doi:10.1002/PSSA.201900794. [CrossRef]

- Osvald J. Interface traps contribution to capacitance of Al2O3/(GaN) AlGaN/GaN heterostructures at low frequencies. Physica E: Low-dimensional Systems and Nanostructures. 2017; 93:238-42. [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).