Submitted:

05 October 2023

Posted:

09 October 2023

You are already at the latest version

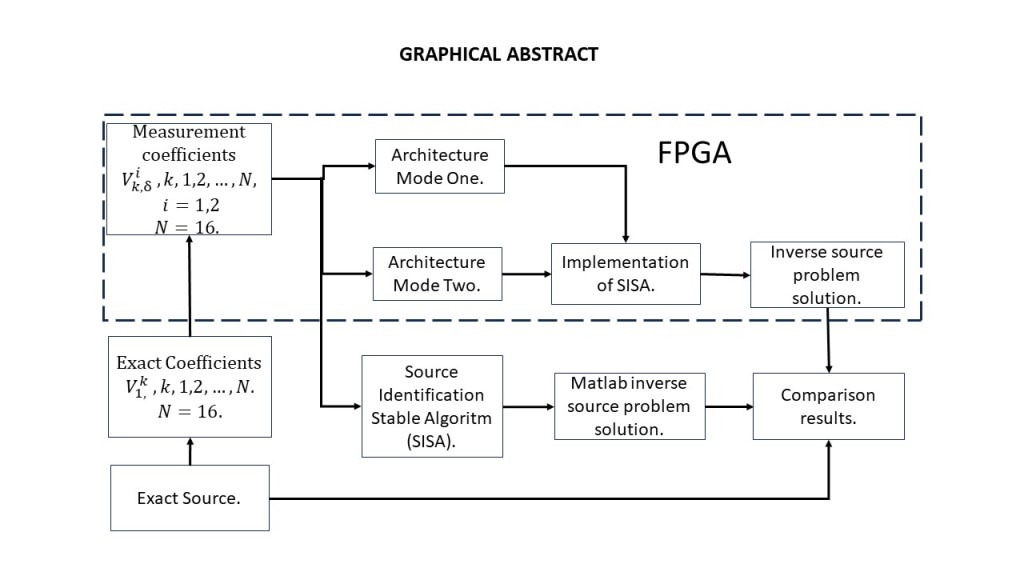

Abstract

Keywords:

1. Introduction

2. Basic elements

2.1. FPGA

- FPGAs are more flexible than Complex Programmable Logic Devices (CPLDs), generally having a greater number of both logic blocks and programmable interconnects.

- FPGAs have a lower development cost than Application-Specific Integrated Circuits (ASICs). While an ASIC can perform the same operations as an FPGA and is specific to the application, it cannot be reprogrammed.

- FPGAs have a faster time-to-market and lower non-recurring engineering (NRE) cost than ASICs.

- Throughput: it refers to the amount of data that is processed per clock cycle (bits/second).

- Latency: it refers to the time between data input and processed data output (clock cycles).

- Timing: it refers to the logic delays between sequential elements (frequency).

2.2. Inverse and Ill-Posed Problems

- For each a solution to the problem exists.

- For each a solution to the problem is unique.

- The solution x to the problem continuously depends on the initial data y.

2.3. Algorithm Implementation in FPGA

3. Stable source identification algorithm

3.1. Mathematical model

3.2. Forward problem

3.3. Stable algorithm for the inverse source problem

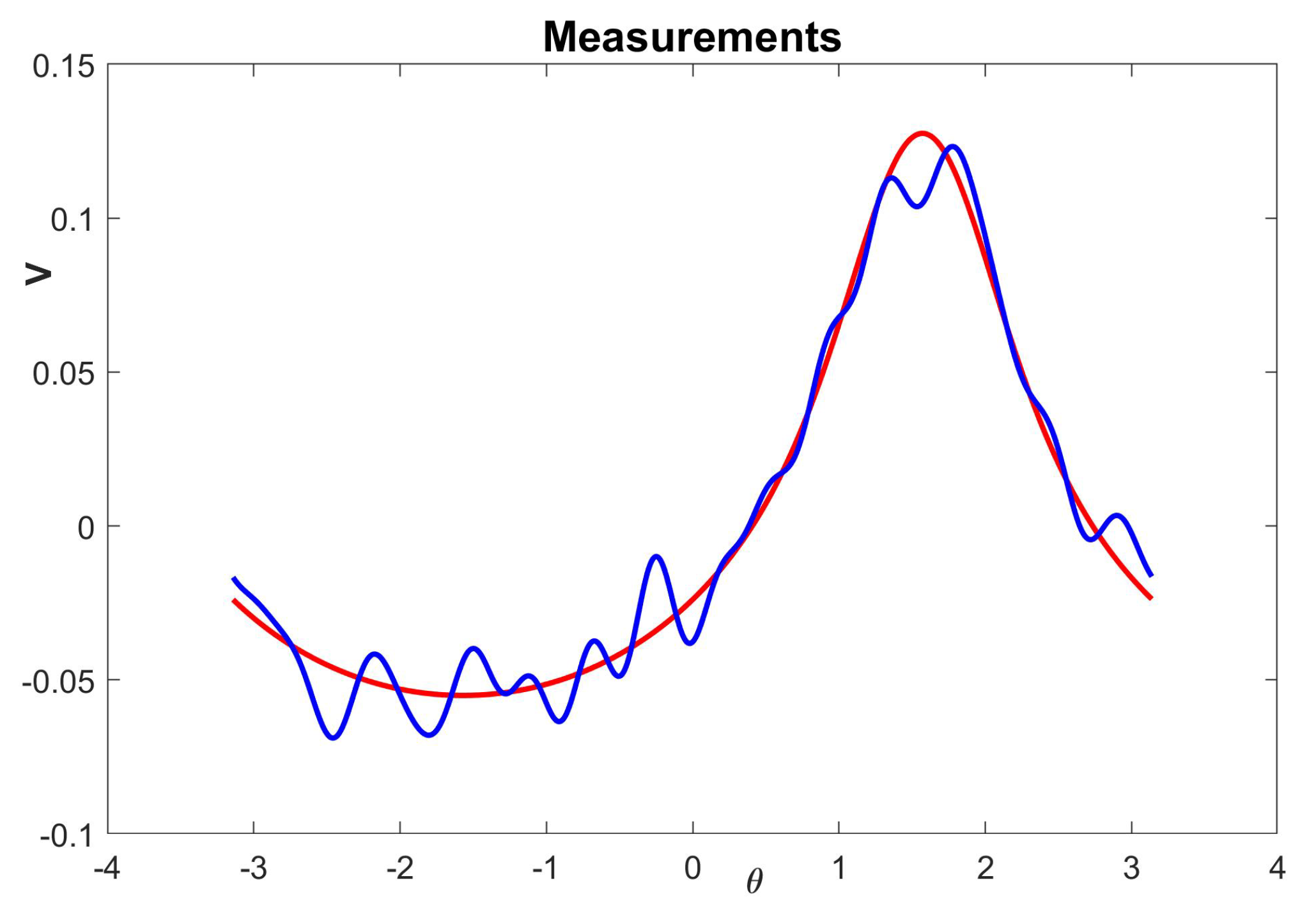

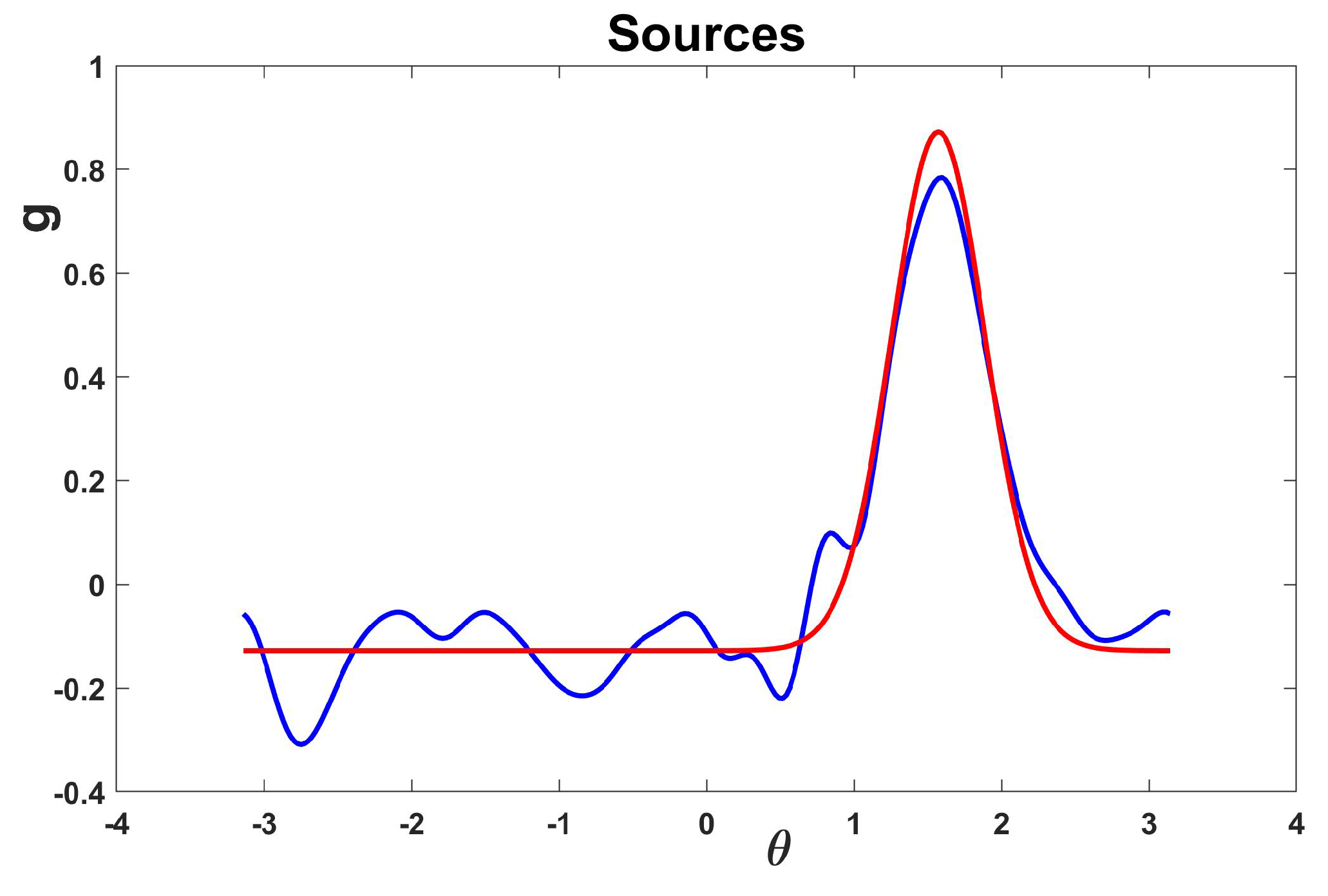

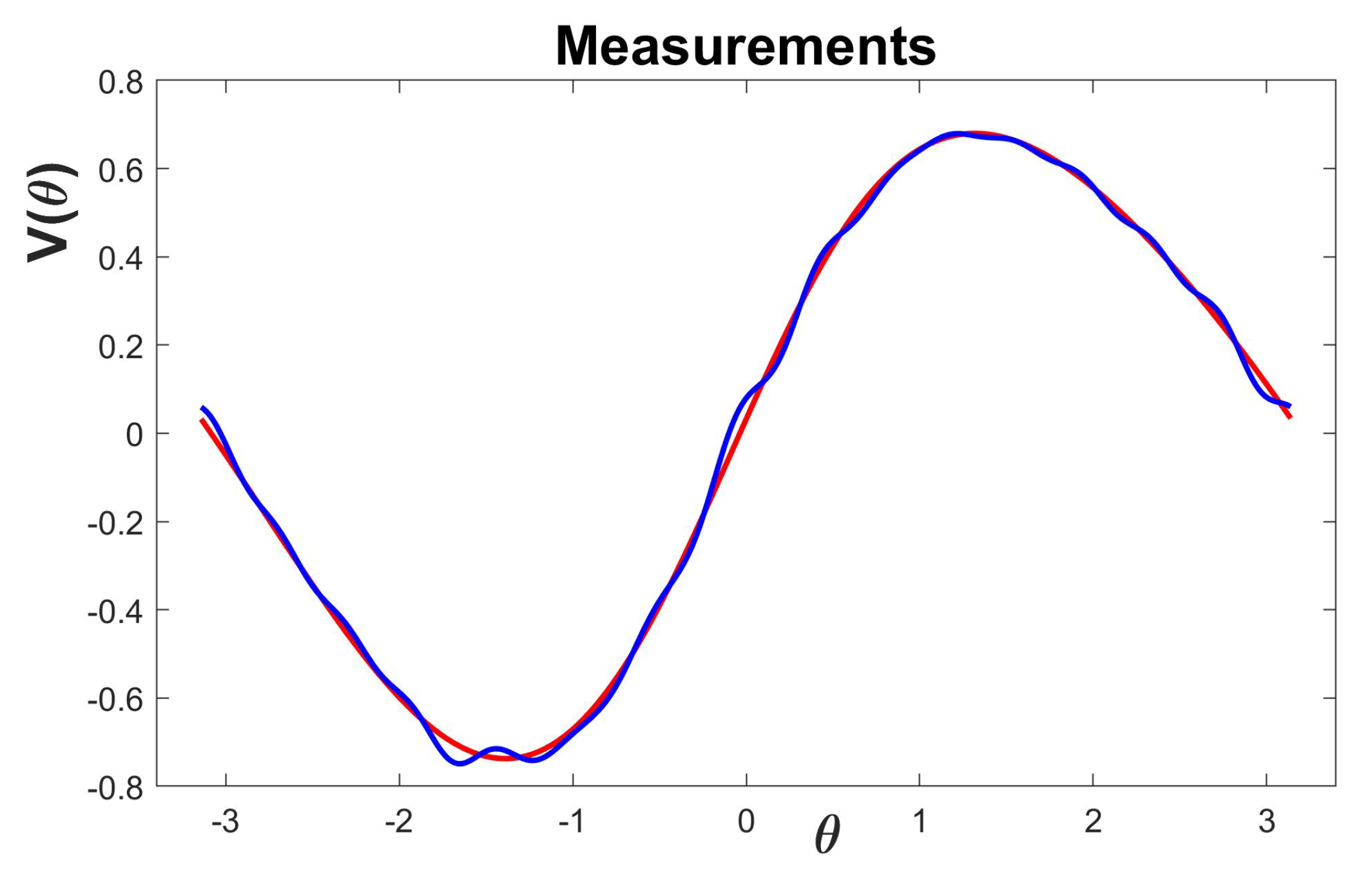

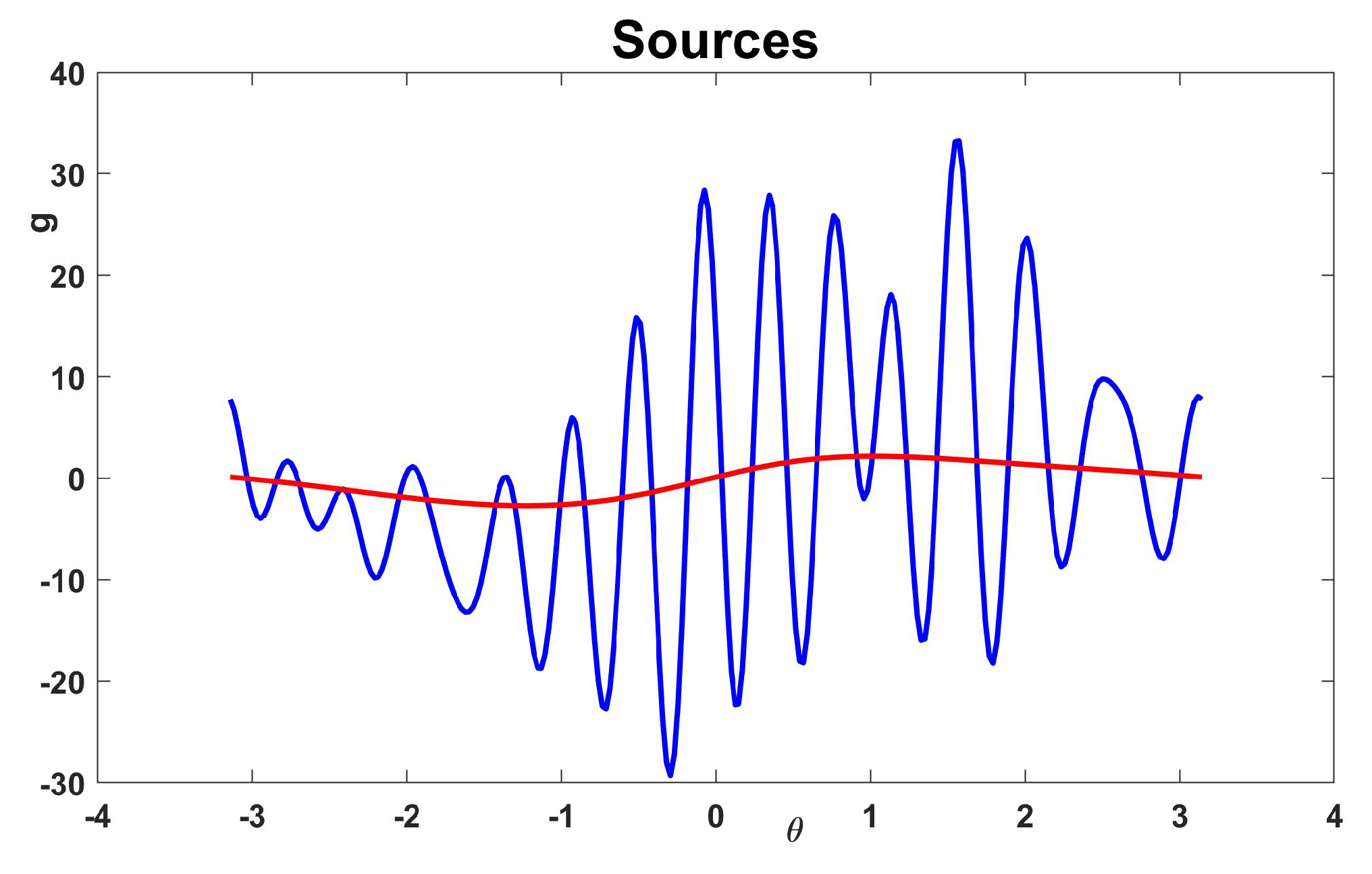

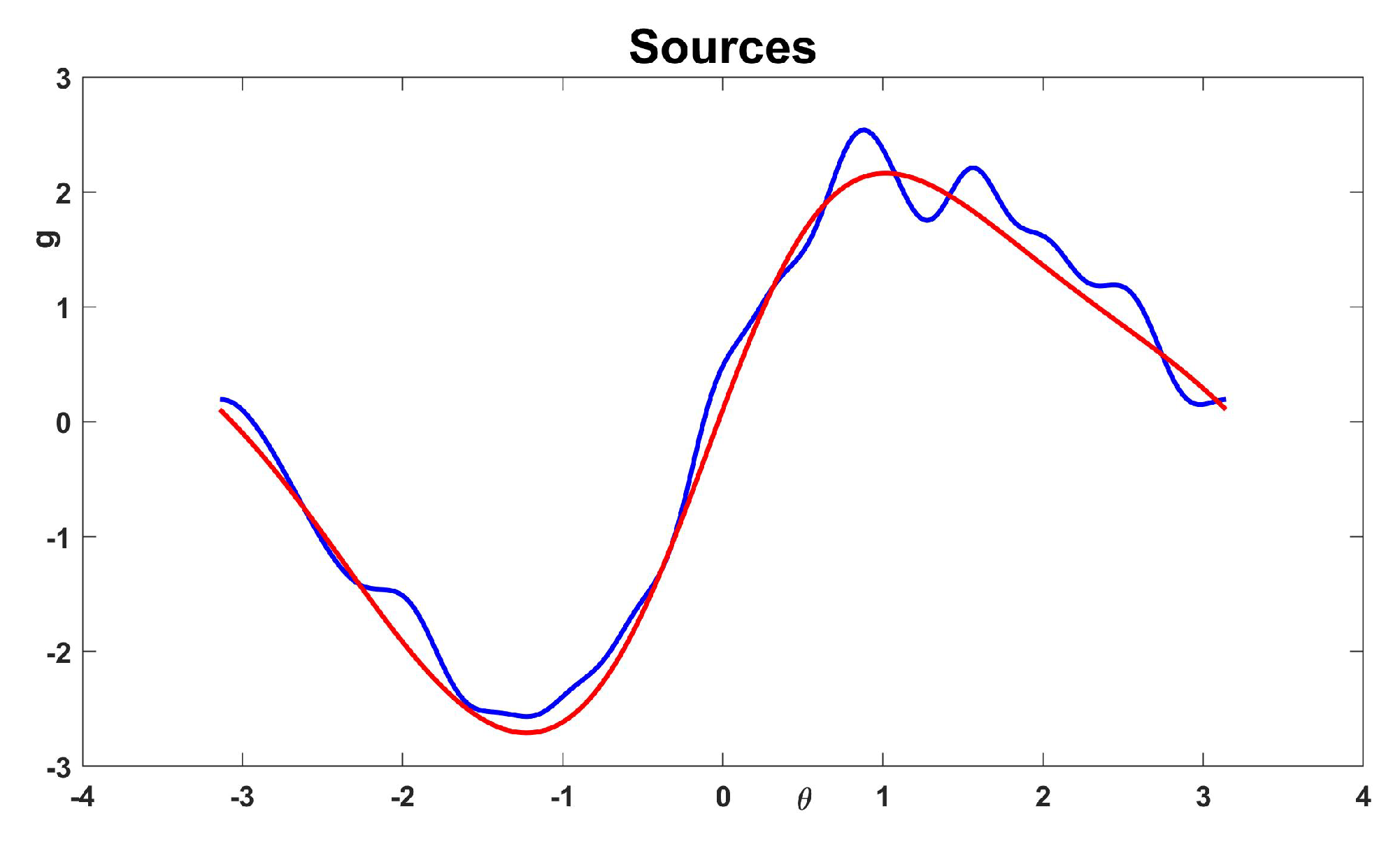

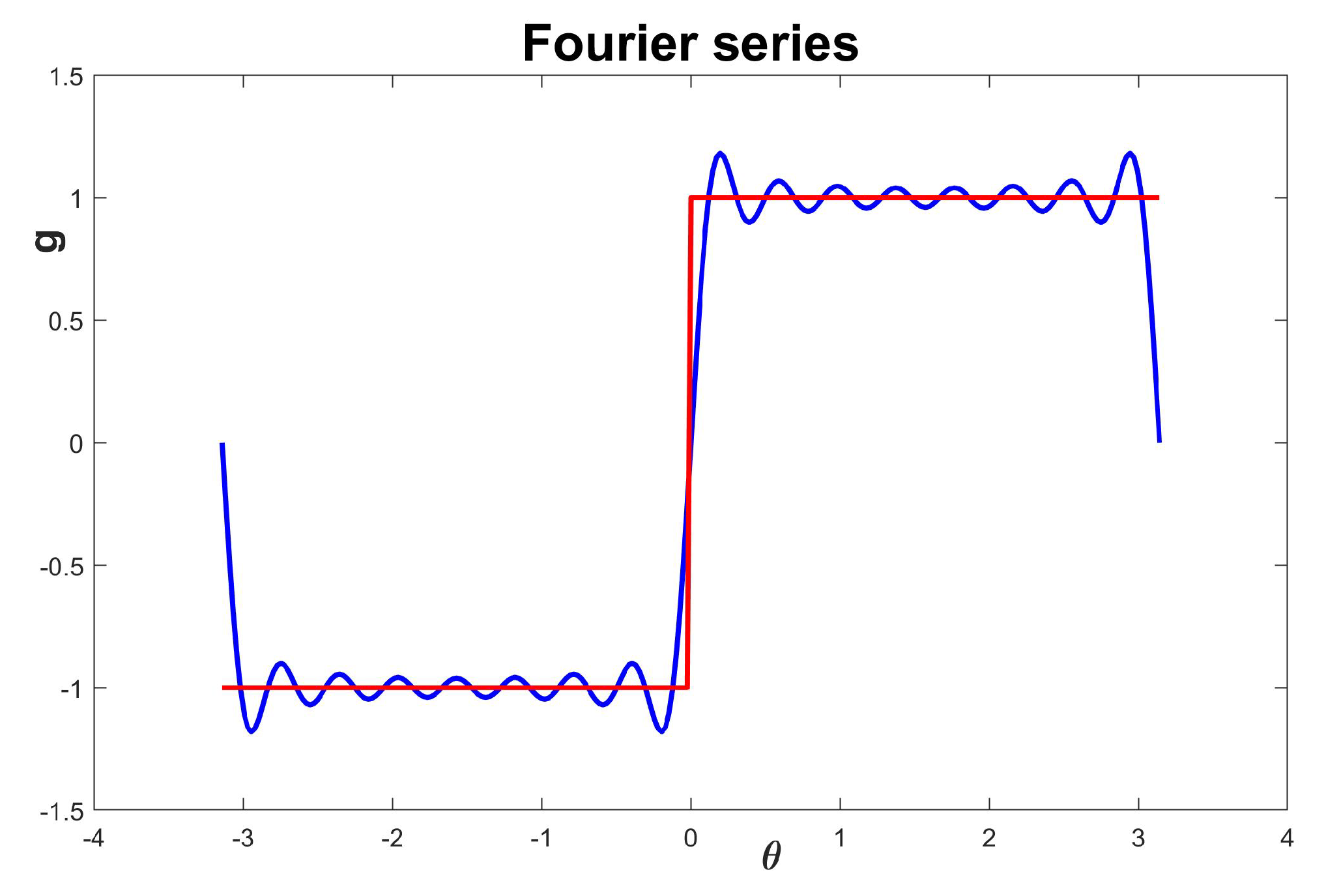

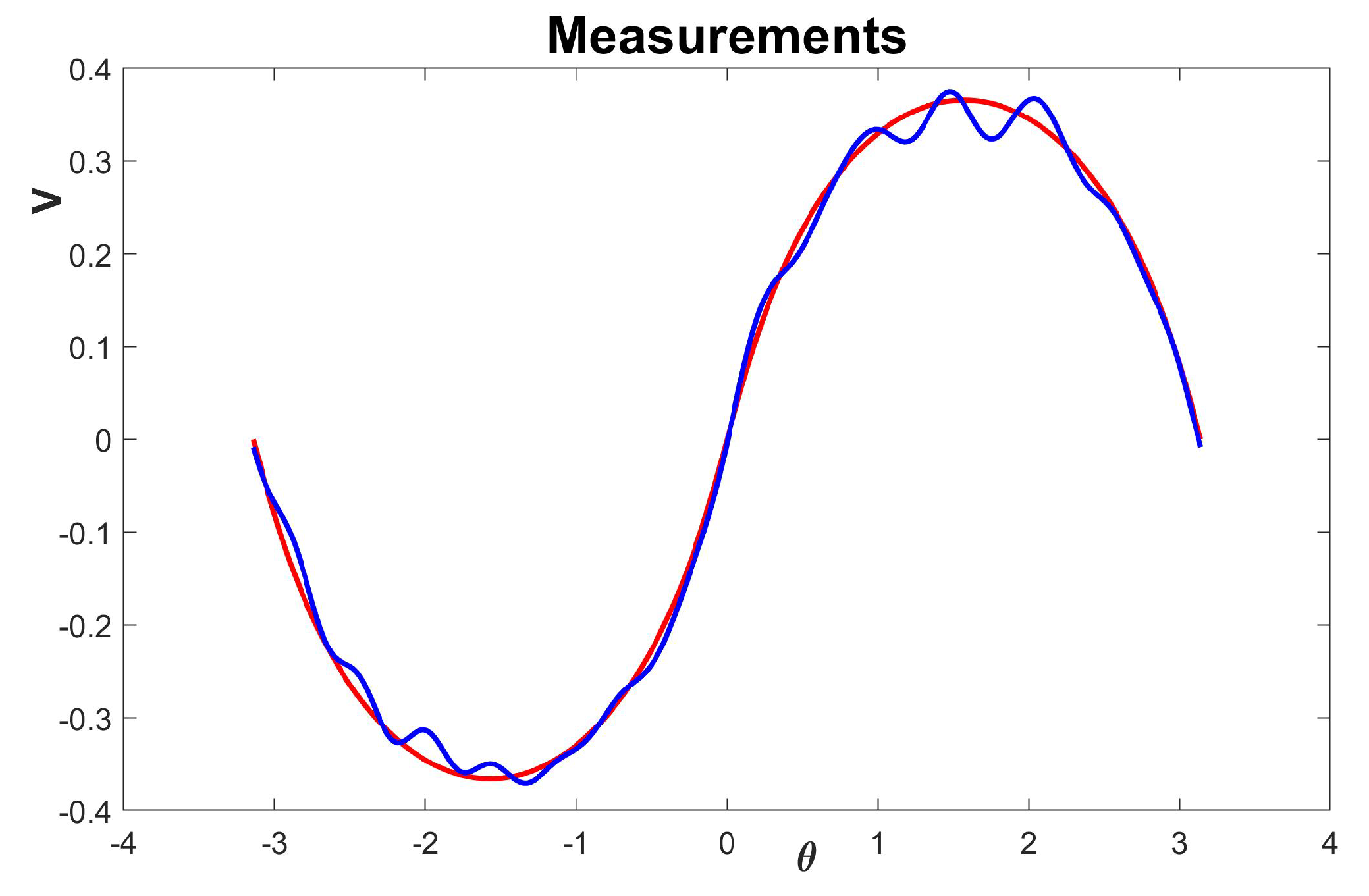

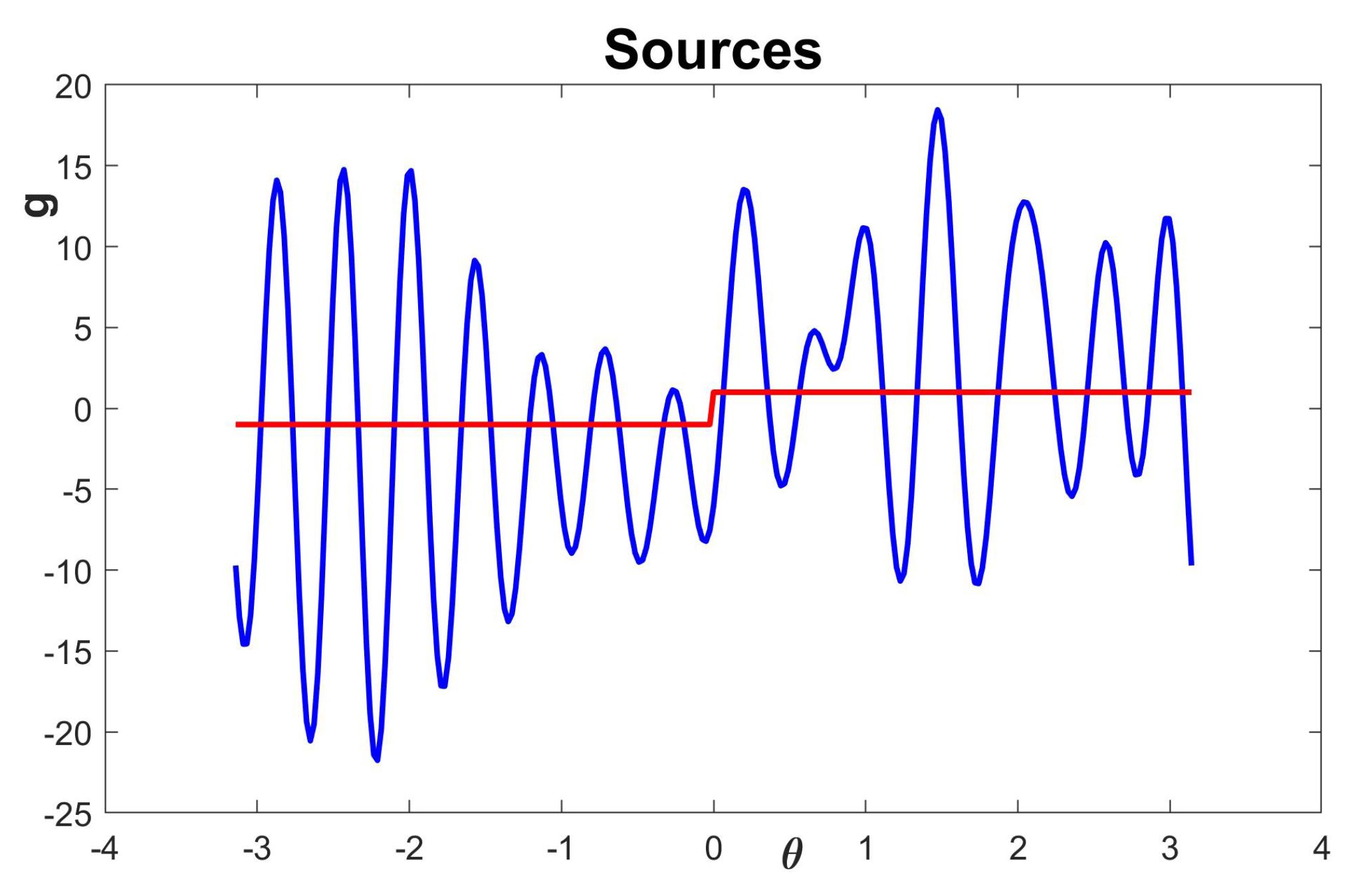

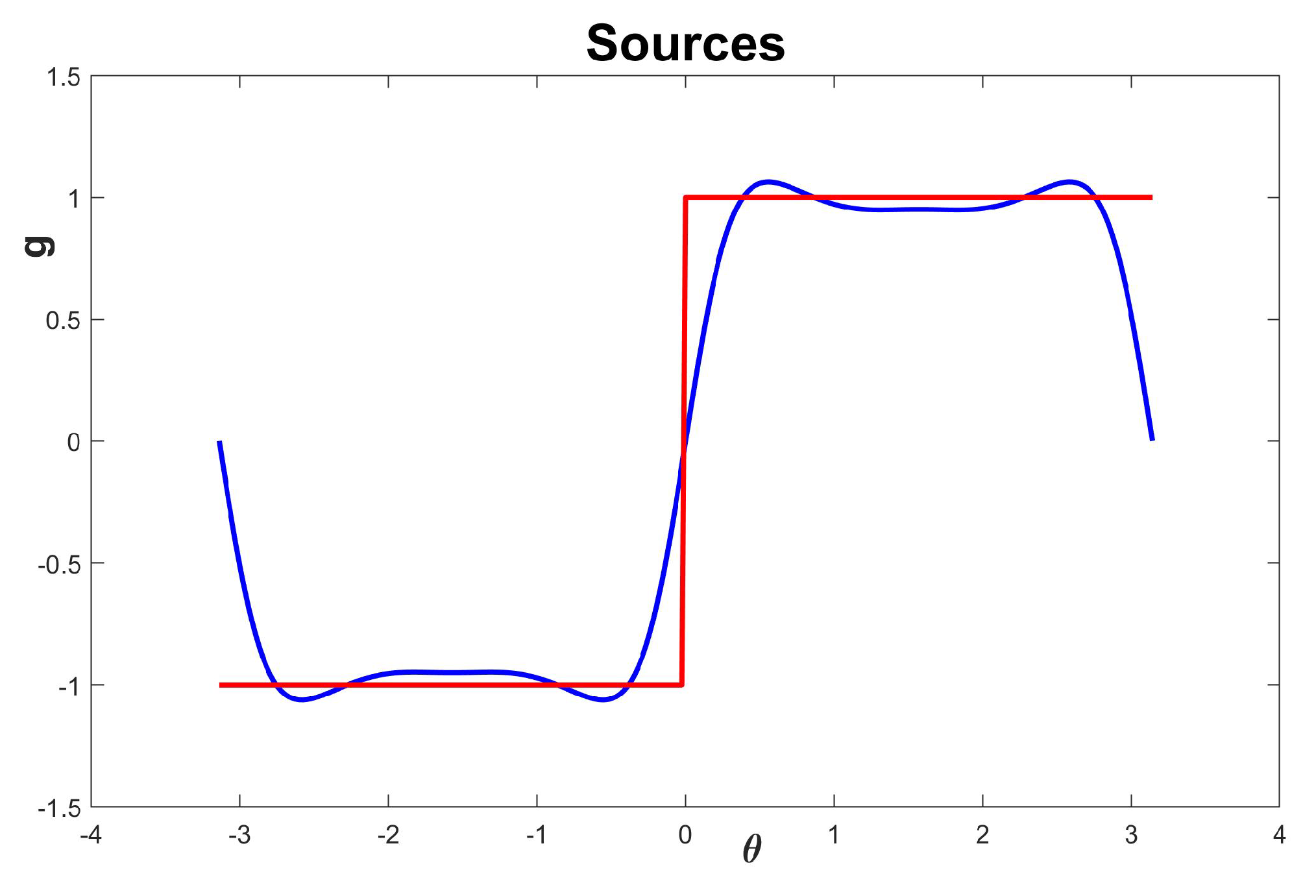

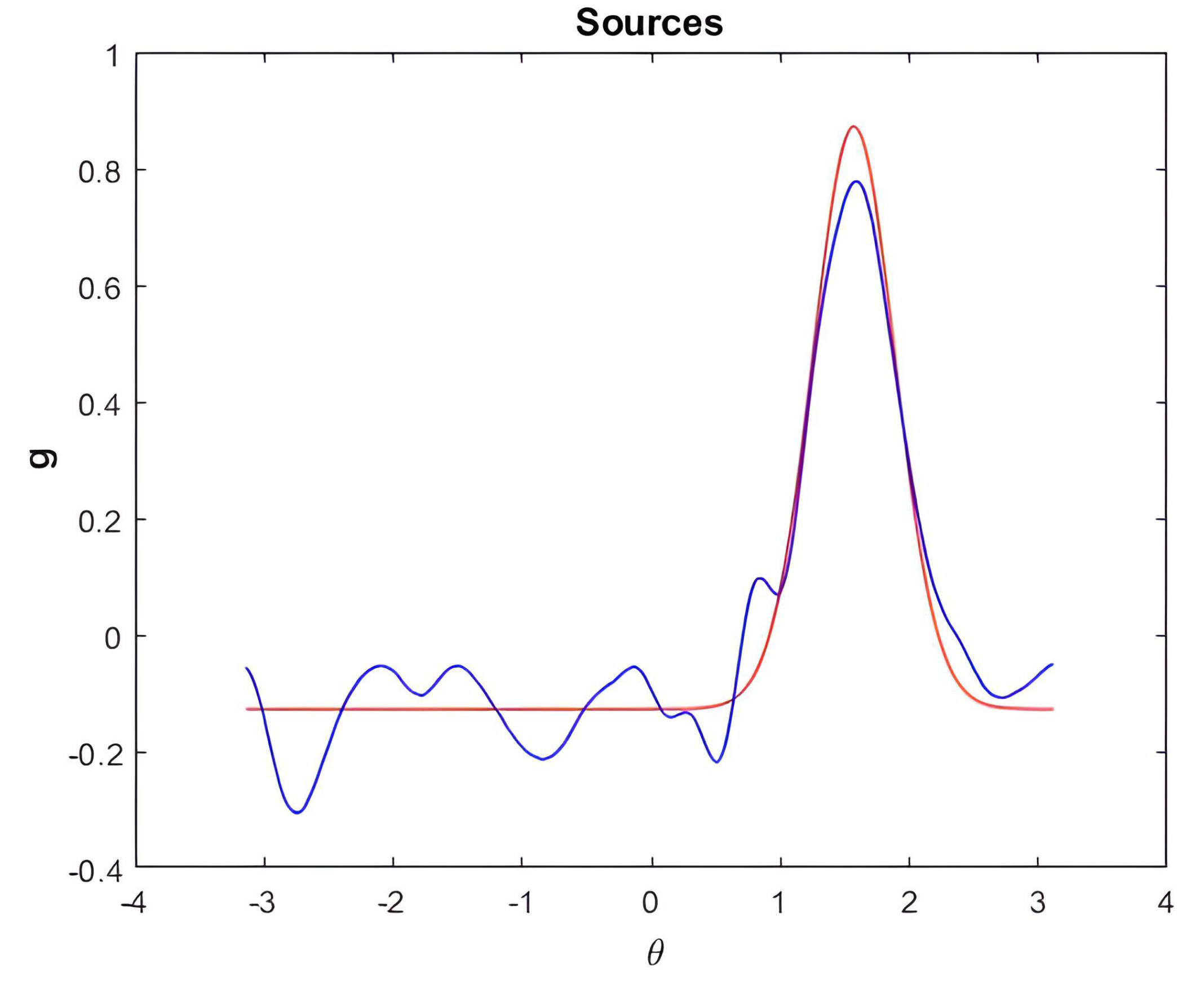

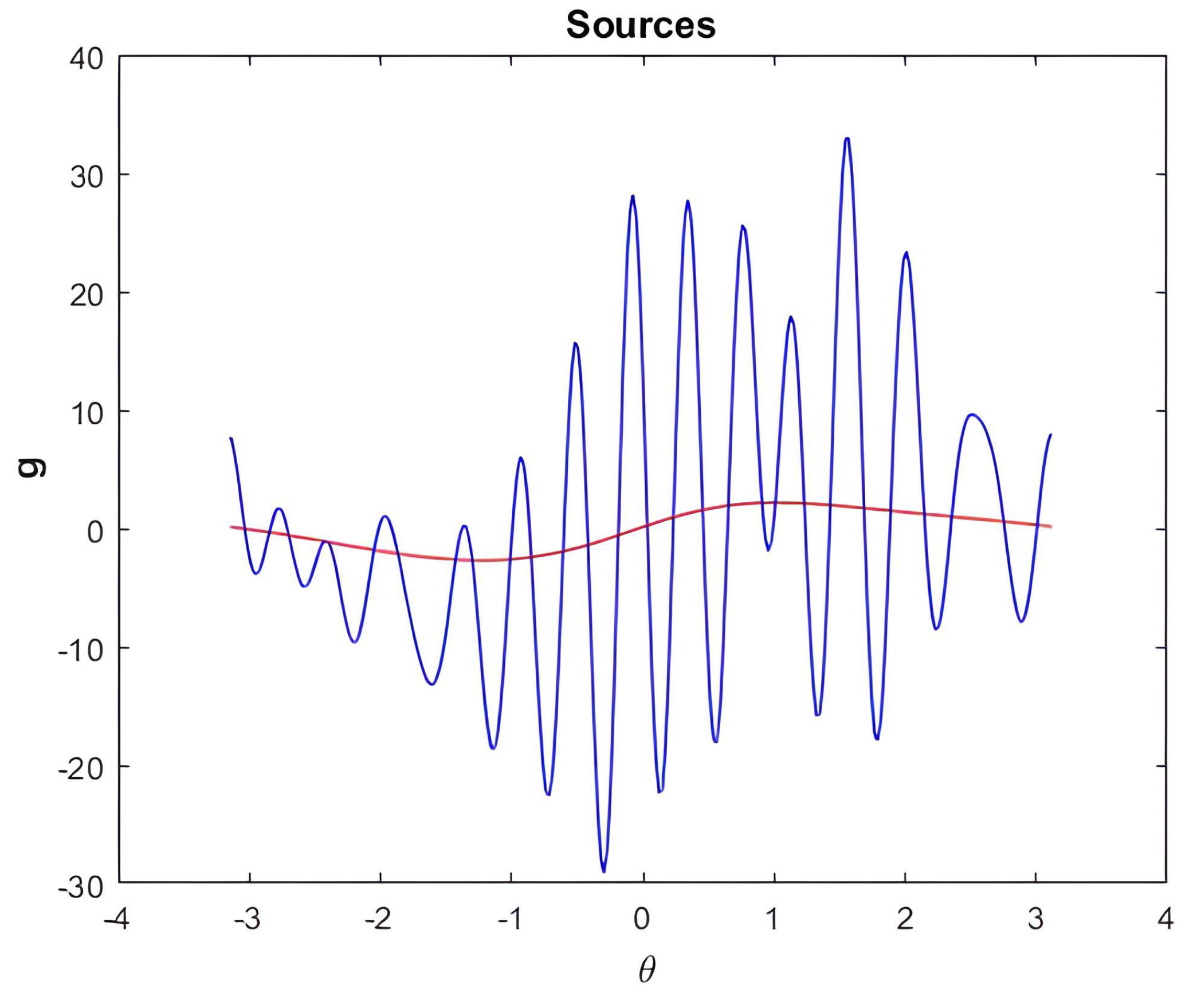

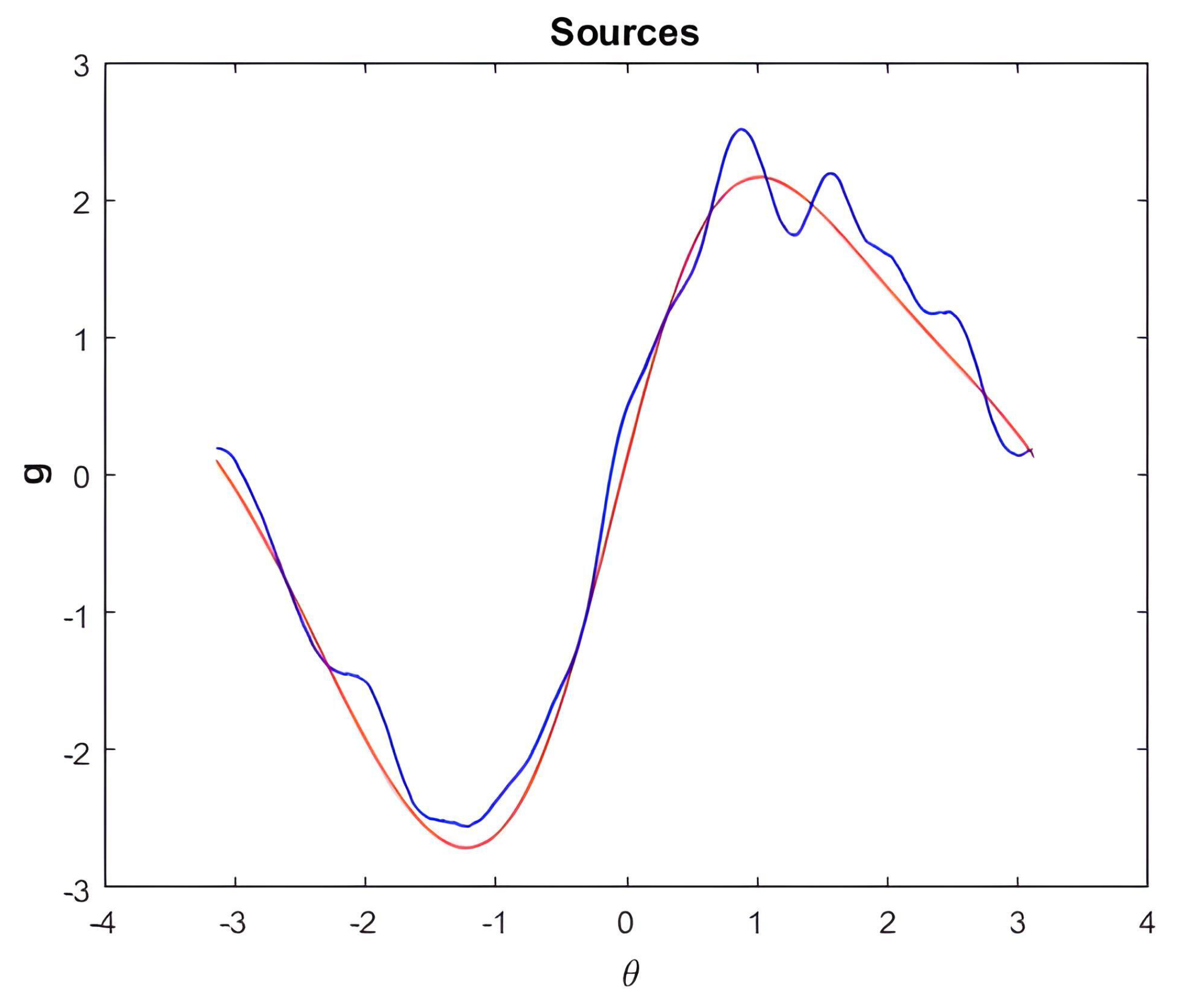

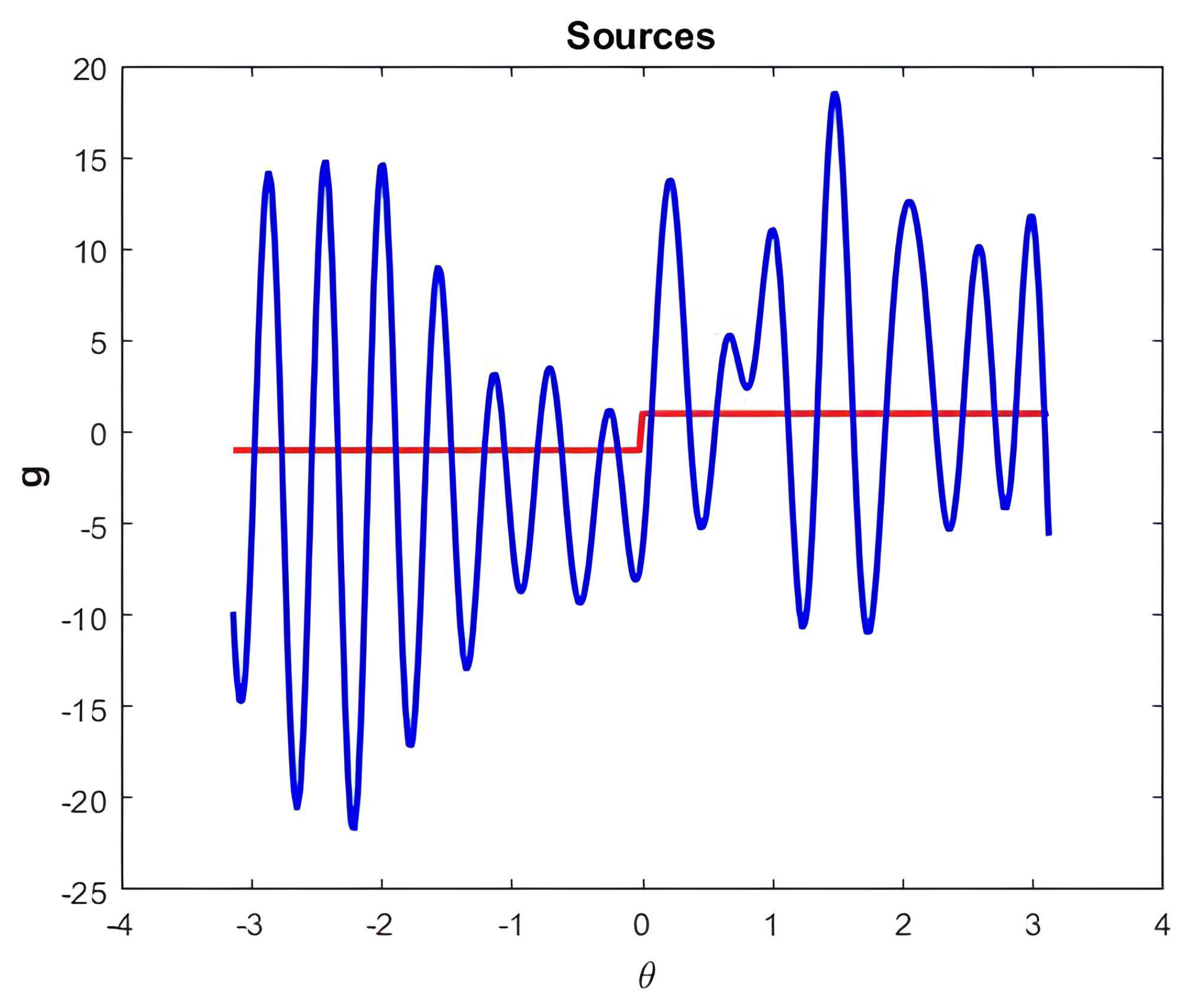

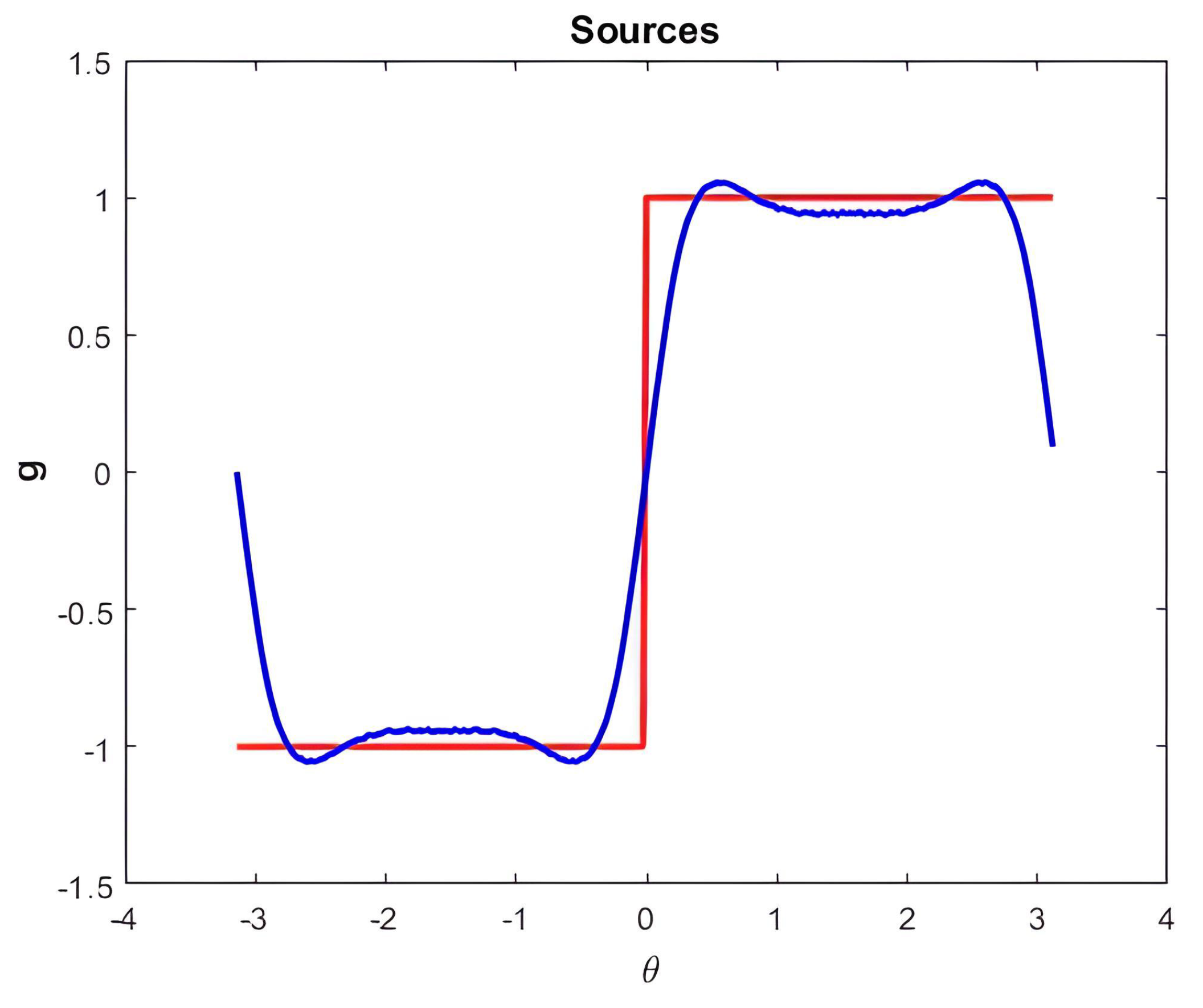

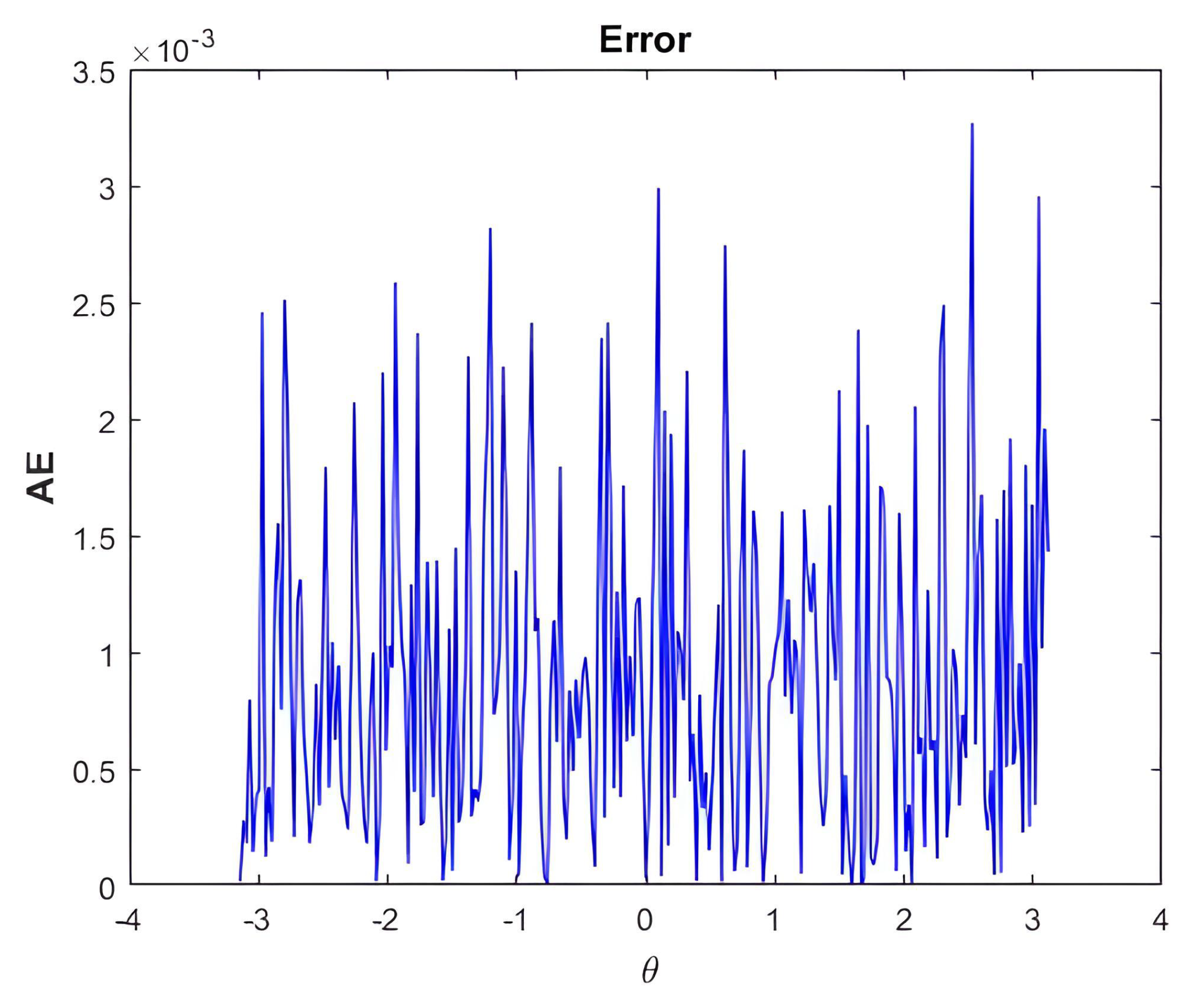

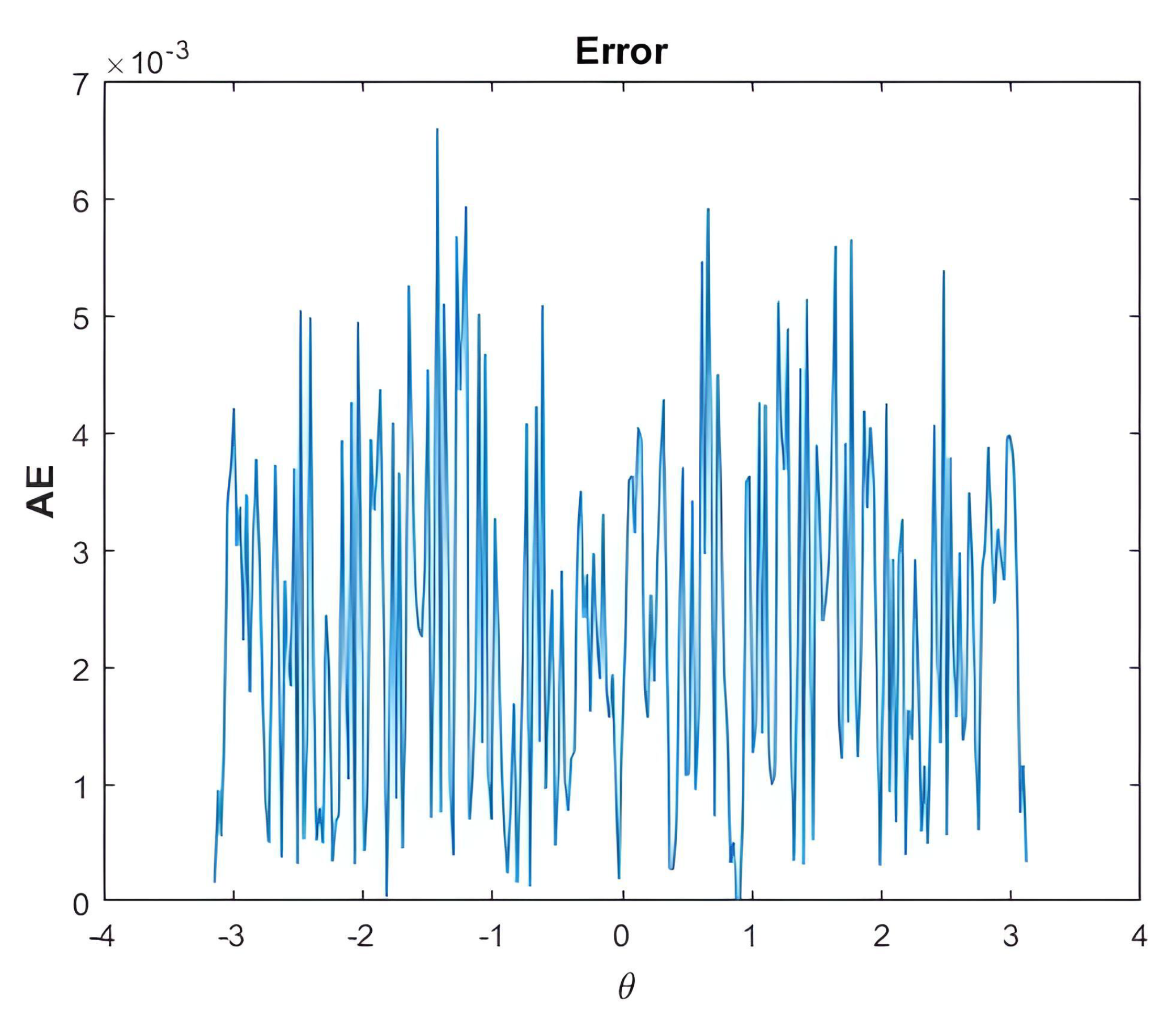

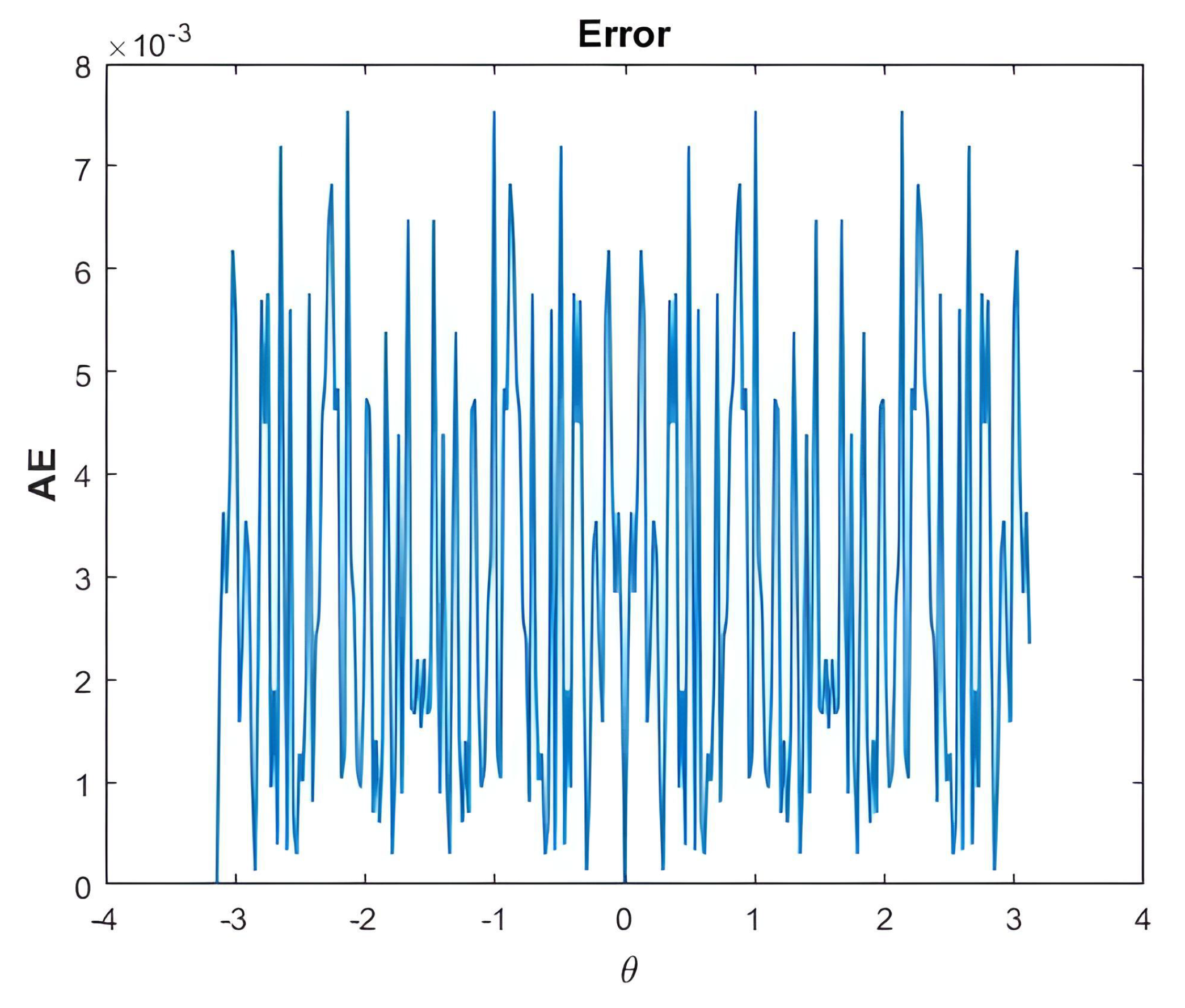

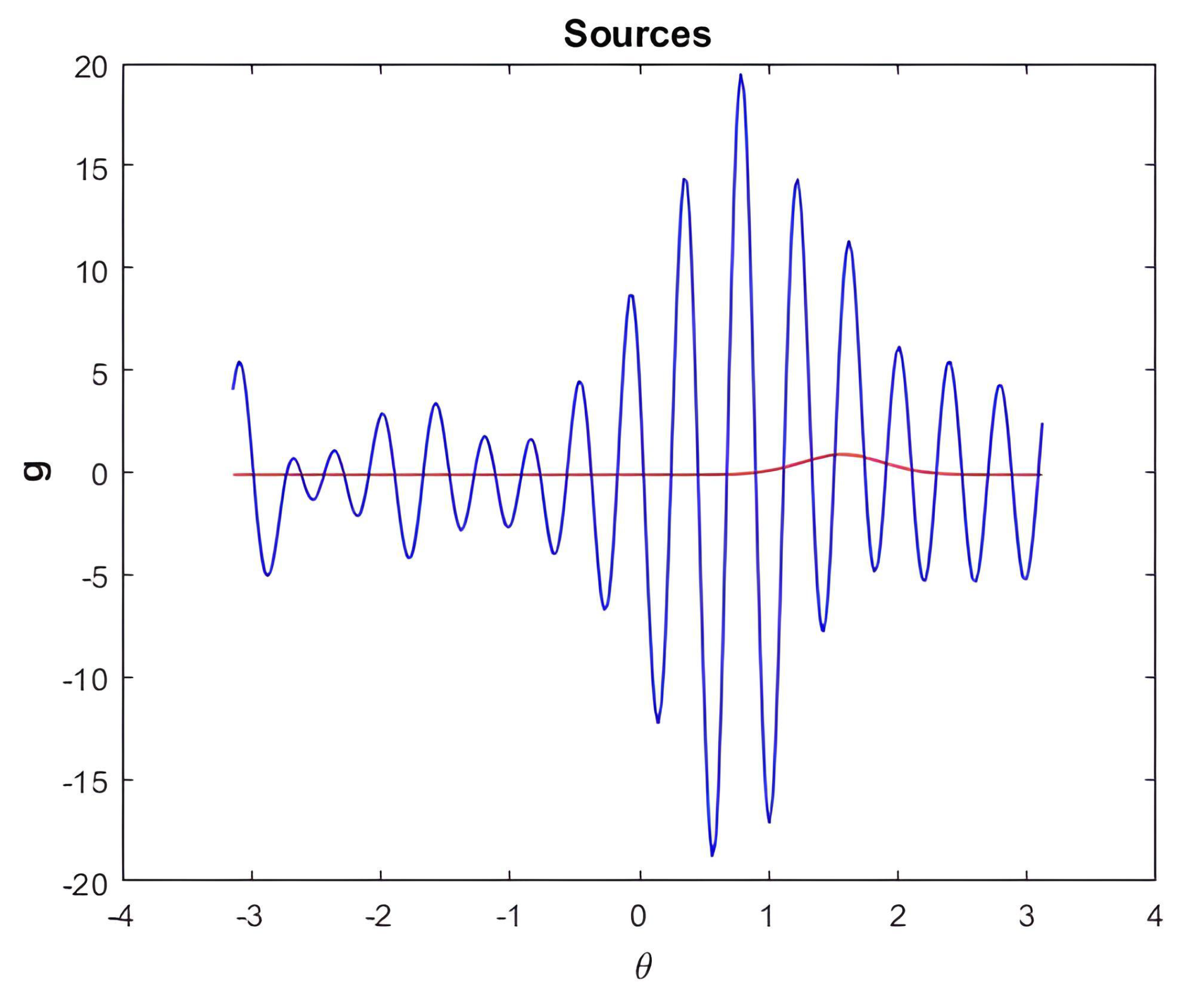

4. Numerical examples: MATLAB implementation

- We took some values for parameters , , , and , and defined a source g on .

- We solved the boundary value problem (1)-(5).

- We computed the exact measurement , using Eq. (8) for , which was chosen by numerical tests.

- To emulate the measurement (with error), we added an appropriate random error to the coefficients and , where , using the rand function of MATLAB. Hence, we obtained coefficients and , , of the measurement with error , which satisfies .

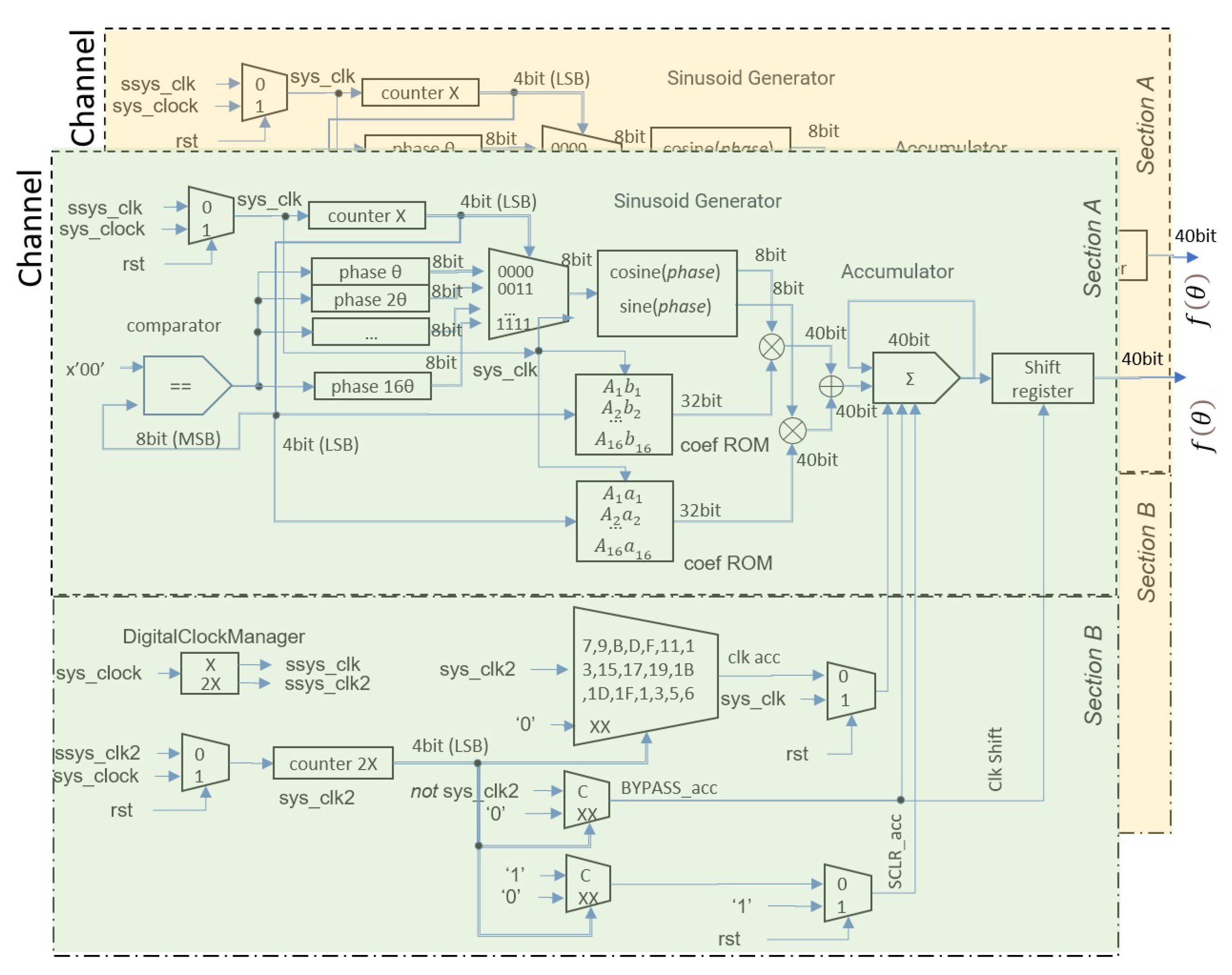

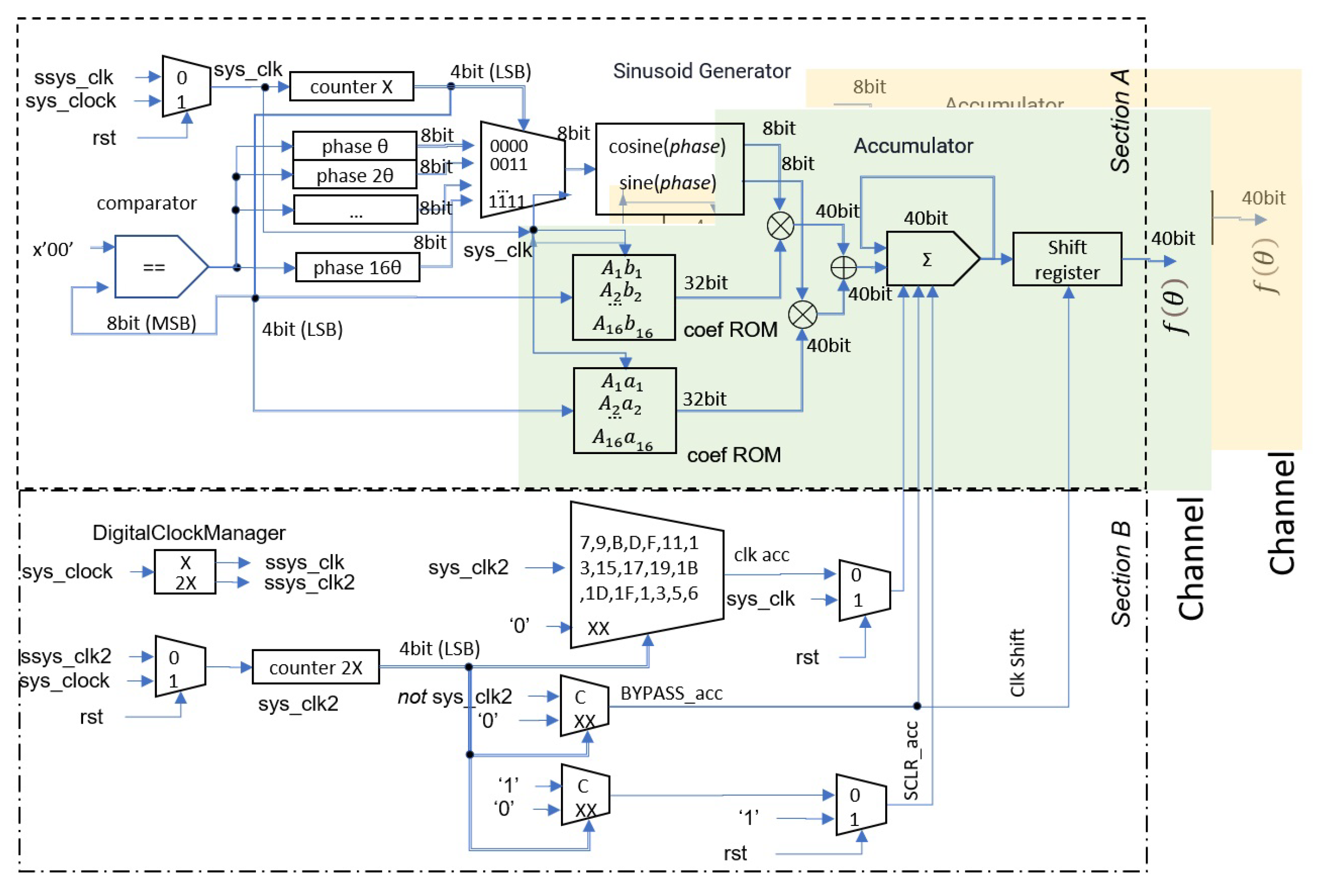

5. FPGA implementation

- Perform the products and . The two’s complement format is chosen for the number representation, as the algorithm involves signed arithmetic operations.

- Sum the results from the previous step.

- Temporarily store the result.

- Perform the products , and add them to the temporary result.

- Repeat the process until term .

- A double memory block ROM to store the coefficients y .

- A DDS Xilinx module (see [17]) to generate the values of and for .

- Multiplexers to maintain synchrony in the Control Section.

5.1. Architecture description

- Section A: This section contains the arithmetic operations.

- Section B: This section contains the control of the operations in Section A, which synchronizes the pipeline operations.

- The trigonometric base.

- Linear combination of the elements of the base.

- Control module.

- Acts as an 8-bit selector control in the 16-to-1 multiplexer.

- Increments the consecutive value from 1 to 16 in resolution.

- Synchronizes the addressing and reading of the ROM memory.

- A two-cycle latency for the DDS module to reflect the sine and cosine values on the data bus and for the memory ROM module to reflect the coefficients simultaneously on the data bus. Both modules work in parallel.

- A one-cycle latency for each operation (product and sum). Those operations are performed in series.

- A one-cycle latency to store the result in the accumulator.

- A latency of 16 cycles to obtain .

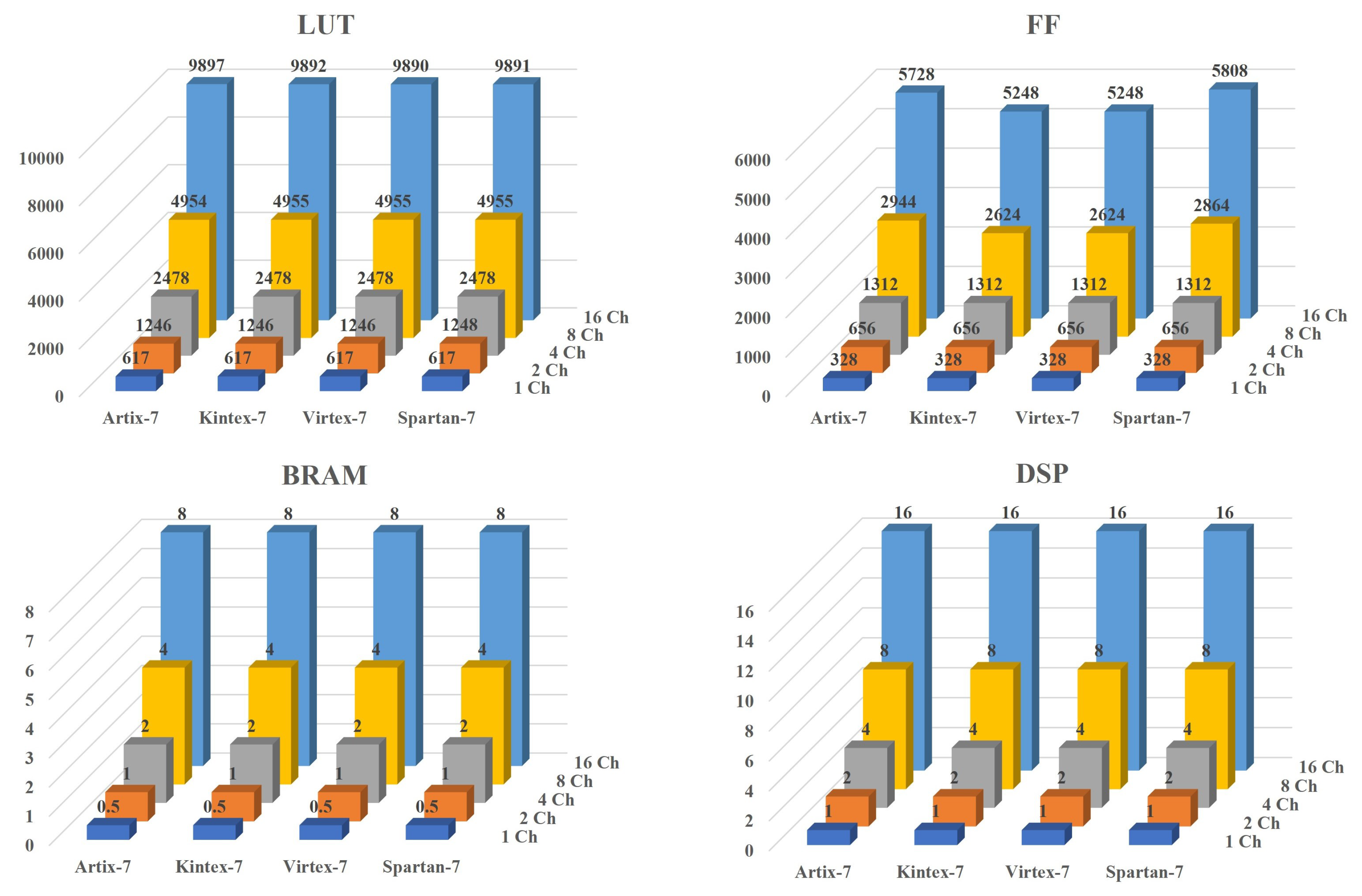

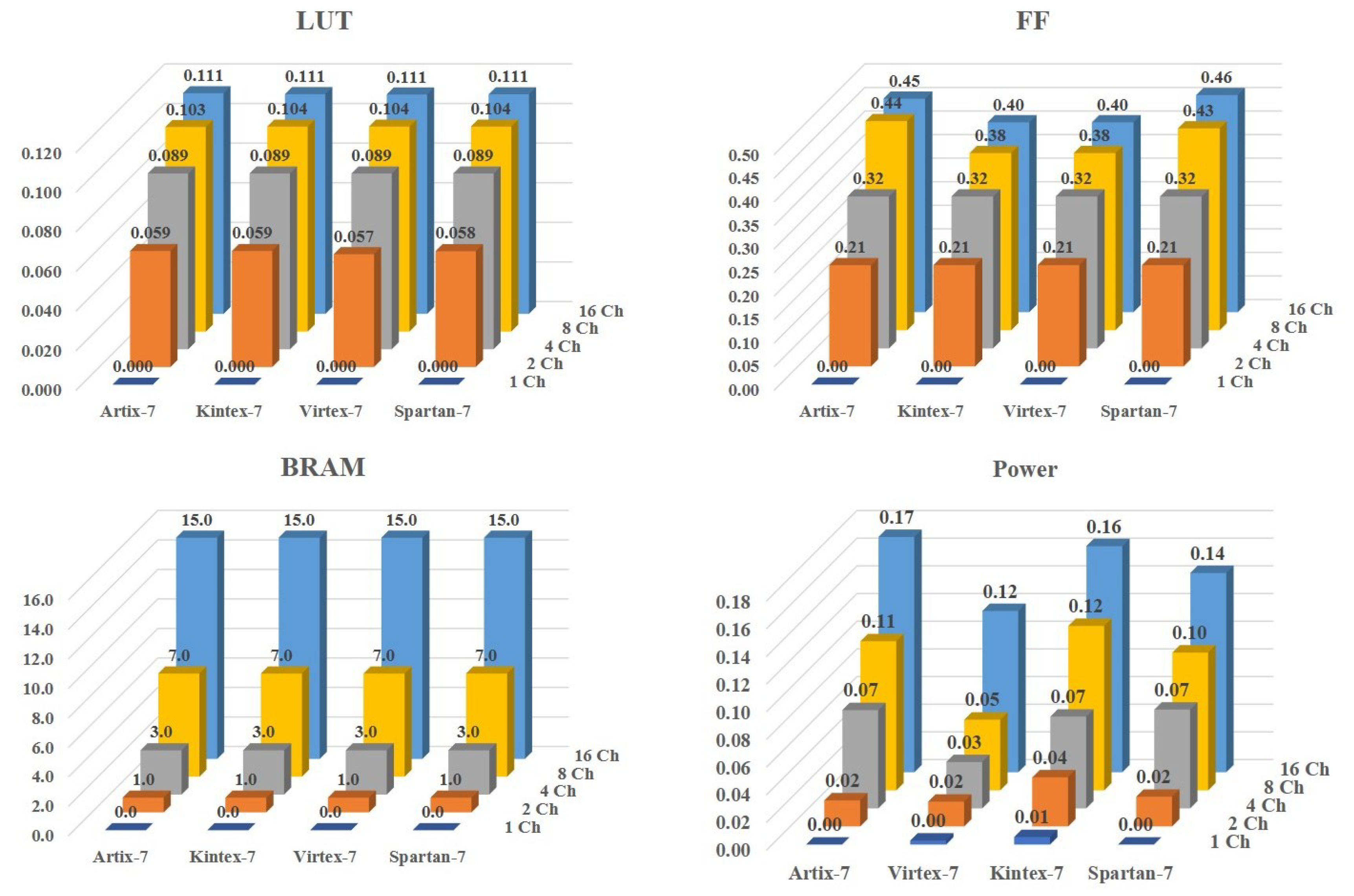

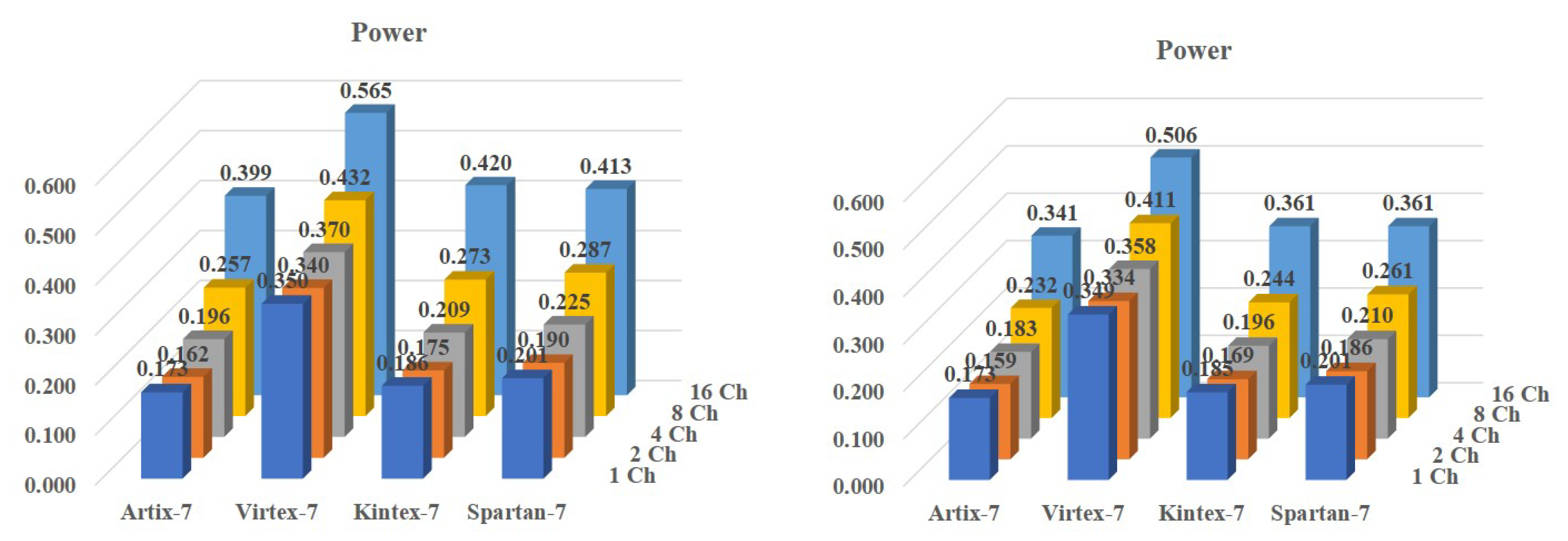

5.2. Resource description

- LUTs (Lookup Tables): These contain the logical elements that determine the output from one or multiple inputs. They are essentially truth tables created from the description of the VHDL program.

- FFs (Flip Flops): Sequential logical elements with one bit of memory.

- RAM blocks: Each block has a storage capacity of 32 K-bit.

- DSP blocks: Specialized blocks for product, sum, and accumulation operations for signed numbers in two’s complement format. These operations are called: multiply-accumulate (MAC).

- Power consumption: Determines the energy consumption of the system.

6. Validation of the hardware implementation

7. Discussion

8. Conclusion

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Xilinx, 7 Series FPGAs Data Sheet: Overview, DS180 (v2.6.1), 8 September 2020. Available online: https://docs.xilinx.com/v/u/en-US/ds180_7Series_Overview (accessed on 10 April 2023).

- Morín-Castillo, M.M.; Netzahualcoyotl-Bautista, C.; Conde-Mones, J.J.; Oliveros-Oliveros, J.J.; Santillán-Guzmán, A. Stable identification of sources associated with epileptic focus on the cerebral cortex, Rev. Mex. Ing. Biomed. 2019, 40, 1–14. [Google Scholar]

- Morín-Castillo, M.M.; Arriaga-Hernández, J.; Cuevas-Otahola, B.; Oliveros-Oliveros, J.J. Analysis of Dipolar Sources in the Solution of the Electroencephalographic Inverse Problem. Mathematics 2022, 10, 1–22. [Google Scholar] [CrossRef]

- Gockenbach, M.S. Linear inverse problems and Tikhonov regularization, The Carus Mathematical Monographs, 32, Publisher: The Mathematical Association of America, 2016.

- Kirsch, A. An Introduction to the mathematical theory of inverse problems, 2nd ed.; Vol 120, Publisher: Appl. Math. Sci., Springer, New York, 2011.

- Algredo-Badillo, I.; Conde-Mones, J.J.; Hernández-Gracidas, C.A.; Morín-Castillo, M.M.; Oliveros-Oliveros, J.J.; Feregrino-Uribe, C. An FPGA-based analysis of trade-offs in the presence of ill-conditioning and different precision levels in computations. PLoS One 2020, 15, 1–26. [Google Scholar] [CrossRef] [PubMed]

- Morín, M.M.; Netzahualcoyotl, C.; Oliveros, J.J.; Conde, J.J.; Juárez, H. Stable identification of sources located on separation interfaces of two different homogeneous media, Adv. Differ. Equ. Control Process. 2019, 20(1), 53–97. [Google Scholar]

- Hennessy, J.L.; Patterson D.A. Computer architecture: a quantitative approach; 5th ed.; Publisher: Elsevier, 2011.

- lsuwailemo, A.M. Real-time FPGA-based Image Enhancement Using Histogram Projection Technique for Uncooled Infrared Imagers, J. King Saud Univ., Eng. Sci., 2007, 21, 15–22. [Google Scholar] [CrossRef]

- Nayak, M.R.; Bag, J.; Sarkar, S.; Sarkar, S.K. Hardware implementation of a novel water marking algorithm based on phase congruency and singular value decomposition technique, Int. J. Electron. Commun. 2017, 71, 1–8. [Google Scholar] [CrossRef]

- Saric, R.; Jokic, D.; Pokvic, L.G.; Badnjecvic, A. FPGA-based real-time epileptic seizure classification using Artificial Neural Network. Biomed. Signal Process. Control 2020, 62, 1–10. [Google Scholar] [CrossRef]

- Conde Mones, J.J.; Estrada Aguayo, E.R.; Oliveros Oliveros, J.J.; Hernández Gracidas, C.A.; Morín Castillo, M.M. Stable Identification of Sources Located on Interface of Nonhomogeneous Media. Mathematics 2021, 9, 1–23. [Google Scholar] [CrossRef]

- Arias-Cruz, J.A.; Morín-Castillo, M.M.; Oliveros-Oliveros, J.J.; and Gutiérrez-Arias, J.E. Stable identification of sources located on the cerebral cortex from EEG over the scalp, Rev. Mex. Fis. 2023, 69, 1–8. [Google Scholar] [CrossRef]

- Badia, E.A.; Duong, T.H. Some remarks on the problem of source identification from boundary measurements. Inverse Probl. 1998, 14, 883–891. [Google Scholar] [CrossRef]

- Harize, S.; Benouaret, M.; Doghmane, N. A methodology for implementing decimator FIR filters on FPGA, Int. J. Electron. Commun. 2013, 67(12), 993–1004. [Google Scholar] [CrossRef]

- Hansen, P.H. The L-curve and its use in the numerical treatment of inverse problems. In Computational Inverse Problems in Electrocardiography, P. Johnston (Ed.), WIT Press, Southampton, 2001, pp. 119–142.

- Xilinx, DDS Compiler v6.0, PG141, 21 January 2021. Available online: https://docs.xilinx.com/v/u/en-US/pg141-dds-compiler (accessed on 10 April 2023).

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).