Submitted:

07 June 2023

Posted:

08 June 2023

You are already at the latest version

Abstract

Keywords:

1. Introduction

2. Retimer Circuit Latency and Jitter Performance Analysis

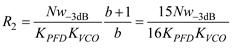

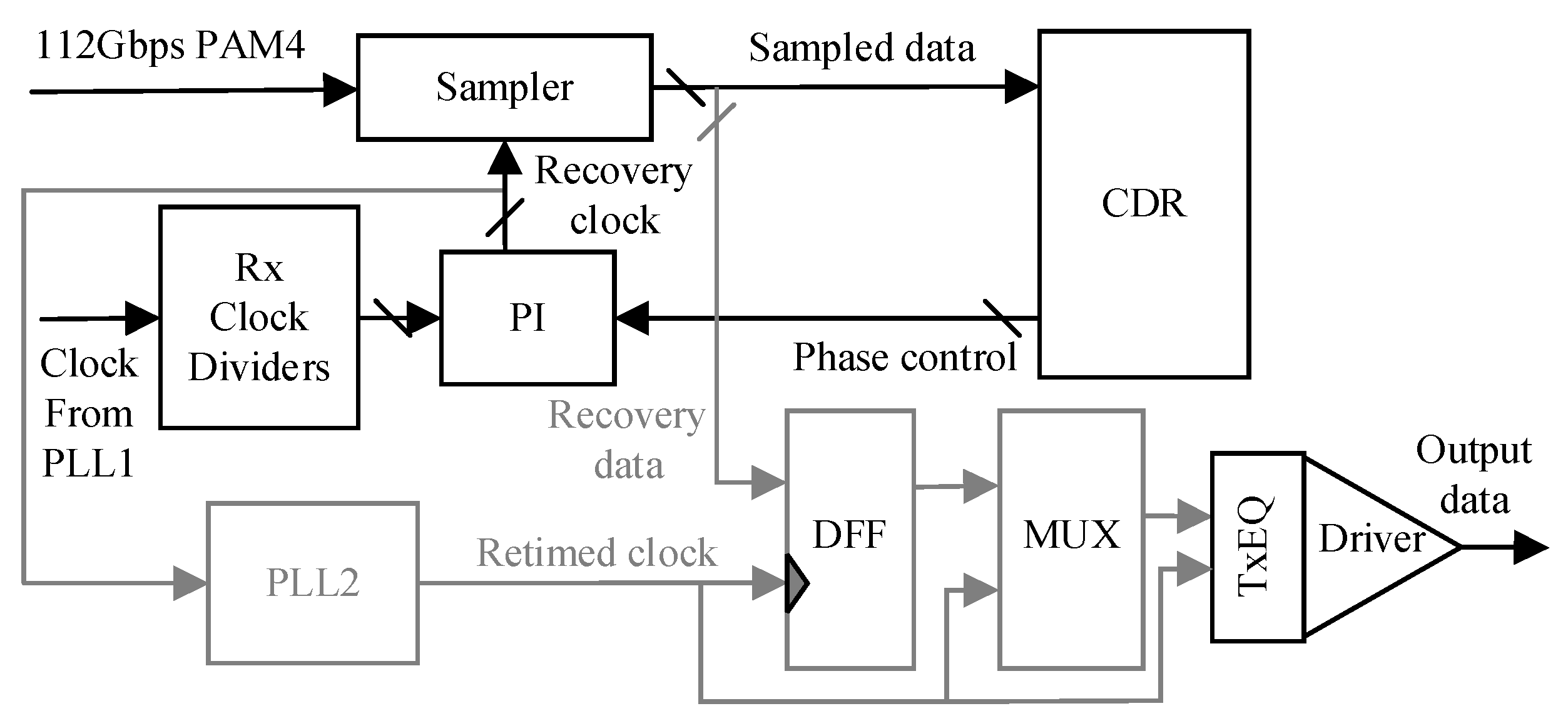

3. The Retimer Circuit Architecture Proposed in This paper

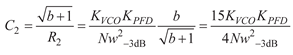

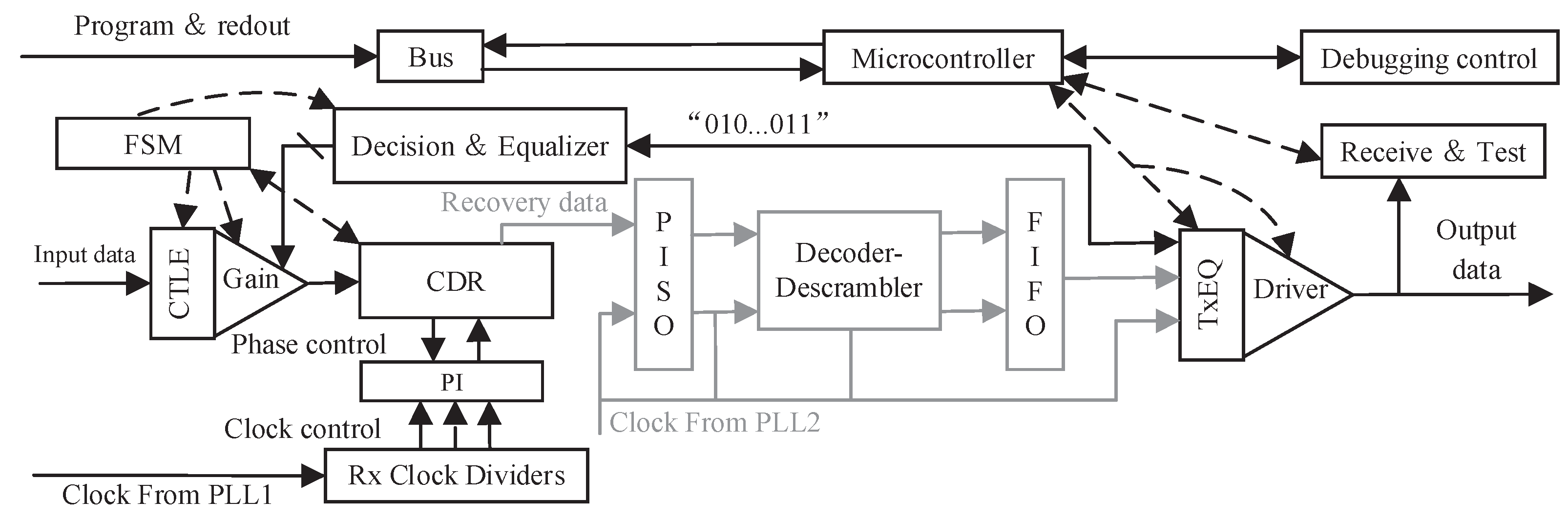

3.1. Low Delay Low Jitter Retiemr Circuit Based on CDR+PLL Architecture

3.2. CDR Design

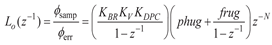

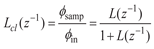

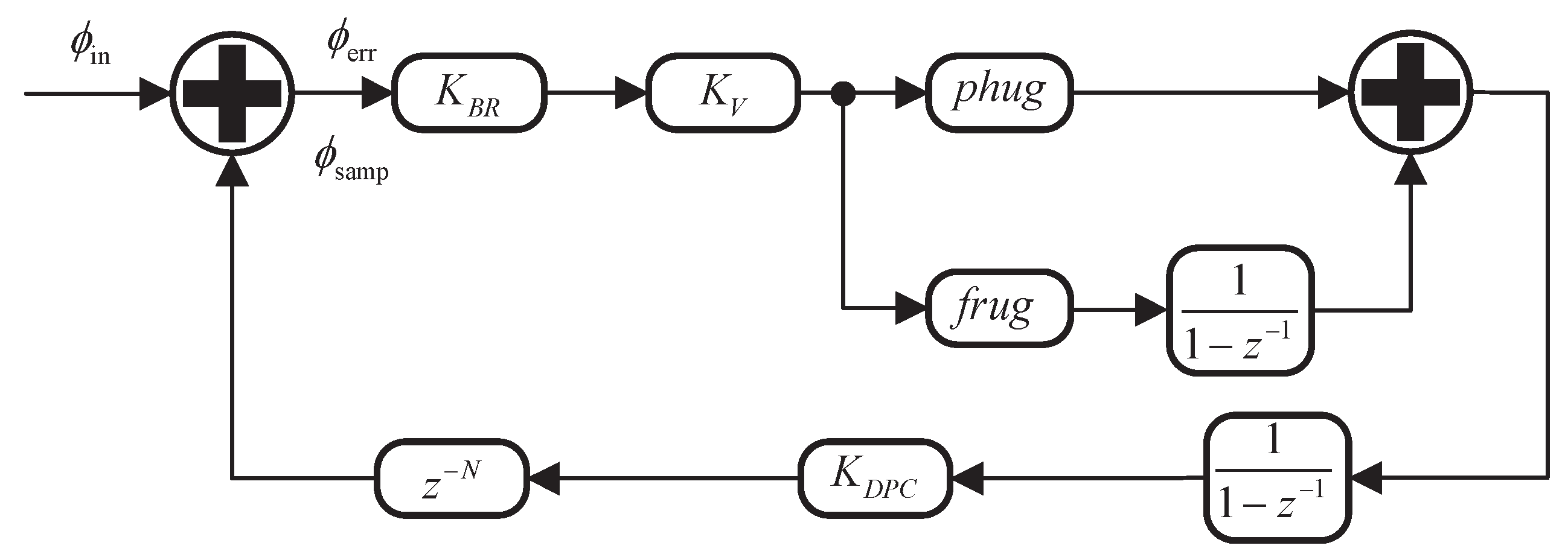

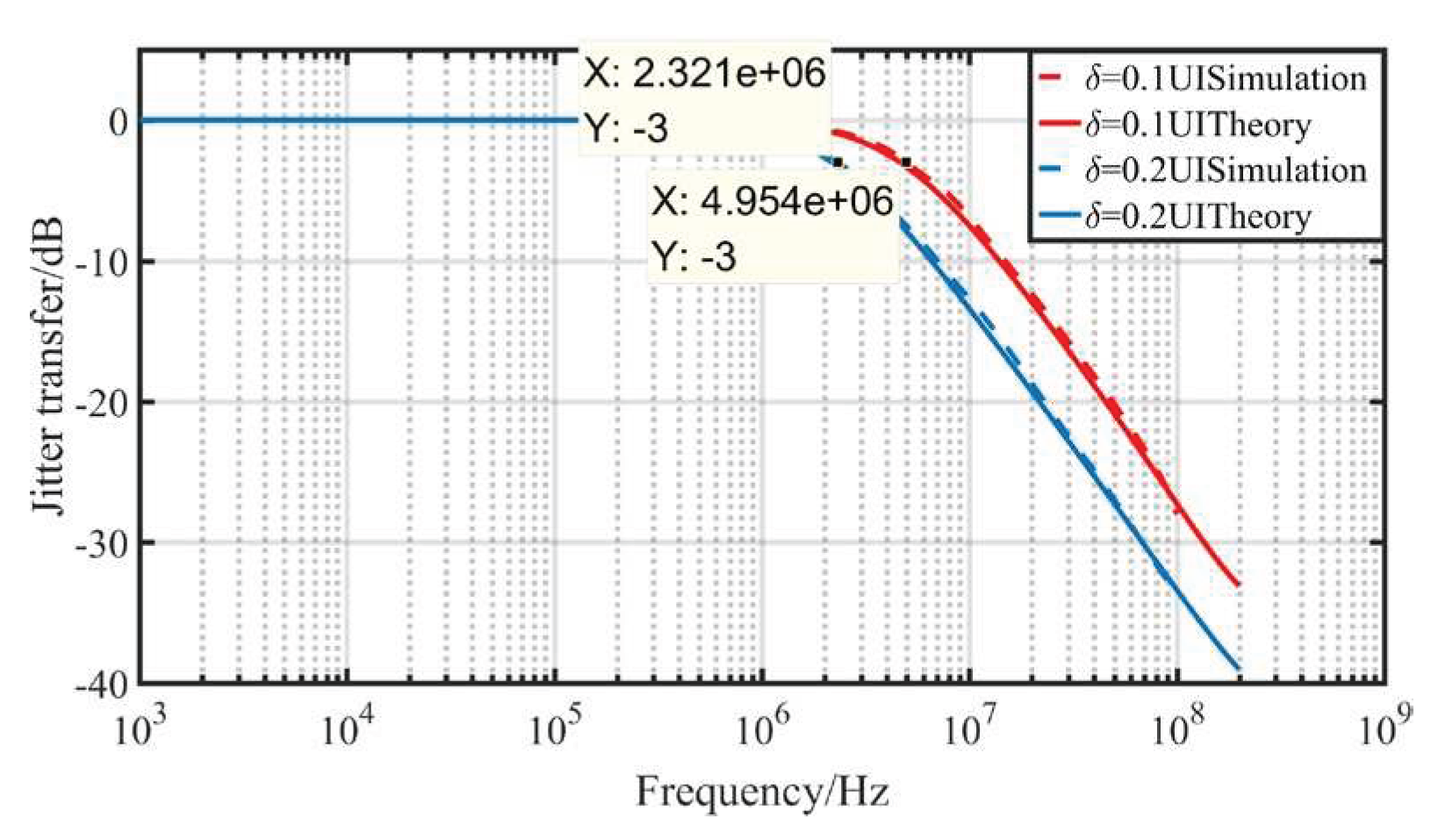

3.2.1. Modeling Analysis and Parameter Design of CDR

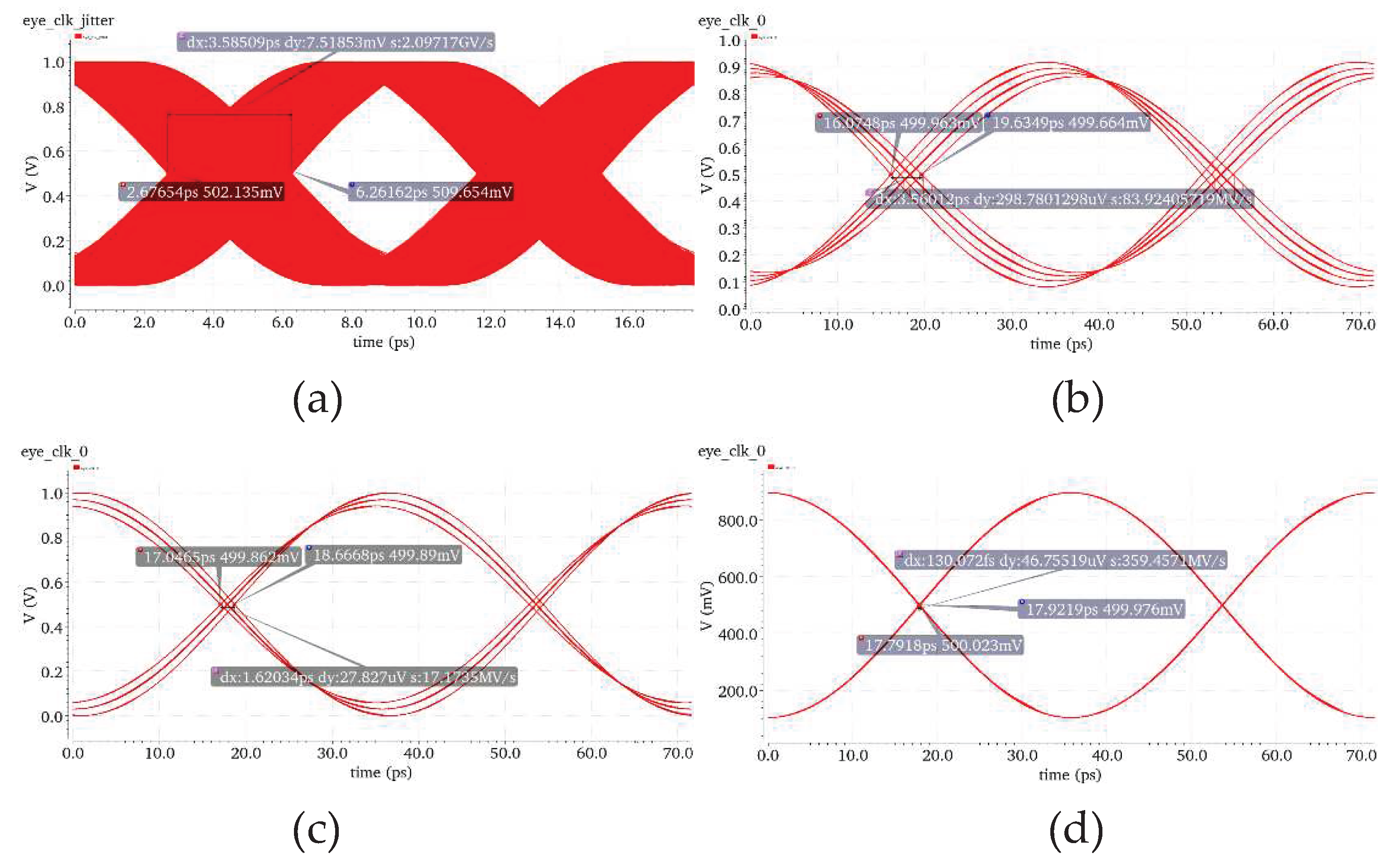

3.2.2. Simulation Verification of CDR.

3.3. PLL Design

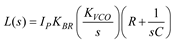

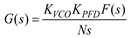

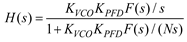

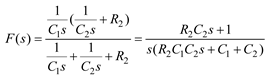

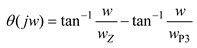

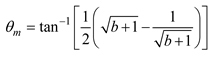

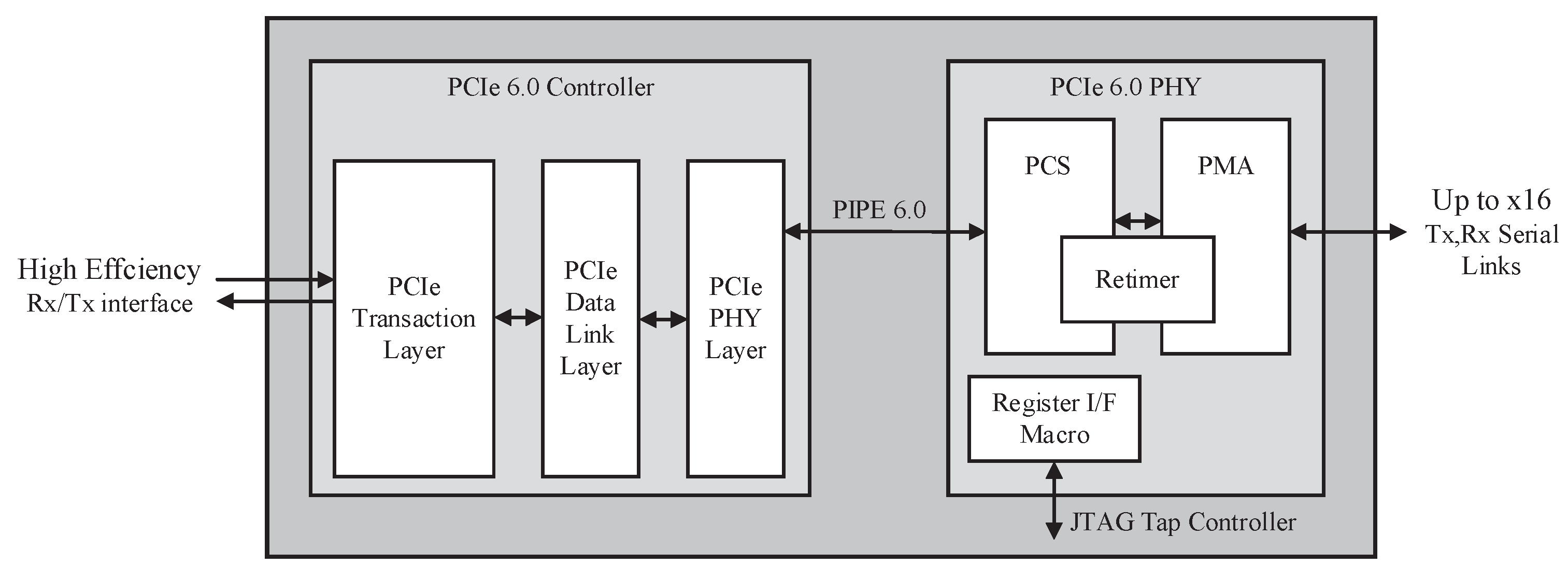

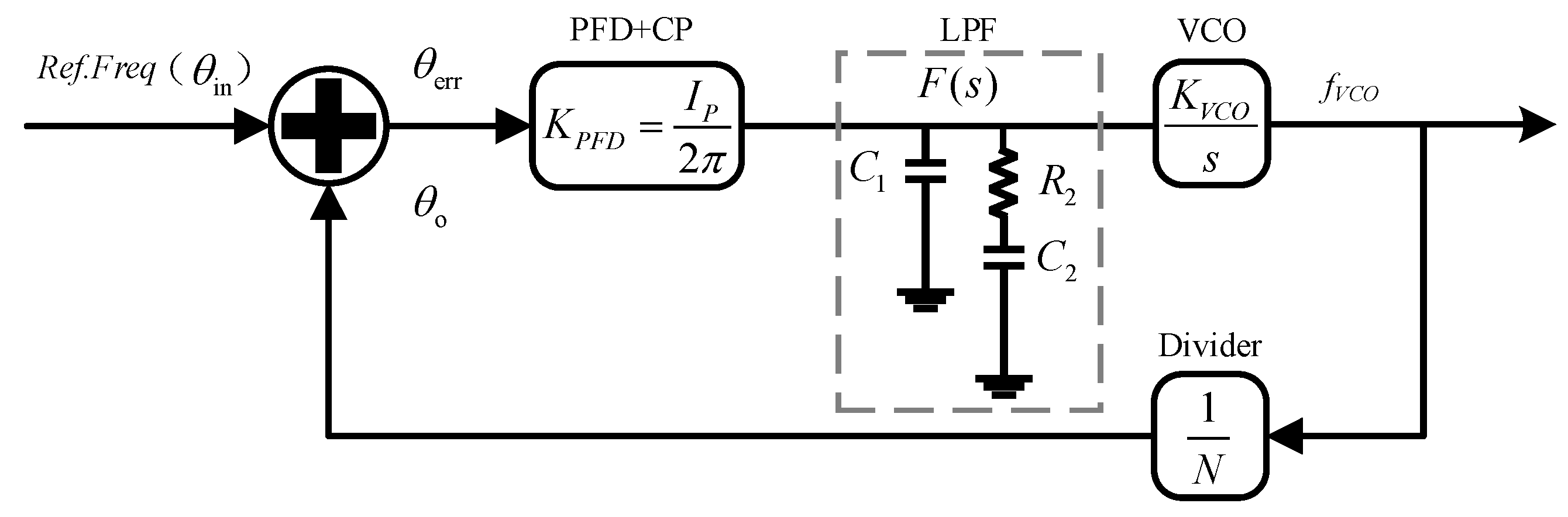

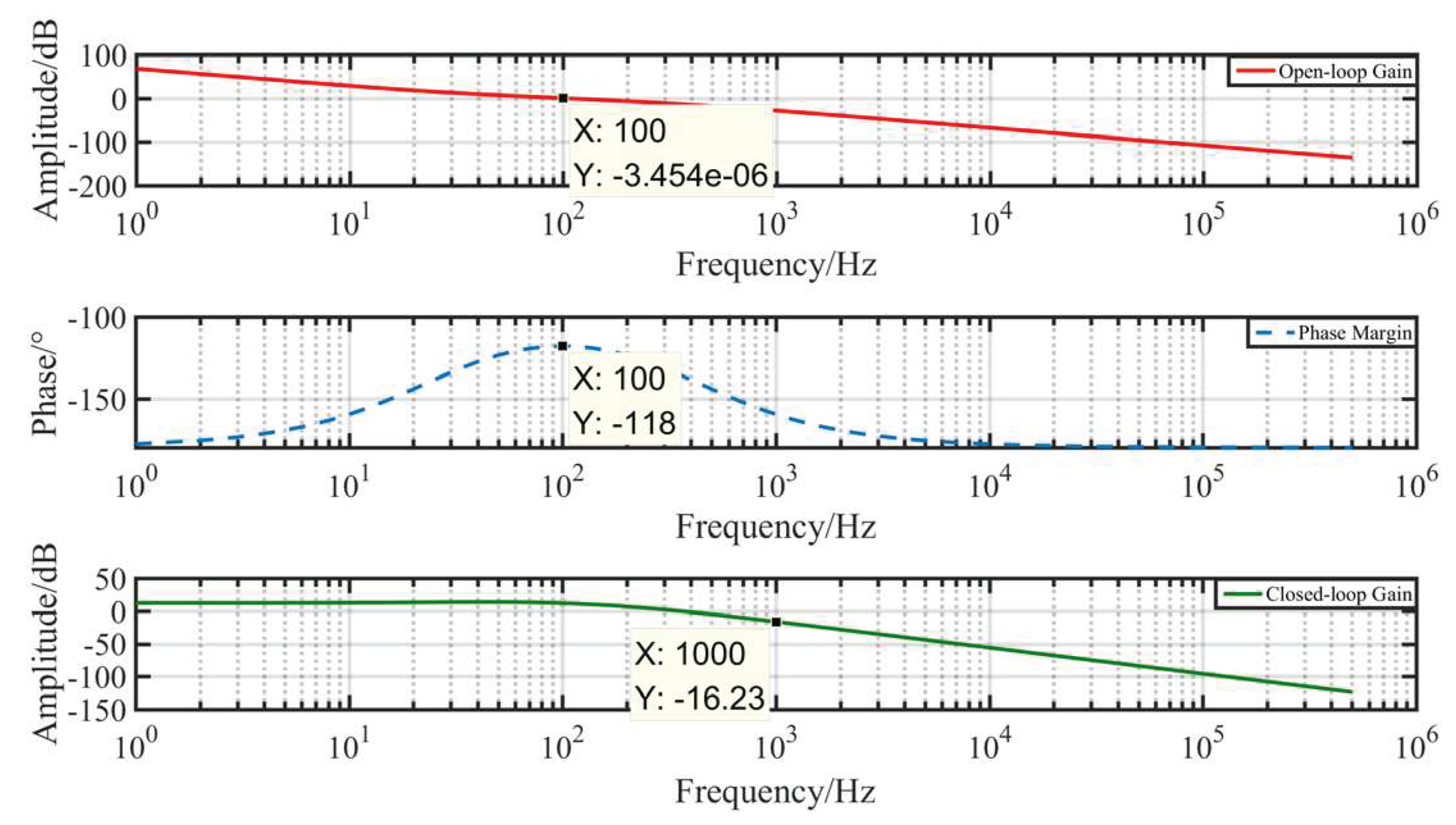

3.3.1. PLL Linear Model Analysis

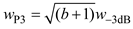

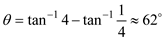

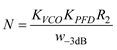

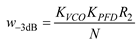

3.3.2. PLL Parameter Design

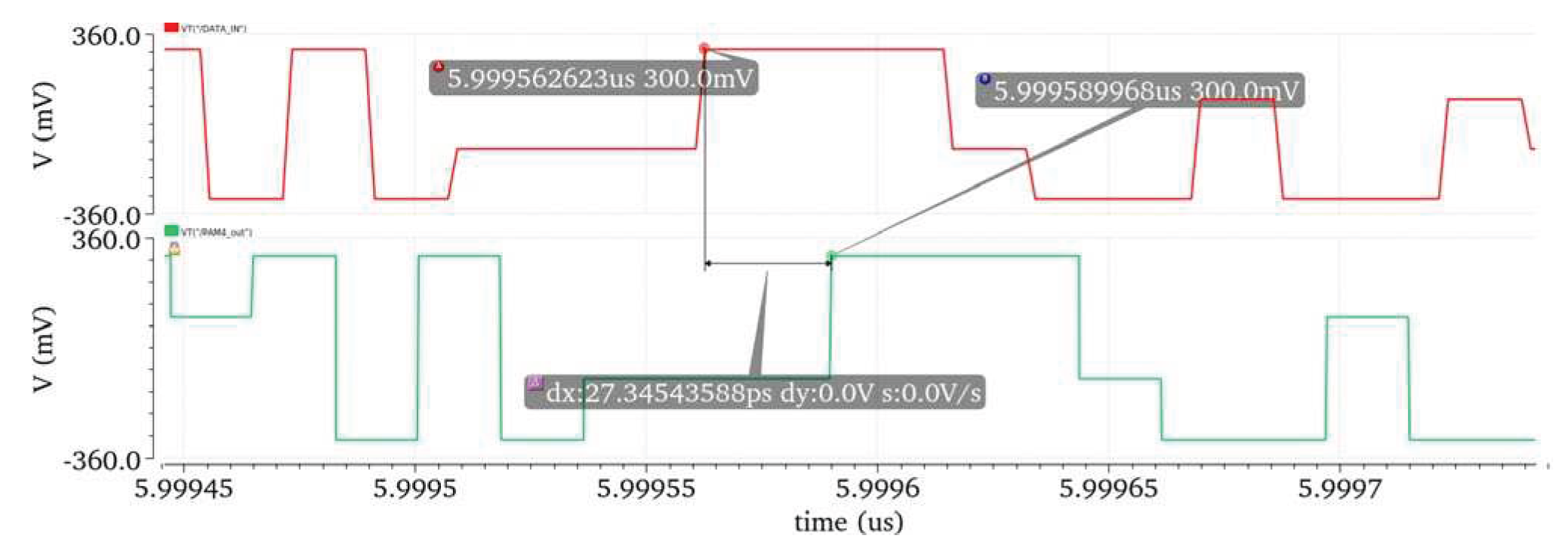

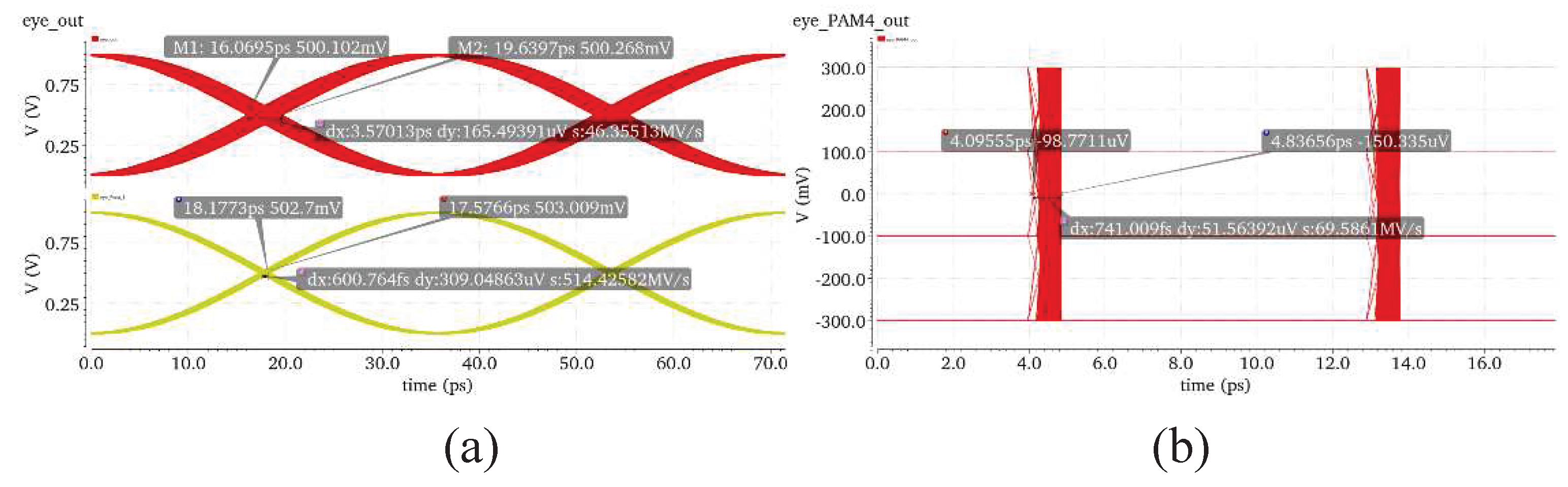

4. Retimer Circuit Simulation

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Chang, F.L.; Amber, T.; Arun, T.; et al. 6.5 A 400Gb/s Transceiver for PAM-4 Optical Direct-Detect Application in 16nm FinFET. In Proceedings of the 2019 IEEE International Solid- State Circuits Conference (ISSCC), San Francisco, CA, USA, 2019, pp. 120-122. [CrossRef]

- Robert, R.; Michael, R.; Fran, K.; et al. A 4.5 mW/Gb/s 6.4 Gb/s 22+1-Lane Source Synchronous Receiver Core with Optional Cleanup PLL in 65 nm CMOS. In Proceedings of the 2010 IEEE Journal of Solid-State Circuits (JSSC), Dec. 2010, vol. 45, no. 12, pp. 2850-2860. [CrossRef]

- Hiok-Tiaq Ng; Ramin, F.R.; William, J.D.; et al. A second-order semidigital clock recovery circuit based on injection locking. In Proceedings of the 2003 IEEE Journal of Solid-State Circuits (JSSC), Dec. 2003, vol. 38, no. 12, pp. 2101-2110. [CrossRef]

- Tamer, A.; Robert, D.; Ron, H.; Chih-Kong, K. Y.; A 100+ Meter 12 Gb/s/Lane Copper Cable Link Based on Clock-Forwarding. In Proceedings of the 2013 IEEE Journal of Solid-State Circuits (JSSC), April 2013, vol. 48, no. 4, pp. 1085-1098. [CrossRef]

- Yasuhiro, N.; Toshihide, S.; Hideki, K.; et al. A 43-Gb/s full-rate-clock 4:1 multiplexer in InP-based HEMT technology. In Proceedings of the 2002 IEEE Journal of Solid-State Circuits (JSSC), Dec. 2002, vol. 37, no. 12, pp. 1703-1709. [CrossRef]

- S. Hu; et al. A 50Gb/s PAM-4 Retimer-CDR + VCSEL Driver with Asymmetric Pulsed Pre-Emphasis Integrated into a Single CMOS Die. 2019 Optical Fiber Communications Conference and Exhibition (OFC), San Diego, CA, USA, 2019, pp. 1-3.

- T. Tang; B. Wray; R. Murugan; Die-Package-PCB Signal Integrity Performance Debug of a High-Speed (25Gbps) Retimer: Simulation to Measurement Correlation. 2020 IEEE International Symposium on Electromagnetic Compatibility & Signal/Power Integrity (EMCSI), Reno, NV, USA,2020, pp.170-175. dio: 10.1109/EMCSI38923.2020.9191568.

- P. Mishra; A. Tan; B. Helal; et al. A 112Gb/s ADC-DSP-Based PAM-4 Transceiver for Long-Reach Applications with >40dB Channel Loss in 7nm FinFET. In Proceedings of the 2021 IEEE International Solid- State Circuits Conference (ISSCC), San Francisco, CA, USA, 2021, pp. 138-140. doi: 10.1109/ISSCC42613.2021.9365929.

- Zhao, L.W. The low latency of data transmission design based on FPGA. Master’s Degree Thesis, Zhengzhou University, Zhengzhou, China, 2017. https://kns.cnki.net/KCMS/detail/detail.aspx?dbname=CMFD201702&filename=1017128975.nh.

- Wang, C. Design and implementation of Low-Latency error correction coding for Ultra-High-Speed interconnection transmission Links. Master’s Degree Thesis, National University of Defense Technology, Changsha, China,2020. [CrossRef]

- GUO, K.L.; WANG, H.M.; LIU, T.; et al. A Non - Equivalent Tail Current Source Based New Phase Interpolator with High Linearity for High - Speed SerDes. Journal of Air Force Engineering University (Natural Science Edition), 2020, vol. 21, no. 4, pp. 61 – 67. [CrossRef]

- Li, T.J.; Zhang, G.; Zhang, J.M.; Xin, K.W. A Novel High-Gain PAM4 Baud-Rate Phase Detector for ADC-Based CDR. 2022 7th International Conference on Integrated Circuits and Microsystems (ICICM), Xi’an, China, 2022, pp. 606-609. [CrossRef]

- Luan, W.H.; Wang, D.J.; Jia, Chen. Modeling Analysis and Circuit Design of Second-Order Clock Data Recovery Circuit Applied to 10 Gbase-KR. Microelectronics and Computers ,2020, vol. 37, no. 03, pp. 1-4. [CrossRef]

- Jeff, L.S.; John, S. A digital clock and data recovery architecture for multi-gigabit/s binary links. Proceedings of the IEEE 2005 Custom Integrated Circuits Conference (CICC), San Jose, CA, USA, 2005, pp. 537-544. [CrossRef]

- Xin, K.W.; Lyu, F.X; Wang, J.Y. A Low Noise Clock Generator for High-Speed Serial Interface. Microelectronics, 2019, vol. 49, no. 06, pp. 817-823. [CrossRef]

- Zhang, G. Design of COMS Integrated Phase Locked Loop Circuit. First Edition, Tsinghua University Press, Beijing, China,2013. pp. 15–17.

- Yang, C. Research and design of fast-locked, high-speed and low-jitter clock generation. Master’s Degree Thesis, University of Electronic Science and Technology of China, Chongqing, China,2015.

| CDR Parameters | Design Value |

|---|---|

| PD gain (KBR) | 0.56 |

| Voting gain (KV) | 0.54*64=19.2 |

| Proportional path gain (phug) | 1 |

| Integral path gain (frug) | 2-14 |

| Digital phase converter gain (KDPC) | 2-9 |

| Loop latency (N) | 4 |

| PLL Parameters | Design Value |

|---|---|

| Charge pump current (IP) | 0.15mA |

| Filter capacitance (C1) | 2.2616nF |

| Filter capacitance (C2) | 34.119nF |

| Filter resistance (R2) | 187.09Ohms |

| VCO gain (KVCO) | 600MHz/V |

| Divider (N) | 4 |

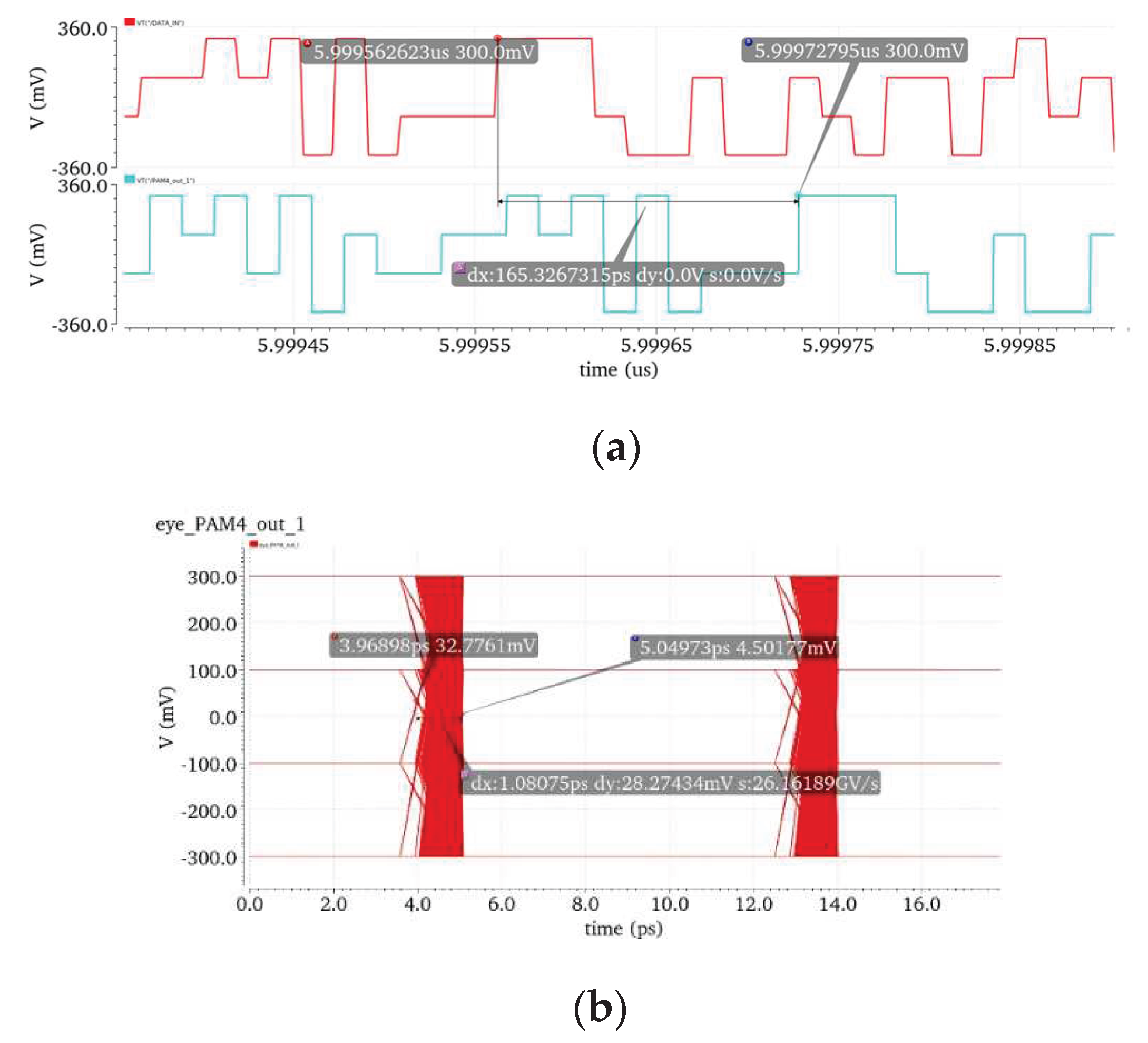

| Parameters | Conventional Retimer | This paper Retimer |

|---|---|---|

| Main structural features | CDR+DFF | CDR+PLL+PLL |

| Retiming data jitter | 1.08ps | 0.741ps |

| Data jitter attenuation | -10.38dB | -13.66dB |

| Penetration latency | 165.3ps | 27.3ps |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).