1. Introduction

This paper considers short binary eBCH codes in situations where very low latency and high reliability are required. The motivation of this work comes from ever-growing low latency and high reliability requirements of wireless communication networks [

1]: "Message transfer latency no longer than 100 ms with 20 ms maximum allowed latency in some specific use cases, without any compromise on reliability.” It is well known that these requirements can be satisfied using short binary error-correcting codes (ECC). In the past, research in this area focused on polar codes (see [

2] and references therein) using successive-cancellation list-decoding (SCLD) and SCLD with cyclic redundancy check (SCLD-CRC). However, other types of channel coding schemes appear to have been overlooked. An important exception is reference [

2], where codes obtained by interpolating between polar codes and Reed-Muller (RM) codes are studied and trade-offs examined between decoding complexity and error performance. We choose extended BCH codes so that they can be compared with polar codes of the same code lengths.

The main contribution of this paper is the presentation of simulation results in order to compare the performance of binary ECC of short length, such as Reed-Muller (RM) codes, polar codes and binary eBCH codes, under additive white Gaussian noise (AWGN). These results serve to verify that short length eBCH codes have better performance than short polar codes of the same length and rate and should be considered as strong candidates in applications where low latency is required.

Simulation results for eBCH codes were obtained with ordered-statistics decoding (OSD) [

3] with reprocessing order 1. In the following,

N denotes the code length and

K the code dimension (or number of information bits). Although decoding complexity depends on many factors, we chose reprocessing order equal to one in OSD so that its complexity, O(

K), is similar to that of SCLD-CRC, O(

Nlog

2N).

2. An Illustrative Example: The Performance of a Polar Code Versus an RM Code and an eBCH Code with Polar Mapping Under AWGN with Length 64

A construction algorithm (algorithm TR1) of polar codes under AWGN is presented in [

4]. Using this algorithm with a 5 dB threshold, it was found that the first instance where RM codes and polar codes differ is at

N=64 and

K=22. Notice that this is different from polar code constructions

under erasures, where the first case in which polar codes and RM codes differ is

N=32 and

K-=16 [

5]. This suggests that polar codes are not the best option for code rates

K/

N lower than 1/2.

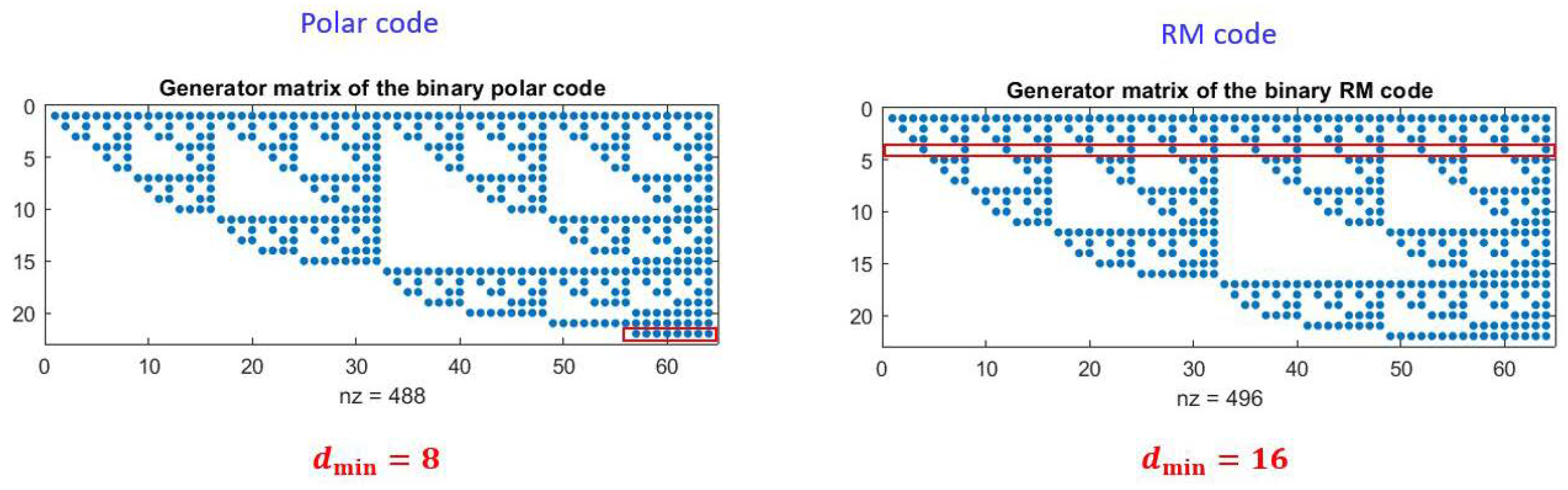

Generator matrices of both codes are depicted in

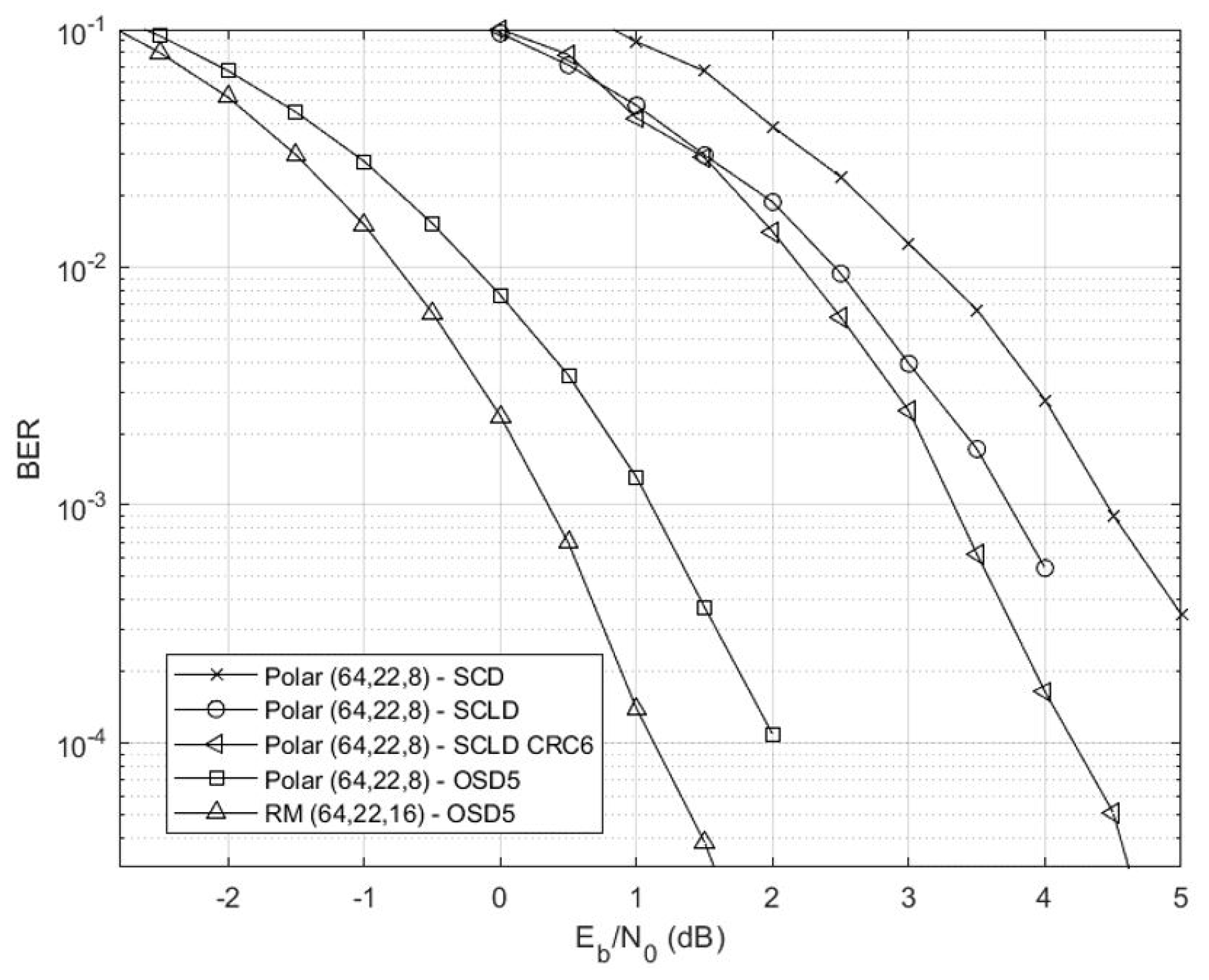

Figure 1 (a dot represents bit value equal to one). Observe that a codeword of Hamming weight (i.e., number of ones) 8 in the generator matrix of the polar code is replaced by a codeword of Hamming weight 16 in the generator matrix of the RM code. This is indicated with a red rectangle in the figure. Since the RM code has a higher minimum Hamming distance, it achieves better performance as shown in the simulation results in

Figure 2, which plots the bit error rate (BER) versus the average bit energy to noise ratio (E

b/N

0) expressed in decibels (dB).

The simulations reported in

Figure 2 utilized the following decoding algorithms: (1) Successive cancellation decoding (SCD) [

6], successive-cancellation list decoding (SCLD) [

7], and (2) SCLD with 6-bit CRC (SCLD-CRC6) ]7], which was found to give best performance among CRC variations, and (3) reprocessing order 5 OSD (OSD5) [

8]. The RM code was simulated using OSD5. As expected, this illustrates the well-known fact that polar codes do not perform well at relatively short lengths.

The idea behind this paper is to extend this example to binary BCH codes which are known to outperform RM codes. Binary extended BCH codes, or eBCH codes, are chosen due to their higher minimum distance for the same rate compared to RM codes and for having the same length as polar codes.

3. Results

3.1. Binary eBCH and Polar Codes of Length 64

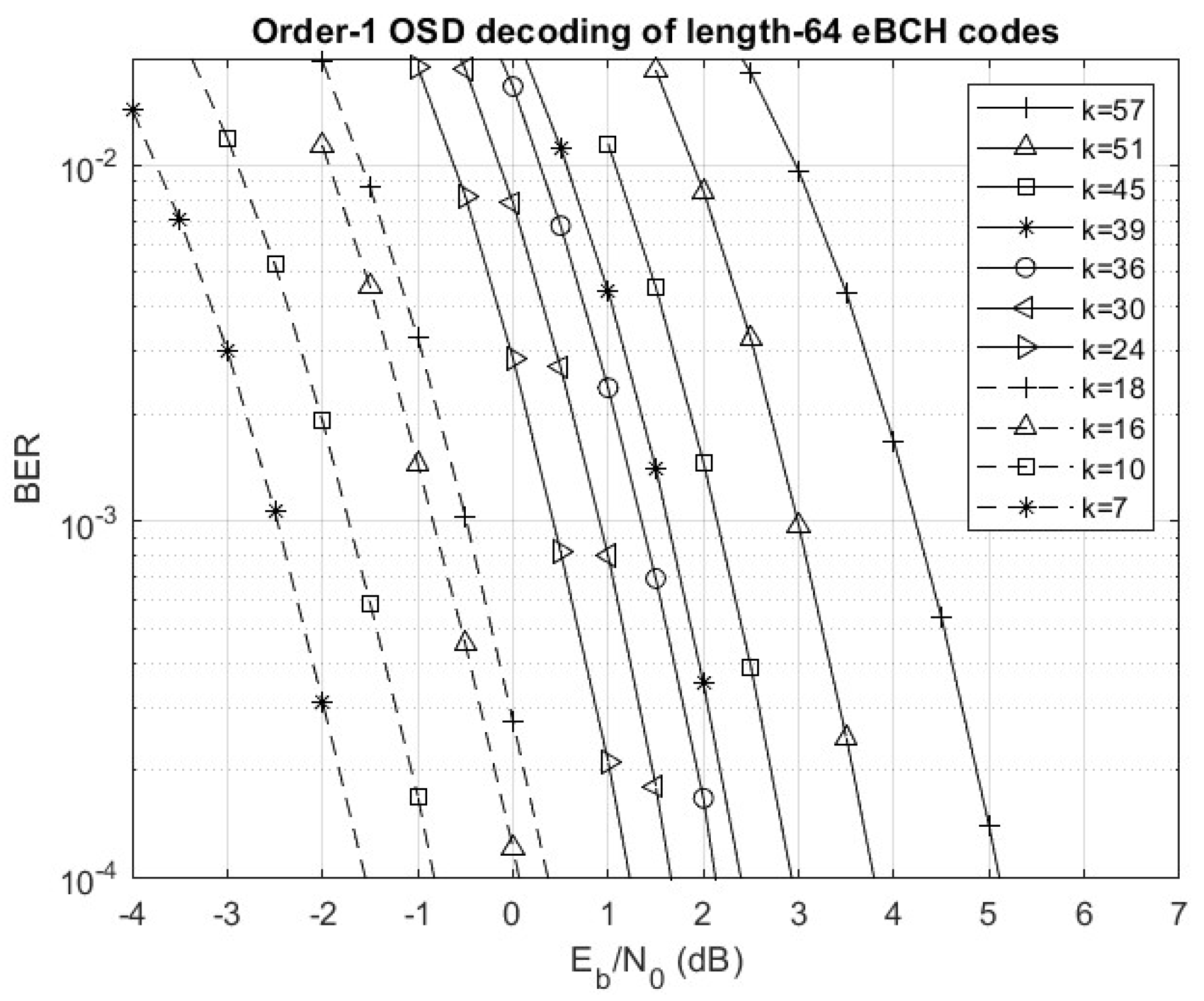

The performance of OSD with reprocessing order 1 for all binary eBCH codes of length 64 was simulated and the results are shown in

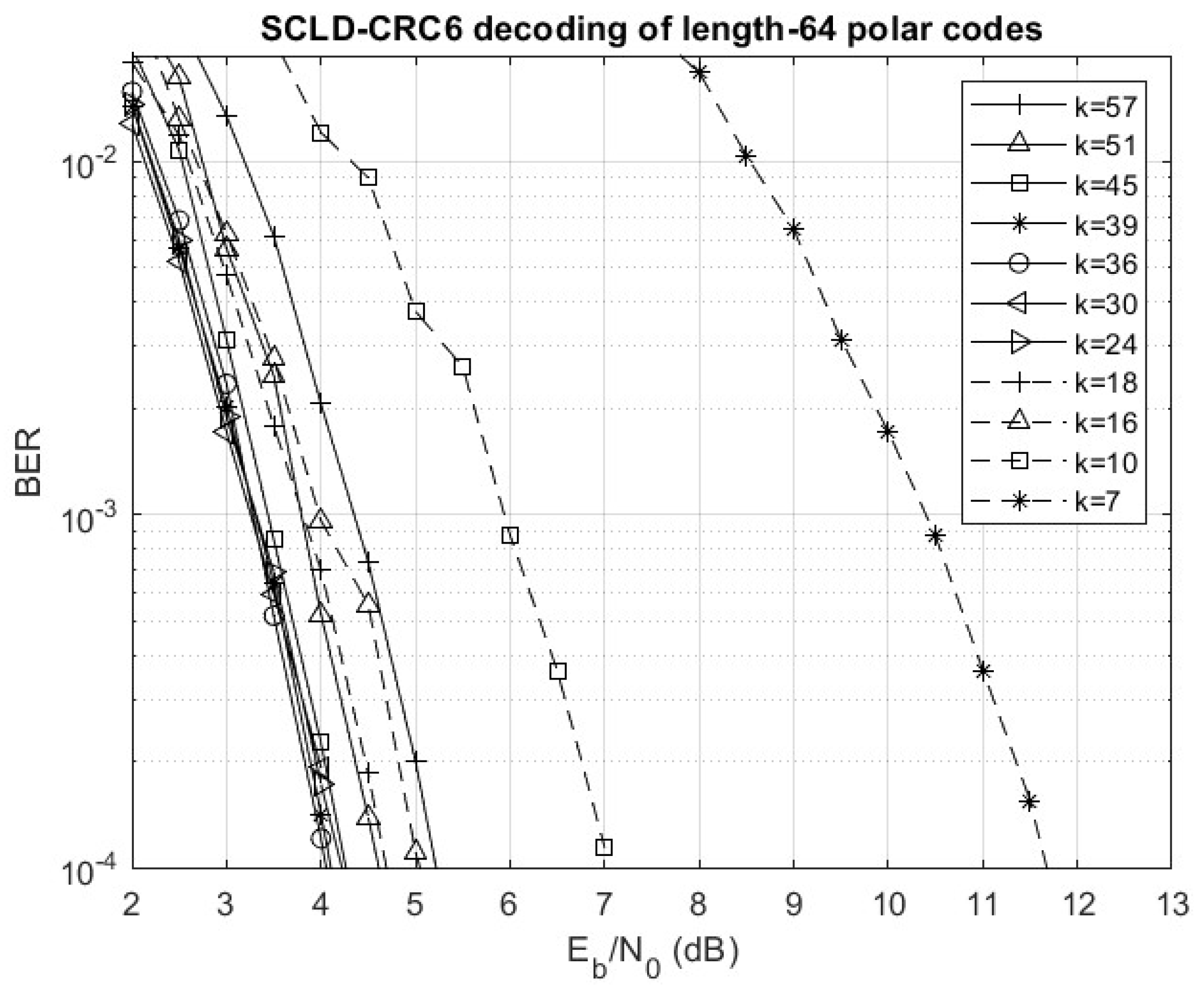

Figure 3. SCLD with a 6-bit CRC of type 6-ITU (denoted SCLD-CRC6) was simulated using the AFF3CT software [

6] for polar codes with the same length 64 and dimensions. The results are presented in

Figure 4. After trying different CRC schemes, a 6-bit CRC was found to give the best performance. The reason for this is that a larger number of CRC bits reduces the coding rate while SCLD yields a smaller reduction in error rate, resulting in an increase in the average bit error rate.

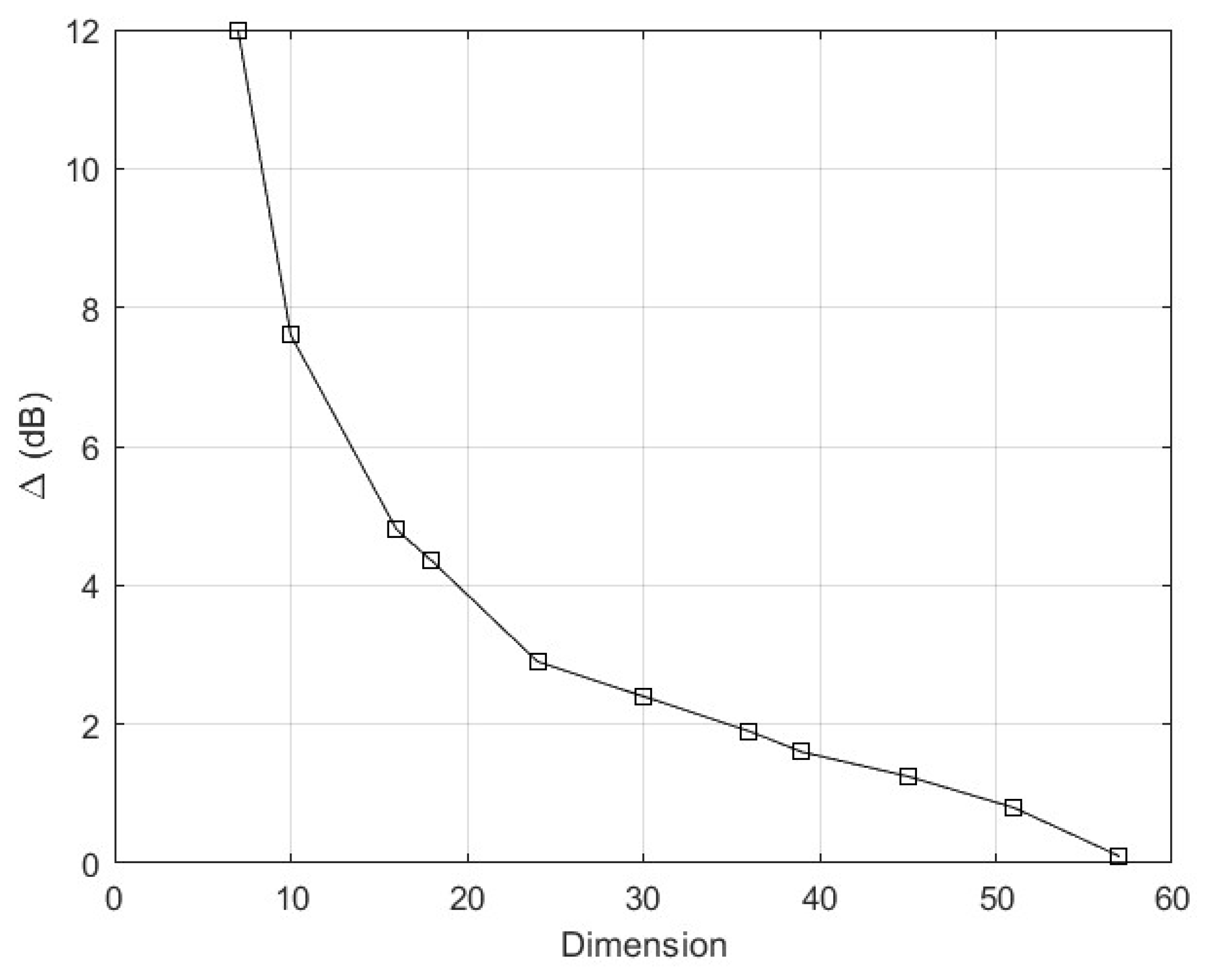

Table 1 shows the difference

in E

b/N

0 (dB) required to achieve an average bit error rate of 10

-3. We observe that polar codes of length 64 and rates less than 1/2 (corresponding to dimension less than 32) give poor performance with at least a 2 dB loss compared with eBCH codes. This additional average power is also shown graphically in

Figure 5.

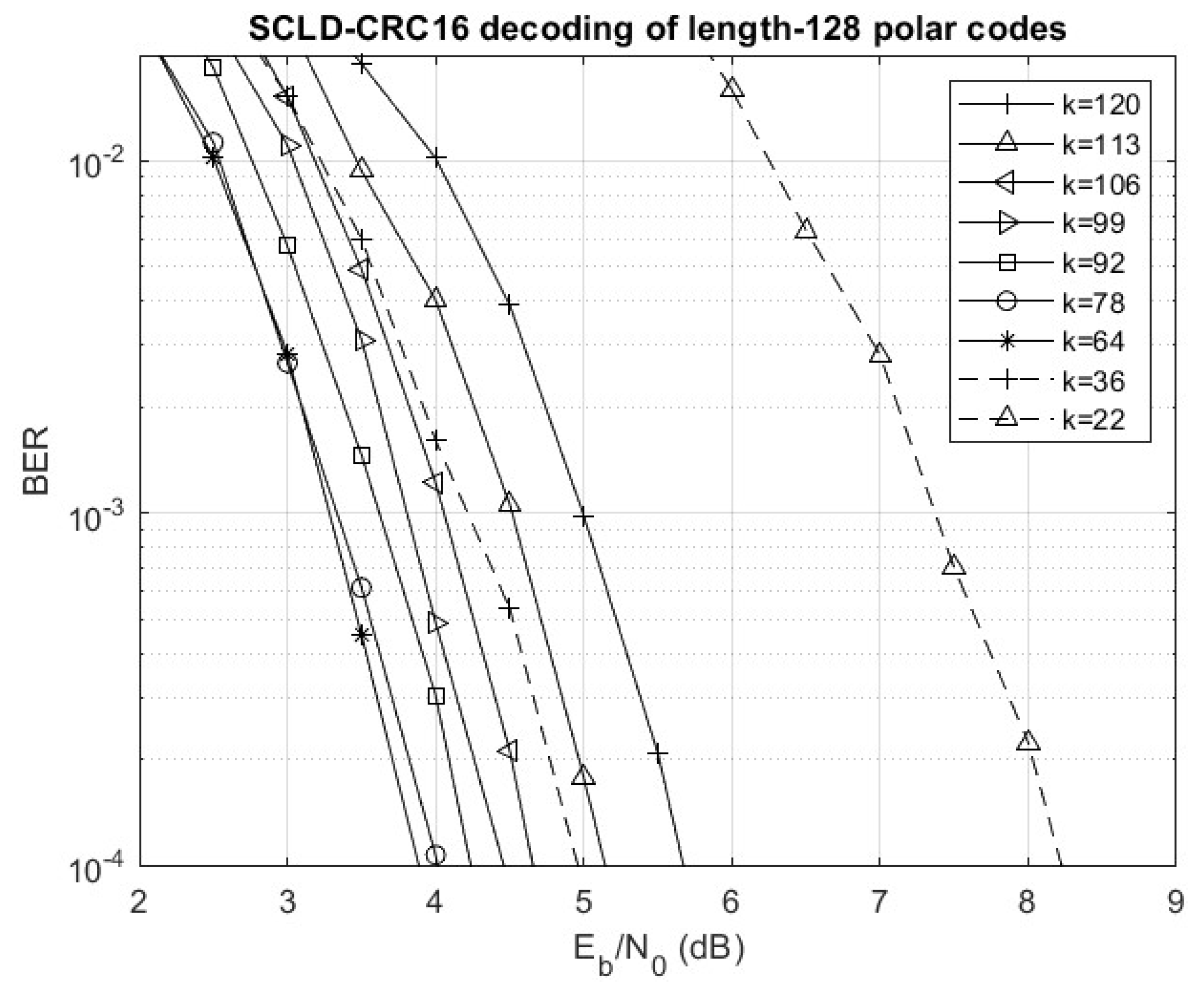

3.2. Binary eBCH and Polar Codes of Length 128

Also simulated was the performance of OSD with reprocessing order 1 for selected binary eBCH codes of length 128. The simulation results are shown in

Figure 6. Here SCLD with a 16-bit CRC of type 16-CCITT (SCLD-CRC16) was simulated with AFF3CT [

6] for polar codes of the same length and dimensions as the selected eBCH codes. Again, we found this 16-bit CRC scheme to give the best performance among different alternatives. In

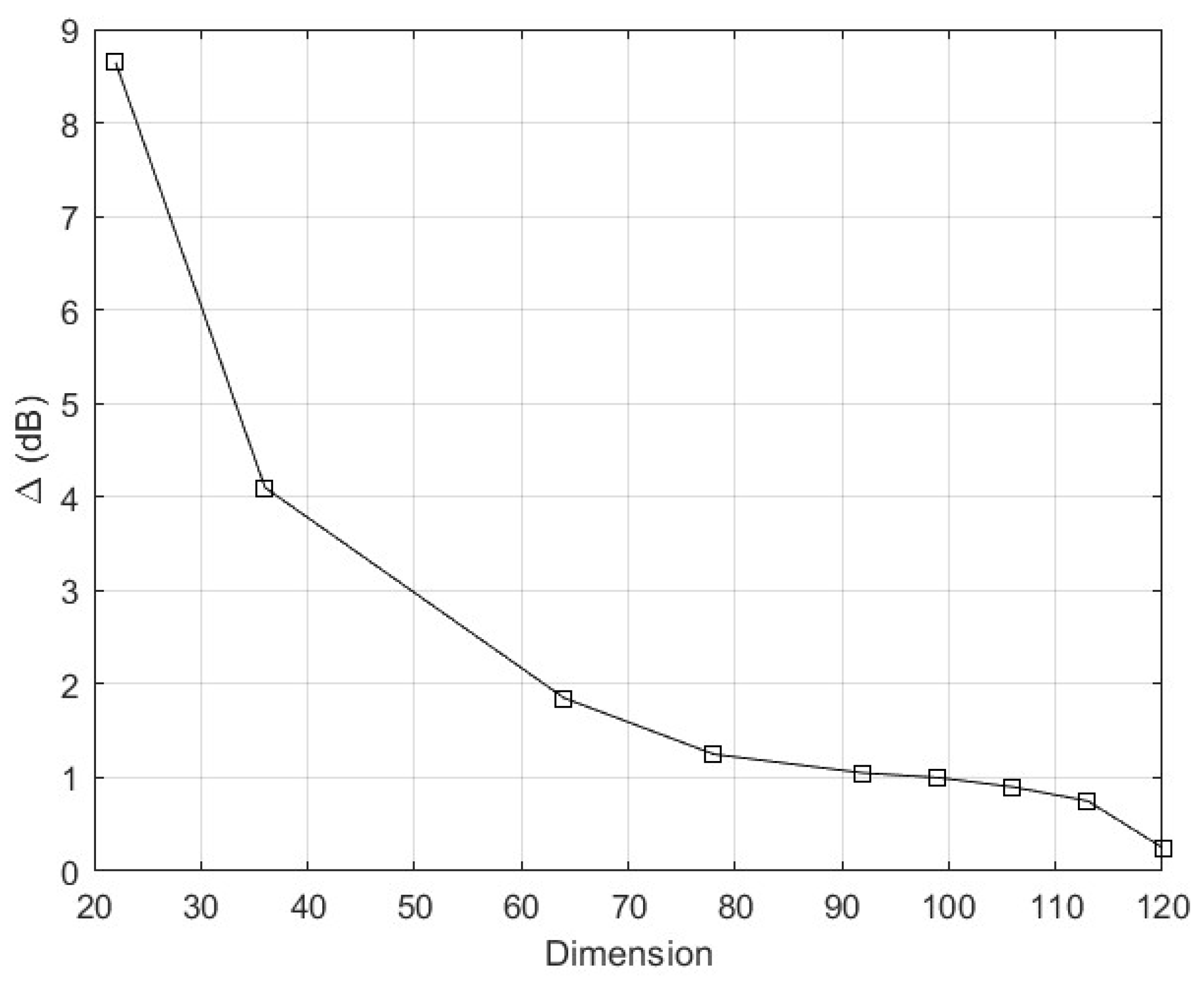

Figure 7 simulation results for polar codes are shown. Once again, the difference

in E

b/N

0 (dB) required to achieve an average bit error rate of 10

-3 was computed and is plotted in

Figure 8.

In the case of N=128, polar codes with rates greater than 1/2 exhibit a relatively small difference of up to 1.4 dB in additional average power required to achieve the same error performance. Just as in the case of N=64, there is a large loss in average power requirements with polar codes compared to eBCH codes at low coding rates.

4. Discussion

In this paper comprehensive simulation results are reported on the performances of length 64 eBCH codes and length 64 polar codes of the same rates. Selected codes of length 128 were also simulated. To reduce complexity, ordered statistics decoding with a reprocessing order equal to 1 was used in the case of eBCH codes, while successive-cancellation list decoding with 6-bit CRC (for N=64) and 16-bit CRC (for N=128) were used for polar codes. The results indicate that polar codes achieve an error performance similar to eBCH codes at high coding rates, with comparable decoding complexity. It was observed that the performance of polar codes degrades significantly at coding rates lower than 1/2. In all cases studied, eBCH codes outperform polar codes.

While the results presented here for eBCH codes were obtained with reprocessing order-1 OSD, it should be remarked that recently there has been a renewed interest in devising efficient decoding techniques of linear block codes based on bit reliability values, such as Guessing Random Additive Noise Decoding (GRAND) [

10] and ordered-reliability direct error pattern testing (ORDEPT) [

11]. Moreover, at the time of this writing, the authors became aware of a new algorithm for OSD with low complexity that uses reduced Gaussian elimination that is introduced in [12]. The reported results in this paper serve to further motivate the study of decoding algorithms that trade-off a good error performance (high reliability) and low decoding complexity for short binary eBCH codes and other linear block codes.

In summary, a performance comparison has been reported for binary codes of lengths 64 and 128 to achieve ultra-low latency. It has been shown that short eBCH codes with low-complexity decoding based on ordered statistics outperform short polar codes with SCLD-CRC of the same rates. The difference in performance was found to be relatively small only at very high coding rates, while at low coding rates polar codes with SCLD-CRC suffer high performance degradation. Future research includes the implementation of promising reliability-based decoding algorithms for eBCH codes and more generally for linear block codes, and the evaluation of their decoding complexity with specific hardware and software platforms. Another interesting topic to study further is the amount of CRC bits that are required in SCLD-CRC such that a good balance between reliability and average power requirements (due to a decreased coding rate) is achieved.

Conflicts of Interest

The authors declare no conflicts of interest.

References

- Ultra Reliable and Low Latency Communications. 3GPP. Available online: https://www.3gpp.org/technologies/urlcc-2022 (accessed on 16 May 2023).

- M. Mondelli, S. H. Hassani, and R.L. Urbanke. From Polar to Reed-Muller Codes: A Technique to Improve the Finite-Length Performance. IEEE Trans. Communications, 2014; 62, 3084–3091.

- M.P.C. Fossorier and S. Lin. Computationally efficient soft-decision decoding of linear block codes based on ordered statistics. IEEE Trans. Info. Theory, 1996; 42, 738–750.

- B. Tahir and M. Rupp. New construction and performance analysis of Polar codes over AWGN channels. Proc. ICT 2017, pp. 1-4 Limassol, Cyprus, 2017.

- E. Arikan. A Performance Comparison of Polar Codes and Reed-Muller Codes. IEEE Comm. Letters. vol. 12. no. 6. pp.447-449. June 2008.

- Cassagne, O. Hartmann, et al. AFF3CT: A Fast Forward Error Correction Toolbox. SoftwareX. 2019. vol. 10. pp. 1–7. Available online: https://github.com/aff3ct/aff3ct.

- Li, H. Shen, and D. Tse. An adaptive successive cancellation list decoder for polar codes with cyclic redundancy check. IEEE Communications Letters (COMML), December 2012; 16, 2044–2047. [Google Scholar]

- R.H. Morelos-Zaragoza. The Art of Error Correcting Codes. Second edition. John Wiley & Sons Ltd. 2006.

- K. R. Duffy, J. Li, and M. Medard, Capacity-achieving guessing random additive noise decoding. IEEE Trans. Info. Theory, 2019; 65, 4023–4040.

- R. Hadavian, X. Huang, D. Truhachev, K. El-Sankary, H. Ebrahimzad and H. Najafi, Ordered Reliability Direct Error Pattern Testing Decoding Algorithm. Submitted to IEEE Trans. Communications. Oct. 2023. arXiv:2310.12039v1.

- M. Fossorier, M. Shakiba-Herfeh and H. Zhang, Modified OSD Algorithm with Reduced Gaussian Elimination. IEEE Comm. Letters, 2024; 28, 1755–1759.

|

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).