Article

Not peer-reviewed version

## A Comparative Study of n- and p-Channel FeFETs with Ferroelectric HZO Gate Dielectric

Paul Jacob , Pooja Chandrashekar Patil , Shan Deng , Kai Ni , <u>Khushwant Sehra</u> , Mridula Gupta , Manoj Saxena , David MacMahon , <u>Santosh Kurinec</u>\*

Posted Date: 10 October 2023

doi: 10.20944/preprints202310.0587.v1

Keywords: ferroelectric; FeFETs; HZO; polarization; charge trapping

Preprints.org is a free multidiscipline platform providing preprint service that is dedicated to making early versions of research outputs permanently available and citable. Preprints posted at Preprints.org appear in Web of Science, Crossref, Google Scholar, Scilit, Europe PMC.

Copyright: This is an open access article distributed under the Creative Commons Attribution License which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Disclaimer/Publisher's Note: The statements, opinions, and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions, or products referred to in the content.

Article

# A Comparative Study of n- and p- Channel FeFETs with Ferroelectric HZO Gate Dielectric

Paul Jacob <sup>1</sup>, Pooja C. Patil <sup>1</sup>, Shan Deng <sup>1</sup>, Kai Ni <sup>1</sup>, Khushwant Sehra <sup>2</sup>, Mridula Gupta <sup>2</sup>, Manoj Saxena <sup>3</sup>, David MacMahon <sup>4</sup> and Santosh Kurinec <sup>1\*</sup>

- <sup>1</sup> Electrical & Microelectronic Engineering, Rochester Institute of Technology, New York 14623, United States

- <sup>2</sup> Department of Electronic Science, University of Delhi South Campus, New Delhi 110021, India

- <sup>3</sup> Department of Electronics, Deen Dayal Upadhyaya College, University of Delhi, New Delhi 110078, India

- <sup>4</sup> Micron Technology Inc, Manassas, VA 20110, United States

- \* Correspondence: skkemc@rit.edu

Abstract: This study investigates the electrical characteristics observed in n-channel and p-channel ferroelectric field effect transistor (FeFET) devices fabricated through a similar process flow with 10 nm of ferroelectric hafnium zirconium oxide (HZO) as the gate dielectric. The n-FeFETs demonstrate a faster complete polarization switching compared to the p-channel counterparts. Detailed and systematic investigations using TCAD simulations reveal the role of fixed charges and interface traps at the HZO-interfacial layer (HZO/IL) interface in modulating the subthreshold characteristics of the devices. A characteristic crossover point observed in the transfer characteristics of n-channel devices is attributed with the temporary switching between ferroelectric-based operation to charge-based operation, caused by the pinning effect due to the presence of different traps. This experimental study helps understand the role of charge trapping effects in switching characteristics of n- and p-channel ferroelectric FETs.

Keywords: ferroelectric; FeFETs; HZO; polarization; charge trapping

#### 1. Introduction

Ferroelectric field effect transistors (FeFETs), particularly hafnium oxide (HfO2) based FeFETs, have captured the interest of semiconductor technology as the dominant candidates for future memory applications. FeFETs have all the design components of a traditional MOSFET with a sandwiched ferroelectric material layer as the gate dielectric. The two polarization states of the dielectric determine two separate threshold voltages giving rise to a memory window (MW) between two non-volatile memory states. The discovery of ferroelectricity in hafnium oxide based dielectrics which are CMOS compatible, has attracted enormous interests in integrating FeFETs in emerging non volatile memory, in-memory computing, and neuromorphic computing applications [1-3]. This is in conjunction with rapid developments in artificial intelligence (AI) technology, which has put forward the requirements for high-speed, energy efficient, and non-volatile memories [4-6]. In this regard, the research community has observed a shift from the existing von Neumann computer architectures, driven by developments in FeFET technology [7-9]. FeFETs have demonstrated scalability, low power operation due to their CMOS compatibility, and faster non-destructible read/write operation capabilities.

The ferroelectricity observed in ferroelectric materials is primarily due to their non-centrosymmetric structure [1]. A large number of ferroelectric materials have been reported in the literature, however the most popular ones are PZT, PVDF, and HZO [1]. In such materials the polarization direction is controlled by the displacement of the atoms, their degree of variation in crystalline phase and material compositions [10-19].

Among the various dopants in hafnium oxide (HfO2) such as Al, Sr, La, Gd, Si, and Zr that enable ferroelectricity, Zr doped HfO2 films have been observed to demonstrate stable ferroelectric behavior over a wide range of temperatures, compositions, and require a lower processing

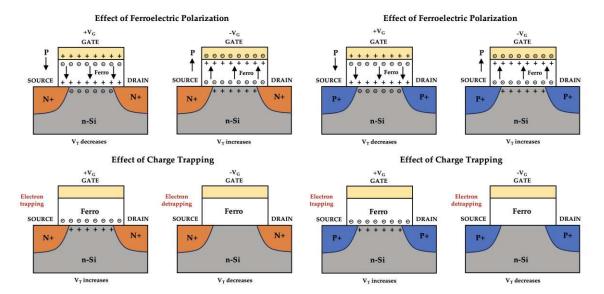

temperature [20-24]. The principle of a FeFET is the change in threshold voltage resulting from the polarization states of the gate dielectric that induce charges at the gate/channel region. Figure 1 depicts the effects of up and down polarization in n-FeFET and p-FeFET and comparing with charge trapping effects which are opposite to the polarization effects [25].

**Figure 1.** Effect of polarization switching and charge trapping on the threshold voltage shift in MOSFETs.

Hafnium oxide based FeFETs, however, may encounter undesirable charge trapping during the program and erase cycles required for polarization switching [1,20,26]. This is due to the defect density in HfO2, which limits the span of the memory window post program cycles [1,20,26]. Therefore, the devices demonstrate a slower read operation which leads to a departure from the theoretical values of the memory window (MW) [1,27]. This calls for an early assessment of the different kinds of traps that form in the dielectric stack of the fabricated structure and is the focus of this study.

### 2. Materials and Methods

#### 2.1. Experimental

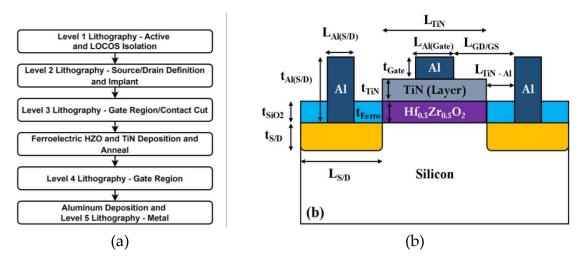

The FeFETs were fabricated in a student run fab [28] at Rochester Institute of Technology (RIT) on 1-10  $\Omega$ -cm base resistivity silicon wafers with 10 nm ALD deposited hafnium zirconium oxide (Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>) as the gate dielectric and 15 nm of sputtered TiN as the gate electrode, followed by an anneal at 600° C to achieve the ferroelectric phase. The process flow consisted of 5 mask levels designed in-house using Mentor Graphics Pyxis, fabricated by a Heidelberg DWL 66+ direct laser writer, and using the ASML PAS5500 i-line stepper for lithography. The devices consisted of LOCOS (local oxidation of silicon) isolated FETs with ion implanted source and drain regions implanted by the Varian 350D ion implanter. For the n-channel devices, a P31 implant species were used, and for the p-channel devices a B11 implant species were used. The process flow and the device schematics are shown in Figure 2.

**Figure 2. (a)** Process flow for the fabrication of FeFETs, and **(b)** Schematic diagram of a fabricated FeFET.

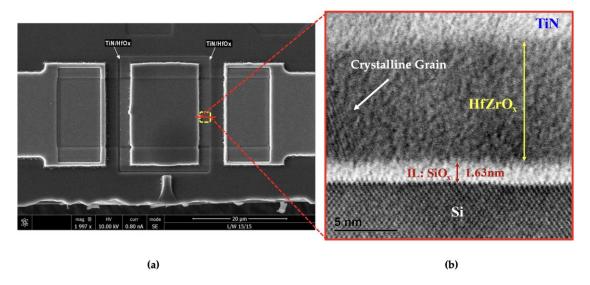

A scanning electron micrograph image of a fabricated device (with designed 15  $\mu$ m channel length and 15  $\mu$ m channel width) and a high-resolution TEM image of the gate dielectric are shown in Figure 3. A close observation of the TEM image reveals the crystalline nature of the deposited ferroelectric HZO (Hf0.5Zr0.5O2) thin film on the silicon substrate. Further, at the HZO/Si interface, a thin interfacial layer (IL) of SiOx (~ 1.63 nm) is observed.

Figure 3. (a) SEM image of a FeFET (top view), and (b) Cross-sectional TEM image of the gate stack.

#### 2.2. Polarization Characterization of HZO

The HZO layer employed in this work was characterized for its polarization behavior by fabricating MFM capacitors. The fabricated test structure helps in the assessment and characterization of the deposited thin film ferroelectric layers. The layer stack of the MFM capacitor consists of a bottom electrode deposited by sputtering and standard liftoff procedures to realize a 100 nm TiN layer. This is followed by the conformal atomic layer deposition (ALD) of the 10 nm Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> ferroelectric layer. The top electrode, TiN is then deposited by sputtering.

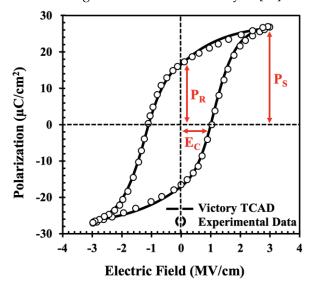

The polarization-electric field (P-E) hysteresis loop of the test structure were recorded with a Keithley 4200 parameter analyzer, illustrated in Figure 4. As observed, the test structure demonstrates good polarization switching behavior with a remanent polarization (2Pr) of 34  $\mu$ C/cm² and a coercive field (Ec) of 1 MV/cm. Also presented is the calibration of a metal-ferroelectric-metal

(MFM) capacitor through Silvaco's Victory TCAD simulator, which will be used as a primer for realizing the fabricated FeFETs through TCAD for further analysis [29].

Figure 4. P-E hysteresis loop.

#### 3.1. Experimental Results

#### 3.1.1. DC Characterization

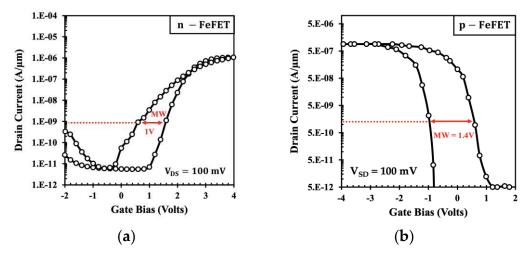

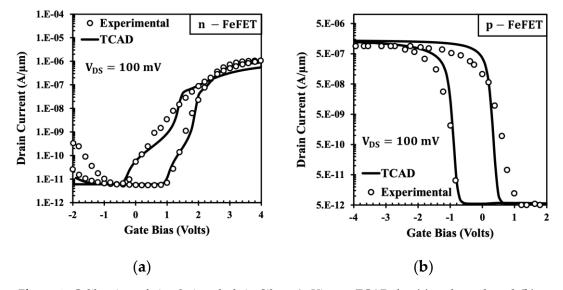

To investigate the DC characteristics, Keithley's 4200-SCS parametric analyzer was used. The transfer characteristics (I<sub>D</sub> vs V<sub>GS</sub>) for the n- and p-FeFETs are shown in Figure 5. The memory window (MW) specified at the drain current of 1 nA/μm, is observed to be 1 V for the n-FeFET and 1.4 V for the p-FeFET. The DC characteristics of the n- and p-FeFETs demonstrate asymmetric subthreshold characteristics. The p-channel devices exhibit steeper subthreshold characteristics compared to their n-channel counterparts. In addition, the n-FeFETs demonstrate a higher contribution of the gate-induced-drain-leakage (GIDL) current component, suggesting the role of stronger band bending at the accumulation region which is responsible for the setup of high electric fields. This consequently results in the tunneling of the valence band (VB) electrons to the conduction band (CB) while generating holes in the VB, otherwise known as band-to-band tunneling (BTBT). Another distinguishing feature of the n-FeFETs is the characteristic crossover point observed during the downward sweep in the transfer characteristics.

**Figure 5.** Transfer characteristics of **(a)** n-channel FeFETs, and **(b)** p-channel FeFETs depicting asymmetric behavior.

5

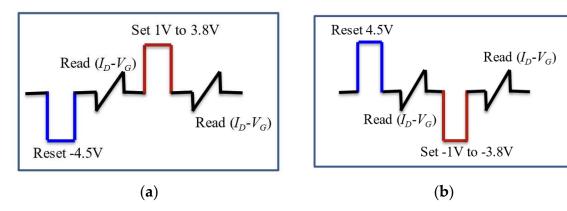

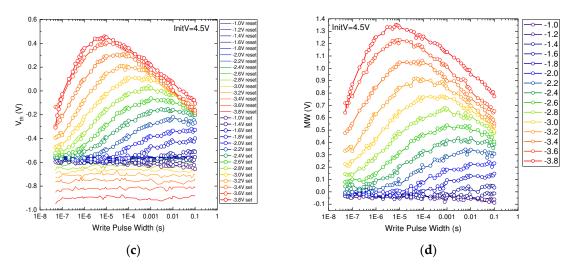

The fabricated n- and p-channel FeFET devices were characterized through a series of read and write pulse cycles using a FormFactor Cascade Microtech Summit 11000/12000 probe station & Keithley 4200-SCS parametric analyzer. The pulse setups for the n- and p-channel devices are shown in Figure 6. For the n-channel devices, the height of the reset pulse is set to -4.5 V with a pulse duration of 1  $\mu$ s, while the set pulse height is varied from 1 V to 3.8 V and the pulse duration is gradually tuned from 50 ns to 0.1 s. The p-channel devices are also subjected to similar pulsing conditions with reversed polarities.

**Figure 6.** Read and write operations performed at the gate electrode of **(a)** n-FeFET, and **(b)** p-FeFET.

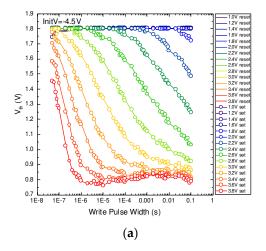

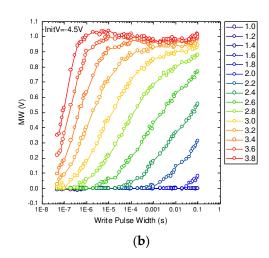

The shift in the threshold voltage (V<sub>TH</sub>) and the resulting MW for the n- and p-channel devices as a function of pulse width is shown in Figure 7. The switching of the polarization dipoles of a particular ferroelectric layer is a function of both the applied bias and the time duration during which the pulse is applied to the ferroelectric gate stack. As observed from Figure 7(a) and Figure 7(c), the V<sub>TH</sub> of both devices can be tuned gradually by varying both the pulse height and the pulse duration. As the pulse height decreases, a longer pulse is required for observing the necessary switching of the polarization dipoles. For the n-channel FeFETs, a maximum MW of 1 V, is achieved with a pulse height of 3.8 V and pulse duration of 1  $\mu$ s, as seen in Figure 7(b). This point corresponds to the complete switching of the polarization dipoles within the ferroelectric layer. Intermediate pulse height/widths can be utilized for partial polarization in multi-level logic devices. For the p-channel devices, however, the pulse characteristics in Figure 7(c) and Figure 7(d) demonstrate a global maxima in the MW at a pulse duration of 10  $\mu$ s and a pulse height of -3.8 V. Further, on increasing the pulse width, a characteristic roll-off in the MW is observed as a function of write pulse width.

**Figure 7.** Partial polarization switching by varying the pulse width: **(a)** Gradual tuning of V<sub>TH</sub>, and **(b)** MW for n-channel, **(c)** Gradual tuning of V<sub>TH</sub>, and **(d)** MW for p-channel by increasing the width of the program pulse.

The switching behavior investigated using different program/erase pulse heights and widths shows a faster complete polarization switching in n-FeFETs (3.8 V, 1  $\mu$ s) than in p-FeFETs (-3.8 V, 10  $\mu$ s).

#### 3.2. Simulation Methodology

The polarization parameters extracted from the test structure's P-E hysteresis loops are fed to the simulation deck to realize ferroelectricity in the HZO. The calibrated simulation deck acts as a primer for realizing FeFET devices for the assessment of the trapping parameters. Table 1 provides the geometrical parameters of the fabricated devices used in simulations.

| Symbols          | Description                          | Value                                 |

|------------------|--------------------------------------|---------------------------------------|

| N <sub>D/S</sub> | Source/Drain Doping                  | 2 x 10 <sup>19</sup> cm <sup>-3</sup> |

| $N_{Subs}$       | Substrate Doping                     | 2 x 10 <sup>15</sup> cm <sup>-3</sup> |

| ts/D             | Junction depth of Source/Drain       | 0.8 μm                                |

| Ls/d             | Lateral Extensions of Source/Drain   | 13 µm                                 |

| tsiO2            | Thickness of Silicon Dioxide         | 100 nm                                |

| <b>t</b> Ferro   | Thickness of Ferro Layer             | 10 nm                                 |

| ttin             | Thickness of TiN Layer               | 12 nm                                 |

| <b>t</b> Gate    | Thickness of Al Gate Contact         | 750 nm                                |

| tal(S/D)         | Thickness of Al Source/Drain Contact | 750 nm                                |

| I.A1(S/D)        | Length of Al Source/Drain Contact    | 9 um                                  |

**Table 1.** Device geometrical parameters depicted in Figure 2(b).

Silvaco's Victory Device simulator is used to identify the different kinds of traps that evolved during the fabrication process [26]. A detailed simulation methodology is presented to capture the switching of the polarization dipoles during the upward and downward sweeps.

#### 3.2.1. Calibration of the Fabricated Devices

In modeling the fabricated devices, p-channel devices are considered first due to their steeper subthreshold characteristics and a parallel memory window. The off-state current is tuned by considering donor type bulk traps in the silicon substrate. The bulk trap density is set as  $1 \times 10^{16}$  cm<sup>3</sup> and the trap level is 0.63 eV. The capture cross section for electrons and holes are set to  $10^{-13}$  cm<sup>2</sup> and  $10^{-14}$  cm<sup>2</sup> respectively in accordance with experimental reports [1,20,30]. Further, the literature survey suggests the role of fixed charges and charge trapping at the HZO/SiO<sub>2</sub> interfacial layer (IL) interface

in modulating the subthreshold characteristics and thus limiting the memory window of the fabricated devices [1,20,30]. Accordingly, acceptor type interface traps were tuned at the HZO/IL interface to obtain a best fit to the experimental data. In this regard, an interface trap density of 1.8x10<sup>13</sup> cm<sup>2</sup>, trap energy level of 0.20 eV and capture cross sections of 10<sup>-13</sup> cm<sup>2</sup> and 10<sup>-14</sup> cm<sup>2</sup> for electrons and holes respectively were defined at the HZO/IL interface [31]. In addition to these, Fermi and SRH models were invoked to capture carrier statistics and the interaction of carriers with traps that evolved during the fabrication process. The Priesach Ferroelectric model was also invoked to model the doping dependent mobility, CVT model [32] and to capture the ferroelectric polarization. The calibrated simulation deck for the p-channel device was then used as the basis for realizing nchannel FeFETs. The off-state current was tuned again by considering the donor type bulk traps in the silicon substrate. The trapping conditions defined in the substrate were similar to that of pchannel devices in order to mimic similar bulk conditions, except that the OFF-state current was tuned by changing the energy of the trap level to 0.43 eV. The interface trap density at the HZO/IL interface was similar to the p-channel case, except that the trap levels were tuned to 0.26 eV to capture the slow subthreshold characteristics observed in Figure 5(a) for n-FeFETs. In addition to this, to capture the GIDL effect observed in n-FeFETs, as seen in Figure 5(a), Kane's BTBT model was invoked, and its coefficients were tuned to achieve the best fit to the GIDL current [27]. The calibrated simulation decks for the n- and p-channel devices are shown in Figure 8.

It is observed that the subthreshold characteristics of n-FeFETs are more affected due to charge trapping at the HZO/SiO<sub>2</sub>(IL) interface suggesting that electrons are more easily trapped than holes. The presence of IL further participates in a tunneling current, due to charge trapping at the HZO/SiO<sub>2</sub> (IL). This results in a charge transfer directly between the HZO and Si channel and is responsible for modulating the subthreshold characteristics of the n-FeFETs.

**Figure 8.** Calibration of simulation deck in Silvaco's Victory TCAD for **(a)** n-channel, and **(b)** p-channel FeFETs.

The characteristic crossover point observed in the n-channel devices during the downward sweep was also captured in the TCAD simulations, as shown in Figure 8(a). A closer insight into this reveals that there is a temporary switching of the ferroelectric based operation to the charged based operation, which arises due to the presence of the fixed charges and charge trapping at the HZO/IL interface and HZO bulk layer.

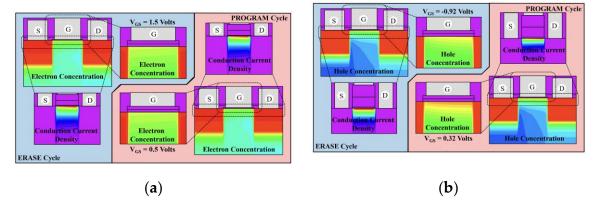

The devices are further investigated by recording the contour plots of electron/hole concentrations and conduction current densities after forward and reverse sweeps at 1 nA/ $\mu$ m. These are depicted in Figure 9(a) for n-FeFETs and in Figure 9(b) for p-FeFETs. For the n-channel device, as observed from Figure 9(a), the shift in electron concentration and conduction current density is not significant after the respective program/erase cycles. In contrast, for the p-channel device, a

significant change in both the hole concentration as well as the conduction current density is observed in Figure 9(b), which accounts for the shift in  $V_{TH}$  observed in both Figure 7(c-d) and Figure 5(b) after subjecting the gate stack to the necessary program cycle.

**Figure 9.** Depiction of electron/hole concentration and conduction current density contour plots for **(a)** n-FeFETs, and **(b)** p-FeFETs.

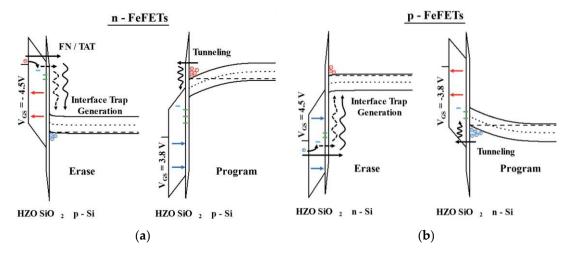

The trapping effects on the MW can be understood by observing the band diagrams recorded at erase and program conditions. This is shown in Figure 10(a) and Figure 10(b) for the n-and p-channel devices, respectively. For the n-FeFET devices, as depicted in Figure 10(a), the carriers can directly tunnel through the HZO and the IL (SiO<sub>2</sub>) through Fowler-Nordheim (FN) tunneling [33]. The carriers can also participate in tunneling with the help of acceptor type traps defined at the HZO/IL interface and at the HZO bulk through the trap-assisted tunneling (TAT) [33]. The injected carriers are 'hot', in the sense that these carriers are energetic and can further participate in the generation of interface traps at the SiO<sub>2</sub> (IL)/Si interface, thereby degrading the quality of the memory window or the devices over time. Consequently, there is a charge sharing directly between the HZO and the silicon channel, which is responsible for modulating the subthreshold characteristics observed in Figure 5(a) and Figure 8(a). Under the program cycle, as depicted in Figure 10(b), the electron carriers tunnel through the SiO2 layer, which is translated to the shift observed in the device threshold voltage. Further, on observing the position of the traps with respect to the fermi level under both erase and program conditions, as seen in Figure 10(a), it can be inferred that most of the tunneled carriers during the program pulse are trapped courtesy of the bulk traps in HZO and at HZO/IL interface. Consequently, the span of the memory window for the n-FeFETs gets limited.

Figure 10. Band diagrams under erase and program conditions for (a) n-FeFETs, and (b) p-FeFETs. Red arrows ( $\rightarrow$ ) in the SiO<sub>2</sub> dictate the orientation of the polarization field, while the green and blue symbols (-/-) represent the traps in bulk HZO and HZO/IL interface.

The band diagrams under erase/program conditions depicted in Figure 10(b) for p-channel devices follow a similar approach. The tunneling probabilities for the holes, however, is much lower than that of the electrons and the charge sharing through FN/TAT is effectively minimized. At a sufficiently higher gate bias, there is still a possibility of 'hot' hole injection, which may result in the generation of traps at the SiO<sub>2</sub>/Si interface. Under the program cycle, similar to the n-channel case, the tunneling of the hole carriers through the SiO<sub>2</sub> is responsible for the shift in the device threshold voltage observed in Figure 5(b) and Figure 8(b). Further, it is also identified that there are multi-level traps present at the HZO/IL interface. These traps are relatively deeper, as discussed in Section 3.1.1, and are responsible for the roll-off in the device V<sub>TH</sub> observed during the pulse characterization of the p-FeFET devices in Figure 7(c).

#### 4. Discussion

In this work, n-FeFETs and p-FeFET devices have been designed, fabricated and investigated using a similar process flow, which is important for their integration in CMOS circuitry. A systematic and calibrated TCAD study is presented to investigate trapping effects on the asymmetric behavior observed in the transfer and pulse characteristics of n- and p-channel FeFET devices. For model validation, fabricated MFM capacitors are realized, and the P-E hysteresis loops are calibrated against the experimental set. The calibrated deck is then used to model the FeFETs to identify the trapping parameters. The n-FeFETs demonstrate faster complete polarization switching compared to their pchannel counterparts. It has been observed that the fixed charges and interface traps at HZO/IL modulate the subthreshold characteristics of the fabricated FeFETs and are responsible for the asymmetricity observed in the transfer characteristics of the two devices. Further, the IL facilitates the tunneling current due to the presence of traps in the bulk HZO and at HZO/IL. This is responsible for the charge sharing directly between the HZO and the silicon channel and limits the span of the memory window for the fabricated devices. The n-channel devices, as observed, are identified to be more affected compared to p-channel devices, suggesting that electrons are more easily trapped than holes. Further, the characteristic crossover point observed in n-FeFETs was found to be associated with the partial recovery of the polarization dipoles due to the charge trapping mechanism, which results in a temporary switch between ferroelectric based operation to charge based operation.

**Author Contributions:** Conceptualization, S.K.; methodology, S.K., P.J. and P.C.P; software, M.S., K.S., M.G.; validation, D.M., K.N. and S.D.; formal analysis, P.J., K.S., K.N. and S.D.; investigation, P.J., K.N. and S.K.; resources, S.K. and K.N.; data curation, P.J., S.K; writing—original draft preparation, K.S., P.J. and S.K; writing—review and editing, P.J., S.K; visualization, K.N., D.M. and S.D; supervision, S.K.; project administration, S.K.; funding acquisition, S.K. All authors have read and agreed to the published version of the manuscript.

**Funding:** The authors acknowledge the support of Semiconductor Research Corporation (SRC) under GRC Projects 2825.001 and 2020-LM-2999. This work was also supported in part by the National Science Foundation, Grant #EEC- 2123863. Any opinions, findings, and conclusions or recommendations expressed in this material are those of the author(s) and do not necessarily reflect the views of the National Science Foundation.

Data Availability Statement: All data are available upon request from the corresponding author.

**Acknowledgments:** The authors acknowledge Uwe Schroeder and Claudia Richter of Nanoelectronic Materials Laboratory (NaMLab), gGmbH for their support in HZO deposition.

**Conflicts of Interest:** The authors declare no conflict of interest.

#### References

- 1. J. Y. Kim, M.-J. Choi, H. W. Jang, APL Materials, 2021, 9(2), 021102.

- 2. H. Mulaosmanovic, J. Ocker, S. Muller, M. Noack, J. Muller, P. Polakowski, T. Mikolajick, S. Slesazeck, *IEEE Symposium on VLSI Technology*, **2017**, T13-3, T176, DOI: 10.23919/VLSIT.2017.7998165.

- 3. H. Mulaosmanovic, E. Chicca, M. Bertele, T. Mikolajick, S. Slesazeck, Nanoscale, 2018, 10, 21755.

- 4. S.-K. Yoon, Y.-S. Youn, J.-G. Kim, S.-D. Kim, The Journal of Supercomputing, 2018, 74, 5293.

- 5. J. C. Mogul, E. Argollo, M. Shah, P. Faraboschi, *Proceedings of the* 12<sup>th</sup> conference on Hot topics in operating systems, **2009**, 1, 14, DOI: 10.5555/1855568.1855582.

9

- T. Ali, K. Mertens, K. Kühnel, M. Rudolph, S. Oehler, D. Lehninger, F. Müller, R. Revello, R. Hoffman, K. Zimmermann, T. Kämpfe, M. Czernohorsky, K. Seidel, J. van Houdt, L. M. Eng, *Nanotechnology*, 2021, 32, 425201.

- 7. R. H. R. Hahnioser, R. Sarpeshkar, M. A. Mahowald, R. J. Douglas, H. S. Seung, Nature, 2000, 405, 947.

- 8. Y. Park, M.-K. Kim, J.-S. Lee, Journal of Materials Chemistry C, 2020, 8, 9163.

- 9. P. A. Merolla, J. V. Arthur, R. Alvarez-icaza, A. S. Cassidy, J. Sawada, F. Akopyan, B. L. Jackson, N. Imam, C. Guo, Y. Nakamura, B. Brezzo, I. Vo, S. K. Esser, R. Appuswamy, B. Taba, A. Amir, M. D. Flickner, W. P. Risk, R. Manohar, D. S. Modha, *Science*, **2014**, 345(6197), 668.

- 10. V. A. Isupov, Ferroelectrics, 2002, 266, 91.

- 11. C. -C. Chung, *Ph.D. Thesis*, University of Connecticut, **2014**, 293. Available at: https://opencommons.uconn.edu/dissertations/293/

- 12. A. S. Bhalla, R. Guo, and E. F. Alberta, Materials Letters, 2002, 54, 264.

- 13. H. Zhu, S. Yamamoto, J. Matsui, T. Miyashita, M. Mitsuishi, RSC Advances, 2018, 8(15), 7963.

- 14. T. Furukawa, Phase Transitions, 1989, 18(3-4), 143.

- 15. J. Wang, H. Li, J. Liu, Y. Duan, S. Jiang, S. Yan, Journal of the American Chemical Society, 2003, 125(6), 1496.

- 16. A. J. Lovinger, Macromolecules, 1981, 14(2), 322.

- 17. S. J. Kim, J. Mohan, J. Lee, J. S. Lee, A. T. Lucero, C. D. Young, L. Colombo, S. R. Summerfelt, T. San, J. Kim, *Applied Physisc Letters*, **2018**, 112(17), 172902.

- 18. T. S. Böscke, J. Müller, D. Bräuhaus, U. Schröder, U. Böttger, Applied Physics Letters, 2011, 99(10), 102903.

- 19. S. J. Kim, J. Mohan, S. R. Summerfelt, J. Kim, *The Journal of The Minerals, Metals & Materials Society*, **2019**, 71, 246.

- 20. K. Ni, P. Sharma, J. Zhang, M. Jerry, J. A. Smith, K. Tapily, R. Clark, S. Mahapatra, S. Dutta, *IEEE Transactions on Electron Devices*, **2018**, 65(6), 2461.

- 21. M. H. Park, Y. H. Lee, H. J. Kim, Y. J. Kim, T. Moon, K. D. Kim, J. Müller, A. Kersch, U. Schroeder, T. Mikolajick, C. S. Hwang, *Advanced Materials*, 2015, 27(11), 1811.

- 22. P. Sharma, K. Tapily, A. K. Saha, J. Zhang, A. Shaughnessy, A. Aziz, G. L. Snider, S. Gupta, R. D. Clark, S. Datta, *IEEE Symposium on VLSI Technology*, 2017, T12-2, T154, DOI: 10.23919/VLSIT.2017.7998160.

- 23. P. D. Lomenzo, S. Jachalke, H. Stoecker, E. Mehner, C. Richter, T. Mikolajick, U. Schroeder, *Nano Energy*, **2020**, 74, 104733.

- 24. J. D. Anderson, J. Merkel, D. Macmahon, & S. Kurinec, "Evaluation of Si:HfO2 Ferroelectric Properties in MFM and MFIS Structures," *IEEE Journal of the Electron Devices Society*, vol. 6, pp. 525-534, **2018**.

- 25. S. Deng, Z. Jiang, S. Dutta, H. Ye, W. Chakraborty, S. Kurinec, & K. Ni, "Examination of the interplay between polarization switching and charge trapping in ferroelectric FET," in *IEEE International Electron Devices Meeting (IEDM)*, 2020, DOI: 10.1109/IEDM13553.2020.9371999.

- 26. E. Yurchuk, J. Müller, S. Müller, J. Paul, M. Pešić, R. van Bentum, U. Schroeder, T. Mikolajick, *IEEE Transactions on Electron Devices*, **2016**, 63(9), 3501.

- 27. H.-T. Lue, C.-J. Wu, T.-Y. Tesng, IEEE Transactions on Electron Devices, 2002, 49(10), 1790.

- 28. RIT Semiconductor & Microsystems Fabrication Laboratory. Available online: http://www.smfl.rit.edu (accessed on September 29<sup>th</sup>, 2023).

- 29. VICTORY Device User's Manual, Silvaco Inc., Santa Clara, CA, USA, 2015.

- 30. H. Bae, S. G. Nam, T. Moon, Y. Lee, S. Jo, D. H. Choe, S. Kim, K. -H. Lee, J. Heo, *IEEE International Electron Devices Meeting (IEDM)*, **2020**, 31.3.1, DOI: 10.1109/IEDM13553.2020.9372076.

- 31. D. Kuzum, J.-H. Park, T. Krishnamohan, H.-S. P. Wong, K. C. Saraswat, *IEEE Transactions on Electron Devices*, **2011**, 58(4), 1015.

- 32. Lombardi, C.; Manzini, S.; Saporito, A.; Vanzi, M. A physically based mobility model for numerical simulation of nonplanar devices. *IEEE Trans. Comput. Des. Integr. Circuits Syst.* **1988**, 7, 1164–1171.

- 33. A. I. Khan, A. Keshavarzi, S. Datta, Nature Electronics, 2020, 3, 588.

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.