**Article**

Not peer-reviewed version

# Effect of Noncircular Channel on Variation of Threshold Voltage in 3D NAND Flash Memory

<u>Donghyun Go</u>, <u>Gilsang Yoon</u>, Jounghun Park, Donghwi Kim, Jiwon Kim, <u>Jungsik Kim</u>\*, <u>Jeong-Soo Lee</u>\*

Posted Date: 3 August 2023

doi: 10.20944/preprints202308.0296.v1

Keywords: 3D NAND flash memory, noncircular cell, spike, TCAD simulation, threshold voltage variation, trapped charge

Preprints.org is a free multidiscipline platform providing preprint service that is dedicated to making early versions of research outputs permanently available and citable. Preprints posted at Preprints.org appear in Web of Science, Crossref, Google Scholar, Scilit, Europe PMC.

Copyright: This is an open access article distributed under the Creative Commons Attribution License which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Disclaimer/Publisher's Note: The statements, opinions, and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions, or products referred to in the content.

Article

# Effect of Noncircular Channel on Variation of Threshold Voltage in 3D NAND Flash Memory

Donghyun Go <sup>1</sup>, Gilsang Yoon <sup>1</sup>, Jounghun Park <sup>1</sup>, Donghwi Kim <sup>1</sup>, Jiwon Kim <sup>1</sup>, Jeong-Soo Lee <sup>1,\*</sup> and Jungsik Kim <sup>2,\*</sup>

- <sup>1</sup> Department of Electrical Engineering, Pohang University of Science and Technology, Pohang 37673, Korea; godhyun@postech.ac.kr (D.G.); ygs6233@postech.ac.kr (G.S.); mancity@postech.ac.kr (J.P.); kdh3879@postech.ac.kr (D.K.); jiwon104@postech.ac.kr (J.W.K.)

- <sup>2</sup> Department of Electrical Engineering, Gyeongsang National University, Jinju 52828, Gyeongnam, Korea

- \* Correspondence: ljs6951@postech.ac.kr (J.-S.L.), jungsik@gnu.ac.kr (J.K.); Tel.: +82-54-279-2380

**Abstract:** Variations in threshold voltage ( $V_{TH}$ ) and charge distributions in noncircular cells of three-dimensional (3D) NAND flash memory are investigated. The electric field difference in the circular and spike regions causes nonuniform trapped electron density in the charge trap layer (CTL) and influences the  $V_{TH}$  variation. Such less-trapped electron (LT) regions in CTL between the circular and spike regions exhibit a lower electric field during the program, resulting in a higher current flow through that region. For the two-spike cells, the charge distribution and  $V_{TH}$  variation are analyzed at different heights ( $H_{Spike}$ ) and angles between spikes. These irregular cells decrease  $V_{TH}$  as the  $H_{Spike}$  increases.

**Keywords:** 3D NAND flash memory; noncircular cell; spike; TCAD simulation; threshold voltage variation; trapped charge

# 1. Introduction

Three-dimensional (3D) vertically stackable structures are the mainstream in NAND flash memory. An increase in the word-line (WL) stack in 3D NAND is required to achieve high capacity and reduce bit costs [1–4]. The high-aspect-ratio (HAR) gate-all-around (GAA) polysilicon channel is effective in enhancing gate controllability and suppressing electrical fluctuations [5–8]. With GAA structures, triple-level and quadruple-level cells have been successfully commercialized in 3D NAND flash memory [9–12]. However, these multilevel operations are susceptible to threshold voltage ( $V_{TH}$ ) variation because of the narrower margins in the programmed  $V_{TH}$  distribution compared with those of single-level cells [13]. In addition, the HAR structure significantly increases process complexity, affecting electrical performance and reliability [14–17]. A tapered structure is typically observed in etched HAR holes, from top to bottom [18-23]. The tapered shape may primarily affect the program/erase (P/E) window of each cell along the WL string [24-25]. Simultaneously, a microtrench structure frequently forms close to the bottom region of the tapered etch hole. The cross-section of the microtrench generates a noncircular channel with spike-wise deformation, which can further degrade the uniformity of the electrical characteristics [26-27]. Although the electrical behavior of noncircular channel shape has been reported in some studies [28], it is not clear how the spike affects electrical properties of the cell and how  $V_{TH}$  is determined by the spike. In this study, the distributions of trapped electrons and inversion electron density were investigated for noncircular cells with single or two spikes using Synopsys Sentaurus technology computer-aided design (TCAD). The channel current density and V<sub>TH</sub> variations were correlated with the spike height and angle between spikes.

2

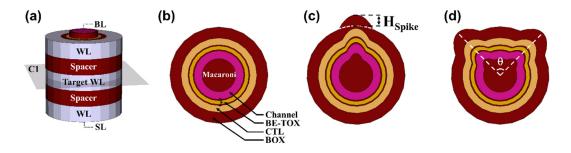

Figure 1a shows a schematic of the 3D NAND flash memory with three WL cells. The radial structure of a cell is composed of a metal gate, blocking oxide (BOX), charge trap layer (CTL), bandengineered tunneling layer (BE-TOX) consisting of O1/N1/O2, polysilicon (poly-Si) channel, and macaroni oxide. Figure 1b,c,d show the cross-sectional schematics of the circular cell (C-cell), single-spike cell (SSC), and two-spike cell (TWSC), respectively. Parameter  $\theta$  was introduced to analyze the effect of the distance between spikes in the TWSC cells, as shown in Figure 1d. The height (Hspike) and angle ( $\theta$ ) between the two spikes varied from 5 to 15 nm and 20° to 135°, respectively.

**Figure 1.** (a) Schematic of 3D NAND flash memory with three WL. Cross-sectional (C1 plane) of (b) circular cell (C-cell) and noncircular cells with (c) single spike and (d) two spikes at an angle  $\theta$  in between.

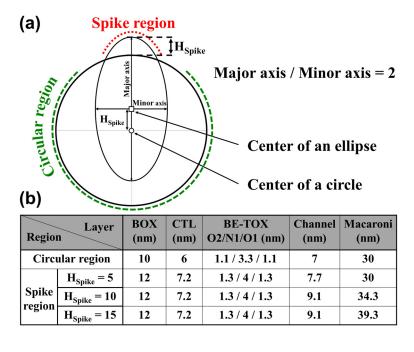

Figure 2 depicts a spike used in the simulation. The spike region was generated by overlapping a conventional circle and an ellipse, as shown in Figure 2a. The center of the ellipse is away from the center of the circle by the H<sub>Spike</sub>, inducing a spike shape in each layer, as shown in Figure 2b. The thickness of each layer in spike region was set to be thicker than in circular region.

**Figure 2.** Description of noncircular cell: (a) Overlapped circle and ellipse for creating noncircular cell and (b) detailed values for the thickness of each layer in circular and spike region.

The Hurkx band-to-band tunneling model for gate-induced drain leakage, high-field-saturation mobility model in the channel were adopted. The quantum confinement effect was also incorporated to accurately analyze the channel current. The oxide layers in the BE-TOX and BOX layers were assumed to have no defects. Transient simulations with a nonlocal tunneling model were performed to simulate the P/E operation. Carriers in the CTL were transported according to the drift-diffusion model, and Shockley–Read–Hall (SRH) model was applied to the capture or emission of carriers into traps. The material properties of the CTL used in this study are listed in Table 1. Silicon nitride has gaussian energy distribution for both electron and hole trap. The spatial distribution of the traps was set constant as we focused on the change in electrical properties due to the noncircular channel shape.

| <b>Table 1.</b> Material | properties o | t silicon nitride | used in CTL. |

|--------------------------|--------------|-------------------|--------------|

|                          |              |                   |              |

| Parameter                              | Value                              |  |

|----------------------------------------|------------------------------------|--|

| Bandgap                                | 5.0 eV                             |  |

| Peak Energy Level of Electron Trap     | $1.0\mathrm{eV}$                   |  |

| Standard Deviation of Electron Trap    | 0.1 eV                             |  |

| Total Density of Electron Trap $(N_T)$ | $5 \times 10^{19}  \text{cm}^{-3}$ |  |

| Peak Energy Level of Hole Trap         | $2.5~\mathrm{eV}$                  |  |

| Standard Deviation of Hole Trap        | 0.1 eV                             |  |

| Total Density of Hole Trap             | $5 \times 10^{18}  \text{cm}^{-3}$ |  |

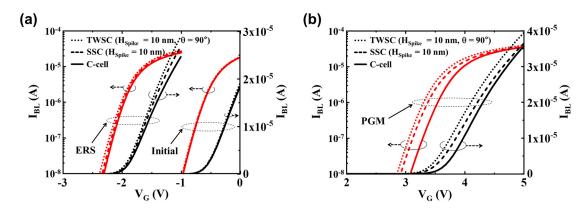

The program (PGM), erase (ERS), and read conditions were  $V_{PGM} = 16 \text{ V} / t_{PGM} = 100 \text{ µs}$ ,  $V_{ERS} = -16 \text{ V} / t_{ERS} = 1 \text{ ms}$ ,  $V_{PASS} = 5 \text{ V} / V_{BL} = 0.05 \text{ V}$ , respectively. Figure 3 shows the bit-line current ( $I_{BL}$ ) vs. gate voltage ( $V_G$ ) curves of the C-cell and noncircular cells at the initial, ERS, and PGM states using 3D TCAD simulation.  $V_{TH}$  was extracted using an  $I_{BL}$  of 2  $\mu$ A. The  $V_{TH}$  values of the C-cell were -0.5, -2, and 3.67 V in the initial, ERS, and PGM states, respectively. For the SSC and TWSC cells, the  $V_{TH}$  in the initial and ERS states were the same as or less different from  $V_{TH}$  in the C-cell as shown in Figure 3a. However, in the PGM state, a negative shift of  $V_{TH}$  was clearly observed for noncircular cells, owing to structural deformation as shown in Figure 3b. The SSC and TWSC cells were simulated with various  $H_{Spike}$  and  $\theta$  values to further reveal their electrical behaviors.

**Figure 3.** Bit-line current vs. gate voltage (I<sub>BL</sub>-V<sub>G</sub>) curves plotted on the log and linear scales: (a) Initial, ERS and (b) PGM states for C-cell, SSC (H<sub>Spike</sub> = 10 nm), and TWSC (H<sub>Spike</sub> = 10 nm,  $\theta$  = 90°).

4

### 3.1. SSC Characteristics

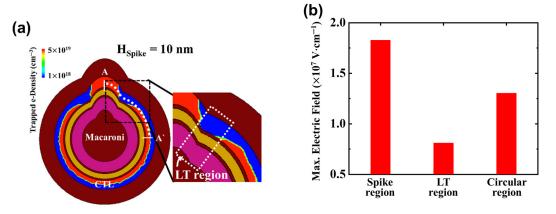

Figure 4a shows the distribution of the trapped electron density (e-density) in the CTL in the PGM state of the SSC. A gradual decrease in the e-density was observed in the region between the spike and circular regions. The less-trapped electron (LT) region is newly defined as where the e-density decreases by 10% of the circular region. Figure 4b shows the maximum electric field (Emax) on the O1 layer of BE-TOX at  $V_{PGM}$  = 16 V in the SSC. The peak in the spike region showed the highest electric field compared with the LT and circular regions. The concave shape in the LT region could reduce Emax and induce smaller trapped charges in the LT region.

**Figure 4.** (a) Cross-sectional distribution of trapped electrons in CTL in PGM state and (b) maximum vertical electric field extracted in O1 layer of BE-TOX during the PGM operation.

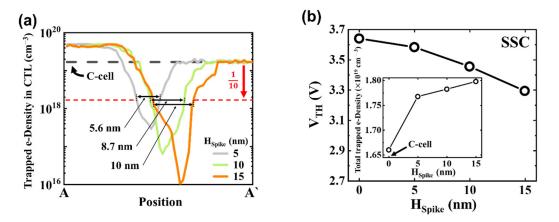

Figure 5a shows the distribution of the average trapped e-density in the PGM state along the A-A` perimeter with different H<sub>Spike</sub> values. The average e-density was obtained by radially integrating the overall charge at each position in the CTL. For the C-cell, a uniform trapped e-density of  $1.6 \times 10^{19}$  cm<sup>-3</sup> was obtained. For the SSC cell, a fully trapped electron of  $5 \times 10^{19}$  cm<sup>-3</sup> was obtained in the spike region. As H<sub>Spike</sub> increased, the minimum trapped e-density decreased, and the LT region expanded from 5.6 to 10 nm. The distribution of the trapped e-density depended on the H<sub>Spike</sub> values, influencing the current flow in the channel and the corresponding  $V_{TH}$  values. A lower  $V_{TH}$  is associated with a reduction in the trapped e-density in the CTL of the circular structure. An increase in H<sub>Spike</sub> lowered  $V_{TH}$ , although it increased the trapped e-density in the SSC, as shown in Figure 5b.

**Figure 5.** SSC: (a) Concentration of trapped electrons in CTL with different  $H_{Spike}$  values along A-A` perimeter. (b)  $V_{TH}$  of C-cell ( $H_{Spike} = 0$ ) and SSC in PGM state with different  $H_{Spike}$  values. Inset: Total trapped electron density vs.  $H_{Spike}$  value.

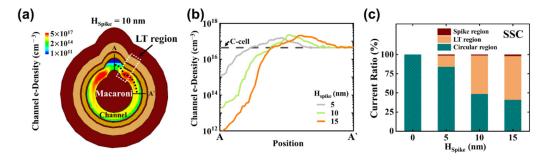

Figure 6a shows the cross-sectional distribution of channel electrons in the SSC with Hspike = 10 nm at  $V_{read} = V_{TH}$ . Because the trapped e-density was high in the spike region, the inversion electron in that region was locally smaller than in other channel regions. However, the LT region had a smaller trapped e-density; thus, more channel electrons and a higher current density were induced. Figure 6b shows the average channel e-density along the A-A` perimeter with different Hspike values. The calculated channel e-density of the C-cell was as high as  $4.6 \times 10^{16}$  cm<sup>-3</sup>. The e-density peak coincided with the minimum trapped e-density in CTL (Figure 5a). As Hspike increased, the peak value increased from  $1.6 \times 10^{17}$  to  $2.1 \times 10^{17}$  cm<sup>-3</sup>. Figure 6c shows the ratio of the currents flowing in the three regions to the total channel current (at  $V_{read} = V_{TH}$ ) in the SSC in the PGM state. At Hspike = 15 nm, the calculated normalized perimeter was as high as 70% for the circular region, 18% for the spike region, and 12% for the two LT regions, respectively. The intensity of current in the LT region became dominant with increasing Hspike. For the SSC with Hspike = 15 nm, 57% of the total current flowed through the two LT regions. During a PGM operation, a reduced electric field in the LT region induced a lower trapped e-density, which again increased the channel e-density.

**Figure 6.** SSC: (a) Cross-sectional distribution of channel electrons with Hs<sub>pike</sub> = 10 nm at  $V_{read} = V_{TH}$  and (b) concentration of channel electrons with different Hs<sub>pike</sub> along A-A` perimeter. (c) Ratio of current flowing through circular, LT, and spike regions to total channel current (I<sub>BL</sub> = 2  $\mu$ A) with different Hs<sub>pike</sub> values.

### 3.2. TWSC Characteritsics

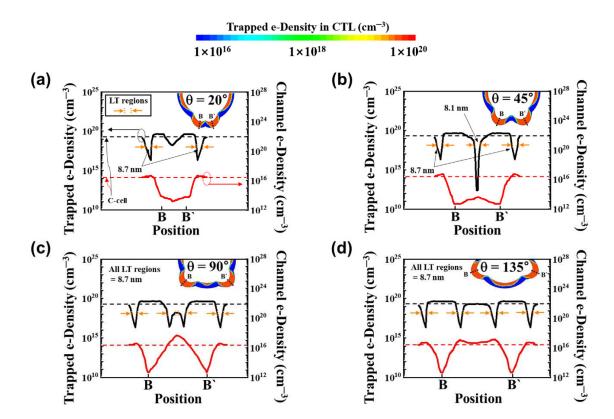

Figure 7 shows the distributions in the trapped e-density in CTL and channel e-density at  $V_{read} = V_{TH}$  along the B-B` perimeter between two spikes in the PGM state. The angle between the spikes varied from 20° to 135° with H<sub>Spike</sub> = 10 nm. The cross-sectional distribution of the trapped electrons in the CTL is shown in the insets. At  $\theta = 135^{\circ}$ , two LT regions were observed in the B-B' region where the minimum trapped e-density of  $2.1 \times 10^{16}$  cm<sup>-3</sup> and the peak channel e-density of  $1.3 \times 10^{17}$  cm<sup>-3</sup> (Figure 7d). At  $\theta = 90^{\circ}$ , two LT regions were close and the minimum trapped e-density is unchanged, but peak channel e-density increased to  $5 \times 10^{17}$  cm<sup>-3</sup> (Figure 7c). As the angle decreased, the LT regions overlapped, and at  $\theta = 45^{\circ}$ , the LT region with the minimum trapped e-density of  $2.5 \times 10^{12}$  cm<sup>-3</sup> and the peak channel e-density of  $3 \times 10^{13}$  cm<sup>-3</sup> was formed (Figure 7b). Both  $\theta = 45^{\circ}$  and  $\theta = 20^{\circ}$ , the B-B' region between two spikes showed a negligible electron density compared with the circular region, suggesting that the channel current mostly flowed through the circular region and the two LT regions outside B-B' (Figure 7a).

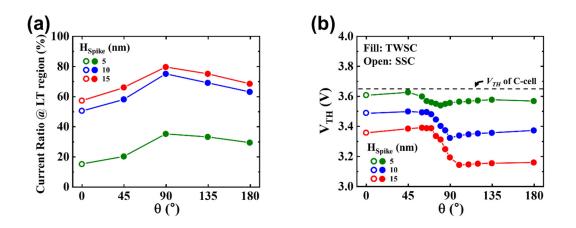

Figure 8a shows the current ratio flowing in the LT regions as functions of  $H_{Spike}$  and  $\theta$  for the TWSCs. The channel current primarily flowed in the LT and circular regions and was lower than 1% in the spike regions. The current ratio was maximum at  $\theta = 90^{\circ}$ ; it significantly increased with a high  $H_{Spike}$  value, increasing from 40% for  $H_{Spike} = 5$  nm to 80% for  $H_{Spike} = 15$  nm. Figure 8b shows the  $V_{TH}$  variation for TWSCs with different  $H_{Spike}$  and  $\theta$  values. The dashed line represents the  $V_{TH}$  value of the C-cell. All the SSCs and TWSCs showed a lower  $V_{TH}$  than the C-cell, and a higher spike induced a more significant decrease in  $V_{TH}$ . For the TWSC cells at approximately  $\theta = 90^{\circ}$ ,  $V_{TH}$  reduction was observed because of the increased channel e-density at that angle (Figure 7c).

**Figure 7.** TWSC with  $H_{Spike}$  = 10 nm and  $\theta$  for (a) 20°, (b) 45°, (c) 90°, and (d) 135° in PGM state. The concentration of trapped electrons in CTL and channel electrons with different  $\theta$  values along B-B' perimeter are shown. Inset: Corresponding cross-sectional distribution of trapped electrons in CTL.

**Figure 8.** (a) Ratio of current flowing through LT region to total channel current (I<sub>BL</sub> = 2  $\mu$ A) with H<sub>Spike</sub> and  $\theta$  of TWSCs and (b)  $V_{TH}$  in PGM state of TWSCs depending on H<sub>Spike</sub> and  $\theta$  of spike.

## 4. Conclusions

We investigated the impact of a noncircular channel with spikes on the  $V_{TH}$  characteristics using 3D TCAD simulations in vertical NAND flash memory. The region with lower trapped charges in the CTL between the spike and circular regions expanded as the spike height increased. SSCs and TWSCs showed lower  $V_{TH}$  than the C-cell. In particular, for the TWSCs, the  $V_{TH}$  variation became severe at  $\theta = 90^{\circ}$  as the spike height increased.

**Author Contributions:** Conceptualization, D.G., and J.W.K.; methodology, J.P., D.K., and G.S.Y.; writing-original draft preparation, D.G., J.K., and J.-S.L.; writing-review & editing, D.G., J.K., and J.-S.L.; supervision, J.-S.L.

**Funding:** This work was supported by National R&D Program through the National Research Foundation of Korea (NRF) funded by Ministry of Science and ICT (2020M3H2A1078045) and by Samsung POSTECH Research Center (SPRC) funded by Samsung Electronic.

**Acknowledgments:** The EDA tool was supported by the IC Design Education Center.

Conflicts of Interest: The authors declare no conflict of interest.

### References

- 1. K. Ishimaru, "Future of non-volatile memory-from storage to computing," in IEDM Tech. Dig., Dec. 2019, pp. 1.3.1–1.3.6, doi: 10.1109/IEDM19573.2019.8993609.

- L. Heineck and J. Liu, "3D NAND Flash Status and Trends,"," in IEEE 14th Int. Memory Workshop (IMW), May 2022, pp. 1-4, doi: 10.1109/IMW52921.2022.9779282.

- 3. J. Choe, "Memory Technology 2021: Trends & Challenges," 2021 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), 2021, pp. 111-115, doi: 10.1109/SISPAD54002.2021.9592547.

- 4. R. Shirota, "3D-NAND flash memory and technology," in Proc. Adv. Non-Volatile Memory Storage Technol., Jan. 2019, pp. 283–319, doi: 10.1016/b978-0-08-102584-0.00009-7.

- 5. J. Y. Seo, Y. Kim, S. H. Park, W. Kim, D.-B. Kim, J.-H. Lee, H. Shin, and B.-G. Park, "Investigation into the effect of the variation of gate dimensions on program characteristics in 3D NAND flash array," 2012 IEEE Silicon Nanoelectronics Workshop (SNW), 2012, pp. 1-2, doi: 10.1109/SNW.2012.6243320.

- 6. A. Silvagni, "3D NAND Flash Based on Planar Cells," Computers, vol. 6, no. 4, p. 28, Oct.2017.

- 7. A. Goda, "3-D NAND Technology Achievements and Future Scaling Perspectives," in IEEE Trans. Electron Devices, vol. 67, no. 4, pp. 1373-1381, April 2020, doi: 10.1109/TED.2020.2968079.

- 8. S. Barraud et al., "7-Levels-Stacked Nanosheet GAA Transistors for High Performance Computing," 2020 IEEE Symp. VLSI Technol., 2020, pp. 1-2, doi: 10.1109/VLSITechnology18217.2020.9265025.

- S. Liang et al., "An Empirical Study of Quad-Level Cell (QLC) NAND Flash SSDs for Big Data Applications," 2019 IEEE International Conference on Big Data (Big Data), 2019, pp. 3676-3685, doi: 10.1109/Big-Data47090.2019.9006406.

- N. Papandreou et al., "Reliability of 3D NAND flash memory with a focus on read voltage calibration from a system aspect," 2019 19th Non-Volatile Memory Technol. Symp. (NVMTS), 2019, pp. 1-4, doi: 10.1109/NVMTS47818.2019.8986221.

- 11. N. Papandreou et al., "Characterization and Analysis of Bit Errors in 3D TLC NAND Flash Memory," 2019 IEEE Int. Rel. Phys. Symp. (IRPS), 2019, pp. 1-6, doi: 10.1109/IRPS.2019.8720454.

- 12. K. Mizoguchi, T. Takahashi, S. Aritome, and K. Takeuchi, "DataRetention Characteristics Comparison of 2D and 3D TLC NAND Flash Memories," in 2017 IEEE International Memory Workshop (IMW), pp. 1–4.

- 13. M. Fukuchi, S. Suzuki, K. Maeda, C. Matsui and K. Takeuchi, "BER Evaluation System Considering Device Characteristics of TLC and QLC NAND Flash Memories in Hybrid SSDs with Real Storage Workloads," 2021 IEEE Int. Symp. Circuits and Systems (ISCAS), 2021, pp. 1-4, doi: 10.1109/ISCAS51556.2021.9401203.

- 14. T. Reiter, X. Klemenschits and L. Filipovic, "Impact of plasma induced damage on the fabrication of 3D NAND flash memory," Solid-State-Electron., vol. 192, 2022, 108261.

- 15. J. Kang et al., "Highly Reliable Cell Characteristics with CSOB(Channel-hole Sidewall ONO Butting) Scheme for 7th Generation 3D-NAND," 2021 IEEE International Electron Devices Meeting (IEDM), 2021, pp. 10.1.1-10.1.4, doi: 10.1109/IEDM19574.2021.9720643.

- 16. Y. -A. Chung et al., "Study of Plasma Arcing Mechanism in High Aspect Ratio Slit Trench Etching," 2019 30th Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC), 2019, pp. 1-4, doi: 10.1109/ASMC.2019.8791770.

- 17. K. Parat and A. Goda, "Scaling Trends in NAND Flash," 2018 IEEE International Electron Devices Meeting (IEDM), 2018, pp. 2.1.1-2.1.4, doi: 10.1109/IEDM.2018.8614694.

- 18. A. Goda and K. Parat, "Scaling directions for 2D and 3D NAND cells," in IEDM Tech. Dig., Dec. 2012, pp. 2.1.1–2.1.4, doi: 10.1109/ IEDM.2012.6478961.

- 19. H. Kim, S. -J. Ahn, Y. G. Shin, K. Lee and E. Jung, "Evolution of NAND Flash Memory: From 2D to 3D as a Storage Market Leader," 2017 IEEE Int. Memory Workshop (IMW), 2017, pp. 1-4, doi: 10.1109/IMW.2017.7939081.

- 20. Y. Yanagihara, K. Miyaji and K. Takeuchi, "Control Gate Length, Spacing and Stacked Layer Number Design for 3D-Stackable NAND Flash Memory," 2012 4th IEEE Int. Memory Workshop, 2012, pp. 1-4, doi: 10.1109/IMW.2012.6213656.

8

- 21. K. Ko, J. K. Lee and H. Shin, "Variability-Aware Machine Learning Strategy for 3-D NAND Flash Memories," in IEEE Trans. Electron Devices, vol. 67, no. 4, pp. 1575-1580, April 2020, doi: 10.1109/TED.2020.2971784.

- 22. U. M. Bhatt, S. K. Manhas, A. Kumar, M. Pakala and E. Yieh, "Mitigating the Impact of Channel Tapering in Vertical Channel 3-D NAND," in IEEE Trans. Electron Devices, vol. 67, no. 3, pp. 929-936, March 2020, doi: 10.1109/TED.2020.2967869.

- 23. J. G. Lee, W. J. Jung, J. H. Park, K. -H. Yoo and T. W. Kim, "Effect of the Blocking Oxide Layer With Asymmetric Taper Angles in 3-D NAND Flash Memories," in IEEE Journal of the Electron Devices Society, vol. 9, pp. 774-777, 2021, doi: 10.1109/JEDS.2021.3104843.

- 24. K. T. Kim, S. W. An, H. S. Jung, K. Yoo and T. W. Kim, "The Effects of Taper-Angle on the Electrical Characteristics of Vertical NAND Flash Memories," in IEEE Electron Device Lett., vol. 38, no. 10, pp. 1375-1378, Oct. 2017, doi: 10.1109/LED.2017.2747631

- 25. U. M. Bhatt, S. K. Manhas, A. Kumar, M. Pakala, and E. Yieh, "Mitigating the impact of channel tapering in vertical channel 3-D NAND," in IEEE Trans. Electron Devices, vol. 67, no. 3, pp. 929–936, Mar. 2020.

- 26. P. Nowakowski, M. Ray, P. Fischione and J. Sagar, "Top-down delayering by low energy, broad-beam, argon ion milling a solution for microelectronic device process control and failure analyses", 28th Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC), 2017, pp. 95-101.

- 27. C. Han, Z. Wu, C. Yang, L. Xie, B. Xu, L. Liu, Z. Yin, L. Jin and Z. Huo, "Influence of accumulated charges on deep trench etch process in 3D NAND memory," Semicond. Sci. Technol., vol. 35, no. 4, 2020, Art. no. 045003, doi: 10.1088/1361-6641/ab73e7.

- 28. A. Fayrushin, H. Liu, A. Mauri, G. Carnevale, H. Cho and D. Mao, "Numerical Study of Non-Circular Pillar Effect in 3D-NAND Flash Memory Cells," 2019 IEEE Workshop on Microelectronics and Electron Devices (WMED), 2019, pp. 1-4, doi: 10.1109/WMED.2019.8714183.

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.