**Article**

Not peer-reviewed version

# An Analytical Model of Dynamic Power Losses in eGaN HEMT Power Devices

Jianming Lei , Yangyi Liu , Wenbo Zhang , Zhanmin Yang , Yalin Chen ,  $\underline{\text{Rui Wang}}$  ,  $\underline{\text{Dunjun Chen}}^*$  , Liang Xu , Jing Yu

Posted Date: 12 July 2023

doi: 10.20944/preprints202307.0804.v1

Keywords: AlGaN/GaN HEMT device; CCM; DCM; dynamic on-resistance; dynamic power loss

Preprints.org is a free multidiscipline platform providing preprint service that is dedicated to making early versions of research outputs permanently available and citable. Preprints posted at Preprints.org appear in Web of Science, Crossref, Google Scholar, Scilit, Europe PMC.

Copyright: This is an open access article distributed under the Creative Commons Attribution License which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Disclaimer/Publisher's Note: The statements, opinions, and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions, or products referred to in the content.

Article

# An Analytical Model of Dynamic Power Losses in eGaN HEMT Power Devices

Jianming Lei <sup>1</sup>, Yangyi Liu <sup>1</sup>, Wenbo Zhang <sup>1</sup>, Zhanmin Yang <sup>1</sup>, Yalin Chen <sup>1</sup>, Rui Wang <sup>2</sup>, Dunjun Chen <sup>2,\*</sup>, Liang Xu <sup>3</sup> and Jing Yu <sup>3</sup>

- <sup>1</sup> The School of Electrical Engineering, Nanjing Vocational University of Industry Technology, Nanjing 210023, China; jmlei82@niit.edu.cn

- <sup>2</sup> The Key Laboratory of Advanced Photonic and Electronic Materials, School of Electronic Science and Engineering, Nanjing University, Nanjing 210093, China

- <sup>3</sup> The Department of R&D, Zhongtian Broadband Technology Co., Ltd, Nantong 226009, China

- \* Correspondence: djchen@nju.edu.cn

Abstract: In this work, we present an analytical model of dynamic power losses for enhancement-mode AlGaN/GaN high-electron-mobility transistor power devices (eGaN HEMTs). To build this new model, the dynamic on-resistance (Rdson) is first accurately extracted by our extraction circuit based on a double-diode isolation (DDI) method for a high operating frequency up to 1 MHz and a large drain voltage up to 600 V, thus the unique problem of an increase in the dynamic Rdson is presented. Then the impact of the current operation mode on the on/off transition time is evaluated by a dual-pulse-current-mode test (DPCT) which including a discontinuous conduction mode (DCM) and a continuous conduction mode (CCM), thus the transition time is revised for different current mode. Afterward the discrepancy between the drain current and the real channel current is qualitative investigated by an external shunt capacitance (ESC) method, thus the losses due to device parasitic capacitance are also taken into account. After these improvements, the dynamic model will be more compatible for eGaN HEMTs. Finally, the dynamic power losses calculated by this model are verified to be in good agreement with experimental results. Based on this model, we propose a superior solution with quasi-resonant mode (QRM) to achieve lossless switching and accelerate switching speed.

Keywords: AlGaN/GaN HEMT device; CCM; DCM; dynamic on-resistance; dynamic power loss

#### 1. Introduction

Enhancement-mode AlGaN/GaN high electron mobility transistor power devices (eGaN HEMTs) are the most promising candidates for next-generation power devices. In such devices, III-V materials have several merits due to their wide bandgap energy, high critical breakdown electric field, high electron mobility and capability [1,2], and polarization effect [3]. Because of these advantages, a high-frequency (high-fs) converter operating in the range of 1-5 MHz based on eGaN HEMTs can be readily realized. Although high-fs operation can help reduce converter size, it will generate more challenges with respect to dynamic power loss. Thus, building an analytical dynamic power loss model for an eGaN-based high- fs switch becomes important for prototype application circuit design.

Recently, some state-of-the-art dynamic power loss models for eGaN HEMTs have been proposed. Wang et al. developed two analytical loss models based on detailed parasitic parameters for high-voltage and low-voltage GaN eHEMTs [4,5]. In these models, the gate charge ( $Q_8$ ) and output charge ( $Q_{oss}$ ) instead of the voltage-dependent capacitance were used to improve the nonlinear characteristics. Shen et al. fully accounted for the effects of parasitic parameters and transconductance [6]. Hou et al. and Guacci et al. investigated the losses caused by output capacitance in a hard switch and soft switch, respectively [7,8]. However, these models did take into account the impact on device loss from some aspects instead of fully evaluated, the results accuracy is affected.

Chen et al. presented a complete analytical loss model for low-voltage eGaN HEMTs, which a piecewise model was employed [9]. Piecewise models are also usually used to evaluate the dynamic

2

power losses for Si- and SiC-based metal-oxide-semiconductor field-effect transistors (MOSFETs) [10–15]. These models are carefully considered and allow accurate evaluation of device power losses. However, these models did not take into account the exclusive dynamic physical characteristics of eGaN HEMTs, such as a strong defect trapping-effect, increased dynamic on-resistance (Rdson), and no reverse body diode. Therefore, these analytical models need to be modified for eGaN HEMTs. In addition, the effect of current operation mode on device transition time and loss is not considered in all known device loss models.

To improve the dynamic power loss model of eGaN HEMTs, we propose three experimental methods according to the practical application of devices in high-fs circuits, such as a double-diode isolation (DDI) method, a dual-pulse-current-mode test (DPCT) method, and an external shunt capacitance (ESC) method. Then, the dynamic  $R_{dson}$  is accurately extracted in a high operating frequency (fs) up to 1 MHz and a high drain voltage up to 600 V; the effect of current operation mode on transition time is revealed for the first time and thus the loss of the device is affected; and the real channel current (Ich) is qualitative modified compared to the drain current ( $I_{drain}$ ) we can directly test in device drain side. Afterward the dynamic power loss of eGaN HEMTs is carefully described by a modified 12-segment piecewise model. Finally, we propose a quasi-resonant mode (QRM) with a low off-state drain voltage ( $V_{ds\_off}$ ), zero turn-on current, and a relatively large on-state peak current for a lossless design and fast transit speed in power switches.

# 2. Background And Methodology

#### 2.1. A. Parameters and Traditional Power Loss Model

```

V_{gs}: gate voltage.

V_{drive\_H}: gate voltage in high level.

V_{drive\_L}: gate voltage in low level.

V_{\scriptscriptstyle mr} : Miller gate voltages during the turn-on transition.

V_{mf}: Miller gate voltages during the turn-off transition.

V_{\rm th} : threshold voltage.

t_{\scriptscriptstyle on} : total turn-on time during the turn-on transition.

t_{dr}: turn-on delay time.

t_{cr}: turn-on current rise time.

t_{vf}: turn-on voltage fall time.

t_{mr}: turn-on Miller rise time.

t_{gr}: turn-on gate voltage rise remaining time.

: total turn-off time during the turn-off transition.

t_{df}: turn-off delay time.

t_{mf}: Miller fall time.

: voltage rise time.

: current fall time.

```

: voltage continuous rise time.

$Q_{gs}$ : gate-source charge.

$Q_{\rm gd}$  : gate-drain charge.

$Q_{od}$  : overcharge gate charge.

${Q_{\! ext{g}} \over ext{g}}$  : total gate charge, equal to the sum of Q $_{\! ext{gs}}$ , Q $_{\! ext{gd}}$ , and Q $_{\! ext{od}}$ .

$I_{d}$ : drain-source current.

$I_{\mathit{sta}}$  : start drain-source current at turn-on transition.

$I_{\it pk}$  : peak drain-source current during on-state.

$V_{ds}$ : drain-source voltage.

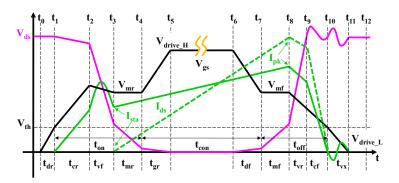

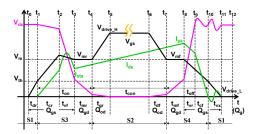

In the piecewise model, the operating sequence of the device is shown in Figure 1. In particular, the device is usually connected to a choke or a transformer in power switches, thus the value of  $I_{sta}$  indicate the current mode of device. ( $I_{sta}$ =0) denotes the device operate in discontinuous conduction mode (DCM), while ( $I_{sta}$ >0) denotes the device operate in continuous conduction mode (CCM).

A traditional calculation formula for high-fs power losses of device is given by [16]

$$P_{sw} = \frac{1}{2} I_{ds} V_{ds} (t_{on} + t_{off}) f_s + \frac{1}{2} C_{oss} V_{ds}^2 f_s + K_{th} I_{dson\_rms}^2 R_{dson} + Q_g V_{gs} f_s$$

(1)

where  $I_{dson\_rms}$  is the on-state drain-source current in root-mean-square (RMS) value,  $K_{th}$  is the temperature coefficients related to  $R_{dson}$ . The first term in Eq. (1) occurs in the crossing area of  $I_{ds}$  and the  $V_{ds}$ , while the second term is the output capacitor energy dissipated in the device during the turn-on transition. Then, the third and fourth terms are the conductive loss and driving loss, respectively. Equation (1) is approximate, as it does not take into account the problem of a dynamic  $R_{dson}$  increase, the impact of  $I_{drain}$  on the transition time, and the discrepancy between  $I_{drain}$  and the real channel current.

Figure 1. Piecewise timing diagram of the power switching devices.

# 2.2. B. Experimental Circuit and Method

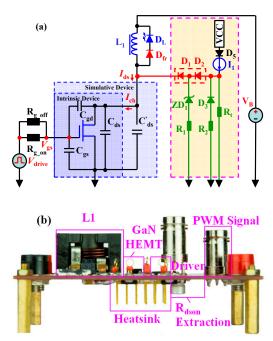

A switching circuit with a floating buck-boost topology is employed to analyze the switching processes, as shown in Figure 1a. In this circuit, an HEMT device is used and shown with a simple three-capacitor model that includes the parasitic capacitors C<sub>gs</sub>, C<sub>gd</sub> and C<sub>ds</sub>. The pulse width modulation (PWM) is produced by a pulse generator (81150A, Keysight Inc.) with a maximum PWM of 120 MHz, and is amplified by a gate driver (SI8271GB), which has a 1.8 A peak source current and a 4.0 A peak sink current, D<sub>1</sub> is selected as a SiC diode (C3D10065E) rated at 15 A / 650 V, which is used to reduce the reverse recovery problem. The parasitic resistor and parasitic inductor are ignored to simply study the important role of the parasitic capacitors at a relatively high-f<sub>s</sub> that is smaller than 30 MHz. Then, various voltages and PWM in DCM and CCM are applied to elucidate the switching processes and the production of dynamic power losses.

Figure 1b shows our novel dynamic  $R_{\text{dson}}$  extraction circuit [17]. In this design, the model of the gate driver is SI8271GB, and  $D_1$  and  $D_2$  (1 A/1k V UF4007) are used in series to isolate the high off-

4

state voltage of the eGaN HEMTs. Then, the dynamic Rdson of the eGaN HEMTs can be easily extracted. Diodes in series make it possible to test the real-time forward voltage drop (V<sub>F</sub>) of D<sub>2</sub> in a low-voltage range and then to precisely estimate V<sub>F</sub> of D<sub>1</sub> in the same forward current. In addition, diodes in series will reduce the parasitic capacitor by half, which is very helpful to the high-fs response of the extraction circuit. We call this method a DDI method. Moreover, ZD1 and D3 are freewheeling diodes and ZD<sub>1</sub> is also a positive clamping diode. These two diodes are a general 5 V Zener ZD<sub>1</sub> and a general small signal diode D<sub>3</sub> (1N4148) with 75 V/150 mA. All of the functional diodes including  $D_1$ ,  $D_2$ ,  $ZD_1$  and  $D_3$  are specially selected with a very low parasitic capacitance, which will improve the high-fs response of the extraction circuit to several MHz. I1 is a constant-current source of only several mA, so it cannot produce a temperature problem and an extra self-heating effect. It consists of a constant-current diode, which is actually a junction field transistor with a gatesource short connection. Therefore, I<sub>1</sub> can achieve an excellent constant current over a wide operating voltage range. Rt provides a minimum load for I1 and suppresses the voltage spike at point B. An isolated low-voltage probe (P2221 from Keysight Inc.) with a 1:1 attenuation can be used to test V<sub>F</sub> of D<sub>2</sub> and the voltage at point B. The low-voltage probe with a 1:1 attenuation will not amplify the background noise and operate in a low-voltage range, so it can obtain an improved test accuracy.

We build the above switching circuit and extraction circuit with one printed circuit board (PCB), as shown in Figure 1c.

**Figure 2.** Lumped equivalent switching circuit with a floating buck-boost topology (a), and a photograph of the assembled printed circuit board (b).

#### 2.3. C. Qualitative Method to Discover the Channel Behavior

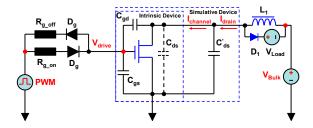

Since we cannot perform the measurements inside the HEMT device directly, we propose a new evaluation method by employing an extended parallel capacitor  $C_{ds}$ , as shown in Figure 3. In this lumped circuit, the intrinsic capacitor  $C_{ds}$  is assumed to not exist, and the extended capacitor  $C_{ds}$  outside the device is assumed to be the intrinsic capacitor. Therefore, the channel current (Ichannel) and Idrain can be measured directly and separately by an oscilloscope and current probes. Although an extra parallel capacitor will lead to an increase in the measured Idrain and Ichannel, this qualitative method can be used to assess the difference between these two currents, and thereby, the cause of the discrepancy can be located. After understanding this reason, the resulting loss effect on the eGaN HEMT device can be further quantified by an analytical method. In the analytical method, the additional  $C_{ds}$  is no longer required, therefore, the  $C_{ds}$  does not materially affect the device losses.

**Figure 3.** The lumped simulation circuit with an extra parasitic capacitor.

#### 3. Extraction of the Dynamic Rdson

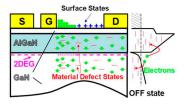

It is well known that a high V<sub>ds\_off</sub> will cause surface- and buffer-related trapping processes, which will lead to a larger dynamic R<sub>dson</sub> compared to the direct current (DC) R<sub>dson</sub> (R<sub>dson\_DC</sub>) [18,19]. Figure 4 illustrates the mechanism of the increase in the dynamic R<sub>dson</sub> induced by the trapping effect. The high electric field helps the electrons escape from the GaN well, and then these electrons are captured by traps or some of the surface states that are activated by a high electric field. When removing the electric field, these trapped electrons cannot be released to the well instantaneously. The reason for the slow return of electrons is that the trapping time of electrons in the off-state is on the order of ns, whereas the detrapping time of electrons in the on-state is on the order of second [20,21]. Thus, trapped electrons accumulate and worsen the device performance at a high f<sub>s</sub>. Meanwhile, electrons migrate from the gate to the gate-drain side adjacent surface to form a virtue gate; hence, the number of electrons in the access region decreases. The decreasing number of electrons in the drift region will result in a large dynamic R<sub>dson</sub> [22,23].

Figure 4. Mechanism for the dynamic Rdson.

In the circuit of Figure 1b, the current  $I_1$  flows partly through  $R_t$  and partly through the HEMT device, and the voltage of point B ( $V_B$ ) can be tested by the voltage probe P2221 directly. Then, the dynamic  $R_{dson}$  can be calculated by

$$R_{dson} = (\overline{V}_B - 2\overline{V}_{F_D 2}) / (\overline{I}_{drain} - I_1 + \overline{V}_B / R_t)$$

(2)

where  $\overline{V_B}$ ,  $\overline{V_F}_{D2}$ ,  $\overline{I}_{drain}$ ,  $\overline{I}_{D2}$ , and  $I_1$  are the average voltages of point B and D<sub>2</sub>, the average currents through a resistive load and D<sub>2</sub>, and the current of the constant-current supply, respectively. Idrain, the voltage of point A (Vdrain) and VFD2 of D2 are tested by a current probe (TCP0020), a high-voltage differential probe (THDP0200), and a low-voltage differential probe with a 1:1 attenuation (TIVH02) and displayed on an oscilloscope (MDO3104). Finally, the calculated dynamic Rdson is normalized by Rdson\_DC, which is 200  $^{m\Omega}$ , from an eGaN HEMT (GS66502B from GaN Systems Inc.) [24].

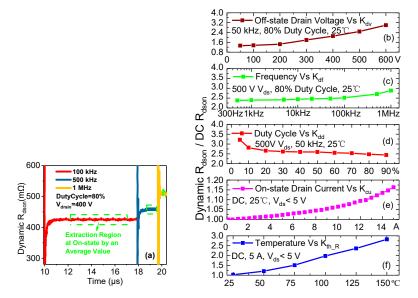

Figure 5b–f show the results of the dynamic  $R_{dson}$  of the eGaN HEMT for various  $V_{ds\_off}$ ,  $f_s$ , duty cycles,  $I_{drain}$  and operating temperatures, which are extracted in the on-state by taking average values in the stable region marked in Figure 5a,b shows that the dynamic  $R_{dson}$  increases as  $V_{drain}$  increases, under the conditions of an 80% duty cycle and an  $f_s$  of 100 kHz, so the dynamic  $R_{dson}$  is voltage-dependent. Figure 5c,d show the dynamic  $R_{dson}$  increases as  $f_s$  increases and duty cycle decreases, respectively for a 500 V  $V_{drain}$  condition, so the dynamic  $R_{dson}$  is also time-dependent. Considering that the dynamic  $R_{dson}$  is not only affected by the trapping effect, we further test the relationship between the dynamic  $R_{dson}$  and  $I_{drain}$  and temperature, as shown in Figure 5e, $f_s$ , respectively. These two tests

will help us isolate the trapping effect caused by the increase in the dynamic R<sub>dson</sub> in a particular complex test condition.

**Figure 5.** Dynamic  $R_{dson}$  extraction waveforms at various  $f_s(a)$  and the dynamic  $R_{dson}$  normalized by  $R_{dson\_DC}$  for various  $V_{ds\_off}(b)$ ,  $f_s(c)$ , duty cycles (d),  $I_{drain}(e)$  and temperatures (f).

In conclusion, the trend of the results of the extracted dynamic R<sub>dson</sub> of the eGaN HEMT is consistent with the mechanism of the trapping-effect-induced increase in the dynamic R<sub>dson</sub>. From Figure 6, we can obtain the real conduction resistance of the eGaN HEMT device under a certain working condition, and then the conduction loss can be corrected.

# 4. Discussion on the Effect of the Drain Current by a Double-Mode Test Technique

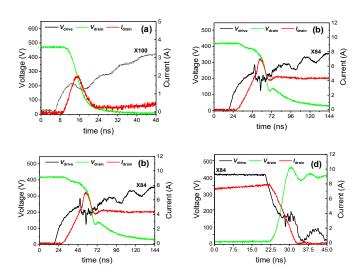

Base on the test circuit in Figure 1, a new double-mode test technique which including a DCM and a CCM is proposed. Then, the tested waveforms during the turn-on and turn-off transitions for various voltage and PWM conditions are illustrated in the Figure 6. To ensure that the switching circuit operates in open-loop CCM and DCM,  $V_{\text{Bulk}}$  is set to 400 V, and the  $V_{\text{Load}}$  is set to 80 V in DCM and 20 V in CCM, so the  $V_{\text{ds\_off}}$  values of the devices in the two modes are different.

**Figure 6.** Experimental waveforms of the HEMT device during the turn-on transitions in 400 V DCM with a  $VL_{oad}$  of 80 V (a) and 400 V CCM with a  $VL_{oad}$  of 20 V (b) and during turn-off transitions in 400 V DCM with a  $VL_{oad}$  of 80 V (c) and 400 V CCM with a  $VL_{oad}$  of 20 V (d).

The current Idrain in DCM exhibits only one resonant waveform when the drain voltage decreases, as shown in Figure 6a, while Idrain in CCM has an extra linear increase before the resonant waveform occurs, as shown in Figure 5b. The corresponding voltage fall time is approximately 14 ns in Figure 6(a) and is approximately 42 ns in Figure 6b, so that the extra linear increase in the current will increase the turn-on time and cause a high dynamic power loss. This linear increase in the current is caused by the high start current and the linear conduction of the eGaN HEM at this time. This means that DCM is a better operating mode for reducing the turn-on time.

In addition, the rise time of the drain voltage during the turn-off transition, which is approximately 10 ns, as shown in Figure 6d, is faster than that of approximately 30 ns in Figure 6c. This is because I<sub>drain</sub> in Figure 6d is higher than that in Figure 6c, and the rise time of the drain voltage during the turn-off transition mainly depends on the charge time of Coss. Moreover, the peak current in DCM during the turn-off transition will be higher than that in CCM under the same output power conditions. This means that DCM is a better operating mode for reducing the turn-off time.

In conclusion, the drain current will significantly affect the turn-on and turn-off times, and DCM is better than CCM for reducing the crossover power losses.

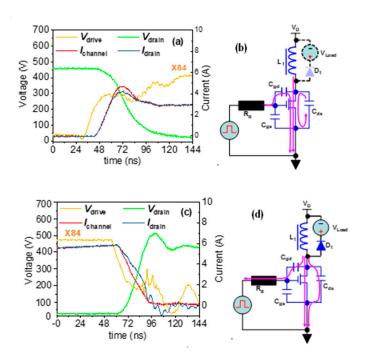

#### 5. Investigation on the Real Channel Current

According to the qualitative method in Figure 2, we can study the discrepancy between  $I_{drain}$  and  $I_{channel}$ . Figure 7a shows the tested  $I_{drain}$ ,  $I_{channel}$ ,  $V_{drain}$  and  $V_{drive}$  values of the AlGaN/GaN HEMT in the turn-on transition for a  $V_{ds\_off}$  of 500V, an  $f_s$  of 100 kHz, and a duty cycle of 16.5%. It is shown that  $I_{channel}$  is larger than  $I_{drain}$  while the drain voltage decreases. The current path in this time interval is shown in Figure 7b, where the channel current partially results from the discharging current of the parasitic output capacitor.

**Figure 7.** Experimental results during the turn-on transition in 500 V CCM (a) and a schematic diagram of the corresponding current path (b) and the experimental results during the turn-off transition in 500 V CCM and a schematic diagram of corresponding current path (d).

Figure 7c shows the tested  $I_{drain}$ ,  $I_{channel}$ ,  $V_{drain}$  and  $V_{drive}$  values of the AlGaN/GaN HEMT during the turn-off transition for a  $V_{ds\_off}$  of 500 V, an  $f_s$  of 100 kHz, and a duty cycle of 16.5%. It is shown that  $I_{channel}$  is smaller than  $I_{drain}$  while the drain voltage increases. The current path in this time interval is shown in Figure 7d where the channel current is partially diverted to the branch of output capacitor.

In conclusion, I<sub>channel</sub> is not exactly equal to I<sub>drain</sub>, and unfortunately, I<sub>channel</sub> cannot be tested directly. However, with the above test results and the current path analysis, we can acquire the reason for the discrepancy between I<sub>channel</sub> and I<sub>drain</sub> so that the real I<sub>channel</sub> value can be obtained by a test of I<sub>drain</sub> and an analytical method, and the power losses of eGaN HEMTs can be correctly evaluated.

# 6. Modeling of Switching Power Losses

Figure 8 shows a detailed timing diagram of the switching period [25] for eGaN HEMTs in DCM or CCM. The operating period of the power devices can be divided into 12-time intervals from to to t12 according to the status of the drain voltage and Idrain in the off-state, on-state, turn-on transition, and turn-off transition. To investigate the detailed dynamic power loss, we reclassify the 12-time intervals into the following four stages (S1-S4) according to their different contributions to the dynamic power loss.

Figure 8. Timing diagram of the GaN HEMT devices.

# 6.1. A. Stage 1(S1) – Off-state with a High V<sub>ds</sub>

During the  $t_0$ – $t_1$ ,  $t_{10}$ – $t_{11}$ time intervals and the time of the off-state, the device sustains a high  $V_{ds}$ . Thus, the voltage-dependent leakage current ( $I_{lk}$ ) will lead to an off-state power loss ( $P_{off}$ ). We can no longer ignore this power loss, especially at a very high drain voltage and a very high frequency. In general, the  $t_0$ – $t_1$  and  $t_{10}$ – $t_{11}$ time intervals can be neglected in comparison with the off-state time, so  $P_{off}$  can be written as

$$P_{off} = I_{lk} V_{ds} [t_{t_0 - t_1} + t_{t_{11} - t_{12}} + (1 - D)T] f_s \approx I_{lk} V_{ds} (1 - D)$$

(3)

where T and D are the period and duty cycle, respectively. In addition, eGaN HEMTs have no reverse recovery problem because the 2DEG in the channel is naturally formed by the polarization effect. This will reduce the power loss and mitigate the electromagnetic interference (EMI) problem which is produced by the reverse recovery caused by ringing.

# 6.2. B. Stage 2(S2) – On-state in Saturation Region

During the  $t_4$ – $t_7$  time intervals, the device is in the on-state. The RMS value of the drain current ( $I_{drain\_rms}$ ) can be written as

$$I_{\text{drain\_rms}} = \sqrt{f_s \int_0^{1/f_s} I_{\text{drain}}^2(\mathbf{t}) d\mathbf{t}}$$

(4)

To take the problem of the increase in the dynamic  $R_{dson}$  into account, the traditional conductive power loss ( $P_{con}$ ) can be modified by

$$P_{con} = I_{drain\_rms}^2 R_{dson\_DC} k_{dv} k_{df} k_{dd} k_{th\_R} k_{cu}$$

$$\tag{5}$$

where  $k_{\text{dv}}$ ,  $k_{\text{df}}$ ,  $k_{\text{dd}}$ ,  $k_{\text{au}}$  and  $k_{\text{th}\_R}$  are the dynamic coefficients of  $R_{\text{dson}}$  related to the voltage,  $f_{\text{s}}$ , the duty cycle, the current and the temperature, respectively.

# 6.3. C. Stage 3(S3) – Turn-on Transition

$$P_{\text{turn}\_on} = \int_{I_1 - I_4} V_{ds}(t) I_{drain}(t) f_s dt + \frac{1}{2} C_{oss} V_{ds}^2 f_s$$

(6)

1) In the t<sub>1</sub>-t<sub>2</sub> time interval, I<sub>drain</sub> increases almost linearly from 0 to the <sup>1</sup><sub>sta</sub> at t<sub>2</sub>, similar to a Si-based MOSFET [26–27], while V<sub>drain</sub> decreases slightly from V<sub>ds</sub> to V<sub>r</sub> due to the result of the parasitic inductance voltage drop caused by a high di/dt in the circuit. At t<sub>2</sub>, the current of the freewheeling diode D<sub>1</sub> decreases to zero. In this time interval, the gate voltage of the device slightly exceeds V<sub>th</sub>, so the device is operating in a linear region. Meanwhile, the trapping effect for a high electric field will also lead to a large dynamic R<sub>dson</sub> in the linear region (R<sub>turn\_on\_cr</sub>), similar to that in the on-state, as well as an extra gate lag. Thus, the coefficients of the dynamic R<sub>dson</sub> should be the same as those in Figure 4. Assuming that the heatsink is large enough and the self-heating effect is ignored, the t<sub>1</sub>-t<sub>2</sub> time interval, V<sub>r</sub> and the power losses in this time interval (P<sub>turn\_on\_cr</sub>) can be written by

$$R_{turn\_on\_cr} = \frac{\Delta V_{ds}}{\Delta I_{channel}} \approx \frac{k_{dv} k_{df} k_{dd} k_{th\_R} k_{cu} L_{eff\_Gate}}{W_{eff\_Gate} \mu_s C_{gs} (V_{drive\_H} - V_{th})}$$

$$(7)$$

$$t_1 - t_2 = \frac{C_{gs} R_{g\_on} i_{sta} + L_s i_{sta} g_m}{[V_{drive\_H} - 0.5 (V_{mr} + V_{lh})] g_m} k_{lag}$$

(8)

$$V_r = V_{ds} - L_s \frac{i_{sta}}{t_1 - t_2} - R_{turn\_on\_cr} \frac{i_{sta}}{2}$$

(9)

$$P_{\text{turn}\_on\_cr} = \frac{1}{2} i_{sta} V_r(t_1 - t_2) f_s \tag{10}$$

where,  $L_{eff\_Gate}$  and  $W_{eff\_Gate}$  are the effective channel length and width, respectively.  $L_s$  is the source inductor which is in series with and between the source terminal and the ground. The coefficient of the gate lag  $(k_{lag})$  is a fitting parameter, which can be obtained by measuring the turn-on delay for various  $V_{ds\_off}$ ,  $f_s$  and duty cycles.

2) In the t2–t3 t.ime interval, the HEMT device takes over the total inductive load current, and Vds decreases to a boundary voltage of (Vmr-Vth) at t3 due to the discharging of Coss. The stray inductors in series around the circuit are resonant with Coss and the stray capacitors (Cstray) in this time interval. The current path through the device is illustrated in Figure 5b. It is assumed here that Vgs and ista remain unchanged, and the reverse recovery of the D1 is zero. In addition, the current in this time interval is usually large enough; and hence, the charging time of Coss can be ignored. Moreover, voltage-dependent Coss is not suitable for calculating power losses in this time interval because Vdrain is always changing. Therefore, Qgd is used to replace Coss, and then the time interval of t2-t3 can be written as

$$C_{gd_{-}vf} = \frac{Q_{gd}}{\Delta V} = \frac{Q_{gd}}{V_{r} - V_{mr} + V_{th}}$$

(11)

$$t_{2} - t_{3} = \frac{Q_{gd} R_{g_{on}} + C_{stray} (V_{r} - V_{mr} + V_{th}) / g_{m}}{V_{drive} H - V_{mr}}$$

(12)

Then, the power losses in this time interval (Pturn\_on\_vf) can be written by [28]:

$$\overline{I}_{vf} \approx 0.5 \left( \frac{V_r}{R_{turn,on,cr}} + \frac{V_{mr} - V_{th}}{R_{dson}} \right) \tag{13}$$

$$P_{\text{turn}\_on\_vf} = \frac{1}{2} (i_{sta} + \overline{I}_{vf})(V_r - V_{mr} + V_{th})(t_2 - t_3) f_s + \frac{1}{2} C_{stray} [V_r^2 - (V_r - V_{mr} + V_{th})^2] f_s$$

(14)

where  $\overline{I}_{vf}$  is the average channel current during the t2–t3 time interval.

3) During the t<sub>3</sub>-t<sub>4</sub> time interval, the HEMT device operates in an ohmic conducting state. Then, V<sub>drain</sub> continues to decrease until it reaches a low on-voltage (V<sub>on</sub>) from(V<sub>mr</sub>-V<sub>th</sub>). Assuming that i<sub>sta</sub> and the Miller voltage V<sub>mr</sub> do not change, then the t<sub>3</sub>-t<sub>4</sub> time interval, V<sub>on\_r</sub> and the power losses in this time interval (P<sub>turn\_on\_mr</sub>) can be written by [29]:

$$t_3 - t_4 = \frac{Q_{gd} R_{g_{-}on}}{V_{drive\ H} - V_{mr}} \tag{15}$$

$$V_{on\ r} = i_{sta} R_{dson} k_{dv} k_{df} k_{dd} k_{th\ R} k_{cu} \tag{16}$$

$$P_{\text{tum\_on\_mr}} = \frac{1}{2} i_{sta} (V_{mr} - V_{th} - V_{on\_r}) (t_3 - t_4) f_s + \frac{1}{2} C_{stray} [(V_{mr} - V_{th} - V_{on\_r})^2 - V_{on\_r}^2] f_s$$

(17)

From the above analysis, Equation (6) can be modified by

$$P_{\text{tum}\_on}(\text{measured}) = P_{\text{tum}\_on\_cr} + P_{\text{tum}\_on\_vf} + P_{\text{tum}\_on\_mr}$$

(18)

Notice that in this stage,  $i_{sta}$  is a tested drain current instead of a real channel current and they are actually different in the  $t_2$ – $t_3$  time interval, as shown in Figure 5a. However,  $I_{channel}$  is the real factor that results in the power losses in this stage, and the real  $I_{channel}$  is the combined current of  $I_{drain}$  and the discharging current of  $I_{cos}$ :

$$I_{channel} = I_{drain} + I_{Cds} + I_{Ced} \approx I_{drain} + I_{Cds} \tag{19}$$

Thus, Equation (18) can be finally modified by [12]

$$P_{\text{turn }on \ act} = P_{\text{turn }on \ \text{mea}} + P_{\text{turn }on \ dis}$$

(20)

where

$$P_{\text{turn}\_on\_dis} = \frac{1}{2} C_{oss} V_{ds\_off}^2 f_s \tag{21}$$

Thus

$$P_{\text{turn\_}on\_act} = P_{\text{turn\_}on\_cr} + P_{\text{turn\_}on\_vf} + P_{\text{turn\_}on\_mr} + \frac{1}{2} C_{oss} V_{dsf}^{2} f_{s}$$

$$(22)$$

# 6.4. D. Stage 4(S4) – Turn-off Transition

During the  $t_7$ – $t_{11}$  time intervals, the device is in a turn-off transition. In the  $t_7$ - $t_8$  time intervals, the drain voltage increases while  $I_{drain}$  stays almost constant; in the  $t_8$ - $t_9$  time intervals, the drain voltage continuously increases while  $I_{drain}$  decreases slightly; in the  $t_9$ - $t_{10}$  time intervals,  $I_{drain}$  decreases while the drain voltage stays almost constant. Finally,  $I_{drain}$  decreases to zero, and the drain voltage becomes resonant in the  $t_{10}$ - $t_{11}$  time intervals. These crossovers of  $V_{drain}$  and  $I_{drain}$  will cause power losses during the turn-off transition ( $P_{turn\_off}$ ):

$$P_{\text{tum\_off}} = \int_{t_2 - t_{10}} V_{ds}(t) I_{drain}(t) f_s dt$$

(23)

4) In the t<sub>7</sub>-t<sub>8</sub> time interval, the observations are very similar to those in the t<sub>3</sub>-t<sub>4</sub> time interval. The HEMT device goes into a linear region from an ohmic conducting state.  $V_{drain}$  increases to a boundary voltage of  $V_{mf} - V_{th}$ . Assuming that the peak current is unchanged, and  $V_{mf} = V_{mr}$ , then the t<sub>7</sub>-t<sub>8</sub> time interval,  $V_{on\_f}$  and the power losses in this time interval ( $P_{turn\_on\_mf}$ ) can be written by:

$$t_7 - t_8 = \frac{Q_{gd} R_{g\_off}}{V_{mf} - V_{drive\_L}}$$

(24)

$$V_{on\_f} = I_{pk} R_{dson} k_{dv} k_{df} k_{dd} k_{th\_R} k_{cu}$$

(25)

$$P_{\text{tum\_off\_mf}} = \frac{1}{2} i_{pk} (t_7 - t_8) (V_{mf} - V_{th} - V_{on\_f}) f_s$$

(26)

In the t<sub>8</sub>-t<sub>9</sub> time interval, the observations are very similar to those in the t<sub>2</sub>-t<sub>3</sub> time intervals. V<sub>drain</sub> continues to increase faster towards the off-state V<sub>ds\_off</sub>, while I<sub>drain</sub> decreases slightly to i<sub>r</sub>. This current drop is caused by a charging shunt to other peripheral devices [25], and the current path through the device is illustrated in Figure 5d. Assuming that the Miller voltage (V<sub>mf</sub>) remains unchanged and that the current-dependent charging time of C<sub>oss</sub> can no longer be ignored, we have:

$$t_{8} - t_{9} \approx \frac{Q_{gd} R_{g\_off} + C_{stray} (V_{ds} - V_{mf} + V_{th}) / (2g_{m})}{V_{mf} - V_{drive\_L}} + \frac{C_{oss} (V_{ds} - V_{mf} + V_{th})}{i_{pk}}$$

(27)

$$i_r = i_{pk} - C_{stray} \frac{dV_{ds}}{dt} = i_{pk} - C_{stray} \frac{V_{ds} - V_{mf} + V_{th}}{t_8 - t_9}$$

(28)

$$P_{\text{tum}\_off\_vr} = \frac{i_{pk} + i_r}{2} (V_{ds} + V_{mr} - V_{th}) (t_8 - t_9) f_s$$

(29)

6) In the t9-t10 time interval, the observations are similar to those in the t1-t2 time interval. Idrain decreases from ir to a low value because the current begins to divert from the HEMT device to D1. In this time interval, the drain voltage is in a state of resonance, while Vgs decreases to (Vmr-Vth) and the device channel current reaches zero at t10 [30]. Then, the t9-t10 time interval and the power losses at this time interval (Pturn\_off\_cf) can be written by:

$$t_9 - t_{10} = \frac{(C_{gs} R_{g\_off} + L_s g_m) i_r}{[0.5(V_{mf} + V_{th}) - V_{drive\_L}] g_m}$$

(30)

$$P_{\text{tum\_off\_cf}} = \frac{1}{2} i_r V_{ds\_off} (t_9 - t_{10}) f_s + \frac{L_{stray} i_r^2}{2}$$

(31)

7) During the t<sub>10</sub>-t<sub>11</sub> time interval, the device is turned off but V<sub>drain</sub> ringing occurs due to the resonance between C<sub>oss</sub> and L<sub>stray</sub>. These fluctuations of the drain voltage will lead to a slight power loss which depends on the ringing peak voltage (V<sub>ds\_pk</sub>). Assuming that the reverse recovery of D<sub>1</sub> is zero, we have:

$$\frac{L_{stray}i_r^2}{2} = \frac{C_{oss}\Delta V^2}{2} \rightarrow \Delta V = \sqrt{\frac{L_{stray}i_r^2}{C_{oss}}} \rightarrow V_{ds\_pk} = V_{ds\_off} + \Delta V$$

(32)

$$P_{\text{turn}\_off\_vx} \approx \frac{1}{2} C_{oss} (V_{ds\_pk}^2 - V_{ds\_off}^2) f_s$$

(33)

From the above analysis, Equation (23) can be modified by

$$P_{\text{turn off}} \text{ (measured)} = P_{\text{turn off mf}} + P_{\text{turn off vr}} + P_{\text{turn off cf}} + P_{\text{turn off vx}}$$

(34)

instead of real channel currents and they are actually different in the t8–t9 time interval, as shown in Figure 5c. However, Ichannel is the real factor that results in the power losses in this stage, and the real Ichannel is the diverted current of Idrain and the charging current of Coss:

$$I_{channel} = I_{drain} - I_{Cds} - I_{Cgd} \approx I_{drain} - I_{Cds}$$

(35)

Therefore, Equation (34) can be finally modified as [12]:

$$P_{\text{turn } off}(\text{actual}) = P_{\text{turn } off}(\text{measured}) - P_{\text{turn } off}(\text{charge})$$

(36)

where

$$P_{\text{tum}\_off\_char} = \frac{1}{2} C_{oss} V_{ds\_off}^2 f_s \tag{37}$$

Thus

$$P_{\text{turn}\_off\_act} = P_{\text{turn}\_off\_mf} + P_{\text{turn}\_off\_vr} + P_{\text{turn}\_off\_cf} + P_{\text{turn}\_off\_vx} - \frac{1}{2} C_{oss} V_{ds\_off}^{2} f_{s}$$

(38)

Finally, the total power loss (Ptotal) should be described with the sum of Equations (3)–(38):

$$P_{total} = P_{off} + P_{con} + P_{turn \text{ on } act} + P_{turn \text{ off } act}$$

$$(39)$$

In particular, the effects of  $I_{channel}$  and  $I_{drain}$  on  $P_{total}$  can finally cancel out for a hard switch. However, in a soft switch application such as a zero-voltage switch (ZVS),  $P_{tum\_on\_dis}$  is zero; hence,  $P_{tum\_off\_char}$  can no longer cancel out. This correction becomes very meaningful to the universality of the dynamic power loss model for eGaN HEMTs.

As can be seen,  $P_{total}$  in Equation (39) is very different from that in Equation (1). Equation (39) has no power loss of reverse recovery, but it takes the trapping-effect-induced dynamic  $R_{dson}$  and the impacts of the  $I_{drain}$  and the real  $I_{channel}$  into account.

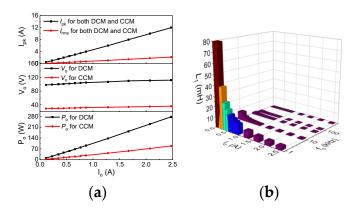

# 7. Model Verification by Experiments

To verify our dynamic power loss model, we adopt a floating buck-boost power converter with a light-emitting diodes (LEDs) operating in DCM and CCMs. To maintain the operation mode and the output current ( $I_o$ ) in an open-loop control system, some key parameters are adjusted (such as  $L_1$ ) or tested (such as the output voltage  $V_o$ , peak operating current  $I_{pk}$ , and the output power  $P_o$ ) in the circuit, as shown in Figure 8, for an input voltage ( $V_{Bulk}$ ) of 400 V, a duty cycle of 10%, and various  $f_s$  and  $I_o$  values.

**Figure 9.** The relationship between Io and  $V_0$ ,  $P_0$ , and  $I_{pk}$  (a) and the relationship between  $I_0$  and inductance of  $L_1$  for various  $f_s$  (b) in an open-loop controlled floating buck-boost power converter.

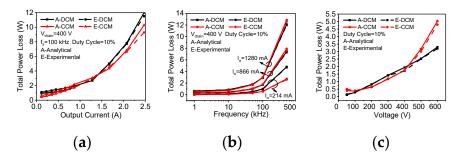

The power losses are then tested by a power analyzer (PW6001-03 from HIOKI Inc.). Figure 10a–c reveal that the analytical results of the total dynamic power losses by the proposed model are in good agreement with experimental results both in CCM and DCMs, even for various  $I_{\rm o}$ ,  $f_{\rm s}$  and  $V_{\rm Bulk}$  values. The experimental results are slightly different from the analytical results, which may be because of the measurement accuracy of the power meter reduced at a high  $f_{\rm s}$ .

**Figure 10.** Comparison of the total dynamic power losses from the analytical and experimental results both in CCM and DCMs and for various  $I_0(a)$ ,  $f_s(b)$  and  $V_{Bulk}(c)$ .

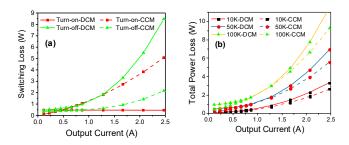

Figure 11a shows the relationship between the total dynamic power losses and I<sub>0</sub> in CCM and DCMs. In the case of a small I<sub>0</sub>, the switching loss is dominant, while in the case of a large I<sub>0</sub>, the conduction loss is dominant. In addition, the dynamic power loss increases faster with the increase in I<sub>0</sub> in DCM than in CCM, indicating that DCM is not suitable for high current conditions.

Figure 11b shows the switching loss during the turn-on and turn-off transitions in CCM and DCM. The results reveal that the switching loss is lower in DCM than in CCM during the turn-on transition but larger during the turn-off transition when Io is larger than 1.25 A. This means that DCM is more suitable for a relatively small Io. In this case, from Figures 10b and Figure 11a, 1.25 A is a moderate output current that is acceptable.

**Figure 11.** Experimental total dynamic power losses (a) and switching losses (b) as a function of the output current in DCM and CCM

To restrain the peak current and obtain a high operating efficiency, the QRM is then proposed. The reason is that QRM works at the DCM boundary, where  $V_{\text{drain}}$  will decrease to a minimum value at the beginning of the turn-on transition while  $I_{\text{drain}}$  decreases to zero. In addition, the peak on-state current in DCM is usually larger than that in CCM, and the current will be at a controllable high level, so the turn-off time is fast in QRM. Therefore, QRM is more suitable for achieving a lossless switch and even for reducing the turn-off transition time.

### 8. Conclusions

An improved 12-time-interval piecewise dynamic power loss model for eGaN HEMTs is developed by specially quantifying the effects of the increase in the dynamic  $R_{dson}$ , the impact of  $I_{drain}$  on the turn-on and turn-off times, and the real  $I_{channel}$ , good agreement with some experimental results is verified.

In this work, three new methods or techniques are proposed, which are DDI method, double-mode test technique and qualitative, respectively. Then, the dynamic R<sub>dson</sub> is obtained by our new extraction circuit at a high operating fs up to 1 MHz and high drain voltage up to 600 V, and the drain current is found to significantly affect the turn-on and turn-off times by a switching circuit operating in DCM and CCM, and the real channel current is accurately calculated to distinguish it from the measured drain current. All of these parameters are included into the power loss model.

14

Moreover, the QRM has a low  $V_{ds\_off}$ , zero turn-on current, and relatively large peak current. Therefore, on the basis of the model, we propose the QRM to obtain a high efficiency and decrease the turn-off switching time for the application of eGaN HEMTs.

**Author Contributions:** Funding acquisition, Liang Xu and Jing Yu; Investigation, Wenbo Zhang; Methodology, Rui Wang; Resources, Zhanmin Yang and Yalin Chen; Supervision, Dunjun Chen; Writing – original draft, Jianming Lei; Writing – review & editing, Yangyi Liu. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was supported by the State Key R&D Project of Jiangsu (BE2021026), and the State Key R&D Project of Jiangsu (BE2022070). (Corresponding author: D. J. Chen)

Data Availability Statement: Data available by request to the corresponding author.

**Conflicts of Interest:** The authors declare no conflict of interest. The funders had no role in the design of the study; in the collection, analyses, or interpretation of data; in the writing of the manuscript, or in the decision to publish the results.

#### References

- 1. J. A. del Alamo and J. Joh, "GaN HEMT reliability," in Proc. Microelectronics Reliability, vol. 49, no. 9-11, pp. 1200-1206, July. 2009, DOI: 10.1016/j.microrel.2009.07.003.

- 2. U. K. Mishra, P. Parikh and Y. F. Wu, "AlGaN/GaN HEMTs-An overview of device operation and applications," Proc. IEEE, vol. 90, no. 6, pp. 1022-1031, July 2002, DOI:10.1109/JPROC.2002.1021567.

- 3. O. Ambacher, B. Foutz, J. Smart, J. R. Shealy, N. G. Weimann, K. Chu, M. Murphy, A. J. Sierakowski, W. J. Schaff, L. F. Eastman, R. Dimitrov, A. Mitchell and M. Stutzmann, "Two-dimensional electron gases induced by spontaneous and piezoelectric polarization in undoped and doped AlGaN/GaN heterostructures," J. Appl. Physics, vol. 87, issue. 1, pp. 334-344, Jan. 2000, DOI:10.1063/1.371866.

- K. Wang, X. Yang, H. Li, H. Ma, X. Zeng, and W. Chen, "An Analytical Switching Process Model of Low-Voltage eGaN HEMTs for Loss Calculation," IEEE Transactions on Power Electronics, vol. 31, no. 1, pp.635-647, Jan. 2016, DOI: 10.1109/TPEL.2015.2409977.

- 5. K. Wang, M. Tian, H. Li, F. Zhang, X. Yang and L. Wang, "An improved switching loss model for a 650V enhancement-mode GaN transistor," in Proc. IEEE Annual Southern Power Electronics Conference (SPEC),2016, pp. 1-6. DOI: 10.1109/SPEC.2016.7846144.

- 6. Y. F. Shen, H. Wang, Z. Shen, F. Blaabjerg and Z. Qin, "An Analytical Turn-on Power Loss Model for 650-V GaN eHEMTs," IEEE Appl. Power Electr. Conf. and Expo. (APEC), pp. 913-918, March 2018, DOI: 10.1109/APEC.2018.8341123.

- R. Hou, J. C. Lu and D. Chen, "Parasitic Capacitance Eqoss Loss Mechanism, Calculation, and Measurement in Hard-Switching for GaN HEMTs," IEEE Appl. Power Electr. Conf. and Expo. (APEC), pp. 919-924, March 2018, DOI: 10.1109/APEC.2018.8341124.

- 8. M. Guacci, M. Heller, D. Neumayr, D. Bortis, J. W. Kolar, G. Deboy, C. Ostermaier and O. Haberlen, "On the Origin of the Coss-Losses in Soft-Switching GaN-on-Si Power HEMTs," IEEE J. Emerg. And Sel. Top. In Power Elect., pp. 1-1, Dec. 2018, DOI: 10.1109/JESTPE.2018.2885442.

- 9. J. Chen, Q. M. Luo, J. Huang, Q. Q. He and X. Du, "A Complete Switching Analytical Model of Low-Voltage eGaN HEMTs and Its Application in Loss Analysis," IEEE T. on Ind. Electr., pp. 1-1, Jan. 2019, DOI: 10.1109/TIE.2019.2891466.

- 10. L. Spaziani, "A study of MOSFET performance in processor targeted buck and synchronous rectifier buck converters," in Proc. High Freq.Power Convers., 1996, pp. 123-137, ISBN: 0931033632.

- 11. J. Klein. (2006). "Synchronous buck MOSFET loss calculations with Excel model." Available: www.fairchildsemi.com.

- 12. A. Lidow, J. Strydom, M. d. Rooij, and D. Reusch, GaN Transistors for Efficient Power Conversion, 2nd ed. Efficient Power Conversion Corporation: Wiley Press, 2015, ISBN: 978-1-118-84476-2.

- 13. Y. Ren, M. Xu, J. Zhou, and F. C. Lee, "Analytical loss model of power MOSFET," IEEE Trans. Power Electron., vol. 21, no. 2, pp. 310-319, Mar. 2006, DOI: 10.1109/TPEL.2005.869743.

- 14. J. Wang, H. S. H. Chung, and R. T. H. Li, "Characterization and experimental assessment of the effects of parasitic elements on the MOSFET switching performance," IEEE Trans. Power Electron., vol. 28, no. 1, pp. 573-590, Jan. 2013, DOI: 10.1109/TPEL.2012.2195332.

- 15. I. Castro et al., "Analytical switching loss model for superjunction MOSFET with capacitive nonlinearities and displacement currents for DC–DC power converters," IEEE Trans. Power Electron., vol. 31, no. 3, pp. 2485-2495, Mar. 2016, DOI: 10.1109/TPEL.2015.2433017.

- 16. J. Cao, Y. Pei and Z. Wang, "Analysis of power of switching components in boost PFC circuit," Advanced Technology of Electrical Engineering and Energy, vol. 21, no. 1, pp. 41-44, Jan. 2002, Paper ID:1003-3076(2002)01-0041-04.

- 17. J. M. Lei, R. Wang, G. Yang, J. Wang, F. L. Jiang, D. J. Chen\*, H. Lu, R. Zhang and Y. D. Zheng, "Precise Extraction of Dynamic Rdson under High Frequency and High Voltage by A Double-Diode-Isolation Method," IEEE J. Electr. Dev. Society, vol. 7, pp. 690-695. July 2019. doi: 10.1109/JEDS.2019.2927608.

- 18. H. Wang, C. Liu, Q. Jiang, Z. Tang and K. J. Chen, "Dynamic Performance of AlN-Passivated AlGaN/GaN MIS-High Electron Mobility Transistors Under Hard Switching Operation", IEEE Elec. Dev. Lett., vol. 36, no. 8, pp. 760-762, Aug. 2015, DOI:10.1109/LED.2015.2450695.

- J. Bocker, C. Kuring, M. Tannhauser and S. Dieckerhoff (2017, October). Ron Increase in GaN HEMTs-Temperature or Trapping Effects. ECCE, 2017 IEEE (pp. 1975-1981). IEEE. Cincinnati, OH. DOI:10.1109/ECCE.2017.8096398.

- 20. J. J. Zhu, X. H. Ma, B. Hou, W. W Chen and Y. Hao, "Investigation of trap states in high Al content AlGaN/GaN high electron mobility transistors by frequency dependent capacitance and conductance analysis," Aip Advances, vol. 4, no.3, pp. 8070-215. March 2014. DOI:10.1063/1.4869020.

- 21. S. D. Gupta, M. Sun, A. Armstrong, R. J. Kaplar, M. J. Marinella, J. B. Stanley, S. Atcitty and T. Palacios, "Slow Detrapping Transients due to Gate and Drain Bias Stress in High Breakdown Voltage AlGaN/GaN HEMTs" IEEE T. Electron Dev., vol. 59, no. 8, pp. 2115-2122, Aug. 2012, DOI: 10.1109/ted.2012.2198652.

- 22. A. M. Wells, M. J. Uren, R. S. Balmer, K. P.Hilton, T. Martin, M. Missous, "Direct demonstration of the virtual gate mechanism for current collapse in AlGaN/GaN HFETs," Solid-State Electronics, Letter, vol. 49, no. 2, pp. 279-282, Feb. 2005, DOI:10.1016/j.sse.2004.10.003.

- 23. R. J. Trew, D. S. Green and J. B. Shealy, "AlGaN/GaN HFET Reliability," IEEE microwave magazine, vol. 10, no. 4, pp. 116-127, July 2009, DOI: 10.1109/MMM.2009.932286.

- 24. "GS66502B bottom-side cooled 650 V E-mode GaN transistor preliminary datasheet, rev-181214," Datasheet, GaN Syst. Inc., Ottawa, ON, Canada, 2009-2018.

- 25. M. Shen and S. Krishnamurthy (2012, Sep.). Simplified loss analysis for high speed SiC MOSFET inverter. 27th Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Orlando, FL (pp. 1682-1687), DOI: 10.1109/APEC.2012.6166047.

- 26. J. G. J. Chern, P. Chang, R. F. Motta and N. Godinho, "A New Method to Determine MOSFET Channel Length," IEEE Electron Device Letters, vol. EDL-1, no. 9, pp. 170-173, Oct. 1980, DOI:10.1109/EDL.1980.25276.

- 27. Y. Ren, M. Xu, J. Zhou and F. C. Lee, "Analytical loss model of power MOSFET," IEEE Transactions on Power Electronics, vol. 21, no. 2, pp. 310-319, April 2006, DOI:10.1109/TPEL.2005.869743.

- N. Roscoe, N. McNeill and S. Finney (2017, Sept.). "A simple technique to optimize SiC device selection for minimum loss." 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe), Warsaw (pp. P.1-P.13), DOI:10.23919/EPE17ECCEEurope.2017.8099013.

- 29. Q. Zhao and G. Stojcic, "Characterization of Cdv/dt Induced Power Loss in Synchronous Buck DC–DC Converters," IEEE Transactions on Power Electronics, vol. 22, no. 4, pp. 1508-1513, July 2007, DOI:10.1109/TPEL.2007.900527.

- 30. Z. Guo, C. Hitchcock and T. P. Chow (2017, June). "Lossless turn-off switching projection of lateral and vertical GaN power field-effect transistors." Physics Status Solidi A (PSSA), vol. 214, no. 8, pp. 3-6, DOI:10.1002/pssa.201600820.

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.