Article

# **Empirical Characterization of ReRAM devices using Memory Maps and Dynamic Route Map**

Rodrigo Picos <sup>1,2,\*</sup>, Stavros G. Stavrinides <sup>3</sup>, Mohamad Moner Al Chawa<sup>4</sup>, D, Carol de Benito<sup>1,2</sup>, Dueñas<sup>5</sup>, Helena Castan<sup>5</sup>, Euripides Hatzikraniotis<sup>6</sup> and Leon O. Chua <sup>7</sup>, D

- Industrial Engineering and Construction Department, Balearic Islands University (Spain);

- <sup>2</sup> Health Institute of the Balearic Islands (Spain)

- <sup>3</sup> School of Science and Technology, International Hellenic University (Greece)

- <sup>4</sup> Institute of Circuits and Systems, Technische Universität Dresden (Germany)

- <sup>5</sup> Facultad de Ciencias, Universidad de Valladolid (Spain)

- 6 Physics Department, Aristotle University of Thessaloniki (Greece)

- Department of Electrical Engineering and Computer Sciences, University of Californa, Berkeley (USA)

- \* Correspondence: rodrigo.picos@uib.es

**Abstract:** Memristors were proposed in the early '70s of the XXth century by Leon Chua as a new electrical element linking the charge and the flux. Since that first introduction, these devices have positioned themselves to be considered as possibly fundamental for the new generations of electronic devices. It has to be mentioned that actual memristors have only been recognized to exist as physical elements. In this paper, we apply a modeling framework to generate a model describing experimental measurements performed on a ReRAM. We show how to apply the Dynamic Route Map technique in the general case to obtain an approximation to the differential equation that determines the behaviour of the device.

Keywords: Memristor; RRAM; compact modeling; Charge and Flux; Phase space

# 1. Introduction

At the beginning of the 1970s Leon Chua had noticed the possible symmetry between the current i, the voltage v, the charge q and the flux  $\varphi$  in electric theory.[1]. The three known passive elements are capacitor, inductor, and resistor. Each element relates a pair of electrical variables: charge with voltage, flux with current, and current with voltage, respectively. Chua suggested the existence of a new fourth electrical element to find the missing elation between charge and flux. This proposed element would behave as a resistor with a memory, thus the name 'memristor'.

In fact, the first experimental description of such a kind of elements had already been performed long time ago [2], but didn't get into the circuit theory mainstream. The theoretical introduction of these devices paved the way to develop a generalization description a class of devices and systems (memristive systems or devices), that are intrinsically nonlinear and defined by a set of differential equations relating the electrical magnitudes to a set of internal state variables [3].

Currently, these novel devices are considered as one of the most promising elements for the next generation of integrated circuit (IC), beyond and more than Moore [4]. For instance, these devices are expected to be a path for alleviating the classical problem of the Von Neumman architecture caused by the need of transferring data between memories and processors, enabling in-memory computing [5]. Thus, an increasing number of applications using memristors are been proposed: innovative memories (ReRAMs, MRAM, etc.) [6–8], new sensor devices [9–12], elemental blocks for artificial neural networks (ANNs) and other bio-inspired systems [13–15], to cite just a few.

Related to fabrication technologies, memristive devices are currently being implemented in many different flavors, ranging from spintronics [16] to many different oxides [17–20], organic materials [21,22], or even emulators [23? –26]. However, it has to be noted that, due to the relatively immature technology, only a handful of foundries are providing memristors into their libraries as standard blocks, as is usual with resistors or

Citation: Picos, R; Stavrinides, S.G.; Al Chawa, M.M.; de Benito, Carol; Dueñas, Salvador; Castan, Helena; Hatzikraniotis, E.; Chua, L.O. Empirical Characterization of ReRAM devices using Memory Maps and Dynamic Route Map. *Preprints* 2021, 1, 0. https://doi.org/

Received: Accepted: Published:

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

capacitors. For instance, and as far as we know, RRAMs are offered by TSMC, Intel and Towerjazz (where this last one seems to be in process of being acquired by Intel), but using old nodes. This implies that they can be implemented in cheaper designs, allowing their use in low-cost edge IoT platforms [27]. The low maturity also leads to the same problems that were found in other technologies, as the reliability or the various forms of variability they present: the usual device-to-device, plus a cycle to cycle variability [28,29].

The simulation of these devices is also a hot topic inside the modelling community [30,31], and there are two main approaches to this task. The first approach uses current and voltage [32–36] as the electrical variables of interest. The second approach, in line with Chua's original proposal, uses instead charge and flux approach [37????-41].

An interesting way to check a model is using a tool named as the Dynamic Route Map (DRM). This technique helps to represent how the system's governing variable evolves versus its rate of change (the temporal derivative). As is discussed in the corresponding section, this representation can provide a very significant insight on how these variables evolve and their relations. This DRM can also be understood inside the formalism proposed by Corinto [42], as the equation relating the internal variables with their derivatives. Thus, in this paper, we will exploit this relation, and we will use experimental measurements to get an approximation to this relation that will allow us to model the behavior of the device.

#### 2. Memristor Modelling Framework

As hinted in the introduction, a framework for memristor modelling was proposed by Corinto and Chua in [42]. In that work, the authors propose a consolidated theoretical framework that allows a unified approach to modelling, and they also check the possible advantages of the flux–charge  $(\varphi$ -q) variables used in this context. In this proposal, they define the different memristors presented in the taxonomy by [43] (the ideal, the generic, and the extended memristor) as being just different approximations in the equations. The most general type in this classification are extended memristors, which are memristors that are described by additional state variables  $\mathbf{X} = (X_1, X_2, ...)$  (other than just the electrical  $\varphi$  and q, or v and i). The most general expression relating all these variables can be expressed as follows

$$Q = f(\varphi, v, \mathbf{X}) \tag{1}$$

where the flux  $(\varphi)$  and the charge (Q) are linked to the voltage (v) and the current (i) respectively as follows

$$\frac{d\varphi}{dt} = v \tag{2}$$

$$\frac{dQ}{dt} = i \tag{3}$$

In addition, the evolution of the internal variables **X**, is described by a differential equation:

$$\frac{d\mathbf{X}}{dt} = \mathbf{g}_{\prime}(\varphi, v, \mathbf{X}) \tag{4}$$

In order to obtain an equivalent expression to Ohm's law, Eq. 1 can be derived with respect to time:

$$i = \frac{dQ}{dt} = \frac{\partial f(\varphi, v, \mathbf{X})}{\partial \varphi} \frac{d\varphi}{dt} + \frac{\partial f(\varphi, v, \mathbf{X})}{\partial v} \frac{dv}{dt} + \sum_{i} \frac{\partial f(\varphi, v, \mathbf{X})}{\partial X_{i}} \frac{dX_{j}}{dt}$$

(5)

The above equation can be further simplified using the Lagrangian L and the Jacobian J, as expressed in Eqs. (6) and (7), respectively:

$$L(\varphi, v, \mathbf{x}) = \frac{\partial g_{\varphi}(\varphi, v, \mathbf{x})}{\partial v} \tag{6}$$

$$\mathbf{J}(\varphi, v, \mathbf{X}) = \left(\frac{\partial g_{\varphi}(\varphi, v, \mathbf{X})}{\partial X_1}, ..., \frac{\partial g_{\varphi}(\varphi, v, \mathbf{X})}{\partial X_n}\right) \tag{7}$$

$$i = \frac{\partial f(\varphi, v, \mathbf{X})}{\partial \varphi} v + L(\varphi, v, \mathbf{x}) \frac{dv}{dt} + \mathbf{J}(\varphi, v, \mathbf{x}) \cdot \frac{d\mathbf{X}}{dt}$$

(8)

It is interesting to point out that the two last right terms in Eq. 8 have a clear physical meaning, being parasitic elements. Especially, the part with dv/dt can be connected to a capacitive element, while the term with  $dX_j/dt$  can be identified as a current source. In the case where parasitic elements are present, the most general (i.e. extended) memristors may be reduced to generic memristors (plainly, just memristors). This is caused by function  $g_{\varphi}$  being dependent only on flux  $\varphi$  and the state variables  $\mathbf{x}$ , thus L=0. Moreover, the original memristors, as defined in [1] are generic memristors that don't depend on any internal state variable (i.e. J=0). It has also to be noticed that it has been demonstrated in [42] that the following relation has to hold:

$$L(\varphi, v, \mathbf{x}) \frac{dv}{dt} + \mathbf{J}(\varphi, v, \mathbf{x}) \cdot \frac{d\mathbf{X}}{dt} = 0$$

(9)

Therefore, we can determine the memristance M to be as follows

$$M(\varphi, v, \mathbf{X}) = \frac{\partial f(\varphi, v, \mathbf{X})}{\partial \varphi} = f_M(\varphi, v, \mathbf{X})$$

(10)

The above expressions can also be formulated in terms of charge and current as of the variables as in [?]. In this case, the parasitic elements would have been inductors, and voltage sources [42].

In brief, the relevant relations for a flux-controlled memristor can be described using Eqs. 3, 4 and 11:

$$v = M(Q, i, \mathbf{X}) \cdot i \tag{11}$$

The above Eq. (11) shows the dependence of the memristance in the most general case (i.e. an extended memristor). There, the voltage across the terminals is named v, while i is the current and Q is the charge (the first momentum of the current, as in [42]). The internal variables are included as the vector  $\mathbf{x}$ , and their dynamics are defined by  $\mathbf{g}_{\mathbf{Q}}$  and Eq. 4.

It is worth to point out that the overhead framework has already been employed to successfully model various sorts of memristive systems, additionally enhancing the generalized framework for compact modelling in the flux-charge space [44]. Some interesting works utilising this approach may be found in the literature, as [45] where a memristor model is developed using a charge-dependent mobility. A model for PCM is proposed in [37], and in [38] or [40], the authors proposed semi-empirical models for ReRAMs, being considered to be memristors, and [46?] where a Monte Carlo model for ReRAMs was presented. A delay model for memristive crossbars was derived in [47] utilizing a flux-charge definition. Finally, in [48] light bulbs based on incandescent filaments are shown to be generic memristors, while [49,50] perform a experimental characterization of a memristive system by using the flux-charge notation, and present a discussion of the influence of the waveform's frequency and shape.

### 3. The Dynamic Route Map

It is common knowledge that Nonlinear Dynamics are illustrated and further studied by utilizing the state space (otherwise known as the phase space) approach. This approach was initially introduced by J. Liouville [51], further utilized by H. Poincaré to study the three-body problem [52]. Since then, the study of nonlinear systems and the relevant methods in nonlinear dynamics have been developed within the phase space approach. This was due to the fact that important features and attributed of nonlinear systems are clearly emerging within the state space. It should be noted that the case of the two-dimensional phase space, also mentioned as phase portrait (( $x = t^2 + t^2 +$

On the other hand, the study of memristors is conducted within the previously described framework (Section 2), where the dynamics of an extended memristor that is flux-controlled is presented. It is apparent that due to the principle of duality, the corresponding charge-controlled extended memristor could be easily described within the same frame. Clearly, memristors are nonlinear elements and that is due to their hysteretic behaviour, which is their main fingerprint [54]. As a result, phase space emerges as the proper space for studying memristor dynamics and this way useful information on their dynamical properties could be provided. Toward this, a new tool in the phase space, the recently introduced, novel technique of the Dynamic Route Map has been proposed for studying memristor devices. This technique allows for acquiring information regarding their switching properties and features in general [55].

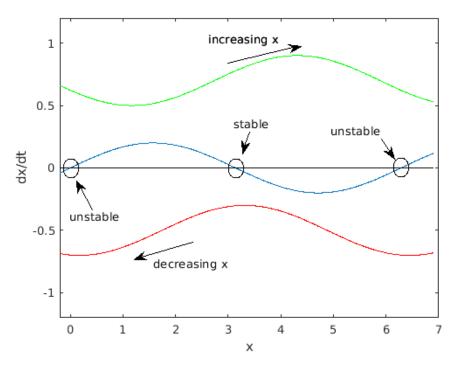

The dynamic route concept within the phase space as this was applied in the case of memristors, considers the definition of the trajectory of one of the system's state variables as the voltage or the current through the device (according on whether the memristor is flux or charge controlled) gets a specific value. This procedure can be considered to be equivalent to plotting equation 4. Expanding this concept from a specific trajectory to a family of trajectories, the Dynamic Route Map is defined as a a parametric collection of a theoretically infinite number of dynamic routes [55]. An illustration of a typical DRM is presented in Figure 1, where three representative cases of DRM are presented. The one in the middle is a characteristic case that includes one stable and two unstable equilibria. It is apparent that the DRM is infinitely dense and that for properly visualizing it usually only a finite number of them is presented.

A comprehensive apposition of the features demonstrated by the DRM technique appears in [55]). For the reader's convenience, we present the most important in the lines that follow:

- Any point belonging to the positive half-plane,i.e., dx/dt > 0 moves to the right of its dynamic route, thus increasing the value of variable x.

- any point belonging to the negative half-plane,i.e., dx/dt < 0 moves to the left of its dynamic route, thus decreasing the value of variable x.

- The higher a dynamic route is located, the faster a point will move along it, as long as this route belongs to the upper half-plane (thus its points move to the right).

- The lower a dynamic route is, the faster a point will travel along it, as long as this route belongs to the lower half-plane (thus its points move to the left).

- All the points with null velocity dx/dt = 0),i.e., those found on the horizontal axis, define equilibrium states of the system, and are called equilibrium points.

- Equilibrium points may be stable or unstable. This means that the dynamic routes that lead to them may converge towards them or diverge from them, correspondingly.

It is very important to mention that the dynamic route corresponding to a null parameter value (i.e. for memristors that would be a voltage v=0 or a current i=0) defines the so-called Power-Off Plot (POP), which provides the stability points [?]. In specific, memristors having one stable and two unstable equilibria appear to be volatile, while memristors with one unstable and two stable equilibrium points appear to be non-volatile.

As a final point, we would like to mention that the DRM can be used to study the dynamics of the switching process in a memristive device (i.e. the setting and resetting

**Figure 1.** Example of an arbitrary typical DRM. The three curves correspond to three different situations: the blue line presents three intersection points with zero, thus showing that the system, for that case, has two unstable and a stable points. The red line shows a case where the variable x is always decreasing, while the green line shows the opposite case where x is always growing.

procedures). These dynamics can be visualized on the DRM, since these two operations are achieved when the operation point is obliged to shift its dynamic route, during some time; something that happens when positive or negative voltage pulses are applied, further resulting in switching between two equilibria.

## 4. Experimental Results

# 4.1. Description of the used devices

The devices used are  $TiN/Ti/HfO_2/W$  metal–insulator–metal (MIM) stacks [56]. They were made on a 100 mm-diameter Si-n<sup>++</sup> wafer by doing first a deposition of a 200 nm-thick Ti adherence layer, which was then followed by a deposition of a 50 nm-thick W layer. Both of those layers were grown using Magnetron sputtering. A plasma-enhanced chemical vapor deposition (PECVD) using silane (SiH<sub>4</sub>) as the precursor process was used to create a 100 nm SiO<sub>2</sub> isolation oxide. This was in turn patterned using photolithography and dry etching. The apertures of the SiO<sub>2</sub> layer define the active area of the MIM devices. After that, the 10 nm HfO<sub>2</sub> film was deposited by atomic layer deposition (ALD) at 225 °C using Tetrakis(dimethylamino)hafnium (TDMAH) and H<sub>2</sub>O as precursors and N<sub>2</sub> as the carrier and purge gas. Magnetron sputtering was used again to define the top electrode as a metal layer of 10 nm-thick Ti and a 200 nm-thick TiN. The electrode was patterned by a lift-off process.

During the last step, magnetron sputtering was used to deposite a 500 nm Al layer on the back of the wafer for electrically contacting the botton electrode through the Si-n<sup>++</sup> substrate used to fabricate the devices. The final TiN/Ti/HfO<sub>2</sub>/W devices present a square shape, and the fabricated areas range between 22 um<sup>2</sup> and 120120 um<sup>2</sup>

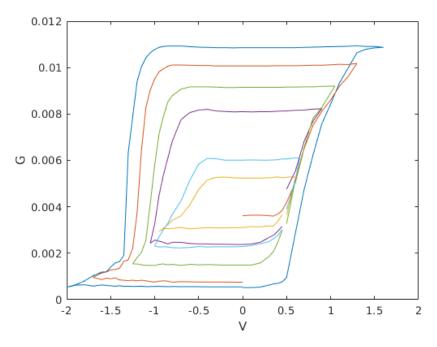

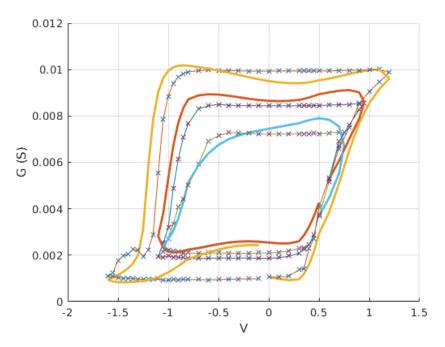

A typical curve representing the evolution of the conductance *G* for a set of different amplitudes of a triangular input waveform is presented in Fig. 2.

**Figure 2.** Measured values of the conductance G (in S), for different amplitudes of the applied input waveform.

#### 4.2. Model Generation

The previous sections describe the theoretical framework. In this section, following the work published in [?], we propose using a experimental approximation to the variation of the memristance:

$$i = \frac{1}{M} v = G v \tag{12}$$

where the dynamics of the memconductance *G* is determined by a differential equation:

$$\frac{dG}{dt} = g_G(G, v) \tag{13}$$

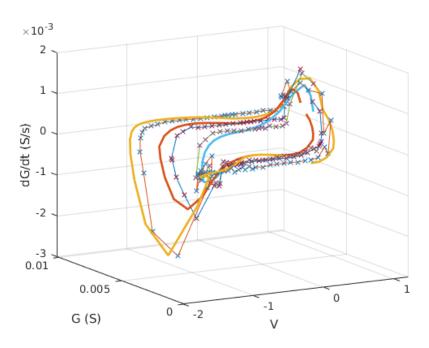

It is clear that Eq. 13 corresponds to a possible DRM. Due to our election of G as the variable of interest, it is possible to calculate an approximation for dG/dt from the experimental data, plotting it as a function of G and v.

As a first step, we have approximated the temporal variation of *G* by a discrete approximation:

$$\frac{dG}{dt} \approx \frac{G(t) - G(t - dt)}{dt} \tag{14}$$

where dt is the time interval between two samples. Once this is calculated, we can plot the DRM for this data as a 3D picture, as shown in Fig. 3. This Figure shows a subset of the data, marked as the lines with a 'x' symbol. This subset of data has been then used to obtain an approximation to Eq. 13 with a polynomial function (using MATLAB *polyfit55*).

$$g_G(G, v) \approx \sum_{i=0..5, j=0..3} p_{i,j} v^i G^j$$

(15)

The value of each coefficient  $p_{i,j}$  is provided in Table 1, together with the 95% confidence

Table 1: Coefficients for the approximation of  $g_G$  in Eq. 15. The units for coefficient  $p_{ij}$  are  $s^{-1}V^{-i}\Omega^{j-1}$ .

| Coefficient     | Value     | 95% Confidence         |

|-----------------|-----------|------------------------|

| p <sub>00</sub> | -3.19E-04 | (-5.93E-04, -4.56E-05) |

| $p_{10}$        | 3.77E-04  | (-1.03E-04, 8.57E-04)  |

| p <sub>01</sub> | 3.42E-01  | (-7.88E-02, 7.63E-01)  |

| p <sub>20</sub> | 1.96E-03  | (1.04E-03, 2.88E-03)   |

| p <sub>11</sub> | -4.70E-01 | (-9.22E-01, -1.84E-02) |

| p <sub>02</sub> | -1.24E+02 | (-3.43E+02, 9.56E+01)  |

| p <sub>30</sub> | 3.52E-03  | (2.18E-03, 4.87E-03)   |

| p <sub>21</sub> | 2.68E-01  | (-2.57E-01, 7.93E-01)  |

| p <sub>12</sub> | 2.28E+02  | (8.40E+01, 3.72E+02)   |

| p <sub>03</sub> | 1.33E+04  | (-3.44E+04, 6.10E+04)  |

| $p_{40}$        | 2.26E-03  | (1.37E-03, 3.14E-03)   |

| p <sub>31</sub> | -1.41E-01 | (-5.16E-01, 2.34E-01)  |

| p <sub>22</sub> | -1.62E+02 | (-2.46E+02, -7.74E+01) |

| p <sub>13</sub> | -3.65E+04 | (-5.37E+04, -1.93E+04) |

| $p_{04}$        | -4.13E+04 | (-4.57E+06, 4.49E+06)  |

| p <sub>50</sub> | 4.40E-04  | (2.31E-04, 6.48E-04)   |

| p <sub>41</sub> | -2.46E-01 | (-3.50E-01, -1.42E-01) |

| p <sub>32</sub> | -2.41E+01 | (-4.71E+01, -9.93E-01) |

| p <sub>23</sub> | 1.15E+04  | (7.47E+03, 1.55E+04)   |

| $p_{14}$        | 1.80E+06  | (1.11E+06, 2.49E+06)   |

| p <sub>05</sub> | -3.56E+07 | (-1.92E+08, 1.20E+08)  |

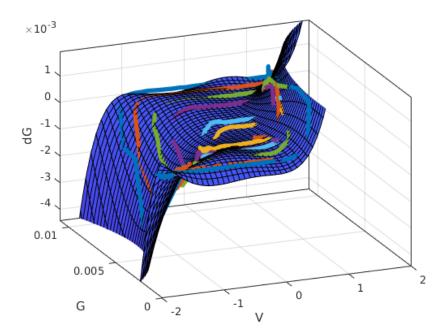

interval, as provided by MATLAB. Notice that this polynomial is actually an approximation to  $g_G$ . Figure 4 shows the surface defined by this approximation and the original data.

The validity of the proposed method has been tested using the fitted polynomial approximation to predict the response of the system to a specific input. This has been done by integrating the differential equation system formed by Equation 12 and 13, where  $g_M$  is the fitted approximation using the coefficients from Table 1 and the initial condition was chosen as the experimental initial value of G. The results of this integration are depicted in Fig. 5, where the thick lines are the model and the thin lines featuring symbols correspond to experimental data. The coincidence between the real data and the predicted by the model values is evident, and it could be improved by using a different approximation to the DRM, as for instance the so-called hysterons proposed in [57].

#### 5. Discussion

As has been shown in the paper, the considered ReRAM devices can be modelled as ideal memristors using the formal framework proposed by Corinto et al [42] along with an experimental approximation to the differential equation governing the behavior of the memristance. This approximation has been calculated using a polynomial fitting to the experimental data. The results have been obtained by integration of this approximation plus the standard equations defined in Section 2. The comparison between the model and the experimental data show a fairly good agreement, justifying the used approach.

Further work related to this should be performed to check this conclusion. Specifically, the effect of the input signal velocity has to be tested, as well as the variability in the cycle to cycle switching characteristics.

**Author Contributions:** Conceptualization, R.P., S.S. and M.A.; methodology, R.P., S.S. and L.C.; software, R.P. and M.A.; validation, R.P., S.D. and H.C.; formal analysis, R.P., S.S. and M.A.; investigation, R.P., S.S., C.B., S.D. and H.C.; resources, R.P., S.D., H.C. and E.H.; data curation, R.P., S.D. and H.C.; writing—original draft preparation, R.P., S.S. and M.A.; writing—review and editing, R.P., S.S., M.A., C.B., S.D., H.C., E.H. and L.C.; visualization, R.P. and S.S.; supervision, R.P. and

**Figure 3.** Experimental DRM, showing only a subset of the measured curves. Notice that this figure can be reduced to Fig. 2 if the dG/dt axis is ignored.

Figure 4. Surface fitting of the data in Fig. 3 using a polynomial.

**Figure 5.** Results obtained using Eq. 15 with the coefficients in Table 1 into Eq. 13.

M.A.; project administration, R.P.; funding acquisition, R.P., S.D. and H.C. All authors have read and agreed to the published version of the manuscript.

Funding: This research received no external funding.

Data Availability Statement: Data may be obtained from the authors by a reasonable petition.

Acknowledgments: N/A.

**Conflicts of Interest:** The authors declare no conflict of interest. The funders had no role in the design of the study; in the collection, analyses, or interpretation of data; in the writing of the manuscript, or in the decision to publish the results.

#### References

- 1. Chua, L.O. Memristor-the missing circuit element. *Circuit Theory, IEEE Transactions on* **1971**, *18*, 507–519.

- 2. Prodromakis, T.; Toumazou, C.; Chua, L. Two centuries of memristors. *Nature materials* **2012**, *11*, 478–481.

- 3. Chua, L.; Kang, S.M. Memristive devices and systems. *Proceedings of the IEEE* **1976**, *64*, 209–223. doi:10.1109/PROC.1976.10092.

- 4. Tetzlaff, R. Memristors and memristive systems; Springer, 2013.

- 5. Sebastian, A.; Le Gallo, M.; Khaddam-Aljameh, R.; Eleftheriou, E. Memory devices and applications for in-memory computing. *Nature nanotechnology* **2020**, *15*, 529–544.

- 6. Kim, H.; Sah, M.P.; Yang, C.; Chua, L.O. Memristor-based multilevel memory. Cellular nanoscale networks and their applications (CNNA), 2010 12th international workshop on. IEEE, 2010, pp. 1–6.

- 7. Stathopoulos, S.; Khiat, A.; Trapatseli, M.; Cortese, S.; Serb, A.; Valov, I.; Prodromakis, T. Multibit memory operation of metal-oxide bi-layer memristors. *Scientific reports* **2017**, *7*, 1–7.

- 8. Eshraghian, K.; Cho, K.R.; Kavehei, O.; Kang, S.K.; Abbott, D.; Kang, S.M.S. Memristor MOS content addressable memory (MCAM): Hybrid architecture for future high performance search engines. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems* **2011**, *19*, 1407–1417.

- 9. Gouder, A.; Jimenez-Solano, A.; Vargas-Barbosa, N.M.; Podjaski, F.; Lotsch, B.V. Photomemristive sensing with charge storing 2D carbon nitrides. *arXiv preprint arXiv:2109.06964*

- 10. Carrara, S. The Birth of a New Field: Memristive Sensors. A Review. *IEEE Sensors Journal* **2020**, 21, 12370–12378.

- 11. Carrara, S.; Sacchetto, D.; Doucey, M.A.; Baj-Rossi, C.; De Micheli, G.; Leblebici, Y. Memristive-biosensors: A new detection method by using nanofabricated memristors. *Sensors and Actuators B: Chemical* **2012**, 171, 449–457.

- 12. Gupta, I.; Serb, A.; Khiat, A.; Zeitler, R.; Vassanelli, S.; Prodromakis, T. Memristive integrative sensors for neuronal activity. *arXiv preprint arXiv:1507.06832* **2015**.

- 13. Yao, P.; Wu, H.; Gao, B.; Tang, J.; Zhang, Q.; Zhang, W.; Yang, J.J.; Qian, H. Fully hardware-implemented memristor convolutional neural network. *Nature* **2020**, *577*, 641–646.

- Pershin, Y.V.; Di Ventra, M. Experimental demonstration of associative memory with memristive neural networks. *Neural Networks* 2010, 23, 881–886.

- 15. Li, C.; Belkin, D.; Li, Y.; Yan, P.; Hu, M.; Ge, N.; Jiang, H.; Montgomery, E.; Lin, P.; Wang, Z.; others. Efficient and self-adaptive in-situ learning in multilayer memristor neural networks. *Nature communications* **2018**, *9*, 1–8.

- 16. Grollier, J.; Querlioz, D.; Stiles, M.D. Spintronic Nanodevices for Bioinspired Computing. *Proceedings of the IEEE* **2016**, *104*, 2024–2039.

- 17. Strukov, D.B.; Snider, G.S.; Stewart, D.R.; Williams, R.S. The missing memristor found. *nature* **2008**, 453, 80–83.

- 18. Dias, C.; Lv, H.; Picos, R.; Aguiar, P.; Cardoso, S.; Freitas, P.; Ventura, J. Bipolar resistive switching in Si/Ag nanostructures. *Applied Surface Science* **2017**.

- 19. Brivio, S.; Tallarida, G.; Cianci, E.; Spiga, S. Formation and disruption of conductive filaments in a HfO<sub>2</sub>/TiN structure. *Nanotechnology* **2014**, *25*, 385705.

- Mohammad, B.; Jaoude, M.A.; Kumar, V.; Al Homouz, D.M.; Nahla, H.A.; Al-Qutayri, M.; Christoforou, N. State of the art of metal oxide memristor devices. *Nanotechnology Reviews* 2016, 5, 311–329.

- 21. Sun, B.; Zhang, X.; Zhou, G.; Li, P.; Zhang, Y.; Wang, H.; Xia, Y.; Zhao, Y. An organic nonvolatile resistive switching memory device fabricated with natural pectin from fruit peel. *Organic Electronics* **2017**, *42*, 181–186.

- 22. Battistoni, S.; Dimonte, A.; Erokhin, V. Organic Memristor Based Elements for Bio-inspired Computing. In *Advances in Unconventional Computing*; Springer, 2017; pp. 469–496.

- 23. Kalomiros, J.; Stavrinides, S.G.; Corinto, F. A two-transistor non-ideal memristor emulator. Modern Circuits and Systems Technologies (MOCAST), 5th International Conference on. IEEE, 2016, pp. 1–4.

- 24. Camps, O.; Al Chawa, M.M.; de Benito, C.; Roca, M.; Stavrinides, S.G.; Picos, R.; Chua, L.O. A Purely Digital Memristor Emulator based on a Flux-Charge Model. 2018 25th IEEE International Conference on Electronics, Circuits and Systems (ICECS). IEEE, 2018, pp. 565–568.

- 25. Al Chawa, M.M.; de Benito, C.; Roca, M.; Picos, R.; Stavrinides, S. Design and implementation of passive memristor emulators using a charge-flux approach. 2018 IEEE International Symposium on Circuits and Systems (ISCAS). IEEE, 2018, pp. 1–5.

- 26. Camps, O.; Picos, R.; de Benito, C.; Al Chawa, M.M.; Stavrinides, S.G. Emulating memristors in a digital environment using stochastic logic. 2018 7th International Conference on Modern Circuits and Systems Technologies (MOCAST). IEEE, 2018, pp. 1–4.

- 27. Yu, S.; Jiang, H.; Huang, S.; Peng, X.; Lu, A. Compute-in-Memory Chips for Deep Learning: Recent Trends and Prospects. *IEEE Circuits and Systems Magazine* **2021**, 21, 31–56.

- 28. Picos, R.; Roldan, J.; Al Chawa, M.; Jimenez-Molinos, F.; Garcia-Moreno, E. A physically based circuit model to account for variability in memristors with resistive switching operation. Design of Circuits and Integrated Systems (DCIS), Conference on. IEEE, 2016, pp. 1–6.

- 29. Naous, R.; Al-Shedivat, M.; Salama, K.N. Stochasticity modeling in memristors. *IEEE Transactions on Nanotechnology* **2016**, *15*, 15–28.

- 30. Panda, D.; Sahu, P.P.; Tseng, T.Y. A collective study on modeling and simulation of resistive random access memory. *Nanoscale research letters* **2018**, *13*, 1–48.

- 31. Kolka, Z.; Biolek, D.; Biolkova, V.; Biolek, Z. Evaluation of memristor models for large crossbar structures. Radioelektronika (RADIOELEKTRONIKA), 2016 26th International Conference. IEEE, 2016, pp. 91–94.

- 32. Messaris, I.; Serb, A.; Khiat, A.; Nikolaidis, S.; Prodromakis, T. A compact Verilog-A ReRAM switching model. *arXiv preprint arXiv:*1703.01167 **2017**.

- 33. Georgiou, P.S.; Yaliraki, S.N.; Drakakis, E.M.; Barahona, M. Window functions and sigmoidal behaviour of memristive systems. *International Journal of Circuit Theory and Applications* **2016**.

- 34. Ascoli, A.; Tetzlaff, R.; Chua, L. Continuous and Differentiable Approximation of a TaO Memristor Model for Robust Numerical Simulations. In *Emergent Complexity from Nonlinearity, in Physics, Engineering and the Life Sciences*; Springer, 2017; pp. 61–69.

- Jimenez-Molinos, F.; Villena, M.; Roldan, J.; Roldan, A. A SPICE Compact Model for Unipolar RRAM Reset Process Analysis. IEEE Transactions on Electron Devices 2015.

- 36. Li, Q.; Serb, A.; Prodromakis, T.; Xu, H. A memristor SPICE model accounting for synaptic activity dependence. *PloS one* **2015**, *10*, e0120506.

- 37. Secco, J.; Corinto, F.; Sebastian, A. Flux-Charge Memristor Model for Phase Change Memory. *IEEE Transactions on Circuits and Systems II: Express Briefs* **2017, in press**.

- Picos, R.; Roldan, J.B.; Al Chawa, M.M.; Garcia-Fernandez, P.; Jimenez-Molinos, F.; Garcia-Moreno, E. Semiempirical Modeling of Reset Transitions in Unipolar Resistive-Switching Based Memristors. RADIOENGINEERING 2015, 24, 421.

- 39. Garcia-Moreno, E.; Picos, R.; Al-Chawa, M.M. SPICE model for unipolar RRAM based on a flux-controlled memristor. Power, Electronics and Computing (ROPEC), 2015 IEEE International Autumn Meeting on. IEEE, 2015, pp. 1–4.

- 40. Al Chawa, M.M.; Picos, R.; Roldan, J.B.; Jimenez-Molinos, F.; Villena, M.A.; de Benito, C. Exploring resistive switching-based memristors in the charge–flux domain: a modeling approach. *International Journal of Circuit Theory and Applications* **2018**, pp. n/a–n/a. cta.2397, doi: 10.1002/cta.2397.

- Al Chawa, M.M.; Picos, R. A Simple Quasi-Static Compact Model of Bipolar ReRAM Memristive Devices. IEEE Transactions on Circuits and Systems II: Express Briefs 2020, 67, 390–394.

- 42. Corinto, F.; Civalleri, P.P.; Chua, L.O. A theoretical approach to memristor devices. *IEEE Journal on Emerging and Selected Topics in Circuits and Systems* **2015**, *5*, 123–132.

- Chua, L.O. Everything you wish to know about memristors but are afraid to ask. Radioengineering 2015, 24, 319.

- 44. Shin, S.; Kim, K.; Kang, S.M. Compact models for memristors based on charge-flux constitutive relationships. *Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on* **2010**, 29, 590–598.

- 45. Picos, R.; Al Chawa, M.M.; Roca, M.; Garcia-Moreno, E. A charge-dependent mobility memristor model. Proceedings of the 10th Spanish Conference on Electron Devices, CDE'2015. IEEE, 2015.

- 46. Picos, R.; Roldan, J.B.; Al Chawa, M.M.; Jimenez-Molinos, F.; Villena, M.; Garcia-Moreno, E. Exploring ReRAM-based memristors in the charge-flux domain, a modeling approach. Proceedings of International Conference on Memristive Systems, MEMRISYS'2015, 2015.

- 47. de Benito, C.; Al Chawa, M.M.; Picos, R.; Garcia-Moreno, E. A procedure to calculate a delay model for memristive switches. Workshop on Memristor Technology, Design, Automation and Computing, 2017.

- 48. Theodorakakos, A.; Stavrinides, S.G.; Hatzikraniotis, E.; Picos, R. A non-ideal memristor device. Memristive Systems (MEMRISYS) 2015 International Conference on. IEEE, 2015, pp. 1–2.

- 49. Al Chawa, M.M.; Rodriguez-Fernandez, A.; Bargallo, M.; Campabadal, F.; de Benito, C.; Stavrinides, S.; Garcia-Moreno, E.; Picos, R. Waveform and Frequency Effects on Reset Transition in Bipolar ReRAM in Flux-Charge Space. Memristive Systems (MEMRISYS) 2017 International Conference on. IEEE, 2017.

- 50. Al Chawa, M.M.; Picos, R.; Covi, E.; Brivio, S.; Garcia-Moreno, E.; Spiga, S. Flux-charge characterizing of reset transition in bipolar resistive-switching memristive devices. 11th Spanish Conference on Electron Devices, 2017.

- 51. Liouville, J. Sur la Théorie de la Variation des constantes arbitraires. *Journal des Mathématiques Pures et Applications* **1838**, *3*, 342–349.

- 52. Poincaré, H. Les méthodes nouvelles de la mécanique céleste 1892-99. 3.

- 53. Ehrenfest, P.; Ehrenfest, T. Encyklopadie der mathematischen Wis-senschaften 1911. 4.

- 54. Chua, L.O. If it's pinched it's a memristor. Semiconductor Science and Technology 2014, 29, 104001.

- 55. Chua, L.O. Five non-volatile memristor enigmas solved. Applied Physics A 2018, 124, 563.

- Poblador, S.; Maestro-Izquierdo, M.; Zabala, M.; Gonzalez, M.B.; Campabadal, F. Methodology for the characterization and observation of filamentary spots in HfOx-based memristor devices. *Microelectronic Engineering* 2020, 223, 111232.

- 57. Miranda, E. Compact model for the major and minor hysteretic I–V loops in nonlinear memristive devices. *IEEE Transactions on Nanotechnology* **2015**, *14*, 787–789.

12 of 11